第9期陈德应等:高次谐波产生阿秒极紫外和X光脉冲研究新进展

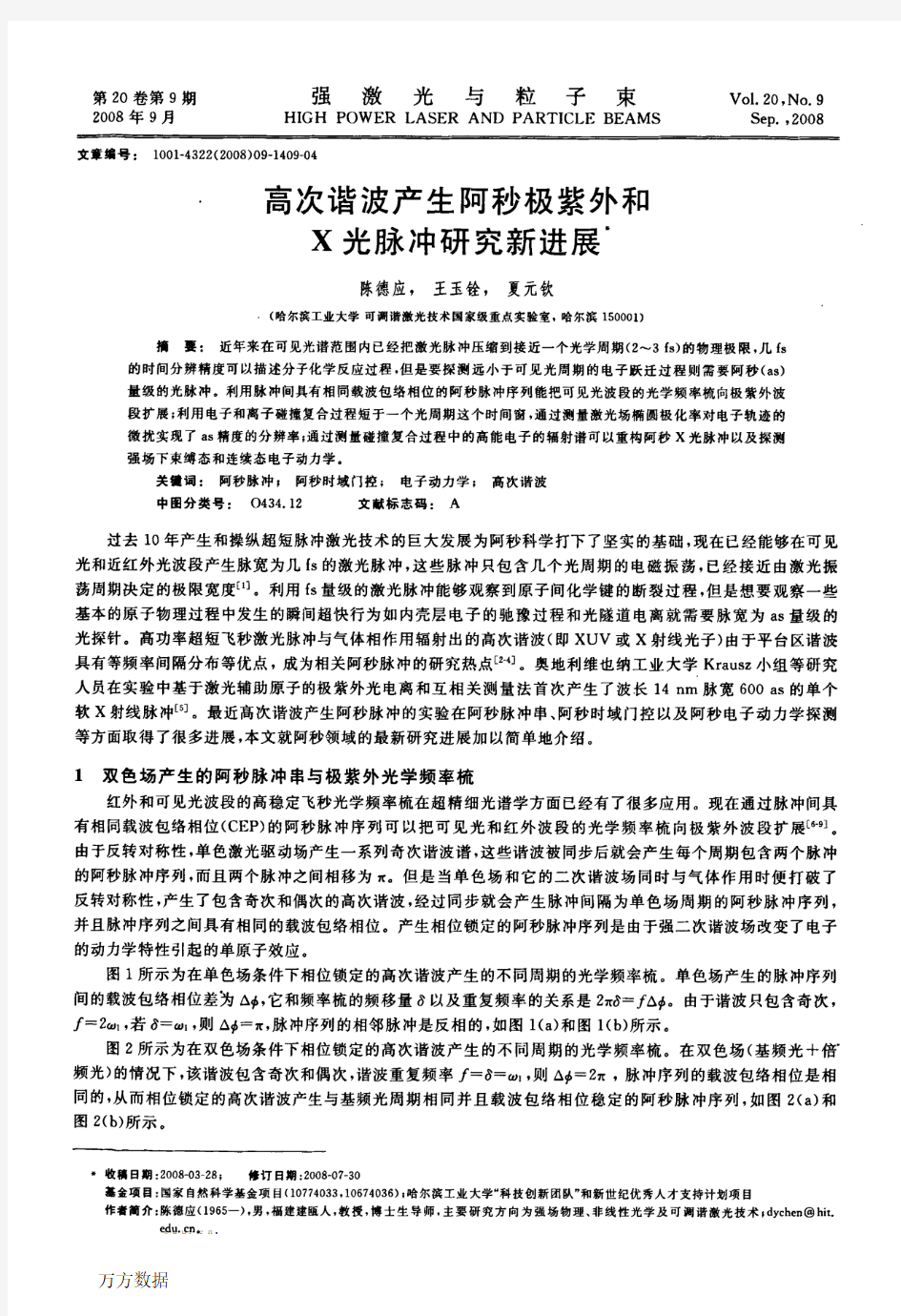

息,比如非弹性散射产生的散射电子的光谱等等。由于电子和离子复合过程短于一个光场周期,利用这个时间窗就可以获得阿秒的分辨率。对电子轨迹产生微扰可以这样实现,在具有椭圆偏振场的基频脉冲中加入一个弱的垂直分量,当电子离开母离子的时候,这个附加的场使电子波包侧向偏移,利用激光场的椭圆极化率和侧移度来测量电子波包的侧向分布。复合电子与母离子的局部作用就是一个空间窗口,椭圆极化率依据电子的空间分布平移空间窗121以阿秒的分辨率给出时间和空间上的信息。如图3(a)所示电子波包产生的侧向移动非线性地与复合时间t和电离时问t“有关,对不同的谐波级次产生的效果也不同,一般累积在短电子轨迹上的侧向位移随着延迟£一“而增大,也随着谐波级次而增大。

图3(b)是实验上测得的氖气中高次谐波信号与椭圆极化率的函数关系,显示出越高级次的谐波对椭圆极化率的变化越敏感。这样对激光偏振状态的轻微调整不仅可以控制总的谐波辐射而且可以很明显地改变谐波谱分布。这种光谱变化被用来求解电子波包动力学,脉冲的时域响应也可以通过测量谐波谱的变化来确定。

3阿秒探测电子动力学

as量级的电子与母离子碰撞复合是很多强场物理现象的核心,许多新的应用都依赖于对这个过程的深入了解,比如产生单个阿秒脉冲、亚埃尺度成像、光学频标的扩展以及产生任意波形as量级脉冲。随着阿秒物理学研究的深入,现在可以利用阿秒极紫外光脉冲来实现电子动力学探测[12。引。由于能量和动量守恒,当电子波包与母离子碰撞复合时,它吸收一个XUV光子产生一个高能电子,由于电子波包是非单色场的,所以在原子核附近发生碰撞复合的电子波包在不同的时刻具有不同的能量,XUV光电子谱就在XUV光脉冲探测的瞬间记录了一个有关碰撞复合能量的阿秒快照。在原子核附近的XUV光脉冲吸收的空间分布就实现了亚埃尺度的空间分辨。通过调整强激光场和XUV探测光脉冲的不同延迟可以在纵深方向探测含时电子数密度和碰撞能量。利用椭圆极化率扫过电子波包获得穿过原子核横截面的电子密度分布。可以设想一个原子就是一个扫描隧道显微镜(STM)的尖端,椭圆极化率相对STM尖端移动,超短XUV脉冲提供了as精度的时间分辨。

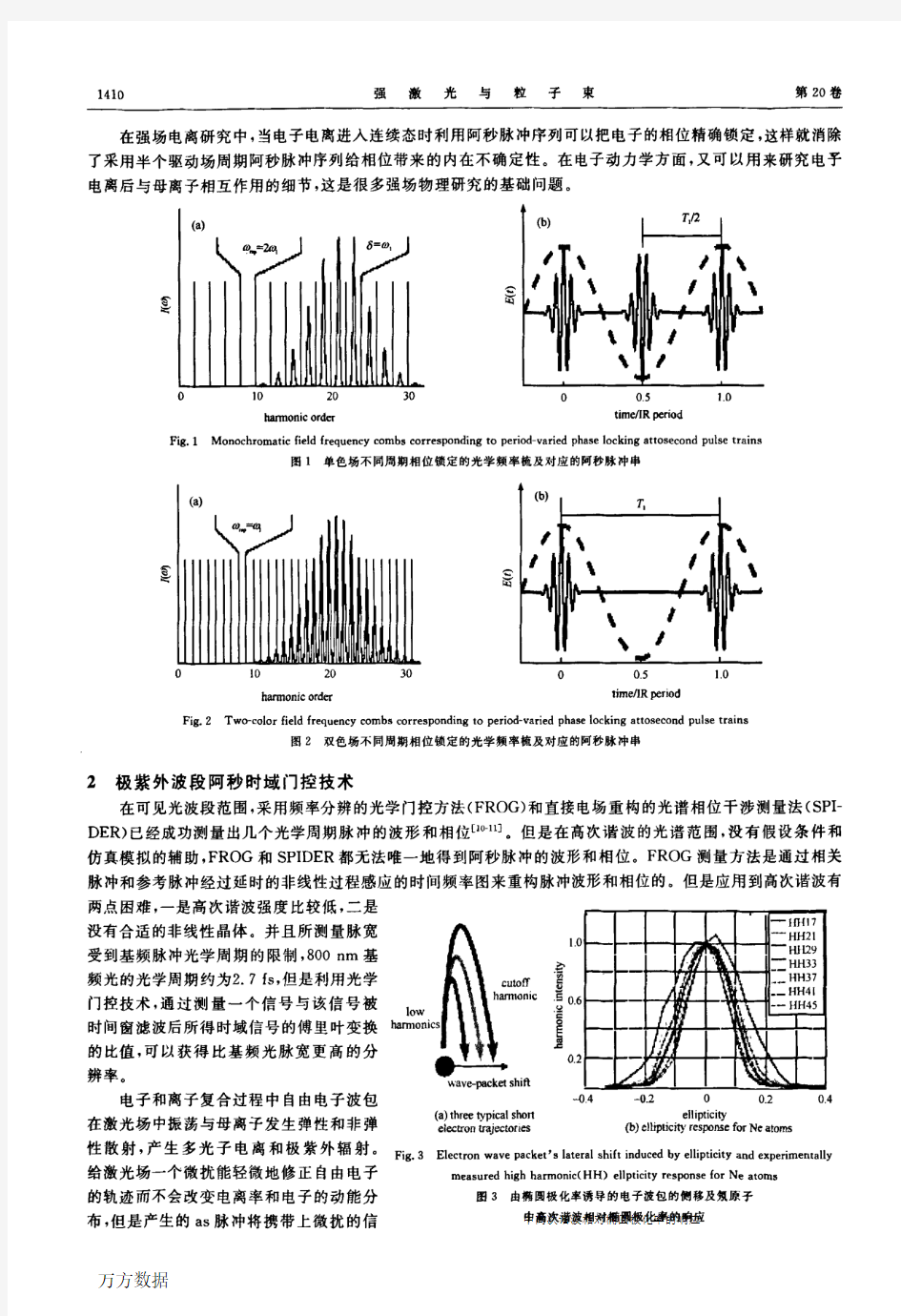

如图4所示,在大多数高能电子返回的时刻,从基态跃迁电子辐射的XUV信号和从碰撞复合波包达到最大值辐射的XUV信号在能量上是分开的。图中最上面圆形突出部分是单光子XUV电离原子释放的电子再散射形成的,里层黑虚线圈部分代表从基态获得的单光子吸收,中间虚线圈是从基态获得的双光子吸收,最外层白虚线圈是碰撞复合信号,从图中可以看出再碰撞复合波包辐射的XUV信号比从基态电子跃迁辐射的XUV信号低6个数量级。原因有两个,一是因为碰撞复合电子波包的横向扩散,二是库仑势的奇点性质导致近核小范围内XUV吸收明显增强。

采用类似光外差测量法可以让强的阈上电离(ATI)电子信号增强弱的碰撞电子信号,如图5所示从颜色上可以判断出测量信号(黑虚线圈标示)强度提高了3个数量级。单光子XUV电离的电子和阈上电离电子之间的干涉也为描述阈上电离峰值相位提供了一种实验方法。总之时间分辨的XUV光谱包含了碰撞复合电子的时间和空间信息,通过仔细分析XUV光谱不仅可以重构阿秒XUV光脉冲而且可以探测强场下束缚态和连续态电子动力学。

e/a.u.

Fig.4Photoelectronspectraof3Dhydrogen

under200asXUV

pulse

radiation图4200asXUV脉冲辐射情况下的

氢原子的3D光电子能谱

P●矗u.

Fig.5InterferencebetweentheXUVandATI

electrons

enhancing

therecollisionsignal图5阈上电离(ATI)和XUV辐射之间

的干涉增强了碰撞信号

高次谐波产生阿秒极紫外和X光脉冲研究新进展

作者:陈德应, 王玉铨, 夏元钦, CHEN De-ying, WANG Yu-quan, XIA Yuan-qin

作者单位:哈尔滨工业大学,可调谐激光技术国家级重点实验室,哈尔滨,150001

刊名:

强激光与粒子束

英文刊名:HIGH POWER LASER AND PARTICLE BEAMS

年,卷(期):2008,20(9)

被引用次数:5次

参考文献(14条)

1.Brabec T;Krausz F Intense few-cycle laser fields:frontiers of nonlinear optics 2000

2.Christov I P;Murnane M M;Kapteyn H C High-harmonic generation of attosecond pulses in the "single-cycle" regime 1997(07)

3.Pukhov A;Gordienko S;Baeva T Temporal structure of attosecond pulses from intense laser-atom interactions 2003

4.Drescher M;Hentschel M;Kienberger R X-ray pulses approaching the attosecond frontier 2001

5.Hentschel M;Kienberger R;Spielmann C Attosecond metrology 2001

6.Mauritsson J;Johnsson P;Gustafsson E Attosecond pulse trains generated using two color laser

fields 2006

7.Nabekawa Y;Shimizu T;Okino T Interferometric autocorrelation of an attosecond pulse train in the single-cycle regime 2006

8.Nikolopoulos L A A;Benis E P;Tzallas P Second order autocorrelation of an XUV attosecond pulse train 2005

9.Jones R J;Moll K D;Thorpe M J Phase-coherent frequency combs in the vacuum ultraviolet via high-harmonic generation inside a femtosecond enhancement cavity 2005

10.Dudovich N;Levesque J;Smirnova O Attosecond temporal gating with elliptically polarized light 2006

11.Kosuge A;Sekikawa T;Zhou X Frequency-resolved optical gating of isolated attosecond pulses in the extreme ultraviolet 2006

12.Lein M Attosecond probing of vibrational dynamics with high-harmonic generation 2005

13.Niikura H;Villeneuve D M;Corkum P B Attosecond light pulses for probing two-electron dynamics of helium in the time domain 2007

14.Smirnova O;Patehkovskii S;Spanner M Direct XUV probing of attosecond electron recollision 2007

本文读者也读过(10条)

1.葛愉成高次谐波辐射发射特性研究[期刊论文]-物理学报2008,57(7)

2.萧珺高次谐波和阿秒脉冲的优化[学位论文]2005

3.兰鹏飞飞秒激光驱动的阿秒脉冲光源产生及控制[学位论文]2009

4.余晓光.颜根英.万慧军.阮文.谢安东.YU Xiao-guang.YAN Gen-ying.WAN Hui-jun.RUAN Wen.XIE An-dong在不同激光脉宽下的高次谐波[期刊论文]-原子与分子物理学报2006,23(5)

5.霍义萍.曾志男.李儒新阿秒脉冲测量的研究进展[期刊论文]-物理2004,33(12)

6.胡杰.刘锋.HU Jie.LIU Feng分子与强激光场相互作用的最新研究进展[期刊论文]-激光与光电子学进展

2007,44(10)

7.陈基根.CHEN Ji-Gen强短脉冲辐照叠加态原子增强阿秒脉冲强度[期刊论文]-原子与分子物理学报2008,25(6)

8.陈基根.杨玉军.曾思良.李琛.朱颀人.CHEN Ji-gen.YANG Yu-jun.ZENG Si-liang.LI Chen.ZHU Qi-ren采用组合脉冲驱动生成单一的X射线阿秒脉冲[期刊论文]-原子与分子物理学报2007,24(2)

9.谢建坤电力系统高次谐波的危害及防制措施[期刊论文]-科技信息2010,2(17)

10.杨林高次谐波产生的主要原因、危害及其抑制措施[期刊论文]-中国科技信息2007(17)

引证文献(3条)

1.叶苗,王其华基于再生锁模控制的激光器高次谐波研究[期刊论文]-激光与红外 2010(11)

2.王超,康轶凡,田进寿,刘虎林两类单阿秒脉冲产生技术的相位依赖性分析[期刊论文]-激光技术 2012(04)

3.卢发铭千赫兹飞秒激光驱动17-40nm高次谐波辐射研究[学位论文]硕士 2009

引用本文格式:陈德应.王玉铨.夏元钦.CHEN De-ying.WANG Yu-quan.XIA Yuan-qin高次谐波产生阿秒极紫外和X光脉冲研究新进展[期刊论文]-强激光与粒子束 2008(9)

设计题目:秒脉冲发生器的设计 设计小组:第三组

1 秒脉冲发生器整体设计方案 1.1秒脉冲发生设计方案概述 秒脉冲发生器是由100HZ时钟产生电路和分频电路两部分构成,其中100HZ时钟产生电路主要由555定时器组成的时钟电路,主要用来产生100HZ的脉冲信号;分频电路主要由74LS192组成的100进制计数器电路,主要用于将100HZ 脉冲信号分成1HZ脉冲信号。该方案通过了Multisim软件仿真,并得到了1HZ的脉冲信号,基本实现了工程训练的要求。

1.2 秒脉冲发生器整体设计电路设计图 图1 秒脉冲发生器整体设计电路设计图1.3 秒脉冲发生器整体设计电路仿真图 图2 秒脉冲发生器整体设计电路仿真图

2 各分电路的元件介绍及设计方案 2.1 100HZ时钟产生电路 图3 100HZ时钟产生电路 2.1.1元件介绍 555芯片引脚图及引脚描述: 555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。 1脚为地。2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。 当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平; 2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。 4脚是复位端,当4脚电位小于0.4V时,不管2、6脚状态如何,输出端3脚都输出低电平。 5脚是控制端。

4 脉冲信号产生电路 4.1 实验目的 1.了解集成单稳态触发器的基本功能及主要应用。 2.掌握555定时器的基本工作原理及其性能。 3.掌握用555定时器构成多谐振荡器、单稳态触发器的工作原理、设计及调试方法。 4.2 实验原理 1.集成单稳态触发器及其应用 在数字电路的时序组合工作中,有时需要定时、延时电路产生定时、展宽延时等脉冲,专门用于完成这种功能的IC,就是“单稳延时多谐振荡器”,也称“单稳触发器”。其基本原理是利用电阻、电容的充放电延时特性以及电平比较器对充放电电压检测的功能,实现定时或延时,只需按需要灵活改变电阻、电容值大小,就可以取得在一定时间范围的延时或振荡脉冲输出。常用的器件有LS121/122、LS/HC123、LS/HC221、LS/HC423、HC/C4538及CC4528B等。 集成单稳态触发器在没有触发信号输入时,电路输出Q=0,电路处于稳态;当输入端输入触发信号时,电路由稳态转入暂稳态,使输出Q=1;待电路暂稳态结束,电路又自动返回到稳态Q=0。在这一过程中,电路输 出一个具有一定宽度的脉冲,其宽度与电路的外接定时元件C ext 和R ext 的数 值有关。 图4-1

集成单稳态触发器有非重触发和可重触发两种,74LS123是一种双可重触发的单稳态触发器。它的逻辑符号及功能表如图4-1、表4-1所示。 在表4-1中“正”为正脉冲,“负”为负脉冲。 LS/HC123的特点是,复位端CLR也具有上跳触发单稳态过程发生的功能。 在C ext >1000pF时,输出脉冲宽度t w ≈0.45R ext C ext 。 器件的可重触发功能是指在电路一旦被触发(即Q=1)后,只要Q还未恢复到0,电路可以被输入脉冲重复触发,Q=1将继续延长,直至重复触发的最后一个触发脉冲的到来后,再经过一个t w (该电路定时的脉冲宽度)时间,Q才变为0,如图4-2所示: 图4-2 74LS123的使用方法: (1)有A和B两个输入端,A为下降沿触发,B为上升沿触发,只有AB=1时电路才被触发。 (2)连接Q和A或Q与B,可使器件变为非重触发单稳态触发器。 (3)CLR=0时,使输出Q立即变为0,可用来控制脉冲宽度。 (4)按图4-3、3-5-4连接电路,可组成一个矩形波信号发生器,利用开关S瞬时接地,使电路起振。 图4-3 图4-4 2.555时基电路及其应用 555时基电路是一种将模拟功能和数字逻辑功能巧妙地结合在同一硅片上的新型集成电路,又称集成定时器,它的内部电路框图如图4-5所示。 图4-5 电路主要由两个高精度比较器C 1、C 2 以及一个RS触发器组成。比较器 的参考电压分别是2/3V CC 和1/3V CC ,利用触发器输入端TR输入一个小于 1/3V CC 信号,或者阈值输入端TH输入一个大于2/3V CC 的信号,可以使触发 器状态发生变换。CT是控制输入端,可以外接输入电压,以改变比较器的参考电压值。在不接外加电压时,通常接0.01μF电容到地,DISC是放电输入端,当输出端的F=0时,DISC对地短路,当F=1时,DISC对地开路。 R D 是复位输入端,当R D =0时,输出端有F=0。 器件的电源电压V CC 可以是+5V~+15V,输出的最大电流可达200mA,当 电源电压为+5V时,电路输出与TTL电路兼容。555电路能够输出从微秒级到小时级时间范围很广的信号。 (1)组成单稳态触发器 555电路按图4-6连接,即构成一个单稳态触发器,其中R、C是外接定时元件。单稳态触发器的输出脉冲宽度t w ≈1.1RC。 图4-6 (2)组成自激多谐振荡器 图4-7 自激多谐振荡器电路 按图4-7连接,即连成一个自激多谐振荡器电路,此电路的工作过程

一、硬件电路设计 (1)复位电路 复位是使单片机处于某种确定的初始状态。单片机工作从复位开始。在单片机RST引脚引入高电平并保持2个机器周期,单片机就执行复位操作。复位操作有两种基本方式:一种是上电复位,另一种是上电与按键均有效的复位。如图1所示为复位电路: 图1复位电路 开机瞬间RST获得高电平,随着电解电容C3的充电,RST引脚的高电平将逐渐下降。若该高电平能保持足够2个机器周期,就可以实现复位操作。根据经典电路选择参数,选取C3=10μF,R1=10KΩ。 (2)晶振电路 单片机的时钟信号通常有两种产生方式:一是内部时钟方式,二是外部时钟方式。内部时钟方式是利用单片机内部的振荡电路产生时钟信号。外部时钟方式是把外部已有的时钟信号引入到单片机内。本次设计中,采用的是12MHz晶振,配上30pF的电容,构成谐振,这样有助于输出稳定的波形。图2所示为晶振电路: 图2晶振电路

在单片机的XTAL1和XTAL2引脚外接石英晶体(简称晶振),作为单片机内部振荡电路的负载,构成自激振荡器,可在单片机内部产生时钟脉冲信号。C1和C2的作用是稳定振荡频率和快速起振。根据经典电路选择参数,本电路选用晶振12 MHz,C1=C2=33PF。其中晶振周期(或外部时钟信号周期)为最小的时序单位。 (3)串口调试电路 二、程序设计 程序思路说明:只需要4个按键。关于频率和占空比的确定,对于12M晶振,输出频率为1KHZ,这样定时中断次数设定为 10,即10MS 中断一次,则TH0=FF,TL0=F6;由于设定中断时间为10ms,这样可以设 * *定占空比可从1-99%变化。即10ms*100=1s #include

脉冲信号发生器 摘要:本实验是采用fpga方式基于Alter Cyclone2 EP2C5T144C8的简易脉冲信号发生器,可以实现输出一路周期1us到10ms,脉冲宽度:0.1us到周期-0.1us,时间分辨率为 0.1us的脉冲信号,并且还能输出一路正弦信号(与脉冲信号同时输出)。输出模式 可分为连续触发和单次手动可预置数(0~9)触发,具有周期、脉宽、触发数等显示功能。采用fpga计数实现的电路简化了电路结构并提高了射击精度,降低了电路功耗和资源成本。 关键词:FPGA;脉冲信号发生器;矩形脉冲;正弦信号; 1 方案设计与比较 脉冲信号产生方案: 方案一、采用专用DDS芯片的技术方案: 目前已有多种专用DDS集成芯片可用,采用专用芯片可大大简化系统硬件制作难度,部数字信号抖动小,输出信号指标高;但专用芯片控制方式比较固定,最大的缺点是进行脉宽控制,测量困难,无法进行外同步,不满足设计要求。 方案二、单片机法。 利用单片机实现矩形脉冲,可以较方案以更简化外围硬件,节约成本,并且也可以实现灵活控制、能产生任意波形的信号发生器。但是单片机的部时钟一般是小于25Mhz,速度上无法满足设计要求,通过单片机产生脉冲至少需要三条指令,所需时间大于所要求的精度要求,故不可取。 方案二:FPGA法。利用了可编程逻辑器件的灵活性且资源丰富的特点,通过Quartus 软件的设计编写,实现脉冲信号的产生及数控,并下载到试验箱中,这种方案电路简单、响应速度快、精度高、稳定性好故采用此种方案。 2 理论分析与计算 脉冲信号产生原理:输入量周期和脉宽,结合时钟频率,转换成两个计数器的容量,用来对周期和高电平的计时,输出即可产生脉冲信号。 脉冲信号的精度保证:时间分辨率0.1us,周期精度:+0.1%+0.05us,宽度精度:

实验8 脉冲信号产生电路 一、实验目的 1. 掌握用基本门电路构成多谐振荡器的方法。 2. 熟悉单稳态触发器的工作原理和参数选择。 3. 熟悉施密特触发器的脉冲整形和应用。 二、实验原理 脉冲信号产生电路是数字系统中必不可少的单元电路。如同步信号、时钟信号和时基信号等都由它产生。产生脉冲信号的电路通常称为多谐振荡器。它不需信号源,只要加上直流电源,就可以自动产生信号。脉冲的整形通常应用单稳态触发器或施密特触发器实现。 脉冲信号的产生与整形可以用基本门电路来实现。现在已经有集成单稳态触发器、集成施密特触发器。另外用555 定时器也可以产生脉冲或实现脉冲整形。本实验主要研究用基本门电路组成的脉冲产生和整形电路。 1. 多谐振荡器 (1) TTL 门电路构成的多谐振荡器 由于 TTL 门电路 速度快,它 适宜于产生 中频段脉冲 源,图2.8.1 是由TTL 反向器构成的全对称多谐振荡器,若取C1= C2 = C,R1= R2= R,则电路完全对称,电容充放电时间相等,其振荡周期近似为T=1.4 RC。一般R1、R2的取值不超过1K,若取R1= R2 = 500Ω ,C1= C2=100pF~100μF,则其振荡频率的范围为几十赫到几十兆赫。 (2) 环形多谐振荡器 图 2.8.2 是用TTL 与非门构成的环形多谐振荡器,图中取R1=100Ω ,R W在2kΩ ~50kΩ之间变化,可调电容C的变化范围是100pF 到50μF,则振荡频率可从数千赫变到数兆赫。电路的振荡周期为T= 2.2 RC,其中R = R1+R W。

(3) 晶体振荡器 用TTL 或CMOS 门电路构成的振荡器幅度稳定性较好,但频率稳定性较差,一般只能达到10-2~10-3数量级。在对频率的稳定度、精度要求高的场合,选用石英晶体组成的振荡器较为适合。其频率稳定度可达10-5以上。图2.8.3 是用CMOS 芯片CD4069 和 晶体构成的多谐振荡器,C o一般取20pF。C S取10~30pF,其输出频率取决于晶体的固有振荡频率。 2. 单稳态触发器 稳态触发器的特点是它只有一个稳定状态,在外来脉冲的作用下,能够由稳定状态翻转到暂稳态。暂稳态维持一段时间TW 以后,将自动返回到稳定状态。TW大小与触发脉冲无关,仅取决于电路本身的参数。单稳态触发器一般用于定时、整形及延时等。单片集成的单稳态触发器有74LS122,CC4098 等。 图 2.8.4 是用与非门构成的微分型单稳态触发器,其输出脉冲宽度为:Tw= 0.8RC。 3. 施密特触发器 施密特触发器的特点是:电路有两个稳定状态,电路状态的翻转依靠外触发电平来维持。一旦外触发电平下降到一定电平 后,电路 立即恢复 到初始稳 态。其工

1.P W M信号概述 脉冲宽度调制(PWM)信号广泛使用在电力变流技术中,以其作为控制信号可完成DC-DC 变换(开关电源)、DC-AC变换(逆变电源)、AC-AC变换(斩控调压)和AC-DC变换(功率因数校正)。 产生PWM信号的方法有多种,现分别论述如下: 1)普通电子元件构成PWM发生器电路 基本原理是由三角波或锯齿波发生器产生高频调制波,经比较器产生PWM信号。三角波或锯齿波与可调直流电压比较,产生可调占空比PWM信号;与正弦基波比较,产生占空比按正弦规律变化的SPWM信号。 此方法优点是成本低、各环节波形和电压值可观测、易于扩展应用电路等。缺点是电路集成度低,不利于产品化。 2)单片机自动生成PWM信号 基本原理是由单片机内部集成PWM发生器模块在程序控制下产生PWM信号。 优点是电路简单、便于程序控制。缺点是不利于学生观测PWM产生过程,闭环控制复杂和使用时受单片机性能制约。 3)可编程逻辑器件编程产生PWM信号 基本原理是以复杂可编程逻辑器件(CPLD)或现场可编程门阵列器件(FPGA)为硬件基础,设计专用程序产生PWM信号。 优点是电路简单、PWM频率和占空比定量准确。缺点是闭环控制复杂,产生SPWM信号难度大。 4)专用芯片产生PWM信号 是生产厂家设计、生产的特定功能芯片。 优点是使用方便、安全,便于应用到产品设计中。缺点是不利于学生观测PWM产生过程和灵活调节各项参数。 2.电子元件构成PWM发生器电路 图1电子元件构成PWM发生器电路 3.集成芯片SG3525构成PWM发生器电路 一、PWM信号发生电路说明 实验电路中,驱动开关管的PWM信号由专用PWM控制集成芯片SG3525产生(美国

CD4060秒脉冲产生电路 一摘要 数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。诸如按时自动打铃,时间程序自动控制,定时启闭路灯,定时开关烘箱,通断动力设备,甚至各种定时电气的的自动启用等。这些都是以数字时钟作为时钟源的。 数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。目前,数字钟的功能越来越强,并且有多种专门的大规模集成电路可供选择。 经过了数字电路设计这门课程的系统学习,特别经过了关于组合逻辑电路与时序逻辑电路部分的学习,我们已经具备了设计小规模集成电路的能力,借由本次设计的机会,充分将所学的知识运用到实际中去。 二主要技术指标 1.设计一个有时、分、秒(23小时59分59秒)显示的电子钟 2.该电子钟具有手动校时功能 三方案论证与选择 要想构成数字钟,首先应选择一个脉冲源——能自动地产生稳定的标准时间脉冲信号。而脉冲源产生的脉冲信号的频率较高,因此,需要进行分频,使高频脉冲信号变成适合于计时的低频脉冲信号,即“秒脉冲信号”(频率为1HZ)。经过分频器输出的秒脉冲信号到计数器中进行计数。将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。“时计数器”采用24进制计时器,可实现对一天24小时的累计。此时需要分别设计60进制,24进制计数器,各计数器输出信号经译码器到数字显示器,使“时”、“分”、“秒”得以数字显示出来。 值得注意的是:任何计时装置都有误差,因此应考虑校准时间电路。校时电路一般采用手动调整。手动调整可利用手动的节拍调准显示时间。 CD4060由一振荡器和14级二进制串行计数 器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。所有的计数器位均为主从触发器。在CP1(和CP0)的下降沿计数器以二进制进行计数。在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间无限制。 CD4060引脚图:

秒信号发生器电路图两个 秒信号发生器: 下面介绍的秒信号发生器可用在LED数字钟中,为数字钟提供秒基准信号。字串7 附图1电路由14位二进制串行计数器/分频器和振荡器 CD4060、BCD同步加法计数器CD4518构成的秒信号发生器。 电路中利用CD4060组成两部分电路。一部分是14级分频器,其最高分频数为16384;另一部分是由外接电子表用石英晶体、电阻及电容构成振荡频率为32768Hz的振荡器。震荡器输出经14级分频后在输出端Q14上得到1/2秒脉冲并送入由1/2 CD4518构成的二分频器,分频后在输出断Q1上得到秒基准脉冲。 检验电路是否工作,可测量CD4060的9脚有无振荡信号输出。调整微调电容可校准振荡频率。 附图2是另一款秒信号发生器电路。它由双BCD同步加计数器CD4518、四输入端与非门CD4011和四2输入端或非门CD4001等构成。 电路中利用CD4060组成两部分电路。一部分是14级分频器,

其最高分频数为16384;另一部分是由外接电子表用石英晶体、电阻及电容构成振荡频率为32768Hz的振荡器。震荡器输出经14级分频后在输出端Q14上得到1/2秒脉冲并送入由1/2 CD4518构成的二分频器,分频后在输出断Q1上得到秒基准脉冲。 检验电路是否工作,可测量CD4060的9脚有无振荡信号输出。调整微调电容可校准振荡频率。 电路中,由CD4011门I构成晶体振荡电路产生的1MHz脉冲信号,经反相器门II送至由CD4518构成的多级计数分频器。其中第一级10分频后输出为100KHz,第二级输出为10KHz,第三级输出为1000Hz,第四级输出为100Hz、第6级输出为1Hz。 由CD4011的门III、IV构成R-S触发器和CD4001的一个门组成了秒信号控制门。单允许工作开关K3置“开”位置时,允许输出秒信号;置“关”位置时,禁止输出秒信号。走时、校准开关K2置“走时”位置时,输出秒信号;置“校准”位置时,输出校准信号。若秒信号与标准时间相差较大,把K1置“快校”位置,送出10KHz信号;若接近标准时间,则置“慢校”位置,送出100Hz信号。

脉冲发生器工作原理 泥浆流动引起叶轮在其外部旋转。叶轮和脉冲发生器内部的主轴含有强力磁铁。叶轮与主轴之间的磁耦合运动产生两者间的磁力吸引。当叶轮在脉冲发生器外部旋转时,主轴则由于磁耦合作用在脉冲发生器内部旋转。 这是叶轮,这是主轴。把主轴伸入到叶轮里,来讲述这种磁耦合的强度。当试图转动主轴时,而主轴依然粘附在叶轮上。想转到主轴是非常困难的,磁耦合作用是相当强的。 脉冲发生器是一个充满油的密封单元。任何外部压力,象静水压力,可以通过这种活动的橡胶皮囊传递到脉冲发生器内部,或者对于没有橡胶皮囊的脉冲发生器,它是通过这个壳体里的活塞传递的。脉冲发生器内部与外部的压力是平衡的。由于脉冲发生器总与它周围的环境处于压力相等的状态,这样它不易损坏。压力平衡是由脉冲发生器的小直径促成的。脉冲发生器的壁较薄,能够承受足够的机械载荷,由于内外压力平衡,不必承受外部压力。 脉冲发生器内含有一个液压泵,液压泵是由六个柱塞和液缸组成。这六个柱塞随着其下端旋转斜盘的转动,在液缸内交替上下运动。通过六个柱塞的交替运动,把泵下端腔里的油,通过一组单流阀泵入到提升阀活塞液缸里。 这是活塞。在产生脉冲过程中,活塞被向上推入液缸里,使提升阀轴伸出。当活塞向上运动时,打开了液缸壁上的一组小孔,使液流回到液缸里,因此起到限制活塞继续运动和降低内部压力。 在主轴的下端是电磁发电机。它是由六个固定的线圈和八个磁极构成,当主轴旋转时,带动其下端的磁极相对线圈转动,线圈内磁场的变化从而产生电流。 主轴的旋转速度控制液压和产生电量的大小。主轴转动越快,产生电量越大。通常主轴的转速为2800rpm~3500rpm。 现在讲解更复杂的部件。我们怎样控制提升阀轴的运动? 首先,当提升阀轴向下回缩时,让我们描述其液压油流的流动方向。(驱动活塞向上运动时)油从泵下面的腔中直接进入泵里,并通过泵和其出孔进入到活塞缸里。然而回缩活塞时(提升阀向下运动),油顺着中心管向下流入到主阀里。 主阀内部有一个带小孔的活塞,允许一部分油直接流过主阀。流过主阀的油通过中心管向下继续流动,最终流过一个电磁控制阀,然后进入到电磁控制阀下

电子技术综合训练 设计报告 题目:脉冲信号发生器 姓名:xxx 学号:xxxxxxx 班级:xx 电气及其自动化xx 同组成员:xxx 指导教师:xxx 日期:2011年1月4日

脉冲信号发生器的原理主要分为四部分,即正弦波的产生,方波的变换,分频电路和倍频电路,并由这四部分最终产生三种不同频率的信号,其要点在于电路的线路连接及焊接。通过设计体会理论与实际结合的重要性. 关键字:正弦发生多谐振荡器降频电路锁相环

一、设计任务和要求 (5) 1.1设计任务 (5) 1.2设计要求 (5) 二、系统设计 (6) 2.1系统要求 (6) 2.2方案设计 (6) 2.3系统工作原理 (7) 三、单元电路设计 (8) 3.1 RC正弦发生器 (8) 3.1.1电路结构及工作原理 (9) 3.1.2电路仿真 (9) 3.1.3元器件的选择及参数确定 (9) 3.2 555定时器组成的多谐振荡器 (9) 3.2.1电路结构及工作原理 (9) 3.2.2电路仿真 (11) 3.3 74LS161计数器降频电路 (11) 3.3.1电路结构及工作原理 (11)

3.3.2电路仿真 (11) 3.3.3元器件的选择及参数确定 (11) 3.4 锁相环升频电路 (13) 3.4.1电路结构及工作原理 (13) 3.4.2元器件的选择及参数确定 (15) 四、系统仿真 (17) 五、电路安装、调试与测试 (18) 5.1电路安装 (17) 5.2电路调试 (17) 5.3系统功能及性能测试 (17) 5.3.1测试方法设计 (18) 5.3.2测试结果及分析 (18) 结论 (19) 参考文献 (20) 总结、体会和建议 (21) 附录 (22)

如何看懂脉冲电路 2010-06-2215:28:07作者:来源:21IC电子网 脉冲电路是专门用来产生电脉冲和对电脉冲进行放大、变换和整形的电路。家用电器中的定时器、报警器、电子开关、电子钟表、电子玩具以及电子医疗器具等,都要用到脉冲电路。 在电子电路中,电源、放大、振荡和调制电路被称为模拟电子电路,因为它们加工和处理的是连续变化的模拟信号。电子电路中另一大类电路的数字电子电路。它加工和处理的对象是不连续变化的数字信号。数字电子电路又可分成脉冲电路和数字逻辑电路,它们处理的都是不连续的脉冲信号。 电脉冲有各式各样的形状,有矩形、三角形、锯齿形、钟形、阶梯形和尖顶形的,最具有代表性的是矩形脉冲。要说明一个矩形脉冲的特性可以用脉冲幅度Um、脉冲周期T或频率f、脉冲前沿t r、脉冲后沿t f和脉冲宽度t k来表示。如果一个脉冲的宽度t k=1/2T,它就是一个方波。 脉冲电路和放大振荡电路最大的不同点,或者说脉冲电路的特点是:脉冲电路中的晶体管是工作在开关状态的。大多数情况下,晶体管是工作在特性曲线的饱和区或截止区的,所以脉冲电路有时也叫开关电路。从所用的晶体管也可以看出来,在工作频率较高时都采用专用的开关管,如2AK、2CK、DK、3AK 型管,只有在工作频率较低时才使用一般的晶体管。 就拿脉冲电路中最常用的反相器电路(图1)来说,从电路形式上看,它和放大电路中的共发射极电路很相似。在放大电路中,基极电阻R b2是接到正电源上以取得基极偏压;而这个电路中,为了保证电路可靠地截止,R b2是接到一个负电源上的,而且R b1和R b2的数值是按晶体管能可靠地进入饱和区或止区的要求计算出来的。不仅如此,为了使晶体管开关速度更快,在基极上还加有加速电容C,在脉前沿产生正向尖脉冲可使晶体管快速进入导通并饱和;在脉冲后沿产生负向尖脉冲使晶体管快速进入截止状态。除了射极输出器是个特例,脉冲电路中的晶体管都是工作在开关状态的,这是一个特点。

脉冲发生器 要想构成数字钟,首先应选择一个脉冲源——能自动地产生稳定的标准时间脉冲信号。而脉冲源产生的脉冲信号的频率较高,因此,需要进行分频,使高频脉冲信号变成适合于计时的低频脉冲信号,即“秒脉冲信号”(频率为1HZ)。经过分频器输出的秒脉冲信号到计数器中进行计数。将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。“时计数器”采用24进制计时器,可实现对一天24小时的累计。此时需要分别设计60进制,24进制计数器,各计数器输出信号经译码器到数字显示器,使“时”、“分”、“秒”得以数字显示出来。 值得注意的是:任何计时装置都有误差,因此应考虑校准时间电路。校时电路一般采用手动调整。手动调整可利用手动的节拍调准显示时间。 C D4060由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。所有的计数器位均为主从触发器。在CP1(和CP0)的下降沿计数器以二进制进行计数。在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间无限制。 CD4060引角图

CD4060内部方框图 CD4060B典型振荡器连接 上图-RC振荡器下图-晶体振荡器RC振荡器中T=2.2R1C,R2=2*R1~10*R1

脉冲发生器是数字钟的核心部分,它的精度和稳定度决定了数字钟的质量,通常用晶体振荡器发出的脉冲经过整形、分频获得1Hz的秒脉冲。如晶振为32768 Hz,通过15次二分频后可获得1Hz的脉冲输出 CD4060秒脉冲发生器电路

脉冲波形发生电路设计一.实验目的 1.学习脉冲波形发生电路的设计方法和调试方法。 2.学习按模块划分电路的设计与调试的方法。二.555内部结构图和芯片引脚图 555内部结构图: 555引脚图:

三.红外发射管和光电三极管的工作原理 1.红外发射管: 红外光发射管具有单向导电性。只有当外加的正向电压使得正向电流足够大时才发射红外光,正向电流越大发光越强,其工作原理图参见图2(a)。此次实验中的R1 建议选取1k?。 2.光电三极管: 光电三极管依据光照强度来控制集电极电流的大小,其功能可等效为一只二极管与一只晶体管相连,并仅引出集电极和发射极,如图3(a)所示。其符号如图3(b)所示,常见外形如图3(c)所示。 有光照射时,光电三极管的集电极电流约在几十微安到几毫安之间,为保证光电三极管的输出电压Vo 可以正确驱动后面的数字IC,合理选取接收电路中R2 的阻值。其应用参考电路参见图2(b)。

四.实验任务及电路图 1.电路原理图 VCC VCC 2.设计思路 首先将555接成单稳态触发器,输出接发光二极管。 然后考虑输入。为了能在物体挡住光超过2秒以上电路仍然能够正常

运行,在输入端接入一个微分电路,保证输入脉宽不超过2秒。 同时因为前方光电三极管的输出电压在有光时为低电平,无光时为高电平,而电路要实现的功能是遮挡时发光二极管,所以在无光时应输入低电平,所以在光电三极管的输出与后方的输入间加了一个反相器。 最后考虑选作任务,首先要让发光三极管在被挡住时,LED一直亮,这个只需去掉微分电路就可以了。但是这样在光线重新照射时LED会马上灭掉,这是因为在遮挡时,555中的三极管是不导通的,所以C2两端是有压差的,即(见555内部结构图),这样在光线重新照射时,输入会跳为高电平,所以=1,Q=0,=0,内部三极管导通,=1,保持0,所以LED就会灭掉。而且是我们不希望出现的情况,因为上述分析是基于门电路的均较长的情况下分析的,实际上这些跳变都是瞬间完成的,所以之后电路的情况并不是能准确预测的。 解决这个问题的思路就是希望能在时,保持1,这样跳变为1之后就有,LED保持亮着,而且经过1~2秒后熄灭。 实现这个功能只需在那一个三极管的c、e端与C2并联,b端接输入即可。 为了在输入为低时三极管导通,选用PNP三极管。 3.参数计算 (1)R2阻值的选取: 为保证在有光时vo输出的是低电平,则R2上的压降应接近5V,以10微安计算,则R2应取100 k?左右。 (2)R3和C3的选取

1实验目的 1.学习脉冲波形发生电路的设计方法和调试方法。 2.学习按模块划分电路的设计方法和调试方法。 2电路设计 图1:电路设计 2.1输入电路 电路图的最左侧是输入电路,R1=56kΩ,是预习时按照100μA选取的,经过实验验证可以正常工作。输出端有一个施密特反相器,是为了给波形整形,因为光电三极管的输出是模拟量,往往会有噪声,施密特反相器就能使得波形变为陡峭的方波,提高电路的稳定性。 2.2微分电路 输入电路的右侧是微分电路,作用是从输入电路端取边沿,输出尖峰脉冲,以触发后一级的单稳态电路。稳态时,若突然有物体遮挡光电三极管,电容左端由高电平跳变到低电平,但是电容两端的电压不能突变,所以右端的电压也会跳变成低电平,形成负的尖峰脉冲,此后很快电容就会充电回到高电平。如果没有微分电路,若物体一直遮挡着光电三极管,555定时器接成的单稳态电路就会一直处于暂稳态,这是不符合要求的。

2.3单稳态电路 单稳态电路在电路的最右侧,由555定时器接成。稳态时,输入端TRI处于高电平,输出OUT、DIS都是低电平,且C3上无电荷。触发时,TRI端收到一个负的尖峰脉冲,输 V CC时放电,且输出端回到出端OUT瞬间变为高电平,LED灯亮,同时C3充电,至2 3 低电平,回到稳态。 2.4放电电路 选做任务中要求电路能重复触发,就需要在触发时给C3放电,从而能重新计时。由于实验箱中只有NPN型三极管,故需要将触发信号经过施密特反相器后再连接到三极管基极,这样还能对信号进行整形,提高质量。当触发信号来临时,三极管就会导通,C3迅速放电。 2.5计数电路 利用74HC161改接成的十进制计数器进行计数,计数信号经过施密特反相器后,再次反相,作为时钟信号。为了完成选做任务,还需将555定时器的输出端连到74HC161的异步置零端,以实现所有物体经过后计数置零的目的。 3波形分析 3.1输入电路波形 遮挡红外发射管若干次,可以得到如图2的波形。可以看出黄色的光电三极管的输出波形虽然都是正脉冲,但是波形很不理想,毛刺较多;经过施密特反相后的绿色波形则十分规整,毛刺很少,基本上都是方波了,适合作为后一级的输入。 图2:输入电路波形

1.秒信号的发生电路 秒信号发生电路由集成电路555定时器与RC组成的多谐振荡器构成。需要的芯片有集成电路555定时器,还有电阻和电容。下图为其电路图: 图 3-1 秒信号发生电路 振荡电路是数字钟的核心部分,它的频率和稳定性直接关系到表的精度。因此选择555定时器构成的多谐振荡器,其中电容C1为47微法,C2为0.01微法,两个电阻R1=R2=10K欧姆。此时在电路的输出端就得到了一个周期性的矩形波,其振荡频率为: f=1.43/[(R1+2R2)C] (3-1)由公式(3-1)代入R1 ,R2和C的值得,f=1Hz。即其输出频率为1Hz的矩形波信号 2. 用555制作秒脉冲

输出频率为1Hz,占空比为50%. 由于CD4060在MULTISIM中仿真不了,所以本设计采用三片74HC161和一片74HC160IC级联,构成2^15分频器。单元电路连接如下图所示: 3、基于NE555的秒方波发生器的设计 用NE555芯片以及外围电路搭建成一个多谐振荡器,通过设计外围电路的参数输出方波频率为1Hz,故称为秒方波发生器。由于脉冲的占空比对系统的影响不大,故把占空比设计为1/3。输出方波用作计数器及D触发器的clk信号。NE555定时器引脚图如图1所示,脉冲频率公式: f=1/(R1+2R2)C㏑2 选择R1=47K,R2=47K,RV1=2K,C=10μF,形成电路图如图2所示:

图6 2kΩ Key=A 图7秒脉冲发生器 2.1振荡器电路 2.1.1 用555作振荡器 采用集成电路555定时器与RC 组成的多谐振荡器。输出的脉冲频率为 =2)2+(1=121In C R R f 1KHz ,周期T =1=f S 1ms 。取电阻为千欧级,电 容0.01uF 到0.1uF 。若参数选择:R 1=R 2=10k 欧姆,C 1=47uF 时,可以得到秒脉冲信号。虽然直接得到了秒脉冲,但从计时精度的角度考虑,振荡器的振荡频率越高,钟表计时的精度就越高,所以一般不直接输出秒脉冲信号。

1.PWM 信号概述 脉冲宽度调制(PWM )信号广泛使用在电力变流技术中,以其作为控制信号可完成DC-DC变换(开关电源)、DC-AC变换(逆变电源)、AC-AC变换(斩控调压)和AC-DC 变换(功率因数校正)。 产生PWM 信号的方法有多种,现分别论述如下: 1)普通电子元件构成PWM 发生器电路基本原理是由三角波或锯齿波发生器产生高频调制波,经比较器产生PWM 信号。三角波或锯齿波与可调直流电压比较,产生可调占空比PWM 信号;与正弦基波比较,产生占空比按正弦规律变化的SPWM 信号。 此方法优点是成本低、各环节波形和电压值可观测、易于扩展应用电路等。缺点是电路集成度低,不利于产品化。 2)单片机自动生成PWM 信号 基本原理是由单片机内部集成PWM 发生器模块在程序控制下产生PWM 信号。 优点是电路简单、便于程序控制。缺点是不利于学生观测PWM 产生过程,闭环控制复杂和使用时受单片机性能制约。 3)可编程逻辑器件编程产生PWM 信号基本原理是以复杂可编程逻辑器件(CPLD )或现场可编程门阵列器件 (FPGA)为硬件基础,设计专用程序产生PWM信号。 优点是电路简单、PWM 频率和占空比定量准确。缺点是闭环控制复杂,产生SPWM 信号难度大。 4)专用芯片产生PWM 信号 是生产厂家设计、生产的特定功能芯片。优点是使用方便、安全,便于应用到产品设计中。缺点是不利于学生观测 PWM 产生过程和灵活调节各项参数。 2. 电子元件构成PWM发生器电路

图1电子元件构成PWM 发生器电路 3. 集成芯片SG3525构成PWI 发生器电路 、PWM 信号发生电路说明 实验电路中,驱动开关管的 PWM 信号由专用PWM 控制集成芯片SG3525 产生(美国Silicon General 公司生产),PWM 信号发生器电路如图 图2 PWM 信号发生器电路图 SG3525采用恒频脉宽调制控制方案,内部包含有精密基准源、锯齿波振荡 器、误差放大器、比较器、分频器和保护电路等。调节 Ur 的大小,在OUTA 、 2所示。 I l 22K Rw Ur 10K R2K R5 -CZI 10K J' R2 10 R1 =±C1 15K 0.01uF VREF VCC OSC OUT VC SYNC RT D ISC OUT A CT OUT B CMPEN IN+ IN - SS GND SD +15V 15 T + 15 T HF R6 10K V_G Dz R9 30K Dz PWM 13 12 10 ----- S G3525AN 8 4148 11 14 16 4 3 6' 7 5 9 "2 1 光电隔离 上C2 T~ 100uF

精密秒脉冲发生器电路 第一种:使用价格低廉的32768HZ 晶体,配上HC4060 电路,自身工作电压 2 -6V,静态电流仅仅20 uA 左右。没有任何分频和其他多余器件,如果集成电路采用贴片封装,体积将非常小。本身具有天然的 秒闪烁脉冲信号。 也可以配套CD4060 电路,但是电压范围为 3 -18V,静态电流随电压提高而上升,在+5V 供电时,静态电流约0.25 -5uA,主要考虑的是在 3.0V 电池供电时的停振问题。而HC4060 电路工作电压可以低一些。(本电路还可以输出其他标准频率的参考信号,印刷板上预留了 5 种频率输出信号的焊盘)。 主要参数:供电:DC5V. 月误差:≤ 15S。提示:输出应该外加高输入阻抗的缓冲级。 第二种:是曾经大名鼎鼎的高频高精度晶体振荡电路,也叫“高频石英钟电路”,由于原来是驱动步进电机的,所以其输出间隔是2*0.5HZ/S,我们仅仅使用单边电路,可以得到30 个脉冲/S。其供电电压仅仅 1.5 V,神奇的低!工作电流不到1uA,输出电压也很低,因此,使用分立的PNP 三极管把电平提高到任意值。需要注意:1.5V 电源的正端子,应该就是+5V 电源的正端子。 市场上已经较难购买到5512F 电路了。 上面的电路无需太多调整,本身就有非常准确的精度。如果与单片机配套,单片机需要干的事情仅仅就是计数而已。对5512F 电路,单片机还需要生成一个秒脉冲输出信号。(0.5S 的高低交替电平输出)。 主要参数:供电:DC5V. 月误差:≤ 6S。提示:输出应该外加高输入阻抗的缓冲级。

计数译码显示在现代科学技术中应用非常广泛,它由计数器、译 码器和显示器三部分组成,包含数字电子系统的组合逻辑电路和时序 逻辑电路,因此本实验是一个综合性的实验。次实验的目的是: 掌握中规模集成计数器74LS90的功能和使用方法; 学习使用74LS48BCD码译码器和共阴极数码管显示器; 掌握计数、译码、显示电路综合应用方法; 学会用规模集成计数器74LS90等芯片设计任意进制计 数器的方法。 熟悉用Multisim仿真数字电路的方法。 实验仪器与元件 数字逻辑实验箱; 示波器; 74LS90 二——五——十进制计数器; 74LS48BCD码七段译码驱动器; 七段共阴极数码管; 仿真实验PC机; 其他可选芯片:74LS161,74LS00,74LS20。 实验器件及原理 它是一种中规模集成电路,种类很多,不但可以实现计数、分频, 而且可以实现测量、运算、定时、延时等控制功能。目前各类计数器均有典型产品,如属于二进制计数器的74LS161、74LS163……,属于十进制计数器的74LS90、74LS160等。 本实验采用的是74LS90二—五—十进制异步计数器。74LS90的内部结构是一个二分频和五分频电路,可以独立地作为二进制和五进制计数器使用,同时进行适当的连接又可以构成十进制计数器。

超短脉冲激光烧蚀技术应用探究 近年来随着超短脉冲激光烧蚀技术的发展,该技术被广泛应用于工业领域。短脉冲激光与物质相互作用时间介于纳秒与飞秒之间,其峰值功率可达兆瓦级,因此在加工中可应用于高精度、高硬材料的精细加工上,同时也可以实现材料的三维加工,该方式称为“冷”加工。文章旨在介绍超短脉冲技术的应用研究,使人们对该技术有一定的宏观认识。 标签:超短脉冲;激光烧蚀;应用探究;宏观认识 1 短脉冲激光器与金属相互作用理论 短脉冲诱导烧蚀材料的过程的建立需要一定的时间,并且与激光强度有直接关系。当脉宽给定时,只有当激光场的强度超过一定值时,形成的等离子体才能发生不可逆的损伤阈值,该阈值范围通常以激光的能流阈值表示。根据文献指出,脉冲宽度从连续到几十个皮秒范围内,烧蚀过程为离子雪崩过程,开始于内部电子。通过对超短脉宽烧蚀阈值的研究发现,当偏离了脉冲宽度平方根法则的时候,能量在很大范围内变动均可引起材料的烧蚀,如图1所示为超短脉冲激与金属作用的过程。 当前人们于超短脉冲激光烧蚀物质的机理和研究还没有获得完全的认知,研究的模型是将物质看做一个总体的系统去考虑,只有达到了该物质的沸点或熔点时,使得物质蒸发或者熔化而使材料被去除。应用傅里叶传热模型对上述过程可进行具体的描述,但是他不适用于描述和分析超短脉冲激光与金属薄膜或者介质膜的作用过程。原因是由于载流子的特征尺寸与膜层的厚度相当,同时其特征时间与传输能量的时间接近。 当超短脉冲激光与金属材料作用发生激光烧蚀时,材料的表面的电子吸收激光的能量后变为非平衡状态,发生了相互制约的现象。造成电子爆炸运动速度接近于费米速率。同时热电子通过碰撞作用使得内部电子获得加热,之后参与碰撞的电子达到短暂的呈费米分布的热平衡态。电子与晶格通过碰撞耦合效应,使得电子温度降低和晶格温度升高,最终电子温度与材料的晶格温度达到平衡。 2 短脉冲激光烧蚀研究方法 激光烧蚀的研究方法包括:实验方法测定,理论计算分析和数值模拟。实验方法能够准确的对后两种方法进行检验。但实验方法需要的成本巨大。理论计算分析和数值模拟方法是一种对于研究激光烧蚀问题的非常有的方法,其理论分析过程非常严谨,但是也存在一定的边界条件限制,需要进行相应的假设,处理问题的范围有限。但其可低成本、高精度模拟短脉冲烧蚀机理内的复杂问题,一直是各大科研院校应用的最广泛的方法。若条件允许会采用实验方法进行验证,不断修正算法达到近乎理想的模拟及精密数值计算水平。

沈阳航空航天大学 课程设计 (说明书) 脉冲分频信号产生器设计 班级24020103 学号2012040201131 学生姓名郁健 指导教师关庆阳

沈阳航空航天大学 课程设计任务书 课程名称电子技术综合课程设计____ 课程设计题目脉冲分频信号产生器 课程设计的内容及要求: 一、设计说明与技术指标 设计一个脉冲分频信号产生器,技术指标如下: ①能够输出1KHz脉冲信号; ②能够输出10KHz脉冲信号; ③能够输出100Hz脉冲信号; 二、设计要求 1.在选择器件时,应考虑成本。 2.根据技术指标,通过分析计算确定电路和元器件参数。 3.画出电路原理图(元器件标准化,电路图规范化)。 三、实验要求 1.根据技术指标制定实验方案;验证所设计的电路,用软件仿真。 2.进行实验数据处理和分析。 四、推荐参考资料 1. 童诗白,华成英主编.模拟电子技术基础.[M]北京:高等教育出版社,2006年 五、按照要求撰写课程设计报告

成绩评定表: 序号评定项目评分成绩 1 设计方案正确,具有可行性,创新性(15分) 2 设计结果可信(例如:系统分析、仿真结果)(15分) 3 态度认真,遵守纪律(15分) 4 设计报告的规范化、参考文献充分(不少于5篇)(25分) 5 答辩(30分) 总分 最终评定成绩(以优、良、中、及格、不及格评定) 指导教师签字: 2015 年01 月14日

一、概述 该脉冲分频信号产生器可以实现10KHZ 、1KHZ 、100HZ 三路频率输出,电路结构相对简单,输出频率相对稳定,且能够有效的实现频率间的转变,具有节能,经济,功能具备的特点。 二、方案论证 设计一个脉冲分频信号产生器,技术指标如下: ①能够输出1KHz 脉冲信号; ②能够输出10KHz 脉冲信号; ③能够输出100Hz 脉冲信号; 方案一: 方案一原理框图如图1所示。 降频 降频 图1 方案一脉冲分频电路的原理框图 方案二: 方案二原理框图如图2所示。 升频 降频 图2 方案二脉冲分频电路的原理框图 由555定时器组成的多谐振荡器产生频率为10KHZ 的脉冲信号 由74LS160组成的十分频电 路 由74LS160组成的十分频电路 输出 1KHZ 输出 100HZ 输出 10KHZ 由555定时器组成的多谐振 荡器产生频率 为1KHZ 的脉冲信号 锁相环升频 74LS160降频 输出10KHZ 输出100HZ 输出1KHZ