一种高速高增益CMOS运算放大器的设计

匡志伟;唐宁;金剑;任李悦

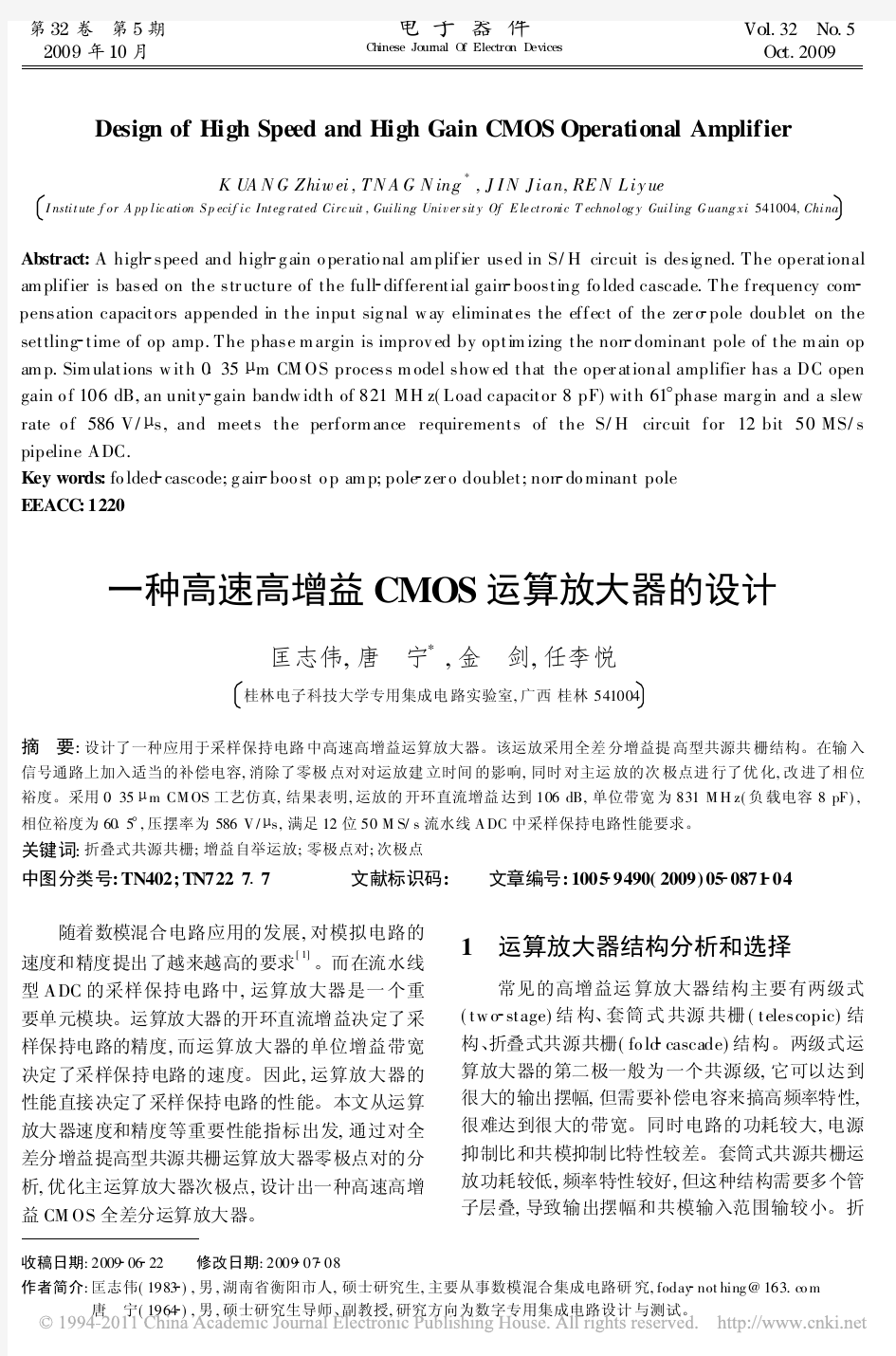

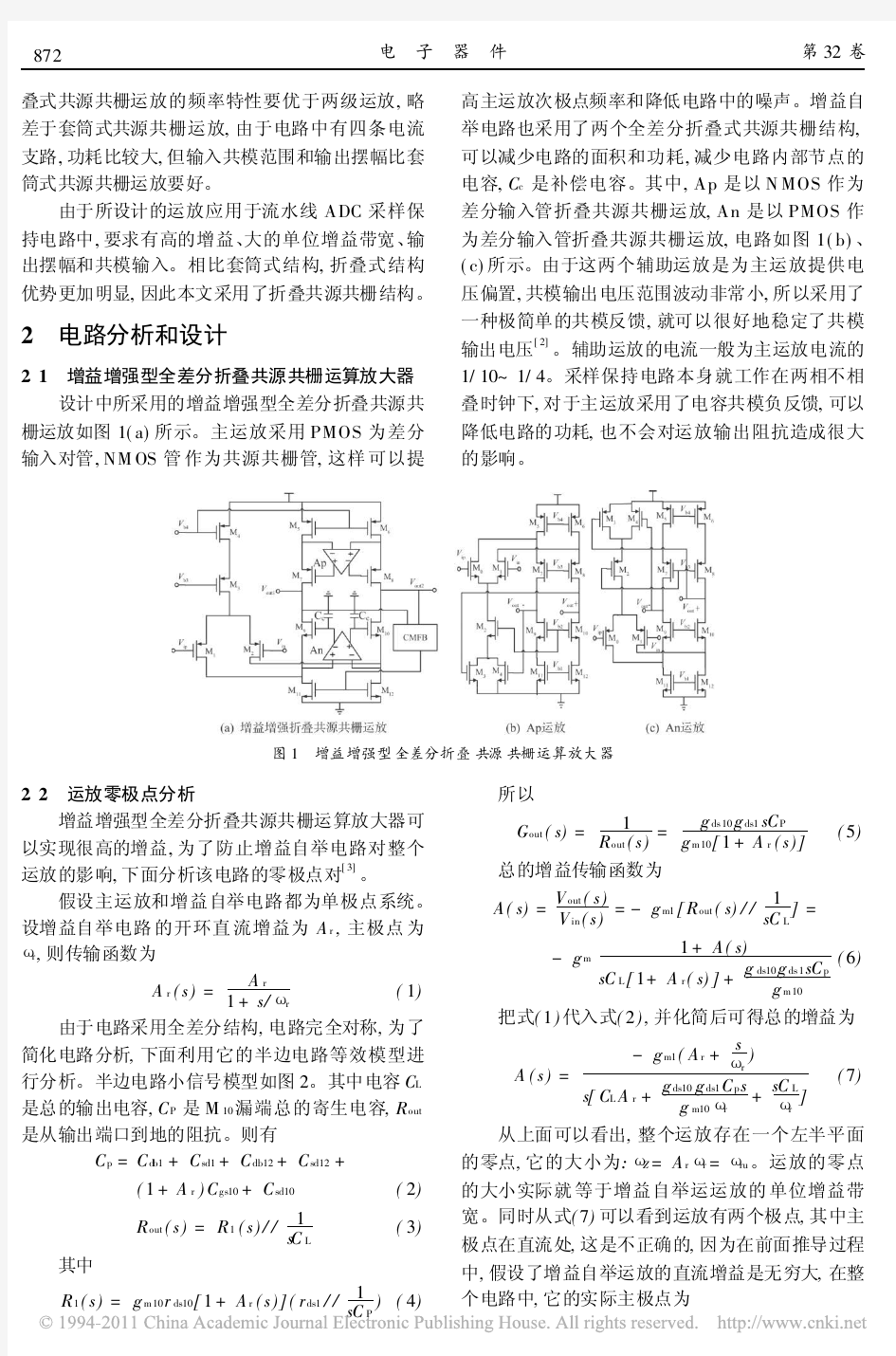

【摘要】设计了一种应用于采样保持电路中高速高增益运算放大器.该运放采用全差分增益提高型共源共栅结构.在输入信号通路上加入适当的补偿电容,消除了零极点对对运放建立时间的影响,同时对主运放的次极点进行了优化,改进了相位裕度.采用0.35 μm CMOS工艺仿真,结果表明,运放的开环直流增益达到106 dB,单位带宽为831 MHz(负载电容8 pF),相位裕度为60.5°,压摆率为586 V/μs,满足12位50 MS/s流水线ADC中采样保持电路性能要求.

【期刊名称】《电子器件》

【年(卷),期】2009(032)005

【总页数】4页(P871-874)

【关键词】折叠式共源共栅;增益自举运放;零极点对;次极点

【作者】匡志伟;唐宁;金剑;任李悦

【作者单位】桂林电子科技大学专用集成电路实验室,广西,桂林,541004;桂林电子科技大学专用集成电路实验室,广西,桂林,541004;桂林电子科技大学专用集成电路实验室,广西,桂林,541004;桂林电子科技大学专用集成电路实验室,广西,桂

林,541004

【正文语种】中文

【中图分类】工业技术