阻抗匹配

一、阻抗

阻抗就是电阻、电容抗及电感抗在向量上的和。在直流电路中,物体对电流阻碍的作用叫做电阻。在交流电路中,除了电阻会阻碍电流以外,电容及电感也会阻碍电流的流动,这种作用就称之为电抗。电容及电感的电抗分别称作电容抗及电感抗,简称容抗及感抗。它们的计量单位与电阻一样,而其值的大小则和交流电的频率有关系,频率愈高则容抗愈小感抗愈大,频率愈低则容抗愈大而感抗愈小。此外电容抗和电感抗还有相位角度的问题,具有向量上的关系式,因此:阻抗是电阻与电抗在向量上的和。写成数学公式:阻抗Z= R+j ( X L– X C) 。其中R为电阻,X L为感抗,X C为容抗。如果( X L– X C) > 0,称为“感性负载”;反之,如果( X L – X C) < 0称为“容性负载”。对于一个具体电路,阻抗随着频率变化而变化。

二、输入阻抗

输入阻抗是指电路输入端的等效阻抗,即电路相对于信号源来说的阻抗。

在输入端上加上一个电压源U,测量输入端的电流I,则输入阻抗R就是U/I。相当于一个电阻的两端,这个电阻的阻值就是输入阻抗,它反映了对电流阻碍作用的大小。对于电压驱动的电路,输入阻抗越大,则对电压源的负载就越轻,因而就越容易驱动,也不会对信号源有影响;而对于电流驱动型的电路,输入阻抗越小,则对电流源的负载就越轻。因此,可以这样认为:如果是用电压源来驱动的,则输入阻抗越大越好;如果是用电流源来驱动的,则阻抗越小越好(只适合于低频电路,在高频电路中,还要考虑阻抗匹配问题;另外如果要获取最大输出功率时,也要考虑阻抗匹配问题)。

三、输出阻抗

输出阻抗是指信号源的内阻,即电路相对于负载来说的阻抗。

输出阻抗的大小视不同的电路有不同的要求,电压源输出阻抗要低,电流源的输出阻抗要高。对于放大电路来讲,输出阻抗的值表示其承担负载的能力,通常输出阻抗小,承担负载的能力就强。

四、反射

信号沿传输线传播时,其路径上的每一步都有相应的瞬态阻抗,无论是什么原因使瞬态阻抗发生了变化,信号都将产生反射现象,瞬态阻抗变化越大,反射越大,此时信号功率没有全部传输到负载处。

在高速的PCB中导线必须等效为传输线,按照传输线理论,如果源端与负载端具有相同的阻抗,反射就不会发生了。如果二者阻抗不匹配就会引起反射,负载会将一部分电压反射回源端。根据负载阻抗和源阻抗的关系大小不同,反射电压可能为正,也可能为负。如果反射信号很强,叠加在原信号上,很可能改变逻辑状态,导致接收数据错误。如果在时钟信号上可能引起时钟沿不单调,进而引起误触发。

五、阻抗匹配

阻抗匹配指信号源内阻跟负载阻抗之间的特定配合关系。在能量传输时要求阻抗匹配,即负载阻抗要和传输线的特征阻抗相等。此时的传输不会产生反射,这表明所有能量都被负载吸收了。反之,当电路阻抗失配时,得不到最大的传输功率,还可能对电路产生损害。在高速PCB设计中,阻抗的匹配与否关系到信号的质量优劣。它反映了输入电路与输出电路之间的功率传输关系。当电路实现阻抗匹配时,将获得最大的功率传输。

阻抗匹配的基本原理

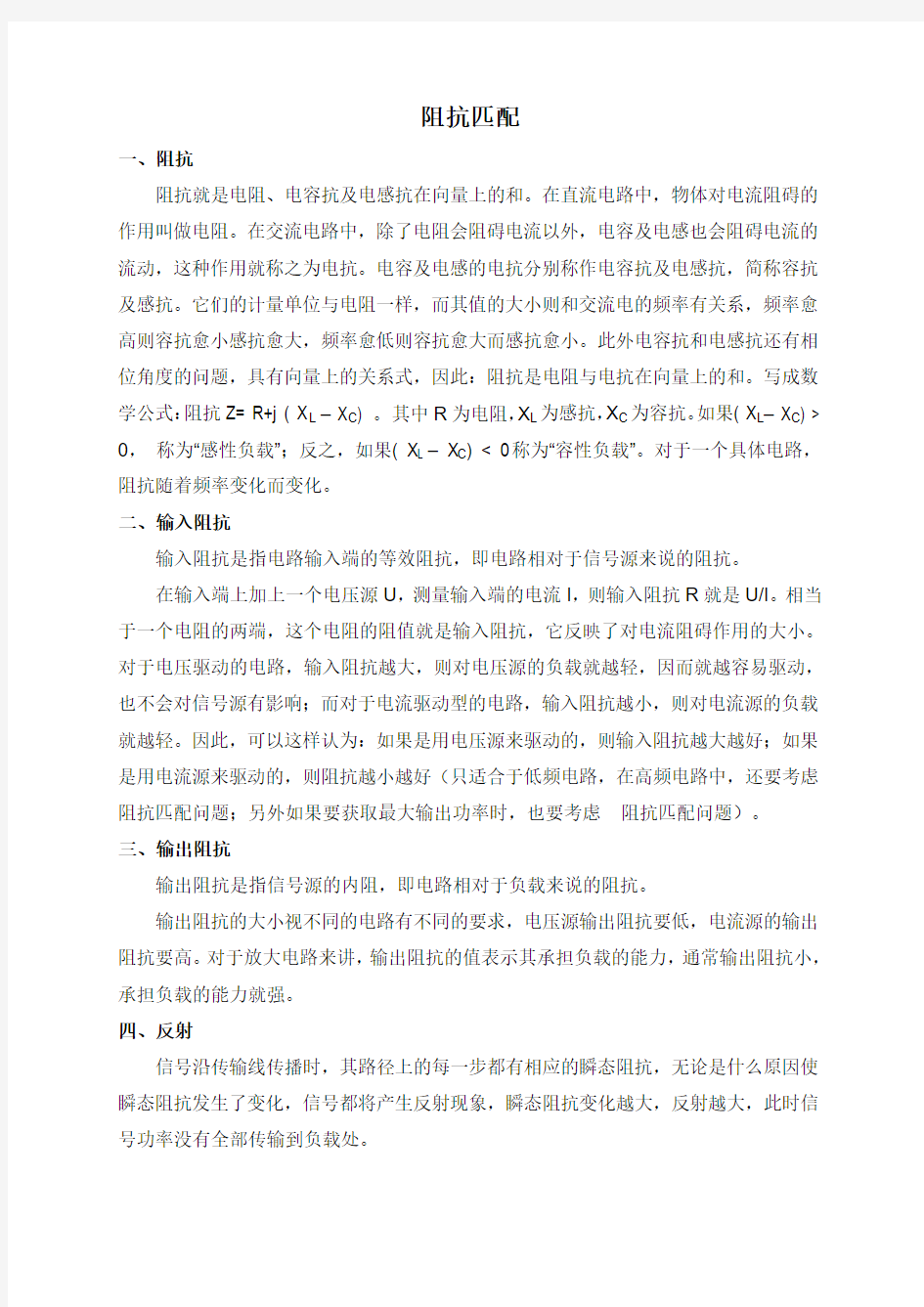

右图中R为负载电阻,r为电源E的内阻,E为电压源。由于r的存在,当R很大时,电路接近开路状态;而当R很少时接近短路状态。显然负载在开路及短路状态都不能获得最大功率。

根据式:

从上式可看出,当R=r时式中的式中分母中的(R-r)的值最小为0,此时负载所获取的功率最大。所以,当负载电阻等于电源内阻时,负载将获得最大功率。这就是电子电路阻抗匹配的基本原理。

阻抗匹配是指负载阻抗与激励源内部阻抗交互相适配,得到最大功率输出的一种工作状态。对于不同特性的电路,匹配条件是不一样的。

一、在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。

二、激励源内阻抗和负载阻抗含有电抗成份时,为使负载得到最大功率,负载阻抗与内阻必须满足共轭关系,即电阻成份相等,电抗成份只数值相等而符号相反,这种匹

配条件称为共轭匹配:

①负载阻抗等于信源内阻抗,即它们的模与辐角分别相等,这时在负载阻抗上可以得到无失真的电压传输。

②负载阻抗等于信源内阻抗的共轭值,即它们的模相等而辐角之和为零。这时在负载阻抗上可以得到最大功率。这种匹配条件称为共轭匹配。

如果信源内阻抗和负载阻抗均为纯阻性,则两种匹配条件是等同的。

阻抗匹配有两种:

一、透过改变阻抗力

把电容或电感与负载串联起来,即可增加或减少负载的阻抗值。在史密斯图表上的点会沿著代表实数电阻的圆圈走动。如果把电容或电感接地,首先图表上的点会以图中心旋转180度,然后才沿电阻圈走动,再沿中心旋转180度。重复以上方法直至电阻值变成1,即可直接把阻抗力变为零完成匹配。

二、调整传输线的波长

由负载点至源点加长传输线,在图表上的圆点会沿著图中心以逆时针方向走动,直至走到电阻值为1的圆圈上,即可加电容或电感把阻抗力调整为零,完成匹配。

阻抗匹配则传输功率大,对于一个电源来讲,当它的内阻等于负载时,输出功率最大,此时阻抗匹配。最大功率传输定理,如果是高频的话,就是无反射波。对于普通的宽频放大器,输出阻抗50Ω,功率传输电路中需要考虑阻抗匹配,可是如果信号波长远远大于电缆长度,即缆长可以忽略的话,就无须考虑阻抗匹配了。高速PCB布线时,为了防止信号的反射,要求是线路的阻抗为50欧姆。这是个大约的数字,一般为了匹配方便,规定同轴电缆基带50欧姆,频带75欧姆,对绞线则为100欧姆。

常见阻抗匹配的方式

串联终端匹配

在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

匹配电阻选择原则:匹配电阻值与驱动器的输出阻抗之和等于传输线的特征阻抗。常见的CMOS和TTL驱动器,其输出阻抗会随信号的电平大小变化而变化。因此,对TTL或CMOS电路来说,不可能有十分正确的匹配电阻,只能折中考虑。链状拓扑结

构的信号网路不适合使用串联终端匹配,所有的负载必须接到传输线的末端。

串联匹配是最常用的终端匹配方法。它的优点是功耗小,不会给驱动器带来额外的直流负载,也不会在信号和地之间引入额外的阻抗,而且只需要一个电阻元件。

常见应用:一般的CMOS、TTL电路的阻抗匹配。USB信号也采样这种方法做阻抗匹配。

(注:源端匹配并非真的消除了接收端的反射,而是恰好利用了这个反射。实际在传输线上信号强度只有一半,加上到接收端是产生反射系数为1的反射,从而接收端看到的信号幅度等于源端的信号幅度)

并联终端匹配

在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。实现形式分为单电阻和双电阻两种形式。

匹配电阻选择原则:在芯片的输入阻抗很高的情况下,对单电阻形式来说,负载端的并联电阻值必须与传输线的特征阻抗相近或相等;对双电阻形式来说,每个并联电阻值为传输线特征阻抗的两倍。(注:这两个阻抗并联正好等于传输线特征阻抗)并联终端匹配优点是简单易行,显而易见的缺点是会带来直流功耗:单电阻方式的直流功耗与信号的占空比紧密相关;双电阻方式则无论信号是高电平还是低电平都有直流功耗,但电流比单电阻方式少一半。

常见应用:以高速信号应用较多。

(1)DDR、DDR2等SSTL驱动器。采用单电阻形式,并联到VTT(一般为IOVDD 的一半)。其中DDR2数据信号的并联匹配电阻是内置在芯片中的。

(2)TMDS等高速串行数据接口。采用单电阻形式,在接收设备端并联到IOVDD,单端阻抗为50欧姆(差分对间为100欧姆)。

阻抗匹配基本認識 阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式得到最大功率输出的一种工作状态。对于不同特性的电路,匹配条件是不一样的。阻抗匹配分为低频和高频两种情况讨论。我们先从直流电压源驱动一个负载入手。由于实际的电压源,总是有内阻的(请参看输出阻抗一问),我们可以把一个实际电压源,等效成一个理想的电压源跟一个电阻r串联的模型。假设负载电阻为R,电源电动势为U,内阻为r,那么我们可以计算出流过电阻R的电流为:I=U/(R+r),可以看出,负载电阻R越小,则输出电流越大。负载R上的电压为:Uo=IR=U×[1+(r/R)],可以看出,负载电阻R越大,则输出电压Uo越高。再来计算一下电阻R消耗的功率为: P=I2×R=(U/(R+r))2×R=U2×R/(R2+2×R×r+r2) =U2×R/((R-r)2+4×R×r) =U2/(((R-r)2/R)+4×r) 对于一个给定的信号源,其内阻r是固定的,而负载电阻R则 是由我们来选择的。注意式中((R-r)2/R),当R=r时,(R-r)2/R可 取得最小值0,这时负载电阻R上可获得最大输出功率 Pmax=U2/(4×r)。即,当负载电阻跟信号源内阻相等时,负载可 获得最大输出功率,这就是我们常说的阻抗匹配之一。 对于纯电阻电路,此结论同样适用于低频电路及高频电路。 当交流电路中含有容性或感性阻抗时,结论有所改变,就是需 要信号源与负载阻抗的的实部相等,虚部互为相反数,这叫做共厄匹配。 Z=R+jX ﹐Z=R-jX 在低频电路中,我们一般不考虑传输线的匹配问题,只考虑信号源跟负载之间的情况,因为低频信号的波长相对于传输线来说很长,传输线可以看成是“短线”,反射可以不考虑(可以这么理解:因为线短,即使反射回来,跟原信号还是一样的)。从以上分析我们可以得出结论:如果我们需要输出电流大,则选择小的负载R;如果我们需要输出电压大,则选择大的负载R;如果我们需要输出功率最大,则选择跟信号源内阻匹配的电阻R。 有时阻抗不匹配还有另外一层意思,例如一些仪器输出端是在特定的负载条件下设计的,如果负载条件改变了,则可能达不到原来的性能,这时我们也会叫做阻抗失配。 在高频电路中,我们还必须考虑反射的问题。当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号叠加在原信号上将会改变原信号的形状。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射。为什么阻抗不匹配时会产生反射以及特征阻抗的求解方法,牵涉到二阶偏微分方程的求解,在这里我们不细说了,有兴趣的可参看电磁场与微波方面书籍中的传输线理论。 传输线的特征阻抗(也叫做特性阻抗)是由传输线的结构以及材料决定的,而与传输线的长度,以及信号的幅度、频率等均无关。 例如,常用的闭路电视同轴电缆特性阻抗为75Ω,而一些射频设备上则常用特征阻抗为50Ω的同轴电缆。另外还有一种常见的传输线是特性阻抗为300Ω的扁平平行线,这在农村使用的电视天线架上比较常见,用来做八木天线的馈线。因为电视机的射频输入端输入阻抗为75Ω,所以

阻抗匹配与史密斯(Smith)圆图:基本原理

在处理 RF 系统的实际应用问题时,总会遇到一些非常困难的工作,对各部分级联电路的不同阻抗进行匹配就是其中之一。一般情况下, 需要进行匹配的电路包括天线与低噪声放大器(LNA)之间的匹配、 功率放大器输出(RFOUT)与天线之间的匹配、 LNA/VCO 输出与混频器输入 之间的匹配。匹配的目的是为了保证信号或能量有效地从“信号源”传送到“负载”。

在高频端,寄生元件(比如连线上的电感、板层之间的电容和导体的电阻)对匹配网络具有明显的、不可预知的影响。频率在数十兆赫兹 以上时,理论计算和仿真已经远远不能满足要求,为了得到适当的最终结果,还必须考虑在实验室中进行的 RF 测试、并进行适当调谐。 需要用计算值确定电路的结构类型和相应的目标元件值。

有很多种阻抗匹配的方法,包括

?

计算机仿真: 由于这类软件是为不同功能设计的而不只是用于阻抗匹配,所以使用起来比较复杂。设计者必须熟悉用正确的 格式输入众多的数据。设计人员还需要具有从大量的输出结果中找到有用数据的技能。另外,除非计算机是专门为这个用途 制造的,否则电路仿真软件不可能预装在计算机上。

? ? ?

手工计算: 这是一种极其繁琐的方法,因为需要用到较长(“几公里”)的计算公式、并且被处理的数据多为复数。 经验: 只有在 RF 领域工作过多年的人才能使用这种方法。总之,它只适合于资深的专家。 史密斯圆图:本文要重点讨论的内容。

本文的主要目的是复习史密斯圆图的结构和背景知识,并且总结它在实际中的应用方法。讨论的主题包括参数的实际范例,比如找出匹 配网络元件的数值。当然,史密斯圆图不仅能够为我们找出最大功率传输的匹配网络,还能帮助设计者优化噪声系数,确定品质因数的 影响以及进行稳定性分析。

图 1. 阻抗和史密斯圆图基础

基础知识

在介绍史密斯圆图的使用之前,最好回顾一下 RF 环境下(大于 100MHz) IC 连线的电磁波传播现象。这对 RS-485 传输线、PA 和天线之间 的连接、LNA 和下变频器/混频器之间的连接等应用都是有效的。

辽宁大学学报 自然科学版 第28卷 第3期 2001年 JOURNAL OF LIAONING UNIV ERSITY Natural Sciences Edition V ol.28 N o.3 2001 关于阻抗匹配问题的分析 郭继红Ξ (辽宁大学信息科学与技术学院,辽宁沈阳110036) 摘 要:就输入电路与输出电路之间的功率传输关系而言,当电路实现阻抗匹配时,电路 将获得最大的输出功率,实现理想的效果. 关键词:阻抗;纯电阻;阻抗匹配. 中图分类号:T N911 文献标识码:A 文章编号:100025846(2001)0320257203 阻抗匹配是无线电技术中常用的一种工作状态,它反映了输入电路与输出电路之间的功率传输关系.当电路实现阻抗匹配时,将获得最大的功率传输.反之,当电路阻抗失配时,不但得不到最大的功率传输,还可能对电路产生损害. 阻抗匹配常见于各级放大电路之间、放大器与负载之间、测量仪器与被测量电路之间、天线与接收机或发射机与天线之间,等等.例如,扩音机的输出电路与扬声器之间必须做到阻抗匹配,不匹配时,扩音机的输出功率将不能全部送至扬声器.如果扬声器的阻抗远小于扩音机的输出阻抗,扩音机就处于过载状态,其末级功率放大管很容易损坏.反之,如果扬声器的阻抗高于扩音机的输出阻抗过多,会引起输出电压升高,同样不利于扩音机的工作,声音还会产生失真.因此扩音机电路的输出阻抗与扬声器的阻抗越接近越好.又如,无线电发射机的输出阻抗与馈线的阻抗、馈线与天线的阻抗也应达到一致.如果阻抗值不一致,发射机输出的高频能量将不能全部由天线发射出去.这部分没有发射出去的能量会反射回来,产生驻波,严重时会引起馈线的绝缘层及发射机末级功放管的损坏.为了使信号和能量有效地传输,必须使电路工作在阻抗匹配状态,即信号源或功率源的内阻等于电路的输入阻抗,电路的输出阻抗等于负载的阻抗.在一般的输入、输出电路中常含有电阻、电容和电感元件,由它们所组成的电路称为电抗电路,其中只含有电阻的电路称为纯电阻电路.下面对纯电阻电路和电抗电路的阻抗匹配问题分别进行简要的分析. 1 纯电阻电路 把一个电阻为R的用电器,接在一个电动势为E、内阻为r的电池组上(如图1所示),在什么条件下电源输出的功率最大呢?这个问题运用全电路欧姆定律I=EΠ(R+ Ξ收稿日期:2001203205 作者简介:郭继红(19572),男,沈阳市人,实验师,从事高频电子线路实验和电视图像处理研究

一,首先给大家介绍一下Polar软件,Polar是专业计算阻抗的软件,其版本包 括:Si6000,Si8000,及Si9000. 二,其次给大家介绍常见的几种阻抗模型:特性阻抗,差分阻抗,共面性阻抗. 1.外层特性阻抗模型: 2.内层特性阻抗模型: 3.外层差分阻抗模型: 4.内层差分阻抗模型: 5.共面性阻抗模型:包括(1)外层共面特性阻抗,(2)内层共面特性阻抗,(3)外层共面差分阻抗,(4)内层共面差分阻抗. 三,再次给大家介绍一下芯板(即Core)及半固化片(即PP), 每个多层板都是由芯板和半固化片通过压合而成的,普通的FR-4板材一般有:生益,建滔,联茂等板材供应商.生益FR-4的芯板根据板厚来划分 有:0.10MM ,0.15MM,,0.2MM ,,0.25MM.0.3MM,0.4MM,0.5MM等,包括有H/HOZ,1/1OZ,等这里有一点需要大家特别注意:含两位小数的板厚是指不含铜的厚度,只有一位小数指包括铜的总厚度,例如:0.10MM 1/1OZ的芯板,其0.10MM是指介质的厚度,其总厚度应为 0.10MM+0.035+0.035MM=0.17MM,再如:0.15MM 1/1OZ的芯板,其总厚度 是:0.15MM+0.035MM+0.035MM=0.22MM,而0.2MM 1/1OZ的芯板,其总厚度就是0.2MM,它的介质厚度应为:0.2MM-0.035MM-0.035MM=0.13MM. 半固化片(即PP),一般包括:106,1080,2116,7628等,其厚度为:106为 0.04MM,1080为0.06MM,2116为0.11MM,7628为0.19MM. 当我们计算层叠结构时候通常需要把几张PP叠在一起,例如:2116+106,其厚度为0.15MM,即6MIL;1080*2+7628,其厚度为0.31MM,即12.2MIL等.但需注意以下几点:1,一般不允许4张或4张以上PP叠放在一起,因为压合时容易产生滑板现象.2,7628的PP一般不允许放在外层,因为7628表面比较粗糙,会影响板子的外观.3,另外3张1080也不允许放在外层,因为压合时也容易产生滑板现象. 后续我会把一些常用的芯板以及各种组合的PP厚度汇总给大家,以便学习用Polar软件计算阻抗及层叠结构时使用! 四, 怎样使用Polar Si9000软件计算阻抗: 首先应知道是特性阻抗还是差分阻抗,具体阻抗线在哪些信号层上,阻抗线的参考面是哪些层?其次根据文件选择正确的阻抗模型来计算阻抗,最后通过调整各层间的介质厚度,或者调整阻抗线的线宽及间距来满足阻抗及板厚的要求! 五,举例说明怎样使用Polar Si9000计算阻抗及设计层叠结构: 1.四层板板厚1.6MM,外层信号线要求控制50欧姆特性阻抗和100欧姆差分阻抗.其设计结构详见:4层板1.6MM阻抗设计.jpg,其中H1代表的是信号层与参考层之间的介质厚度,即L1与L2之间的厚度为3.2MIL,Er1为板材的介电常数,FR-4通常为4.2-4.6,W1称为下线宽,W2称为上线宽,一般认为W1=W+0.5MIL,W2=W-0.5MIL,S1(注意S1<2W)为两根差分线之间的间距(指线边缘与线边缘之间距离),T1信号层的成品铜厚,外层1OZ=1.4MIL,而内层考虑的蚀刻的因素,我们通常认为内层1OZ=1.2MIL,而0.5OZ=0.6MIL。Zdiff为阻抗值。Calculate为计算按钮,各因素是可以互相推算的,例如我们要控制50欧姆的阻抗,线宽为

怎样理解阻抗匹配 阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。阻抗匹配分为低频和高频两种情况讨论。 我们先从直流电压源驱动一个负载入手。由于实际的电压源,总是有内阻的(请参看输出阻抗一问),我们可以把一个实际电压源,等效成一个理想的电压源跟一个电阻r串联的模型。假设负载电阻为R,电源电动势为U,内阻为r,那么我们可以计算出流过电阻R的电流为:I=U/(R+r),可以看出,负载电阻R越小,则输出电流越大。负载R上的电压为:Uo=IR=U/[1+(r/R)],可以看出,负载电阻R 越大,则输出电压Uo越高。再来计算一下电阻R消耗的功率为:P=I2×R=[U/(R+r)]2×R=U2×R/(R2+2×R×r+r2) =U2×R/[(R-r)2+4×R×r] =U2/{[(R-r)2/R]+4×r} 对于一个给定的信号源,其内阻r是固定的,而负载电阻R则是由我们来选择的。注意式中[(R-r)2/R],当R=r时,[(R-r)2/R]可取得最小值0,这时负载电阻R上可获得最大输出功率Pmax=U2/(4×r)。即,当负载电阻跟信号源内阻相等时,负载可获得最大输出功率,这就是我们常说的阻抗匹配之一。对于纯电阻电路,此结论同样适用于低频电路及高频电路。当交流电路中含有容性或感性阻抗时,结论有所改变,就是需要信号源与负载阻抗的的实部相等,虚部互为相反数,这叫做共扼匹配。在低频电路中,我们一般不考虑传输线的

匹配问题,只考虑信号源跟负载之间的情况,因为低频信号的波长相对于传输线来说很长,传输线可以看成是"短线",反射可以不考虑(可以这么理解:因为线短,即使反射回来,跟原信号还是一样的)。从以上分析我们可以得出结论:如果我们需要输出电流大,则选择小的负载R;如果我们需要输出电压大,则选择大的负载R;如果我们需要输出功率最大,则选择跟信号源内阻匹配的电阻R。有时阻抗不匹配还有另外一层意思,例如一些仪器输出端是在特定的负载条件下设计的,如果负载条件改变了,则可能达不到原来的性能,这时我们也会叫做阻抗失配。 在高频电路中,我们还必须考虑反射的问题。当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号叠加在原信号上将会改变原信号的形状。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射。为什么阻抗不匹配时会产生反射以及特征阻抗的求解方法,牵涉到二阶偏微分方程的求解,在这里我们不细说了,有兴趣的可参看电磁场与微波方面书籍中的传输线理论。传输线的特征阻抗(也叫做特性阻抗)是由传输线的结构以及材料决定的,而与传输线的长度,以及信号的幅度、频率等均无关。 例如,常用的闭路电视同轴电缆特性阻抗为75Ω,而一些射频设备上则常用特征阻抗为50Ω的同轴电缆。另外还有一种常见的传输线是特性阻抗为300Ω的扁平平行线,这在农村使用的电视天线架上

阻抗匹配的研究 在高速的设计中,阻抗的匹配与否关系到信号的质量优劣。阻抗匹配的技术可以说是丰富多样,但是在具体的系统中怎样才 能比较合理的应用,需要衡量多个方面的因素。例如我们在系统中设计中,很多采用的都是源段的串连匹配。对于什么情况下需 要匹配,采用什么方式的匹配,为什么采用这种方式。 例如:差分的匹配多数采用终端的匹配;时钟采用源段匹配; 1、串联终端匹配 串联终端匹配的理论出发点是在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使 源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射. 串联终端匹配后的信号传输具有以下特点: A 由于串联匹配电阻的作用,驱动信号传播时以其幅度的50%向负载端传播; B 信号在负载端的反射系数接近+1,因此反射信号的幅度接近原始信号幅度的50%。 C 反射信号与源端传播的信号叠加,使负载端接受到的信号与原始信号的幅度近似相同; D 负载端反射信号向源端传播,到达源端后被匹配电阻吸收;? E 反射信号到达源端后,源端驱动电流降为0,直到下一次信号传输。 相对并联匹配来说,串联匹配不要求信号驱动器具有很大的电流驱动能力。 选择串联终端匹配电阻值的原则很简单,就是要求匹配电阻值与驱动器的输出阻抗之和与传输线的特征阻抗相等。理想的信 号驱动器的输出阻抗为零,实际的驱动器总是有比较小的输出阻抗,而且在信号的电平发生变化时,输出阻抗可能不同。比如电 源电压为+4.5V的CMOS驱动器,在低电平时典型的输出阻抗为37?,在高电平时典型的输出阻抗为45?[4];TTL驱动器和CMOS驱动 一样,其输出阻抗会随信号的电平大小变化而变化。因此,对TTL或CMOS电路来说,不可能有十分正确的匹配电阻,只能折中考

说明:信号源输出阻抗一般都为50ohm ,信号源面板显示的输出信号幅度,频率是图2处信号的幅度,频率。 (1)若负载输入阻抗为50ohm ,则信号源输出与负载输入匹配,则负载获得的信号幅度,频率与2处的电压幅度理论上一致。 (2)若负载输入阻抗为1Mohm ,则信号源输出与负载输入不匹配,则负载获得的信号幅度,频率与1处的电压幅度理论上一致。 ◆ 纯电阻电路:低频和高频都存在;(匹配) 1、 负载电阻R 电压:1 1l i i R U U U r R r R = =++;负载电阻越大,则负载获得的电压越高。 2、 负载R 电流:i l U i R r = +;负载越小,则负载获得的电流越小。 3、 负载获得的功率:2 22222//24l i l i i U U R r P i R U R U R r R R r R r ????====++≤ ? ?+???? ;当且 仅当R=r 时;负载功率最大。 ◆ 存在容性和感性阻抗时,(共轭匹配) 共轭匹配:当交流电路中含有容性或感性阻抗时,若信号源与负载阻抗的实部相等,虚 部互为相反数,此时负载获得最大功率。 源电抗:r r Z r jX =+

负载电抗:R R Z R jX =+ 负载功率: ()() ()()()()22 22 22222 142R r R r R r R r U R U U U P r R r X X R r X X r X X R r X X R R R R = ==≤??+++??+++++++++ ????? 当且仅当R r R r X X =??=-?时,负载获得最大功率。 结论: 1、需要大的电流输出,则选择小的负载R ; 2、需要大的电压输出,则选择大的负载R ; 3、需要输出最大功率,则选择与信号源内阻匹配的电阻R 。(功率传递!) 低频时,信号的波长相对与传输线来说很长,传输线可以看成短线,反射可以不考虑。 高频时,f c λ=;信号频率很高时,信号的波长就很短,当波长和传输线的长度可以比拟时,反射信号叠加在原来信号上将会改变原信号的形状。例:传输线的特性阻抗跟负载阻抗不匹配时,在负载端就产生反射,能量传输不过去,降低效率,功率发射不出去,甚至会顺坏发射设备。 当信号源和传输线、负载的阻抗相互匹配时候,有更多的能量从信号源中发射出来!!! 问题:、25kHz~80kHz 用示波器50ohm 输入阻抗实测,为何信号源输出和示波器显示信号的幅度不一致?(据说这种射频源有些频段幅度不准,建议下次问问罗德斯瓦茨做源的代理)

阻抗计算说明 Rev0.0 heroedit@https://www.doczj.com/doc/4c15630913.html, z给初学者的 一直有很多人问我阻抗怎么计算的. 人家问多了,我想给大家整理个材料,于己于人都是个方便.如果大家还有什么问题或者文档有什么错误,欢迎讨论与指教! 在计算阻抗之前,我想很有必要理解这儿阻抗的意义 z传输线阻抗的由来以及意义 传输线阻抗是从电报方程推导出来(具体可以查询微波理论) 如下图,其为平行双导线的分布参数等效电路: 从此图可以推导出电报方程 取传输线上的电压电流的正弦形式 得 推出通解

定义出特性阻抗 无耗线下r=0, g=0得 注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义) ε μ=EH Z 特性阻抗与波阻抗之间关系可从 此关系式推出. Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现象等等.在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来. z 叠层(stackup)的定义 我们来看如下一种stackup,主板常用的8层板(4层power/ground 以及4层走线层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为 L1,L4,L5,L8 下面熟悉下在叠层里面的一些基本概念,和厂家打交道经常会使用的 Oz 的概念 Oz 本来是重量的单位Oz(盎司 )=28.3 g(克) 在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz, 对

阻抗匹配与史密斯(Smith)圆图: 基本原理 本文利用史密斯圆图作为RF 阻抗匹配的设计指南。文中给出了反射系数、阻抗和导 纳的作图范例,并用作图法设计了一个频率为60MHz 的匹配网络。 实践证明:史密斯圆图仍然是计算传输线阻抗的基本工具。 在处理RF 系统的实际应用问题时,总会遇到一些非常困难的工作,对各部分级联电路的不同阻抗进行匹配就是其中之一。一般情况下,需要进行匹配的电路包括天线与低噪声放大器(LNA)之间的匹配、功率放大 器输出(RFOUT)与天线之间的匹配、LNA/VCO 输出与混频器输入之间的匹配。匹配的目的是为了保证信号或能量有效地从“信号源”传送到“负载”。 在高频端,寄生元件(比如连线上的电感、板层之间的电容和导体的电阻)对匹配网络具有明显的、不可预 知的影响。频率在数十兆赫兹以上时,理论计算和仿真已经远远不能满足要求,为了得到适当的最终结果,还必须考虑在实验室中进行的RF 测试、并进行适当调谐。需要用计算值确定电路的结构类型和相应的目标元件值。 有很多种阻抗匹配的方法,包括: ? 计算机仿真: 由于这类软件是为不同功能设计的而不只是用于阻抗匹配,所以使用起来比较复杂。设计者必须熟悉用正确的格式输入众多的数据。设计人员还需要具有从大量的输出结果中找到有用数据的技能。另外,除非计算机是专门为这个用途制造的,否则电路仿真软件不可能预装在计算机上。 ? 手工计算: 这是一种极其繁琐的方法,因为需要用到较长(“几公里”)的计算公式、并且被处理的数据多为复数。 ? 经验: 只有在RF 领域工作过多年的人才能使用这种方法。总之,它只适合于资深的专家。 ? 史密斯圆图: 本文要重点讨论的内容。 本文的主要目的是复习史密斯圆图的结构和背景知识,并且总结它在实际中的应用方法。讨论的主题包括参数的实际范例,比如找出匹配网络元件的数值。当然,史密斯圆图不仅能够为我们找出最大功率传输的匹配网络,还能帮助设计者优化噪声系数,确定品质因数的影响以及进行稳定性分析。 w w w . p c b t e c h .n e t

什么是典型的电缆阻抗? 同轴电缆使用的最典型阻抗值为50欧姆和75欧姆。50欧姆同轴电缆大概是使用中最常见的,一般使用在无线电发射接收器,实验室设备,以太等环境下。 另一种常用的电缆类型是75欧姆的同轴电缆,一般用在视频传输,有限电视网络,天线馈线,长途电讯应用等场合。 电报和电话使用的裸露平行导线也是典型的阻抗为600欧姆。一对线径标准22的双绞线,使用合适的绝缘体,因为机械加工的限制,平均阻抗大约在120欧姆左右,这是另一种具有自己特有特性阻抗的传输线。 某些天线系统中使用300欧姆的双引线,以匹配折合半波阵子在自由空间阻抗。(但当折合阵子处于八木天线中的时候,阻抗通常会下降很多,一般在100-200欧姆左右) (注:加反射板也会改变阵子的阻抗值,一般会降低,而且反射板越近则阻抗降低越多。) 为什么是50欧姆的同轴电缆? 在美国,用作射频功率传输的标准同轴电缆的阻抗几乎无一例外地都是50欧姆。为什么选用这个数值,在伯德电子公司出示的一篇论文中有解释。 不的的参数都对应一个最佳的阻抗值。内外导体直径比为 1.65时导线有最大功率传输能力,对应阻抗为30欧姆(注:lg1.65*138 =30欧姆,要使用空气为绝缘介质,因为这个时候介电常数最小,

如果使用介电常数为2.3的固体聚乙烯,则阻抗只有不到20欧姆)。最合适电压渗透的直径比为2.7,对应阻抗大约是60欧姆。(顺带一提,这个是很多欧洲国家使用的标准阻抗) 当发生击穿时,对功率传输能力的考量是忽略了渗透电流的,而在阻抗很低,30欧姆时,渗透电流会很高。衰减只源自导体的损失,此时的衰减大约比最小衰减阻抗(直径比3.5911)77欧姆的时候上升了50%,而在这个比率下(D/d=3.5911),最大功率的上限为3 0欧姆电缆最大功率的一半。 以前,很少使用微波功率,电缆也无法应付大容量传输。因此减少衰减是最重要的因素,导致了选择77(75欧姆)为标准。同时也确立了硬件的规格。当低耗的绝缘材料在实际中应用到柔性电缆上,电缆的尺寸规格必须保持不变,才能和现存的设备接口吻合。 聚乙烯的介电常数为2.3,以空气(介电常数为1)为绝缘层的导线的阻抗为77欧姆,如果以聚乙烯来填充绝缘空间的话,阻抗将减少为51欧姆。虽然精确的标准是50欧姆,51欧姆的电缆在今天仍然在使用。 在77欧姆点的衰减最小,60欧姆点的击穿电压为最大,而30欧姆点的功率输送量是最大的。(注:洋人的思维也如此混乱,这些性能指标明明不是由阻抗决定的。前面说过,这些由D/d比决定的。闲扯这些只让人产生误解) 另外一个可以导致50欧姆同轴电缆的事情,如果您使用一个合适直径的中心导体,并将绝缘体注入中心倒替周围,再在外围装上屏

我来大概概括一下ADC输入阻抗的问题: 1:SAR型ADC这种ADC内阻都很大,一般500K以上。即使阻抗小的ADC,阻抗也是固定的。所以即使只要被测源内阻稳定,只是相当于电阻分压,可以被校正。 2:开关电容型,如TLC2543之类。他要求很低的输入阻抗用于对内部采样电容快速充电。这时最好有低阻源,否则会引起误差。实在不行,可以外部并联一很大的电容,每次被取样后,大电容的电压下降不多。因此并联外部大电容后,开关电容输入可以等效为一个纯阻性阻抗,可以被校正。 3:FLASH.html">FLASH型(直接比较型)。大多高速ADC都是直接比较型,也称闪速型(FLASH),一般都是低阻抗的。要求低阻源。对外表现纯阻性,可以和运放直接连接 4:双积分型大多输入阻抗极高,几乎不用考虑阻抗问题 5:Sigma-Delta型。这是目前精度最高的ADC类型,也是最难伺候的一种ADC。重点讲一下要注意的问题: a.内部缓冲器的使用。SigmaDelta型ADC属于开关电容型输入,必须有低阻源。所以为了简化外部设计,内部大多集成有缓冲器。缓冲器打开,则对外呈现高阻,使用方便。但要注意了,缓冲器实际是个运放。那么必然有上下轨的限制。大多数缓冲器都是下轨50mV,上轨AVCC-1.5V。在这种应用中,共莫输入范围大大的缩小,而且不能到测0V。一定要特别小心!一般用在电桥测量中,因为共模范围都在1/2VCC附近。不必过分担心缓冲器的零票,通过内部校零寄存器

很容易校正的。 b.输入阻抗问题。SigmaDelta型ADC属于开关电容型输入,在低阻源上工作良好。但有时候为了抑制共模或抑制乃奎斯特频率外的信号,需要在输入端加RC滤波器,一般DATASHEET上会给一张最大允许输入阻抗和C和Gain的关系表。这时很奇怪的一个特性是,C越大,则最大输入阻抗必须随之减小!刚开始可能很多人不解,其实只要想一下电容充电特性久很容易明白的。还有一个折衷的办法是,把C取很大,远大于几百万倍的采样电容Cs(一般4~20PF),则输入等效纯电阻,分压误差可以用GainOffset寄存器校正。 c.运放千万不能和SigmaDelta型ADC直连!前面说过,开关电容输入电路电路周期用采样电容从输入端采样,每次和运放并联的时候,会呈现低阻,和运放输出阻抗分压,造成电压下降,负反馈立刻开始校正,但运放压摆率(SlewRate)有限,不能立刻响应。于是造成瞬间电压跌落,取样接近完毕时,相当于高阻,运放输出电压上升,但压摆率使运放来不及校正,结果是过冲。而这时正是最关键的采样结束时刻。 所以,运放和SD型ADC连接,必须通过一个电阻和电容连接(接成低通)。而RC的关系又必须服从5.c里面所述规则。 d.差分输入和双极性的问题。SD型ADC都可以差分输入,都支持双极性输入。但这里的双极性并不是指可以测负压,而是Vi+Vi-两脚之间的电压。假设Vi-接AGND,那么负压测量范围不会超过-0.3V。正确的接法是Vi+Vi-共模都在-0.3~VCC之间差分输入。一个典型的

传输线阻抗匹配方法 匹配阻抗的端接有多种方式,包括并联终端匹配、串联终端匹配、戴维南终端匹配、AC终端匹配、肖特基二极管终端匹配。 1.并联终端匹配 并联终端匹配是最简单的终端匹配技术,通过一个电阻R将传输线的末端接到地或者接到V CC上。电阻R的值必须同传输线的特征阻抗Z0匹配,以消除信号的反射。终端匹配到V CC可以提高驱动器的源的驱动能力,而终端匹配到地则可以提高电流的吸收能力。 并联终端匹配技术突出的优点就是这种类型终端匹配技术的设计和应用简便易行,在这种终端匹配技术中仅需要一个额外的元器件;这种技术的缺点在于终端匹配电阻会带来直流功率消耗。另外并联终端匹配技术也会使信号的逻辑高输出电平的情况退化。将TTL输出终端匹配到地会降低V OH的电平值,从而降低了接收器输入端对噪声的免疫能力。 对长走线进行并联终端匹配后仿真,波形如下: 2.串联终端匹配 串联终端匹配技术是在驱动器输出端和信号线之间串联一个电阻,是一种源

端的终端匹配技术。驱动器输出阻抗R0以及电阻R值的和必须同信号线的特征阻抗Z0匹配。对于这种类型的终端匹配技术,由于信号会在传输线、串联匹配电阻以及驱动器的阻抗之间实现信号电压的分配,因而加在信号线上的电压实际只有一半的信号电压。 而在接收端,由于信号线阻抗和接收器阻抗的不匹配,通常情况下,接收器的输入阻抗更高,因而会导致大约同样幅度值信号的反射,称之为附加的信号波形。因而接收器会马上看到全部的信号电压(附加信号和反射信号之和),而附加的信号电压会向驱动端传递。然而不会出现进一步的信号反射,这是因为串联的匹配电阻在接收器端实现了反射信号的终端匹配。 串联终端匹配技术的优点是这种匹配技术仅仅为系统中的每一个驱动器增加一个电阻元件,而且相对于其它的电阻类型终端匹配技术来说,串联终端匹配技术中匹配电阻的功耗是最小的,而且串联终端匹配技术不会给驱动器增加任何额外的直流负载,也不会在信号线与地之间引入额外的阻抗。 由于许多的驱动器都是非线性的驱动器,驱动器的输出阻抗随着器件逻辑状态的变化而变化,从而导致串联匹配电阻的合理选择更加复杂。所以,很难应用某一个简单的设计公式为串联匹配电阻来选择一个最合适的值。 对长走线进行串联终端匹配后仿真,波形如下: 3.戴维南终端匹配

PCB阻抗设计及计算简介

特性阻抗的定义 ?何谓特性阻抗(Characteristic Impedance,Z0) ?电子设备传输信号线中,其高频信号在传输线中传播时所遇到的阻力称之为特性阻抗;包括阻抗、容抗、感抗等,已不再只是简单直流电的“欧姆电阻”。 ?阻抗在显示电子电路,元件和元件材料的特色上是最重要的参数.阻抗(Z)一般定义为:一装置或电路在提供某特定频率的交流电(AC)时所遭遇的总阻力. ?简单的说,在具有电阻、电感和电容的电路里,对交流电所起的阻碍作用叫做阻抗。

设计阻抗的目的 ?随着信号传送速度迅猛的提高和高频电路的广泛应用,对印刷电路板也提出了更高的要求。印刷电路板提供的电路 性能必须能够使信号在传输过程中不发生反射现象,信号 保持完整,降低传输损耗,起到匹配阻抗的作用,这样才 能得到完整、可靠、精确、无干扰、噪音的传输信号。?阻抗匹配在高频设计中是很重要的,阻抗匹配与否关系到信号的质量优劣。而阻抗匹配的目的主要在于传输线上所有 高频的微波信号皆能到达负载点,不会有信号反射回源点。

设计阻抗的目的 ?因此,在有高频信号传输的PCB板中,特性阻抗的控制是尤为重要的。 ?当选定板材类型和完成高频线路或高速数字线路的PCB 设计之后,则特性阻抗值已确定,但是真正要做到预计的特性阻抗或实际控制在预计的特性阻抗值的范围内,只有通过PCB生产加工过程的管理与控制才能达到。

PCB的制造中影响阻抗的因素 ?从PCB制造的角度来讲,影响阻抗和关键因素主要有: –线宽(w) –线距(s)、 –线厚(t)、 –介质厚度(h) –介质常数(Dk) εr相对电容率(原俗称Dk介质常数),白容生对此有研究和专门诠释。 注:其实阻焊也对阻抗有影响,只是由于阻焊层贴在介质上,导致介电常数增大,将此归于介电常数的影响,阻抗值会相应减 少4%

谈谈嵌入式系统PCB设计中的阻抗匹配与0欧电阻 1、阻抗匹配 阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。根据接入方式阻抗匹配有串行和并行两种方式;根据信号源频率阻抗匹配可分为低频和高频两种。 (1)高频信号一般使用串行阻抗匹配。串行电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于20M的信号PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号、数据和地址总线信号等。串行匹配电阻的作用有两个: ◆减少高频噪声以及边沿过冲。如果一个信号的边沿非常陡峭,则含有大量的高频成分,将会辐射干扰,另外,也容易产生过冲。串联电阻与信号线的分布电容以及负载输入电容等形成一个RC电路,这样就会降低信号边沿的陡峭程度。 ◆减少高频反射以及自激振荡。当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号叠加在原信号上将会改变原信号的形状。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射,造成自激振荡。PCB板内走线的低频信号直接连通即可,一般不需要加串行匹配电阻。 (2)并行阻抗匹配又叫“终端阻抗匹配”,一般用在输入/输出接口端,主要指与传输电缆的阻抗匹配。例如,LVDS与RS422/485使用5类双绞线的输入端匹配电阻为100~120Ω;视频信号使用同轴电缆的匹配电阻为75Ω或50Ω、使用篇平电缆为300Ω。并行匹配电阻的阻值与传输电缆的介质有关,与长度无关,其主要作用也是防止信号反射、减少自激振荡。值得一提的是,阻抗匹配可以提高系统的EMI性能。此外,解决阻抗匹配除了使用串/并联电阻外,还可使用变压器来做阻抗变换,典型的例子如以太网接口、CAN总线等。 2、0欧电阻的作用 (1)最简单的是做跳线用,如果某段线路不用,直接不焊接该电阻即可(不影响外观)。 (2)在匹配电路参数不确定的时候,以0欧姆代替,实际调试的时候,确定参数,再以具体数值的元件代替。 (3)想测某部分电路的工作电流时,可以去掉0欧电阻,接上电流表,这样方便测量电流。 (4)在布线时,如果实在布不过去了,也可以加一个0欧的电阻起跨接作用。(5)在高频信号网络中,充当电感或电容(起阻抗匹配作用,0欧电阻也有阻抗!)。充当电感用时,主要是解决EMC问题。 (6)单点接地,例如模拟地与数字地的单点对接共地。 (7)配置电路,可以取代跳线和拨码开关。有时用户会乱动设置,易引起误会,为了减少维护费用,应用0欧电阻代替跳线等焊在板子上。 (8)系统调试用,例如将系统分成几个模块,模块间的电源与地用0欧电阻分开,调试阶段发现电源或地短路时,去掉0欧电阻可缩小查找范围。 上述功能也可使用“磁珠”替代。0欧电阻与磁珠虽然功能上有点类似,但存在本质差别,前者呈阻抗特性,后者呈感抗特性。磁珠一般用在电源与地网络中,有滤波作用。

功率放大器设计的关键:输出匹配电路的性能 2008-05-15 17:51:20 作者:未知来源:电子设计技术 关键字:功率放大器匹配电路匹配网络s参数串联电阻输出功率Cout耗散功率网络分析仪高Q值对于任何功率放大器(功率放大器)设计,输出匹配电路的性能都是个关键。但是,在设计过程中,有一个问题常常为人们所忽视,那就是输出匹配电路的功率损耗。这些功率损耗出现在匹配网络的电容器、电感器,以及其他耗能元件中。功率损耗会降低功率放大器的工作效率及功率输出能力。 因为输出匹配电路并不是一个50Ω的元件,所以耗散损失与传感器增益有很大的区别。输出匹配的具体电路不同,损耗也不一样。对于设计者而言,即使他没有选择不同技术的余地,在带宽和耗散损失之间,在设计方面仍然可以做很多折衷。 匹配网络是用来实现阻抗变化的,就像是功率从一个系统或子系统传送另一个系统或者子系统,RF设计者们在这上面下了很大的功夫。对于功率放大器,阻抗控制着传送到输出端的功率大小,它的增益,还有它产生的噪声。因此,功率放大器匹配网络的设计是性能达到最优的关键。 损耗有不同的定义,但是这里我们关心的是在匹配网络中,RF功率以热量的形式耗散掉的损耗。这些损耗掉的功率是没有任何用途。依据匹配电路功能的不同,损耗的可接受范围也不同。对功率放大器来讲,输出匹配损耗一直是人们关注的问题,因为这牵涉到很大的功率。效率低不仅会缩短通话时间,而且还会在散热和可靠性方面带来很大的问题。 例如,一个GSM功率放大器工作在3.5V电压时,效率是55%,能够输出34dBm的功率。在输出功率为最大时,功率放大器的电流为1.3A。匹配的损耗在0.5dB到1dB的数量级,这与输出匹配的具体电路有关。在没有耗散损失时,功率放大器的效率为62%到69%。尽管损耗是无法完全避免的,但是这个例子告诉我们,在功率放大器匹配网络中,损耗是首要问题。 耗散损失 现在我们来看一个网络,研究一个匹配网络(图1a)中的耗散损失。电源通过无源匹配网络向无源负载传输功率。在电源和负载阻抗之间没有任何其他的限制。把匹配网络和负载合在一起考虑,电源输出一个固定量的功率Pdel 到这个网络(图1b)。输出功率的一部分以热量的形式耗散在匹配网络中。而其余的则传输到负载。Pdel是传输到匹配网络和负载(图1c)上的总功率,PL是传输到负载的那部分功率。 了解了这两个量,我们就可以知道,实际上到底有多大的一部分功率是作为有用功率从电源传输到了负载,其比例等于PL/Pdel。 这是对功率放大器输出匹配的耗散损失的正确测量,因为它只考虑了实际传输功率以及耗散功率。反射功率没有计算进去。 由此可知,这个比例就等于匹配网络工作时的功率增益GP。而工作时的功率增益完整表达式为: 这里,是负载反射系数,是匹配网络的s参数, 损失就是增益的倒数。因此,耗散损失可以定义为: Ldiss = 1/GP。 对于功率放大器而言,我们为它设计的负载一般是50Ω。通常,我们用来测量s参数的系统阻抗也是50Ω。如果系统阻抗和负载都是50Ω,那么就为0,于是,上面的表达式就可以简化为: 在计算一个匹配网络的耗散损失时,只需要知道它的传输值和反射散射参数的大小,这些可以很容易地从s参数的计算过程中得到,因为网络分析仪通常都会采用线性的方式来显示s参数的值。在评估输入和级间耗散损失时,负载的阻抗不是50Ω,但是上述的规律依然适用。 因为反射和耗散损失很容易混淆,射频工程师有时就会采用错误的方法来计算耗散损失。而最糟糕的方法就是采用未经处理的s21来进行计算。一个典型的匹配网络在1GHz(图2)时,对功率放大器而言,是数值为4+j0Ω的负载阻抗。匹配网络采用的是无损耗元件来进行模拟的,所以在匹配网络中不存在功率的耗散问题。然而,s21却是-6dB,因为在50Ω的源阻抗和4Ω的负载之间存在着巨大的不匹配问题。作为一个无损耗网络,除了一些数字噪音外,模拟的耗散损失为0dB。 在电路的模拟当中,我们可能可以采用s21来求出正确的耗散损失。这一过程包括采用复杂模拟负载线的共轭

RFID天线阻抗自动匹配技术 射频设别( Radio Frequency Identification,RFID)技术是从20世纪90年代兴起并逐步走向成熟的一项自动识别技术,通过射频耦合方式进行非接触双向通信,达到目标识别和数据交换的目的。 RFID读写器在移动过程中,天线感应系数和阻抗的易变性造成读写器传输功率不必要的损耗和识别能力的下降。对于读写器天线阻抗的匹配,国外一些大公司的研究已经转向自动匹配方面,并有了比较成功的案例,而国内应用研究主要还集中于手动匹配方面。随着集成技术的发展,天线与读写器模块将向集成化发展,对于天线阻抗的匹配也将提出新的要求,而手动匹配是个耗时长且复杂的过程。 因此,天线阻抗的自动匹配技术也将成为一种发展趋势。本文论证了天线阻抗的手动匹配方法,并在最大化应用集成元件的情况下,提出了一种新的适用于13. 56 MHz RFID读写器的天线阻抗自动匹配方法。 1 阻抗手动匹配技术 RFID系统使用外接天线与电子标签进行无线通信。天线夹具形状和尺寸的易变性使天线的输入阻抗易随外部环境的变化还发生微弱变化,导致传输功率的无用损耗。国际上RFID 读写器天线标准阻抗一般都为50Ω,本文设定阻抗匹配目标为(50 + j0)Ω。天线电路,一般包含3个部分: (1)电磁兼容( EMC)滤波(L0 , C0 )电路;(2)包含可调谐电容C1、C2 的匹配电路;(3)天线。 EMC滤波电路滤去了载波频率为 13. 56 MHz阻抗变换时的谐波干扰。它有一个固定的谐振频率,这个频率是实际数据传输率和最高副载波频率的结合。如用曼切斯特编码时,传输的最高数据率为424 kbit/ s,频率为848 kHz,则谐振频率为14. 408MHz。 图1 天线电路框图 在载波频率为13. 56 MHz时,通过在TX1 和TX2 两点测量天线线路的反射系数(即参数S11 )来手动调谐,直到天线电路的输入阻抗达到目标,计算方程如下: ,又有ZL = 50W,可以看出,要使(S11 ) = 50Ω, S11必须为0。 手动调谐即是交替不断调整电容C1、C2 的值,同时观察曲线变化,直到在所要求的频率点S11等于0。图2为某一天线电路在频率在10~20MHz之间变化时,其反射系数的变化曲线,其中,标记13. 56MHz的点, S11值近似为0,达到了匹配要求。 图2 经过手动匹配的天线smit图 2 阻抗自动匹配技术 本文提出了一种自动匹配技术,其电路,主要包含测量电路,匹配电路和控制电路。因为手工匹配方法耗时长,且需要良好的意识和丰富的经验来选择合适的电容,另外必须配备一些昂贵的设备,如网络分析仪或阻抗分析仪等。对于一些小公司来说,是不现实的。同时,一些手持式RF设备的发展使得手动匹配越来越不适应。对于这些移动设备,最理想的天线电路应该仅仅包含集成模块,且随着阻抗变化可以自动匹配。 图3 自动调谐匹配电路图 2. 1 测试电路 手工匹配采用的是阻抗分析仪或者网络分析仪,网络分析仪是用定向耦合器来测量天线

传输线阻抗匹配的方法 传输线简介传输线(transmission line)输送电磁能的线状结构的设备。它是电信系统的重要组成部分,用来把载有信息的电磁波,沿着传输线规定的路由自一点输送到另一点。 以横电磁(TEM)模的方式传送电能和(或)电信号的导波结构。传输线的特点是其横向尺寸远小于工作波长。主要结构型式有平行双导线、平行多导线、同轴线、带状线,以及工作于准TEM模的微带线等,它们都可借助简单的双导线模型进行电路分析。各种传输TE模、TM模,或其混合模的波导都可认为是广义的传输线。波导中电磁场沿传播方向的分布规律与传输线上的电压、电流情形相似,可用等效传输线的观点分析。 传输线的特性传输线的均匀性 传输导体横截面的形状、使用的材料、导体间的间隔和导体周围的介质,在线路的全部长度上都保持均匀不变的,称为均匀传输线。否则便叫做不均匀传输线。均匀传输线的一次参数均匀地分布于整个传输线上,其数值不随考察点的位置而变化。 传输线在制造和建筑过程中可能出现的偏差,都规定有必要的允许范围。如果出现的不均匀性偏差不超过这些规定,都可以看作是均匀传输线。 性能参数 通常用衰减系数、相移系数、特性阻抗,或与之相对应的其它参数来描述。其数值仅与传输线的结构、几何尺寸、制造传输线使用的材料、工作波长(或工作频率)有关,见表。 传输线阻抗匹配的方法匹配阻抗的端接有多种方式,包括并联终端匹配、串联终端匹配、戴维南终端匹配、AC终端匹配、肖特基二极管终端匹配。 1、并联终端匹配 并联终端匹配是最简单的终端匹配技术,通过一个电阻R将传输线的末端接到地或者接到VCC上。电阻R的值必须同传输线的特征阻抗Z0匹配,以消除信号的反射。终端匹配到VCC可以提高驱动器的源的驱动能力,而终端匹配到地则可以提高电流的吸收能力。