I2C总线结构及工作原理小结

- 格式:pdf

- 大小:193.42 KB

- 文档页数:10

I2C串行总线的组成及工作原理I2C是一种常用的串行通信协议,用于在电子设备之间进行数据传输。

它的全称是Inter-Integrated Circuit,即片间串行总线。

1. 主设备(Master Device):负责发起通信请求并控制整个传输过程的设备。

主设备通常是微控制器、处理器或其他智能设备。

2. 从设备(Slave Device):被主设备控制的设备。

从设备可以是各种外围设备,如传感器、存储器、显示器等。

3. SDA(Serial Data Line):用于数据传输的双向串行数据线。

主设备和从设备都可以发送和接收数据。

4. SCL(Serial Clock Line):用于同步数据传输的时钟线。

主设备产生时钟信号来同步数据传输。

5. VCC(Supply Voltage):提供电源电压给I2C总线上的设备。

6. GND(Ground):提供共地连接。

I2C总线的工作原理如下:1.初始化:主设备发起一次总线初始化,在I2C总线上产生一个启动信号。

启动信号表示I2C总线上有新的数据传输将开始。

2.寻址:主设备发送一个7位的设备地址到总线上指定要与之通信的从设备。

I2C总线上可以存在多个从设备,每个设备都有唯一的地址。

3.数据传输:主设备发送数据或者命令到从设备,或者从设备向主设备发送数据回复。

数据通过SDA线传输,时钟通过SCL线提供。

4.确认(ACK):数据传输完成后,每个接收设备都会回复一个确认信号,表示它已经成功接收数据。

主设备和从设备都可以发送确认信号。

5.停止:主设备发送一个停止信号来结束一次数据传输过程。

停止信号表示I2C总线上没有更多的数据传输。

I2C总线的工作原理是基于主从结构的,主设备控制数据传输的流程。

主设备通过发送启动信号来开始一个数据传输过程,并通过发送设备地址和数据来与特定的从设备进行通信。

通过SCL线的时钟同步,主设备和从设备可以准确地进行数据传输,避免了数据丢失和冲突。

I2C总线工作原理I2C是一种串行通信总线,常用于连接主控制器和外设设备之间。

I2C总线通过低速的串行数据传输,可同时连接多个设备,使用双线(SDA和SCL)来进行通信。

本文将详细介绍I2C总线的工作原理。

1.物理层:I2C总线包含两条线路:数据线(SDA)和时钟线(SCL)。

SDA线用于数据传输,而SCL线用于同步数据传输的时钟信号。

这两条线都由一个上拉电阻连接到正电源,以保持高电平状态。

当总线上的设备需要发送数据时,它将拉低SDA线上的电平。

在同一时间,SCL线上的电平将控制数据的传输速率。

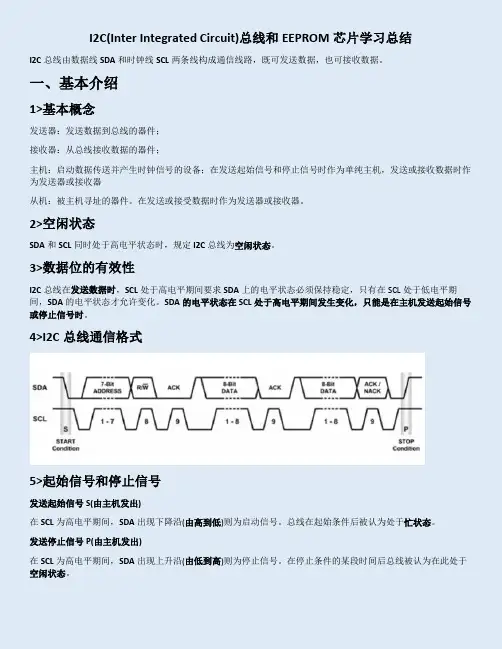

2.起始信号和停止信号:I2C总线使用起始信号和停止信号来定义数据传输的开始和结束。

起始信号是由主控制器发送的,通常在主控制器要发送数据之前。

停止信号也是由主控制器发送的,在数据传输完成后。

起始信号由将SCL线保持高电平,SDA线从高电平跳变到低电平。

停止信号是在SCL线保持高电平,SDA线从低电平跳变到高电平。

3.地址和数据传输:在I2C总线上,每个设备都有一个唯一的7位地址,用于寻址特定的设备。

主控制器在发送数据之前,必须先向设备发送一个地址字节。

地址字节由起始信号之后的8个位组成(其中最高位为0用于读操作,1用于写操作)。

设备在成功接收到其地址之后,将向主控制器发送一个应答位。

4.字节传输:一旦设备的地址被成功接收,主控制器可以开始发送数据字节。

数据字节的传输遵循以下步骤:-主控制器发送一个数据字节-设备接收到数据字节并发送一个应答位-主控制器发送下一个数据字节-设备接收到数据字节并发送一个应答位-重复以上步骤,直到所有数据字节都被传输完成5.应答信号:每当主控制器发送一个应答请求时,设备都应该发送一个应答位来确认数据的接收情况。

应答位是一个低电平脉冲,由设备在接收到数据字节后发送。

如果设备成功接收到数据字节,则发送一个低电平的应答位。

若设备遇到错误或无法接收数据,则发送一个高电平的非应答位。

6.时钟同步:I2C总线的数据传输是由SCL线上的时钟信号进行同步的。

I2C串行总线工作原理及应用I2C(Inter-Integrated Circuit)是一种串行总线协议,用于连接芯片和外设,允许它们之间进行通信和数据交换。

I2C总线由飞利浦公司(现在的恩智浦半导体)于1980年代初引入,是一种简单、高效、可扩展的通信协议。

I2C总线由两根信号线组成,分别是SCL(串行时钟线)和SDA(串行数据线),可以连接多个设备,每个设备都有一个唯一的地址,设备之间可以通过发送和接收数据来进行通信。

I2C总线的工作原理如下:1.主从模式:在I2C总线上,一个设备必须充当主设备,其他设备充当从设备。

主设备负责生成时钟信号和控制整个通信流程,从设备只能在主设备允许时传输数据。

2.起始和停止条件:通信开始时,主设备会发送一个起始条件来指示数据的传输开始。

而通信结束时,主设备会发送一个停止条件来指示数据的传输结束。

3.传输过程:在传输数据之前,主设备首先会发送一个地址码来指定要通信的从设备。

然后,主设备将数据传输到从设备(写操作)或从设备将数据传输给主设备(读操作)。

每个数据字节都会被从设备确认,并继续传输下一个数据字节。

4.时钟和数据线:SCL线用于同步数据传输的时钟信号,SDA线用于传输实际的数据。

数据传输是按字节进行的,每个字节有8个位,其中第一个位是数据位,后面的7个位是地址位或数据位。

I2C总线的应用非常广泛,包括但不限于以下几个方面:1.传感器:I2C总线可以用于将传感器连接到主控芯片。

例如,温度传感器、湿度传感器、光照传感器等可以通过I2C总线传输采集到的数据给主控芯片进行处理和分析。

2. 存储器:I2C总线可以连接EEPROM(Electrically Erasable Programmable Read-Only Memory)和其他类型的存储器芯片,用于存储数据和程序。

主控芯片可以通过I2C总线读取和写入存储器中的数据。

3.显示器:一些液晶显示器和OLED显示器可以通过I2C总线与主控芯片进行通信。

I2C工作原理范文I2C(Inter-Integrated Circuit)是一种串行通信协议,用于在集成电路之间进行通信。

它由Philips公司(现在是恩智浦半导体公司)于1982年推出,并已广泛应用于各种电子设备和嵌入式系统中。

I2C的工作原理如下:1.总线拓扑结构:I2C使用两根线进行通信,一根是串行数据线(SDA),另一根是串行时钟线(SCL)。

所有I2C设备都连接到同一条总线上,并且每个设备都有一个唯一的7位地址。

2. 主从模式:I2C通信分为主设备(Master)和从设备(Slave)。

主设备是发起通信的一方,负责控制总线上的通信。

从设备则是被动接收和响应来自主设备的命令或数据。

3. 起始信号和停止信号:I2C通信始于主设备发送一个起始信号(Start)和一个从设备地址。

起始信号告诉所有从设备,接下来的通信将是针对一些特定从设备的。

停止信号(Stop)则标志着一次通信的结束。

4.寄存器读写:主设备通过发送一个从设备地址和一个读/写位来指定是读取还是写入数据。

在写入模式下,主设备发送数据字节到从设备;在读取模式下,主设备请求从设备发送数据字节。

5.硬件应答:在每个字节的传输结束后,接收方(主设备或从设备)都会返回一个应答位。

如果接收方成功接收到了字节,则返回一个低电平的应答位;否则,返回一个高电平的非应答位。

6.时钟同步:I2C通信的时钟由主设备控制。

主设备在SCL线上产生时钟信号,而从设备则根据这个信号来同步自己的时钟。

总的来说,I2C通信是通过主设备发起的,它控制总线上的通信流程和时钟信号。

从设备根据主设备发送的命令或数据来执行相应的操作,并通过应答位来确认是否成功接收到数据。

这种通信协议适用于多个设备之间进行简单的数据交换和控制操作。

I2C的优点是可以同时连接多个设备,并且只需要两根线就能实现通信。

这大大减少了总线的复杂性和成本。

同时,I2C还具有可靠性高、速度适中、容错能力强等特点,使得它成为了很多电子设备中主要的串行通信协议之一总之,I2C是一种简单、灵活且可靠的串行通信协议。

I2C总线——总结I2C总线是一种串行数据通信协议,用于连接集成电路之间进行通信。

它由Phillips公司于1982年首次提出,并在随后的几十年中得到广泛应用和发展。

I2C总线采用两根线(SDA和SCL)进行通信,具有简单、高效的特点,适用于较短距离的通信。

首先,I2C总线的架构包括两个主要组成部分:主设备和从设备。

主设备通常是微控制器或其他控制器,负责发起和控制通信。

从设备是主设备的外围设备,例如传感器、电池芯片、存储器等。

主设备通过发送信号来控制从设备,并接收从设备发送的响应信号。

在I2C通信中,数据以字节为单位传输,每个字节都包含8位。

通信的起始由主设备发起,并发送设备地址标识。

从设备必须匹配该地址才能进入通信状态。

在通信过程中,主设备发送读取或写入指令,然后发送或接收数据。

每个数据字节都由从设备发送确认信号,以确保数据的准确接收。

除了基本的读写操作,I2C总线还支持一些高级功能,例如时钟同步、主从模式切换和热插拔功能。

这些功能使得I2C总线适用于各种应用场景,包括电子设备、通信系统、工业控制和汽车电子等。

然而,尽管I2C总线具有许多优点,但也存在一些限制和挑战。

首先,I2C总线在传输速度方面不如其他通信协议(如SPI和CAN)。

其次,长距离传输可能受到电压下降、信号失真和干扰等因素的影响。

此外,I2C总线的主设备需要额外的控制逻辑和处理能力,这可能增加系统的复杂性和成本。

综上所述,I2C总线是一种非常常用和实用的串行通信协议。

它具有简单、高效的特点,适用于较短距离的设备间通信。

通过多主机配置和高级功能支持,I2C总线可以满足各种应用的需求。

然而,需要根据具体的应用场景和要求来选择合适的通信协议,以确保系统的性能和可靠性。

I2C(Inter-Integrated Circuit)是一种串行通信协议,用于在芯片之间进行数据传输。

它由飞利浦半导体(现在的恩智浦半导体)于1982年开发,并广泛应用于各种电子设备中。

I2C具有简单、高效和可靠的特点,成为众多芯片和模块之间常用的通信接口之一。

本文将详细介绍I2C的基本工作原理。

一、总线架构I2C采用了主从结构的总线架构,其中主设备(Master)负责发起数据传输请求,而从设备(Slave)则在接收到请求后进行响应。

一个I2C总线上可以连接多个从设备,每个从设备都有一个唯一的地址。

主设备通过发送起始信号(Start)来启动通信,然后选择要与之通信的从设备地址,最后发送停止信号(Stop)结束通信。

二、物理层I2C使用双线制进行数据传输,包括数据线(SDA)和时钟线(SCL)。

数据线上的信号是双向的,用于传输数据。

时钟线则由主设备控制,用于同步数据传输。

三、起始和停止信号I2C通信以起始信号(Start)和停止信号(Stop)来标识通信的开始和结束。

起始信号由主设备产生,它表示将要发起一次新的通信。

停止信号同样由主设备产生,表示一次通信的结束。

四、数据传输格式I2C采用了基于字节的数据传输格式。

每个字节都由8位二进制数据组成,包括7位数据位和1位数据方向位。

数据方向位为0表示发送数据,为1表示接收数据。

在每个字节的传输过程中,都会先发送数据方向位,然后再发送数据位。

五、时钟同步I2C使用时钟同步机制来确保通信的准确性。

时钟线由主设备产生,并控制整个数据传输过程的时序。

在每个时钟周期中,数据线上的数据必须稳定,并且只有在时钟线为低电平时才能改变。

六、地址传输在I2C通信中,每个从设备都有一个唯一的7位地址。

主设备通过发送地址来选择要与之通信的从设备。

地址由8个位组成,最高位是固定的0或1,用于表示读(1)或写(0)操作。

其余的7位用于指定从设备的地址。

七、数据传输流程I2C通信的数据传输流程如下:1. 主设备发送起始信号(Start)。

i2c方案原理一、引言i2c(Inter-Integrated Circuit,简称I2C)是一种串行通信协议,用于连接集成电路芯片。

它由飞利浦公司于1982年推出,并在2006年被发布为开放标准。

i2c方案广泛应用于消费电子、工业自动化、汽车电子等领域,具有简单、灵活、可靠的特点。

二、基本原理i2c方案基于主从结构,其中一个设备充当主设备,其他设备作为从设备。

主设备控制总线的时序和数据传输,从设备响应主设备的请求。

1. 总线结构i2c总线由两根线组成:串行数据线(SDA)和串行时钟线(SCL)。

SDA用于双向数据传输,SCL用于时钟同步。

2. 数据传输数据传输分为两种模式:地址模式和数据模式。

在地址模式下,主设备发送从设备的地址和读写方向的位,从设备通过SDA线响应。

在数据模式下,主设备发送或接收数据位,从设备通过SDA线响应。

3. 时序控制i2c使用时钟同步进行数据传输。

时钟由主设备产生,并控制数据的读写。

三、i2c的工作方式i2c方案的工作方式可以概括为以下几个步骤:1. 总线初始化主设备启动总线,通过发送一个特定的起始条件将总线置为忙状态。

2. 从设备选择主设备发送从设备的地址和读写方向的位,从设备通过SDA线响应。

3. 数据传输主设备根据需要发送或接收数据。

4. 响应控制从设备接收到数据后,通过响应控制线(ACK)发送一个ACK或NACK信号,表示接收到了数据或出现了错误。

5. 信号终止主设备发送一个停止条件来结束数据传输。

四、i2c的优势和应用领域i2c方案具有以下优势,使其广泛应用于各个领域:1. 简单i2c只需要两根线,使硬件设计更加简单。

2. 灵活i2c总线可以连接多个设备,每个设备都有唯一的地址,提供了灵活的系统设计选择。

3. 可靠i2c使用时钟同步,可以有效减少传输错误和冲突。

i2c方案适用于以下领域:1. 消费电子i2c广泛应用于智能手机、平板电脑、数码相机等消费电子产品中,用于连接各个芯片和模块。

单片机中I2C总线接口原理解析与应用场景讨论I2C总线接口原理解析与应用场景讨论在单片机领域,I2C(Inter-Integrated Circuit)总线接口是一种常见的通信标准,被广泛应用于各种电子设备中。

本文将对I2C总线接口的原理进行解析,并讨论其在实际应用中的场景。

一、I2C总线接口原理解析I2C总线接口是一种串行通信协议,由飞利浦(Philips)公司开发,并于1982年发布。

它使用两根线作为物理连接,即SDA(Serial Data Line)和SCL(Serial Clock Line)。

SDA线用于数据传输,而SCL线用于时钟同步。

1. 主从通信模式I2C总线接口支持主从通信模式,其中主设备负责发起通信并控制总线,而从设备则被动等待主设备的命令。

主设备的角色可以由单片机或其他控制器扮演,而从设备则可以是各种外设,如传感器、存储器等。

2. 7位地址编码在I2C总线接口中,每个从设备都被分配了一个唯一的7位地址。

主设备通过发送设备地址来选择要与之通信的从设备。

这种设计使得可以在同一总线上连接多个从设备,从而实现多设备之间的通信。

3. 起始和停止条件I2C总线接口使用起始和停止条件来标识通信的开始和结束。

起始条件是在SCL为高电平时,SDA从高电平跳变到低电平。

停止条件则是在SCL为高电平时,SDA从低电平跳变到高电平。

通过这样的起始和停止条件,可以确保每次通信的可靠性。

4. 传输协议在I2C总线接口中,数据的传输是以字节为单位进行的。

每个字节的传输都包含8位数据位和一个ACK位(应答位)。

发送设备通过在SCL线的一个周期中向SDA线发送一个数据位,而接收设备则在下一个SCL周期的下降沿读取数据位。

5. 时钟速率I2C总线接口的时钟速率可以根据实际需求进行调整。

通常,速率可以在100 kHz至400 kHz之间选择,但一些高性能设备支持更高的速率。

时钟速率的选择应该考虑到总线长度、负载电容和设备的工作频率等因素。

I2C总线协议及工作原理I2C(Inter-Integrated Circuit)是一种串行通信协议,用于连接微控制器、传感器、存储器、显示屏等芯片之间的通信。

它是由飞利浦公司(现在的恩智浦)在1982年提出的,并在很多应用中得到了广泛使用。

本文将详细介绍I2C总线协议的工作原理。

1.起始条件:当主设备(通常是微控制器)希望发送数据或者接收数据时,首先发送一个起始条件。

起始条件是SCL线为高电平时,SDA线从高电平跳变到低电平。

2.地址传输:主设备发送从设备地址和一个读/写位。

从设备地址是每个设备在总线上的唯一标识,用于在多个设备中选择特定的设备进行通信。

读/写位表示主设备是要发送数据给从设备,还是要从从设备读取数据。

3.读/写传输:主设备根据之前发送的读/写位,选择相应的读或写传输方式。

如果主设备要写入数据,则会将数据传输到SDA线上,然后等待从设备的确认。

如果主设备要读取数据,则会接收从设备发送的数据。

在读取数据时,主设备可以发送应答信号或非应答信号,用于告知从设备是否继续传输数据。

4.停止条件:当主设备完成数据的读写操作后,会发送停止条件。

停止条件是SCL线为高电平时,SDA线从低电平跳变到高电平。

通过发送停止条件,主设备告知总线上的其他设备,当前通信已经结束。

在I2C总线上,可以连接多个设备,每个设备都有一个唯一的地址。

当主设备想要与特定的设备进行通信时,需要发送从设备的地址。

在传输数据时,设备之间的数据传输是以字节为单位的。

在每个字节传输结束后,可以选择继续传输下一个字节,或者发送停止条件。

如果从设备没有准备好接收或发送数据,可以发送非应答信号,中断当前传输。

1.高可靠性:I2C总线使用了双线传输,可以检测到传输过程中的错误。

2.多设备连接:可以连接多个设备在同一个I2C总线上进行通信,通过地址选择特定的设备。

3.低成本:I2C总线只需要两根线(SDA和SCL),简化了硬件设计。

4.低功耗:I2C总线的工作电压可以从3.3V到5V,能够满足大部分设备的需求。

I2C总线协议及工作原理I2C(Inter-Integrated Circuit)是一种串行通信总线协议,由Philips公司提出,适用于在电路板上连接各种集成电路的短距离通信。

I2C总线协议的工作原理是基于主从结构的,其中一个设备作为主设备,其他设备作为从设备。

主设备负责发起通信操作,而从设备则被动响应主设备的指令。

主设备在总线上发出启动信号,然后发送器件地址。

发起通信的主设备控制总线的速度和时序,并且主设备确定读写的类型。

从设备根据地址进行匹配,并根据主设备请求的读写进行响应。

通信完成后,主设备会发送停止信号释放总线。

在I2C总线上,每个设备都有一个唯一的7位或10位地址。

主设备在传输数据之前,会发送起始信号,这个信号告诉从设备通信即将开始。

随后主设备会发送一个地址字节,包含了要通信的从设备的地址和读写控制位。

如果从设备的地址和发送的地址匹配,从设备会发送一个应答(ACK)信号,表示准备好接收数据。

主设备然后才开始发送或接收数据。

数据在I2C总线上传输是以字节为单位的,并且每个字节之后都会有一个应答信号。

主设备负责设置时钟线的电平来控制数据的传输,而从设备负责读取或发送数据位。

在读取数据时,主设备会发送应答位,如果从设备准备好读取下一个字节,会发送应答信号;反之,如果从设备不准备好,会发送非应答信号。

在I2C总线上,主设备还可以使用多主模式,允许多个主设备操作相同的总线。

当多个主设备在通信总线上发起通信时,总线的冲突可能会发生。

为了解决这个问题,I2C总线使用了仲裁机制。

仲裁机制根据优先级决定那个设备能够继续发送数据,优先级高的设备可以中断优先级低的设备的传输,从而保证通信的顺利进行。

总结起来,I2C总线协议是一种简单、高效的串行通信协议。

它通过两根线实现设备之间的通信,并且支持多主模式。

它的工作原理是基于主从结构,主设备发起通信,从设备被动响应。

通过仲裁机制,解决了多主模式下的冲突问题。

I2C的原理与应用I2C(Inter-Integrated Circuit)是一种串行通信协议,由飞利浦公司于1980年代开发,用于在数字电子系统中连接各个芯片。

它主要使用两根线进行通信,即SDA(Serial Data Line,串行数据线)和SCL (Serial Clock Line,串行时钟线),同时支持多主机和多从机的通信方式。

I2C协议被广泛应用于各种数字设备的互连,包括传感器、存储器、协处理器等。

I2C的通信原理如下:1.总线结构:I2C总线包含一个主机和多个从机。

主机负责控制总线,并发起数据传输请求;从机等待主机发送命令,并根据命令执行相应操作。

2.时序:I2C总线上的通信需要依靠时钟信号进行同步。

主机通过时钟信号SCL驱动数据传输。

数据线SDA上的数据在时钟信号的上升沿或下降沿进行采样和发送。

3.起始和停止位置:数据传输始于主机发送一个起始信号,结束于主机发送一个停止信号。

起始信号通知所有从机总线上的数据传输即将开始;停止信号表示数据传输已经结束。

4.地址与数据传输:在起始信号之后,主机发送一个地址帧给从机。

地址帧的最高位表示读写操作,从机通过地址帧判断自身是否为数据传输的对象,并相应地进行操作。

主机可以在同一个传输过程中多次发送数据,并且可以从一个从机读取多个字节的数据。

I2C的应用广泛,以下是一些常见的应用领域:1.传感器:I2C通信协议在许多传感器和芯片中得到应用,例如加速度计、陀螺仪、温度传感器和压力传感器等。

这些传感器通过I2C协议与主处理器进行通信,并将采集到的数据传输到主处理器进行处理。

2. 存储器:I2C接口也广泛应用于存储器设备,如EEPROM (Electrically Erasable Programmable Read-Only Memory)和FRAM (Ferroelectric Random Access Memory)。

这些存储器设备可以通过I2C总线进行读写操作,从而存储和检索数据。

I2C总线1.简介I2C(Inter-IC)总线10多年前由Philips公司推出,是近年来在微电子通信控制领域广泛采用的一种新型总线标准。

它是同步通信的一种特殊形式,具有接口线少,控制方式简化,器件封装形式小,通信速率较高等优点。

在主从通信中,可以有多个I2C总线器件同时接到I2C总线上,通过地址来识别通信对象。

2.I²C 总线术语发送端 - 发送数据到总线的器件。

当发送端器件可以主动将数据放到总线,我们称为主控发送端,若可以回应主控端的要求,即称为从属发送端。

接收端- 接收来自总线传输数据的器件。

当接收端器件可以主动接收数据时,我们称为主控接收端,若依照主控端要求而接收,称为从属接收端。

主控端 - 为启动数据传送 (START 指令)、产生时钟 (SCL) 信号并中止数据传送 (STOP指令) 的器件,主控端必须是传送端或接收端。

从属端 - 由主控端定址的器件。

从属端可以扮演接收端或发送端的角色。

多重主控端 - 在总线上可同时存一个以上的主控端,并且不会造成冲突或数据遗失。

通常来说运用 "bit-banged" 软件的主控端并不具有多重主控端能力,I²C 总线控制器提供了一个将多重主控端硬件 I²C 连接端口加入到 DSP 或 ASIC 的简单方法。

仲裁机制- 预先定义在特定时间内只有一个主控端能够取得总线控制权。

同步 - 预先将二个或二个以上的主控端时钟信号予以同步化的定义程序。

SDA- 串行数据信号线 (Serial Data)SCL - 串行时钟信号线 (Serial Clock)3.I2C总线结构I2C 总线上数据的传输速率在标准模式下可达100kbit/s,在快速模式下可达400kbit/s,在高速模式下可达3.4Mbit/s。

I2C串行总线一般有两根信号线,一根是双向的数据线SDA,另一根是时钟线SCL。

所有接到I2C总线设备上的串行数据SDA都接到总线的SDA上,各设备的时钟线SCL接到总线的SCL上。

I2C 总线协议及工作原理一、概括1、 I2C 总线只有两根双向信号线。

一根是数据线SDA ,另一根是时钟线SCL 。

SCL :上涨沿将数据输入到每个 EEPROM 器件中;降落沿驱动 EEPROM 器件输出数据。

(边缘触发 )SDA :双向数据线,为OD 门,与其余随意数目的OD 与 OC 门成 " 线与 " 关系。

I2C 总线经过上拉电阻接正电源。

当总线安闲时,两根线均为高电平(SDL=1;SCL=1 )。

连到总线上的任一器件输出的低电平,都将使总线的信号变低,即各器件的 SDA 及 SCL 都是线“与”关系。

2、主设施与从设施系统中的全部外头器件都拥有一个 7 位的 "从器件专用地点码 " ,此中高 4 位为器件种类,由生产厂家拟订,低 3 位为器件引脚定义地点,由使用者定义。

主控器件经过地点码成立多机通讯的体制,所以 I2C 总线省去了外头器件的片选线,这样不论总线上挂接多少个器件,其系统仍旧为简洁的二线构造。

终端挂载在总线上,有主端和从端之分,主端一定是带有CPU 的逻辑模块,在同一总线上同一时辰使能有一个主端,能够有多个从端,从端的数目受地点空间和总线的最大电容400pF 的限制。

主端主要用来驱动SCL line ;从设施对主设施产生响应;两者都能够传输数据,可是从设施不可以倡始传输,且传输是遇到主设施控制的。

二、协议1.安闲状态I2C 总线总线的SDA 和 SCL 两条信号线同时处于高电平常,规定为总线的安闲状态。

此时各个器件的输出级场效应管均处在截止状态,即开释总线,由两条信号线各自的上拉电阻把电平拉高。

2.开端位与停止位的定义:开端信号:当 SCL 为高时期, SDA 由高到低的跳变;启动信号是一种电平跳变时序信号,而不是一个电平信号。

停止信号:当 SCL 为高时期, SDA 由低到高的跳变;停止信号也是一种电平跳变时序信号,而不是一个电平信号。

i2c总线工作原理I2C总线是一种用于连接微控制器和外部设备的串行通信协议。

它采用两根信号线,分别是时钟线(SCL)和数据线(SDA),通过这两根线实现数据的传输和通信。

I2C总线的工作原理如下:1. 总线结构:I2C总线由一个主设备和多个从设备组成。

主设备负责发起通信并控制总线,从设备则接受主设备的指令并返回数据。

2. 起始信号和结束信号:通信开始时,主设备发出起始信号。

起始信号由将SCL线拉低,然后再将SDA线由高电平拉低构成,表示通信即将开始。

通信结束时,主设备发出结束信号,由将SCL线保持高电平的同时将SDA线由低电平拉高构成,表示通信结束。

3. 数据传输:数据传输通过时钟线(SCL)和数据线(SDA)进行。

时钟线由主设备控制,用于驱动数据传输。

数据线上的数据必须在时钟线为低电平时才能改变,而在时钟线为高电平时必须保持稳定。

4. 主设备和从设备地址:主设备发送数据时,首先发送从设备的地址。

地址由7位或10位构成,前7位是从设备的地址,最高位是读/写位。

读/写位为0表示写操作,为1表示读操作。

从设备接收到自己的地址后,确认信号应答ACK返回给主设备。

5. 数据传输确认:数据传输时,每传输一个字节后,接收方需要发送一个应答信号ACK给发送方,表示已成功接收。

如果接收方不能接收数据或者接收错误,会发送应答信号NAK给发送方。

6. 时钟速率:I2C总线的时钟速率可以根据需求设定,其中标准模式下的时钟速率为100 kbit/s,快速模式为400 kbit/s,高速模式可达到3.4 Mbit/s。

总的来说,I2C总线通过起始和结束信号进行通信的开始和结束,通过时钟线和数据线实现数据的传输和控制。

主设备发送地址和数据,从设备接收并返回数据。

通过应答信号确认数据是否成功传输。

i2c的基本工作原理

I2C(Inter-Integrated Circuit)是由Philips公司开发的两线式串行总线,产生于20世纪80年代,用于连接微控制器及其外围设备。

I2C总线简单而有效,占用PCB(印制电路板)空间很小,芯片引脚数量少,设计成本低。

I2C总线的工作原理如下:

1.I2C总线由两根双向信号线组成:数据线(SDA)和时钟线(SCL)。

2.I2C总线通过上拉电阻接正电源。

当总线空闲时,上拉电阻使SDA和SCL

线都保持高电平(SDA=1,SCL=1)。

3.为了避免总线信号混乱,要求各设备连接到总线的输出端必须是开漏输

出或集电极开路输出的结构。

根据开漏输出或者集电极开路输出信号的

“线与”逻辑,连到I2C总线的任一器件输出低电平,都会使相应总线

上的信号变低。

4.I2C总线通过上拉电阻接正电源,空闲时为高电平。

连接到总线的器件

输出级必须是漏极开路或集电极开路才能执行线与的功能。

5.工作时,主机发送数据到从机,从机在接收到数据后返回给主机。

以上信息仅供参考,如需了解更多信息,请查阅相关书籍或咨询专业人士。