数字电子技术题库

一、填空题

1.(111001)2=( )10=( )16=( )8421BCD码

2.(21)10=( )2

3.(52)10=( )2=( )8421BCD码( )16

4.(B2)16=( )10=( )2=( )8421B CD码

5.(10110.01)2=()10(325)8 =()16

6.(2F)16 =()2=()8

7.( 01011001 )2 =()8 =()16 =()8421BCD

8.逻辑代数中有、、三种基本逻辑运算。

9.两变量函数F(A,B)的异或表达式和同或表达式为和。

10.在数字电路中,三极管通常工作在和状态。

11.四个变量的逻辑函数的最小项共有个,对于变量的任一组取值,任意两个最小项的乘积为,所有最小项的和为。

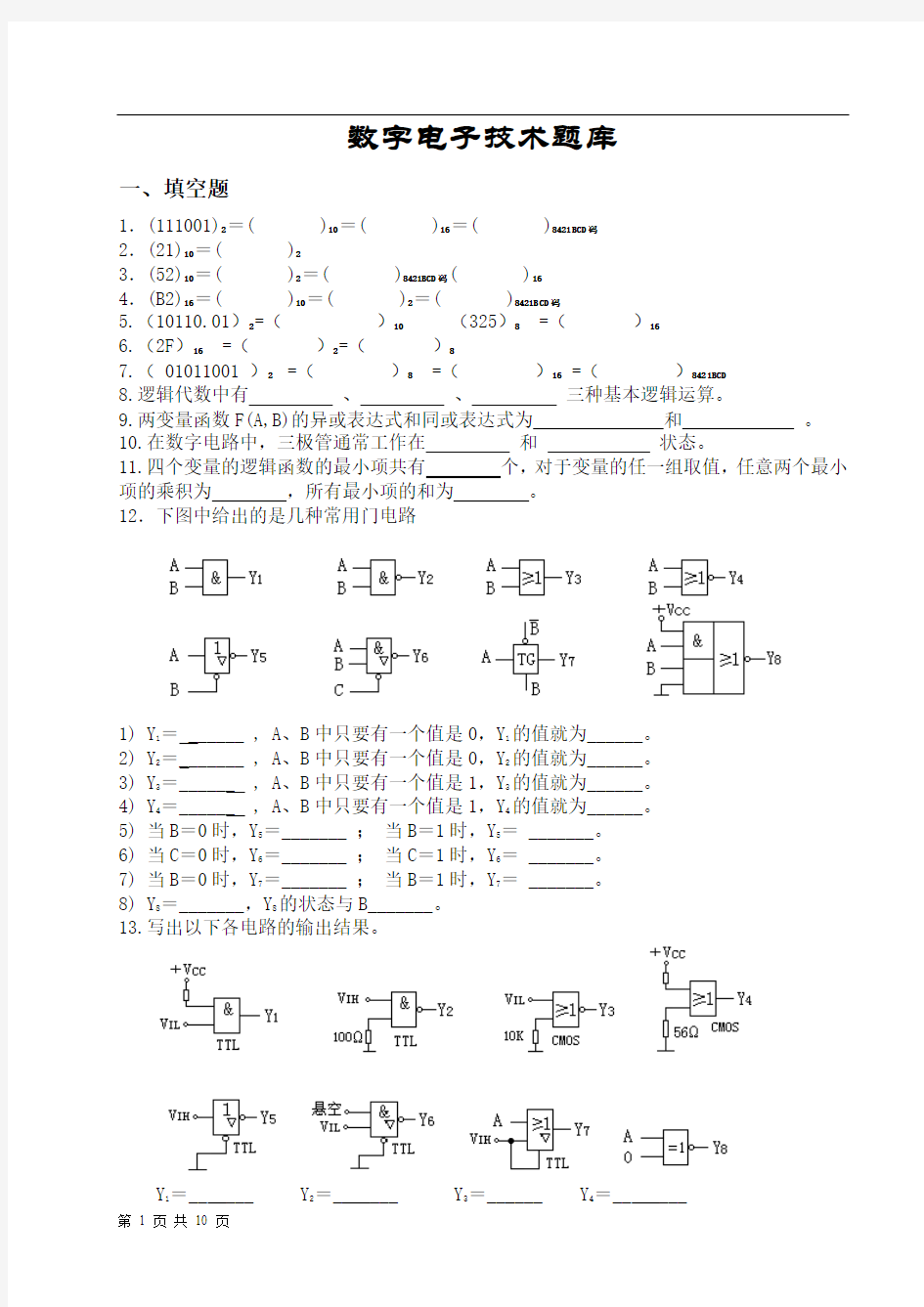

12.下图中给出的是几种常用门电路

1)Y1= ______ , A、B中只要有一个值是0,Y1的值就为______。

2)Y2=_______ , A、B中只要有一个值是0,Y2的值就为______。

3)Y3=______ , A、B中只要有一个值是1,Y3的值就为______。

4)Y4=______ , A、B中只要有一个值是1,Y4的值就为______。

5)当B=0时,Y5=_______ ;当B=1时,Y5= _______。

6)当C=0时,Y6=_______ ;当C=1时,Y6= _______。

7)当B=0时,Y7=_______ ;当B=1时,Y7= _______。

8)Y8=_______,Y8的状态与B_______。

13.写出以下各电路的输出结果。

Y 3=__ ____ Y 6=___ ___ Y 7=__ ___ Y 8=__ ___

14.TTL 电路是由________组成的逻辑电路,并因此得名。CMOS 电路以________为驱动管,以________为负载管;驱动管和负载管的________极相连作为输入端,________极相连作为输出端。

15.触发器有两个________状态,要使电路由一个状态转换到另一个状态,必须要有外加_______ _。

16.要对16个输入信号进行编码,至少需要 二进制数码。

17.一个八选一的数据选择器有 个数据输入端, 个地址输入端。

18.BCD 七段译码器输入的是 位 码。输出端有 个。

19.下图给出的是几种常用触发器。

1)FF 1是同步RS 触发器,Q 1n+1 =________ ,时钟信号B 的________期间有效。

2)FF 2是维持阻塞型D 触发器,Q 2n+ 1=________ ,时钟信号B 的________沿到来后有效。

3)FF 3是主从JK 触发器,Q 3n+1=________ ,时钟信号B 的 沿到来后有效。

20.由与非门组成的基本RS 触发器的输入信号和不得同时为________,否则它们状态将_______ _。

21.同步RS 触发器和基本RS 触发器的区别是前者状态的翻转与时钟脉冲CP________,而后者与CP___ __ __。

22.触发器有 个稳定的输出状态,下降沿触发的JK 触发器的特性方程为 ,T 触发器只有 和 两种逻辑功能。

23. 是构成计数器和寄存器的重要组成部分。

24.触发器是具有 功能的单元电路,RS 触发器的特性方程是 ,T 触发器的特性方程为 ,T ’触发器具有 功能。

25.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接 电平。

26.JK 触发器具有 、 、 和 功能。

27.在数字系统中,根据逻辑功能特点的不同,数字电路可以分为 逻辑电路和 逻辑电路。

28.在数字电路中,编码器和译码器属于 逻辑电路,而计数器和寄存器属于 逻辑电路。

29.目前国产的集成逻辑门电路中,74LS00系列属于 类型逻辑门电路,CD4011属于 类型逻辑门电路。

30.时序电路的特点是:在任何时刻的输出,不但与当时的________状态有关,而且还与前一时刻的_______ _状态有关。

31.按照计数器中各触发器受到计数脉冲控制的情况,可以分为 计数器和 计数器。

32.数码寄存器采用________ 输入,________ 输出。

33.寄存器分为 寄存器和 寄存器两种。

35.下图是用D触发器组成的左移寄存器,请将“串行输入端”、“串行输出端”、“并行输出端”分别填入图中相应位置的横线上。当D随输入脉冲依次输入D0D1D2D3=1011时,经过四个CP脉冲后,Q0Q1Q2Q3的状态为________。

36.单稳态触发器有和两个不同的工作状态。

37.555定时器是一种多用途的数字—模拟混合集成电路,可以方便地构成,和。

38.555构成多谐振荡器,关键要将和接在一起,再加上一个电容,类似于施密特反相器。

二、选择题

1.通常,具有同样功能的TTL电路比CMOS电路工作速度________。

A.高 B.相同 C.低 D.不确定

2.在不影响逻辑功能的情况下,TTL与非门的多余端可________。

A.接高电平 B.接低电平 C.悬空 D.接地

3.在不影响逻辑功能的情况下,CMOS或非门的多余端可________。

A.接高电平 B.接低电平 C.悬空 D.不确定

4.三极管的截止条件为________。

A.U BE > U ON B.U BE < U ON C.U CE = V CC D.U CE < V CC

5.下列逻辑式属于与非式的是。

A.F=AB C? B.F=ABC C.F=A B? D.F=A B?

6.增强型NMOS管的截止条件为________。

A.U GS > U T B.U GS < U T C.U DS = V DD D.U DS < V DD

7.三逻辑变量的取值组合共有种。

A.4种 B.6种 C.8种 D.16种

8.下列几种逻辑门中,可以用作反相器的是。

A.与门 B.与非门 C.或门 D.传输门

9.能够通过并联输出端实现线与的门电路是________。

A.集电极开路门 B.普通与非门 C.三态门 D.CMOS传输门

10.能实现脉冲延时的电路是。

A.多谐振荡器 B.单稳态触发器 C.施密特触发器 D.CMOS传输门11.决定组合逻辑电路某一时刻输出的有关因素是________,而决定时序逻辑电路在某一时刻输出的有关因素是__________;

A.该时刻的输入 B.电路的历史状态

12.下列逻辑电路中,不是组合逻辑电路的是。

A.译码器 B.寄存器 C.全加器 D. 数值比较器

13.下列数字部件中,属于组合逻辑电路的有()

A. 触发器

B. 计数器

C. 数据选择器

D. 移位寄存器

14.下列选项中,不属于组合电路的描述方法的是()

A.逻辑表达式 B.真值表 C.卡诺图 D、状态转换图

15.8选1数据选择器有几个地址控制端。()

A.1 B.2 C.3 D.4

16. 8421BCD码译码器的数据输入线与译码输出线的组合是。

A.4:16 B.4:10 C.10:4 D.16:4

17.选择下图所示FF1~FF2中的一个或多个触发器填入空内。

(1)满足Q n+1=1的触发器是____________________;

(2)满足Q n+1=Q n的触发器是____________________;

(3)满足Q n+1=Q n的触发器是____________________;

(4)满足D触发器功能的是____________________;

(5)满足T触发器功能的是____________________。

18.JK触发器在CP作用下,若状态必须发生翻转,则应使。

A.J=K=0 B.J=1,K=0 C. J=0,K=1 D.J=K=1

19.计数器异步置0端的信号______使电路置0,同步置0端的信号_______使电路置0。

A.只有在时钟脉冲上升沿到来时才能

B.只有在时钟脉冲下降沿到来时才能

C.只有在时钟脉冲触发沿到来时才能

D.无论时钟脉冲为何值都能

20.N进制计数器是指该计数器________。

A.有N个有效状态 B.由N个触发器组成

C.有N个输出端 D.有N个有效循环

21.由M个触发器构成N进制计数器,条件是________。

A.M>=N B.2M>=N C.2M<=N D.M< N

22.由四个触发器构成十进制计数器,其无效状态有________。

A.四个 B.五个 C.六个 D.七个

A.无效状态多 B.由移位寄存器组成

C. 有N个有效状态,且每个有效状态中只有一位为0或1

D.有效状态多

三、判断题

1.增强型NMOS管的截止条件为U GS <=U T。()

2.增强型PMOS管的截止条件为U GS <=U T。()

3.集电极开路门可实现线与。()

4.在电源电压均为5V时,具有同样功能的TTL电路比CMOS电路工作速度高。()5.在电源电压均为5V时,具有同样功能的TTL电路比CMOS电路功耗大。()6.TTL门电路的输入端悬空时相当于接逻辑0。()

7.CMOS门电路的输入端悬空时相当于接逻辑1。()

8.组合逻辑电路某一时刻的输出仅决定于该时刻的输入。()

9.时序逻辑电路的特点必含有存储电路。()

10.同步计数器一定有同步置0或同步置数输入端。()

11.同步计数中各触发器触发脉冲的来源相同。()

12.异步计数器一定有异步置0或异步置数输入端。()

13.异步计数器中各触发器触发脉冲的来源不同。()

14.异步置0端为计数器置0时无需与时钟脉冲CP相配合。()

15.因为同步置0端为计数器置0时,组成计数器的各触发器同时变为0状态,故称之为同步置0端。()

16.如果A + B = B + C,则A = C 。()

17.集成逻辑门电路中多余的输入端可以悬空。()

18.逻辑函数Y = 的对偶式Y,= 。()

19.电平触发的同步RS触发器具有空翻现象。()

20.五进制计数器的计数输出状态一定是000到101。()

21.如果AB =BC ,则A=B。()

22.n个变量的逻辑函数的最小项共有2n个,其中对于变量的任何一种取值只有一个最小项的值为1。()

23.将二进制代码转换成相应的信息的过程称为编码,而用二进制代码表示某种含义的信息的过程称为译码。()

24.CMOS门电路的多余输入端可以悬空,而TTL门电路的多余输入端不可以悬空。( )

25.74LS20属于CMOS类型逻辑门电路,CD4011属于TTL类型逻辑门电路。()

26.输出低电平有效的译码驱动器要接共阳极的数码管才能正常显示数字。()

27.边沿型触发器比主从型触发器具有更强的抗干扰能力。()

28.对于一个四位二进制计数器,若采用置数法实现七进制计数器,最多可以有十六种不同的方案。()

29.数码寄存器通常采用串行输入,并行输出的工作方式。()

30.输出高电平有效的译码驱动器要接共阴极的数码管才能正常显示数字。()

31.主从型RS触发器比基本RS触发器具有更强的抗干扰能力。()

32.可逆计数器就是既能实现加法功能又能实现减法功能的计数器。()

33.同步时序逻辑电路中各触发器触发脉冲的来源相同,异步时序逻辑电路中各触发器触发

四、逻辑函数化简

1.用公式法把下列函数化简为最简的与或表达式。

(1)F= AB AB

+

(2)F=

(3)F=

(4)F= AB ABD AC BCD

+++

(5)C

+

+

Y+

=

B

A

A

C

B

(6)F=

(7)F= A B ABC B C

++?

(8)F=

2. 用卡诺图把下列函数化简为最简与或表达式。

(1)F(A,B,C,D) = ∑m(3,4,6,7,10,13,14,15)

(2)F(A,B,C,D)=∑m(0,2,6,8) 且AB + AC = 0

(3)F(A,B,C,D) = ∑m(0,2,5,7,8,10,13,15)

(4)F(A,B,C,D)=∑m(3,5,7,11)+∑d(8,9,10,12,13,14,15)

(5)F(A,B,C,D) = ∑m(1,7,9,10,11,12,13,15)

(6)F(A,B,C,D)=∑m(1,5,7,9,15)+ ∑d(3,8,11,14)

五、分析题

1. 下图是用集成译码器74LS138来驱动指示灯的电路,请问:(1)当接地,接一脉冲信号并接一盏指示灯C时,试写出A、B、C三盏指示灯的变化规律。

(2)当接高电平,接一脉冲信号并接一盏指示灯C时,试写出A、B、C三盏指示灯的变化规律。

2.电路如图所示,请问:

(1)要使指示灯处于常亮的状态,

A、B、C三个开关应如何处理?

(打开、闭合)

A、B、C三个开关应如何处理?

3.分析该电路的逻辑功能。(分别写出该电路的时钟方程、驱动方程、状态方程、列出状态转换表、画出状态转换图、说明其逻辑功能并检查能否自启动)

4. 分析电路的逻辑功能。(分别写出该电路的时钟方程、驱动方程、状态方程、列出状态转换表、画出状态转换图、说明其逻辑功能并检查能否自启动)

5.分析下图的计数器电路,画出电路的状态转换图,说明这是多少进制的计数器。十六进制计数器74LS161为异步清零,同步置数。

六、设计题

1. 用八选一数据选择器CT74LS151(逻辑符号示意图如下)实现一个三输入多数表决电路。(提示:先列出真值表,求出逻辑函数表达式,然后在逻辑符号示意图上画出具体连线图)

2. 用八选一数据选择器CT74LS151(逻辑符号示意图如下)实现如下功能:判断三个输入变量,当它们相同时输出为1,否则为0。(提示:先列出真值表,求出逻辑函数表达式,然后在逻辑符号示意图上画出具体连线图)

3. 用八选一数据选择器CT74LS151(逻辑符号示意图如下)实现组合逻辑函数 F(A,B,C)

= ,请写出具体分析过程并在逻辑符号示意图上画出连线图。

4. 有一火灾报警系统,设有烟感、温感和紫外光感三种不同类型的火灾探测器。为了防止误报警,只有当其中两种或三种探测器发出探测信号时,报警才产生报警信号。用与非门设计产生报警信号的电路。

5. 试用一片3线-8线译码器74LS138实现一个三变量的判奇电路,要求三个输入变量中有奇数个为1时,输出为1,否则为0。(提示:先列出真值表,求出逻辑函数表达式,然后在逻辑符号示意图上画出具体连线图)

6.试用一片3线-8线译码器74LS138实现如下逻辑函数

Y+

=

A

+

A

AB

BC

C

B

7.用集成十进制同步计数器74LS160(逻辑符号示意图如下)构成一个七进制计数器。(该计数器为同步置数,异步清零,当CT T=CT P=1时,在CP上升沿实现计数功能)

8. 用集成十进制同步计数器74LS160(逻辑符号示意图如下)构成一个五进制计数器。提示:74LS160是异步清零,同步置数。要求用两种方法:(1)复位法;(2)置数法,并设预置数S i=0011。

9. 已知74LS160为集成十进制同步计数器,且该计数器为异步清零,同步置数。

(1)请问下图中左图为几进制计数器

(2)利用置数法在74LS160的基础上改接一个四进制计数器,并设预置数S i=0011。

七、根据给定电路,画出输出波形

1. 根据给定的CP 、A、B的电压波形,画出触发器的输出端Q的波形,设触发器的初始状态为0。

2. 根据给定的CP电压波形,画出触发器的输出端Q1和Q2的波形,设触发器的初始状态为0。

3. 电路如图所示,CP、 A和B的波形如下,并设触发器的初态为0,试画出Q的波形图。

4. 在图示电路中,已知为异步置0端,低电平有效;CP、A、B和C的波形如图所示,设触发器的初态为0,试画出输出端Q的波形。

5. 在图示电路中,已知为异步置1端,低电平有效;CP、A、B和C的波形如图所示,设触发器的初态为0,试画出输出端Q的波形。

注意:本试卷共 8 页, 7 道大题,满分为 100 分;考试时间为 100 分钟 一、填空题(共18分,每空3分) 1、根据图1-1所示电路中电压和电流的参考方向,试计算该元件吸收功率 瓦。 5V 图1-1 2、计算图1-2所示电路中端口1-2端的等效电阻eq R = 。 图1-2 3、电路如图1-3所示,应用戴维宁定理将其等效为一个电阻和一个电压源的串联,试计算该串联电路的等效电阻为 Ω。 10 图1-3 4、电路如图1-4所示,开关S 在t=0时动作,计算在t=0+时电压=+)0(C u V 。 u C 图1-4 5、电路如图1-5所示,试写出电压1u = 。

图1-5 6、电路如图1-6所示,当电路发生谐振时,谐振的频率= ω。 图1-6 二、选择题(共33分,每题3分,答案填在答案卡内,填在别处无效) 1、电路如图2-1所示,电路中的= X U。 A.-5V; B. 5V; C. 10V; D. -10V; 图2-1 2、电路如图2-2所示,电路一端口的输入电阻= ab R。 A. 55Ω; B. 11Ω; C. 30Ω; D. 10V; a b 图2-2 A. 55Ω; B. 15A; C. 5A; D. 10A;

图2-3 A. 55Ω; B. 15A ; C. 5A ; D. 3A ; 图2-4 5、电路的图如图2-5所示,树的树枝数为 。 A. 3; B. 4; C. 5; D. 6; 图2-5 6、电路如图2-6所示,当=L R Ω时可获得最大功率。 A. 30; B. 25; C. 150; D. 180 ; 360V R L 图2-6 A. 10; B. ; C. 2; D. 8; L u L 图2-7 8、Z 参数方程是 。 A. ???+=+=2 2212122 121111U Y U Y I U Y U Y I & &&&&&; B. ???-=-=221221I D U C I I B U A U &&&&&&; C. ???+=+=2221212 2 121111U H I H I U H I H U &&&&&&; D. ???+=+=2221212 2 121111I Z I Z U I Z I Z U &&&&&&; 9、单位阶跃函数的像函数是 。 A. 1; B. 1; C. 1 ; D. s ;

北京理工大学数电期末试卷(含答案)

课程编号:ELC06011 北京理工大学2010-2011学年第二学期 2009级数字电子技术基础B 期末试题A 卷 注:试题答案必须书写在答题纸上,在试题和草稿纸上答题无效。 班级 学号 姓名 成绩 一、(20分)填空 1.在如下门电路中,哪些输出端能够直接互连 bcde 。若输出端不能互连,为什么? 输出都呈现低阻抗,如果相连,如果一个门工作在高电平, 一个门工作在低电平,会使两个门内部形成过电流而损坏器件67 a ) 普通TTL 门电路;b )普通CMOS 门电路;c )OC 门;d )三态输出门; e )OD 门。 2.一个4位D/A 转换器的分辨率为 1/15 1/(2^n-1) ,若参考电压V REF = 6V ,当输入码为0110时,输出电压为 6/16*(8*0+4*1+2*1+1*0)=2 V 。 3.存储容量为2K ×8位的随机存储器,地址线为 11(2的几次方就是十几根) 根,数据线为 8 根;若用1K ×4位的RAM 来实现上述存储容量,需要4 片。 4.A/D 转换器一般需要经过采样、保持、 量化 、 编码 4个过程。 5.单稳态触发器输出脉冲的频率取决于 ,输出脉冲的宽度取决于 。 6.施密特触发器有 2 个稳定状态,单稳态触发器有 1 个稳定状态,多谐振荡器 0 个稳定状态。 7.ROM 设计的组合逻辑电路如图T1所示,写出逻辑函数0Y 和1Y 的表达式。 0Y = ∑(m1,m2,m6) ,1Y = ∑(m0,m1,m5) 。

A B 0Y 1 Y 0123C 4567 图T1 二、(10分) 将下列各式化简为最简与或式,方法不限。 1.CD D AC ABC C A F 1+++= 2.CD B BCD A C B A D C AB F 2+++=,约束条件:B ? C ?+A ?CD ?=0 答案略 三、(10分) 已知图T3中(a )(b )(c )为TTL 门电路,(d )(e )为CMOS 门电路,分别写出各电路的输出状态(0或1或高阻)或输出表达式。 V Ω 1001 Y A B C D R V CC 2 IL V 3 Y IH V 0 (a ) 高电平 V L 代表低电平(b )cmos ,ABCD (c )高阻

电子线路分析与实践2期末复习辅导 2010年10月 练习题 一、填空题 1.(11011)2 =(________)10 2.8421BCD 码的1000相当于十进制的数值 。 3.格雷码特点是任意两个相邻的代码中有_______位二进制数位不同。 4.逻辑函数的反演规则指出,对于任意一个函数F ,如果将式中所有的_________互换,_________互换,_________互换,就得到F 的反函数F 。 5.二极管的单向导电性是外加正向电压时 ,外加反向电压时 。 6.晶体三极管作开关应用时一般工作在输出特性曲线的 饱和 区和 截止 区。 7.TTL 三态门的输出有三种状态:高电平、低电平和 状态。 8. 集 电极开路门的英文缩写为 OC 门,工作时必须外加 和 。 9.一个2线-4线译码器,其输入端的数目与输出端数目相比较,后者较 。 10. 输出n 位代码的二进制编码器,一般有 __________个输入信号端。 11.全加器是指能实现两个加数和____________三数相加的算术运算逻辑电路。 12.时序逻辑电路的输出不仅与 当前输入状态 有关,而且与 输出的原始状态 有关。 13.与非门构成的基本RS 锁存器的特征方程是 S+ n Q R ,约束条件是 。 14.时序逻辑电路中,按照触发器的状态是否同时发生变化可分为 和 。 15.JK 触发器当J =K =________时,触发器Q n+1=Q n 。 16.用555定时器构成的多谐振荡器,若充放电回路中有电阻、电容,则该多谐振荡器形成的脉冲周期T ___0.7(R1+2R2)C ____。 17.A/D 转换需要经过 采样 、 保持 、 量化 和 编码 四个步骤。 18.根据D/A 转换器分辨率计算方法,4位D/A 转换器的分辨率为 6.7% 。 19.DAC 的转换精度包括 分辨率 和 转换误差 。 20.为使采样输出信号不失真地代表输入模拟信号,采样频率f s 和输入模拟信号的最高频率f i max 的关系是 。 21.在A/D 转换时,将一个时间上连续变化的模拟量转换为时间上离散的模拟量的过程称采样。 22.在A/D 转换中,用二进制码表示指定离散电平的过程称为 量化 。 23.CPLD 的含义是 。 二、选择题 1. 十进制数85转换为二进制数为( ) A .1001011 B .1010011 C .1100101 D .1010101 2. 二进制数11011转换为十进制数为( ) A .32 B .27 C .64 D .128 4. 8421BCD 码110011.001表示十进制为( ) A .33.2 B .51.0125 C .63.2 D .51.2 5.在下列一组数中,与2)111001(相等的数是( ) A .16)34( B .(65)8 C . 10 )57(

第1章习题答案 1-1.按照集成度分类,试分析以下集成器件属于哪种集成度器件:(1)触发器;(2)中央处理器;(3)大型存储器;(4)单片计算机;(5)多功能专用集成电路;(6)计数器;(7)可编程逻辑器件。 解:(1)小规模;(2)大规模;(3)超大规模;(4)超大规模;(5)甚大规模;(6)中规模;(7)甚大规模。 1-2.将下列十进制数转换为二进制数、八进制数和十六进制数。 (1)45(2)78(3)25.125 (4)34.25 (5)65 (6)126 解:(1)(45)10=(101101)2=(55)8=(2D)16(2) (78)10=(1111000)2=(170)8=(78)16(3) (25.125)10=(11001.001)2=(170.1)8=(78.2)16(4) (34.25)10=(100010.01)2=(42.2)8=(22.4)16(5) (65)10=(1100101)2=(145)8=(65)16(6) (126)10=(1111110)2=(176)8=(7E)16 1-3.将下列十六进制数转换为二进制数和十进制数。解:(1)(49)16=(1001001)2=(73)10(2)(68)16=(1101000)2=(104)10(3)(22.125)16=(1100101)2=(145)10(4)

(54.25)16=(1010100.00100101)2=(84.14453125)10(5)(35)16=(110101)2=(53)10(6)(124)16=(100100100)2=(292)10 1-4.将下列八进制数转换为二进制数和十进制数。 解:(1)(27)8=(010111)2=(23)10(2)(56)8=(101110)2=(46)10(3)(12.34)8=(1010.011100)2=(10.4375)10(4)(74.25)8=(111100.010101)2=(84.328125)10(5)(35)8=(11101)2=(29)10(6)(124)8=(1010100)2=(84)10 1-5.将下列二进制数转换为十六进制数、八进制和十进制数。 解:(1)(1110001)2=(71)16=(161)8=(113)10(2)(10101.001)2=(15.2)16=(25.1)8=(21.125)10(3)(10111.1101)2=(17.D)16=(27.64)8=(23.8125)10(4)(10001)2=(11)16=(21)8=(17)10(5)(1010101)2=(55)16=(125)8=(85)10 1-6.试求出下列8421BCD码对应的十进制数。 解:(1)(111001)8421BCD=(39)10(2)(1001.0010)8421BCD=(9.2)10(3)(10111.1000)8421BCD=(17.8)10(4)(100001)8421BCD=(21)10(5)(1010101.00100111)8421BCD=(55.27)10 1-7.试求出下列5421BCD码对应的十进制数。 解:(1)(111001)5421BCD=(36)10(2)(1000.0011)5421BCD=(5.3)10(3)(10100.1100)5421BCD=(14.9)10(4)

课程编号:ELC06011 理工大学2010-2011学年第二学期 2009级数字电子技术基础B 期末试题A 卷 注:试题答案必须书写在答题纸上,在试题和草稿纸上答题无效。 班级 学号 成绩 一、(20分)填空 1.在如下门电路中,哪些输出端能够直接互连 bcde 。若输出端不能互连,为什么? 输出都呈现低阻抗,如果相连,如果一个门工作在高电平, 一个门工作在低电平,会使两个门部形成过电流而损坏器件67 a ) 普通TTL 门电路;b )普通CMOS 门电路;c )OC 门;d )三态输出门; e )OD 门。 2.一个4位D/A 转换器的分辨率为 1/15 1/(2^n-1) ,若参考电压V REF = 6V ,当输入码为0110时,输出电压为 6/16*(8*0+4*1+2*1+1*0)=2 V 。 3.存储容量为2K ×8位的随机存储器,地址线为 11(2的几次方就是十几根) 根,数据线为 8 根;若用1K ×4位的RAM 来实现上述存储容量,需要 4 片。 4.A/D 转换器一般需要经过采样、保持、 量化 、 编码 4个过程。 5.单稳态触发器输出脉冲的频率取决于 ,输出脉冲的宽度取决于 。 6.施密特触发器有 2 个稳定状态,单稳态触发器有 1 个稳定状态,多谐振荡器 0 个稳定状态。 7.ROM 设计的组合逻辑电路如图T1所示,写出逻辑函数0Y 和1Y 的表达式。 0Y = ∑(m1,m2,m6) ,1Y = ∑(m0,m1,m5) 。

A B 0Y 1 Y C 图T1 二、(10分) 将下列各式化简为最简与或式,方法不限。 1.CD D AC ABC C A F 1++ += 2.CD B BCD A C B A D C AB F 2+++=,约束条件:B ? C ?+A ?CD ?=0 答案略 三、(10分) 已知图T3中(a ) (b )(c )为TTL 门电路,(d )(e )为CMOS 门电路,分别写出各电路的输出状态(0或1或高阻)或输出表达式。 V 1 Y A B C D 2 V 3 Y V 0 (a ) 高电平 V L 代表低电平(b )cmos ,ABCD (c )高阻 4 Y A B 5 Y IH V (d ) CMOS 高阻 (e )高电平 图T3 四、(10分)

诚信应考,考试作弊将带来严重后果! 华南理工大学期末考试 《数字电子技术》试卷A 注意事项:1. 考前请将密封线内填写清楚; 2. 所有答案请直接答在试卷上(或答题纸上); 3.考试形式: 闭卷; 。 题号一二三四总分 得分 评卷人 一. 单项选择题:(在每小题的备选答案中选出一个正确的答案,并将正确答案 10 题号 123456789 答案 1 A.10000000 B. 000100101000 C.100000000 D.100101000 2.已知函数F的卡诺图如图1-1, 试求其最简与 或表达式 3. 已知函数的反演式为,其 原函数为()。 A. B . C. D. 4.对于TTL数字集成电路来说,下列说法那个是错误的: (A)电源电压极性不得接反,其额定值为5V; (B)不使用的输入端接1; (C)输入端可串接电阻,但电阻值不应太大; (D)OC门输出端可以并接。 5.欲将正弦信号转换成与之频率相同的脉冲信号,应用 A.T,触发器 B.施密特触发器

C.A/D转换器 D.移位寄存器 6.下列A/D转换器中转换速度最快的是()。 A.并联比较型 B.双积分型 C.计数型 D.逐次渐近型 7. 一个含有32768个存储单元的ROM,有8个数据输出端,其地址输入端有()个。 A. 10 B. 11 C. 12 D. 8 8.如图1-2,在TTL门组成的电路中,与非门的输入电流为I iL≤–1mA?I iH≤20μA。G1输出低电平时输出电流的最大值为I OL(max)=10mA,输出高电平时最大输 出电流为I OH(max)=–0.4mA 。门G1的扇出系数是()。 A. 1 B. 4 C. 5 D. 10 9.十数制数2006.375转换为二进制数是: A. 11111010110.011 B. 1101011111.11 C. 11111010110.11 D. 1101011111.011 10. TTL或非门多余输入端的处理是: A. 悬空 B. 接高电平 C. 接低电平 D.接”1” 二.填空题(每小题2分,共20分) 1.CMOS传输门的静态功耗非常小,当输入信号的频率增加时,其功耗将______________。 2. 写出四种逻辑函数的表示方法: _______________________________________________________________; 3.逻辑电路中,高电平用1表示,低电平用0表示,则称为___逻辑; 4. 把JK触发器改成T触发器的方法是_____________。 5.组合逻辑电路是指电路的输出仅由当前的_____________决定。 6.5个地址输入端译码器,其译码输出信号最多应有_____________个。 7.输入信号的同时跳变引起输出端产生尖峰脉冲的现象叫做_____________。8.一片ROM有10根地址线,8根数据输出线,ROM共有________个存储单元。9.N个触发器组成的计数器最多可以组成_____________进制的计数器。 8.基本RS触发器的约束条件是_____________。 三.电路分析题(36分) 1.图3-1(a)所示电路, 移位寄存器原来的数据是,数据从Di顺序输入到移位寄存器,试问: (1) 在图3-1(b)所示输入波形作用下,在T1到T2期间,输出端X、Y的波形? (2) 该电路的逻辑功能?(12分)

09年 5、电路如图1.2所示,TG 为CMOS 传输门,G 为TTL 与非门,则当C=0时 P= ;当C=1时P= 。 B & TG A C C Ω k 10P G 图1.2 6. 当TTL 门电路的输入端悬空时,应视为 (高电平,低电平,不定)。此时,如用万用表测量其输入端电压,读数约为 (0V ,1.4V ,3.6V )。 六、(4分)写出图6所示TTL 门电路构成的组合电路的输出表达式。 图6 七、(6分)写出图7所示电路的逻辑表达式,列出真值表,说明电路逻辑功能。 A B C 图7 八(8分)将图8(a)所示电路用其他器件实现,要求直接在图上画出连线。 (1) 改用3线/8线译码器74LS138和适当的门实现该逻辑电路,图8(b)为 74LS138符号图; (2) 改用8选一数据选择器实现,图8 (c )为8选一数据选择器逻辑符号。 P 图8(a )

图8(b ) 08年 4.函数式D C AB F ++=,写出其对偶式='F ()A B C D +。 5.由TTL 与非门组成的电路如图1-2所示。设与非门输出高电平U OH =3.6V ,低电平为U OL =0.3V ,电压表内阻为20k Ω/V 。当输入ABC =000,开关S 断开时,用万用表测出U 1= 1.4V ,U 2= 0.3V ;当输入ABC =101,开关S 闭合时,U 1= 0.3V ,U 2= 3.6V 。 A B C 图1-2 6.对CMOS 或非门电路,判断下面结论对错: (1)输入端悬空可能造成逻辑出错; (对) (2)输入端对地接大电阻(如510 k Ω)相当于接高电平1; (错) (3)输入端对地接小电阻(如510 Ω)相当于接低电平0; (对) 7.CMOS 电路如图1-3所示,TG 为CMOS 传输门,G 为TTL 与非门,则C=0, P= 0 ; G G G 1 2A

安 徽 建 筑 大学 试 卷( A 卷) 第 1 页 共 6 页 ( 2014—2015学年第2 学期 ) 适用年级专业:电气、自动化、测控专业 注 :学 生 不 得 在 草 稿 纸 上 答 题,答 题 不 得 超 出 框

( )3.下图所示施密特触发器电路中,它的回差电压等于多少 A.2v B.5v C.4v D.3v ( )4.请判断以下哪个电路不是时序逻辑电路: A.计数器 B.寄存器 C.数据比较器 D.触发器 ( )5.某电路的输入波形 Ui 和输出波形Uo 如下图所示,则该电路为: A.施密特触发器 B.反相器 C.单稳态触发器 D.JK 触发器 ( )6.已知逻辑函数 C B C A AB Y '+'+= 与其相等的函数为: A.AB B. C A AB '+ C.C B AB '+ D.C AB + ( )7.下列触发器中上升沿触发的是( )。 A.主从RS 触发器; B.JK 触发器; C.T 触发器; D.D 触发器 ( )8.下列几种A/D 转换器中,转换速度最快的是。 A.并行A/D 转换器 B.计数型A/D 转换器 C.逐次渐进型A/D 转换器 D.双积分A/D 转换器 ( )9.单稳态触发器的输出脉冲的宽度取决于( ) A .触发脉冲的宽度 B .触发脉冲的幅度 C .电路本身的电容、电阻的参数 D .电源电压的数值 ( )10. 指出下列电路中能够把串行数据变成并行数据的电路是( )。 A .JK 触发器 B .3/8线译码器 C .移位寄存器 D .十进制计数器 三、逻辑函数化简及形式变换:(共15分,每题5分) 1.(代数法化简为最简与或式)CD ACD ABC C A F +++'='1 2.(卡诺图法化简逻辑函数) υ

1、3线–8线译码器分析 【习题】分析图P4–5所示电路,写出F1、F2、F3的函数表达式。 图P4–5 (1)3线–8线译码器特性: Y m A A A Y m A A A Y m A A A Y m A A A Y m A A A Y m A A A Y m A A A Y m A A A 0021044210 1121055210 2221066210 3321077210 ==== ==== ==== ====(2)利用3线–8线译码器特性写函数表达式: CBA D A B C D A B C D m m m m m m Y Y Y F + ? + ? ? ? = + + = ? ? = ? ? = 7 4 1 7 4 1 7 4 1 1 2、3线–8线译码器设计 【例4–9】用译码器实现一组多输出函数 F AB BC AC F AB BC ABC F AC BC AC 1 2 3 =++ =++ =++ ? ? ? ? ? (1)将输出函数写成最小项表达式,并进行变换: 7 5 4 1 7 5 4 1 7 5 4 1 1 ) ( ) ( ) ( Y Y Y Y m m m m m m m m ABC C B A C B A C B A C B B A C B A A C C B A AC C B B A F ? ? ? = ? ? ? = + + + = + + + = + + + + + = + + = (2)画实现电路:

3、触发器电路状态转移方程 【习题】 (1)A Q A AQ J n n =+=11 B Q B BQ K n n =+=11 ][][111111↓?+=+=+CP BQ Q A Q K Q J Q n n n n n (2)n Q A D 2⊕= ][][22212↑?+=⊕==+CP Q A Q A Q A D Q n n n n 4、小规模时序逻辑电路分析 【例6–1】参见教材。

通信 071~5 班 20 08 ~20 09 学年 第 二 学期 《数字电子技术基 础》 课试卷 试卷类型: A 卷 一、 单项选择题(每小题2分,共24分) 1、8421BCD 码01101001.01110001转换为十进制数是:( ) A :78.16 B :24.25 C :69.71 D :54.56 2、最简与或式的标准是:( ) A :表达式中乘积项最多,且每个乘积项的变量个数最多 B :表达式中乘积项最少,且每个乘积项的变量个数最多 C :表达式中乘积项最少,且每个乘积项的变量个数最少 D :表达式中乘积项最多,且每个乘积项的变量个数最多 3、用逻辑函数卡诺图化简中,四个相邻项可合并为一项,它能:( ) A :消去1个表现形式不同的变量,保留相同变量 B :消去2个表现形式不同的变量,保留相同变量 C :消去3个表现形式不同的变量,保留相同变量 表1 D :消去4个表现形式不同的变量,保留相同变量 4、已知真值表如表1所示,则其逻辑表达式为:( ) A :A ⊕B ⊕C B :AB + BC C :AB + BC D :ABC (A+B+C ) 5、函数F(A ,B ,C)=AB+BC+AC 的最小项表达式为:( ) A :F(A,B,C)=∑m (0,2,4) B :F(A,B,C)=∑m (3,5,6,7) C :F(A,B,C)=∑m (0,2,3,4) D :F(A,B,C)=∑m (2,4,6,7) 6、欲将一个移位寄存器中的二进制数乘以(32)10需要( )个移位脉冲。 A :32 B : 10 C :5 D : 6 7、已知74LS138译码器的输入三个使能端(E 1=1,E 2A =E 2B =0)时,地址码A 2A 1A 0=011,则输出Y 7 ~Y 0是:( ) A :11111101 B :10111111 C :11110111 D :11111111 8、要实现n 1n Q Q =+,JK 触发器的J 、K 取值应是:( ) A :J=0,K=0 B :J=0,K=1 C :J=1,K=0 D :J=1,K=1

北京工业大学实验学院2013---2014学年第1学期 数字电子技术I (A)卷课程试卷 适用专业:电子信息工程考试方式:(闭卷)考试时间:2013年12月30日 班级学号: _______________ 姓名:成绩___________ ⑵试题请做在规定处;装订的试卷不得随意拆散,自行拆散成绩以零分记 一、选择题(每小题2分,共20 分) (D )1. N个触发器可以构成最大计数长度为________________ 。 A、N B、2N C、N2 D、2N (C )2.下列几种门电路中,输出端可实现线与功能的电路是__________________ 。 A、传输门 B、异或门 C、OD门 D、三态门 (A )3.下列描述不正确的是_______________ 。 A、时序逻辑电路某一时刻的电路状态取决于电路进入该时刻前所处的状态。 B、寄存器只能存储小量数据,存储器可存储大量数据。 C、主从JK触发器主触发器具有一次翻转性。 D、将移位寄存器首尾相连可构成环形计数器。 (D )4.在四变量卡诺图中,逻辑上不相邻的一组最小项为__________________ 。 A、m 1 与m 3 B、m 4 与m 6 C、m 0 与m 8 D、m 2 与m 8 (D )5.已知逻辑函数Y AB AC BC,与其相等的函数为________________________ 。 A、AB B、AB AC C、AB BC D、AB C (A )6.电路如下图((图中为下降沿JK触发器),触发器当前状态Q3Q2Q1为101 ”, 请问时钟作用下,触发器下一状态为______________ 。 A、“110” B、“100”“010” D、“ 000”

XX大学信息院《数字电子技术基础》 期终考试试题(110分钟)(第一套) 一、填空题:(每空1分,共15分) 1.逻辑函数Y AB C =+的两种标准形式分别为()、 ()。 2.将2004个“1”异或起来得到的结果是()。 3.半导体存储器的结构主要包含三个部分,分别是()、()、()。 4.8位D/A转换器当输入数字量10000000为5v。若只有最低位为高电平,则输出电压为()v;当输入为10001000,则输出电压为()v。 5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。 6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。 二、根据要求作题:(共15分) 1.将逻辑函数P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。 2.图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。 三、分析图3所示电路:(10分) 1)试写出8选1数据选择器的输出函数式; 2)画出A2、A1、A0从000~111连续变化时,Y的波形图; 3)说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。(15分) 五、已知电路及CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。(8分) B C 六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。 (6分) 七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。ROM 中的数据见表1所示。试画出在CP信号连续作用下的D3、D2、D1、D0输出的电压波形,并说明它们和CP信号频率之比。(16分) 表1:

一、 时序逻辑电路与组合逻辑电路不同, 其电路由 组合逻辑电路 和 存储电路(触发器) 两部分组成。 二、描述同步时序电路有三组方程,分别是 驱动方程 、状态方程 和 输 出方程 。 三、时序逻辑电路根据触发器的动作特点不同可分为 同步时序逻辑电路 和 异步时序逻辑电路 两大类。 四、试分析图 T7.5时序电路的逻辑功能,写出电路的驱动方程、状态方程 和输出方程,画出电路的状态转换图和时序图。 解:驱动方程: 00110 1J K J K Q ==== 状态方程: 1001 1 10 10n n Q Q Q Q Q Q Q ++==+ 输出方程: 10Y Q Q = 状态图:功能:同步三进制计数器

五、试用触发器和门电路设计一个同步五进制计数器。 解:采用3个D触发器,用状态000到100构成五进制计数器。 (1)状态转换图 (2)状态真值表 (3)求状态方程

(4)驱动方程 (5)逻辑图(略) [题7.1] 分析图P7.1所示的时序电路的逻辑功能,写出电路驱动方程、状态转移方程和输出方程,画出状态转换图,并说明时序电路是否具有自启动性。 解:触发器的驱动方程 2 0010210 10 21 1 J Q K J Q J Q Q K Q K ====???? ? ? ==??? 触发器的状态方程

1 20 0 1 10 101 1 2 210 n n n Q Q Q Q Q Q Q Q Q Q Q Q + + + = =+ = ? ?? ? ? ?? 输出方程 2 Y Q = 状态转换图如图A7.1所示 所以该电路的功能是:能自启动的五进制加法计数器。 [题7.3] 试分析图P7.3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,并检查电路能否自启动。 解:驱动方程 输出方程 状态方程 状态转换图如图 A7.3所示 01 J X Q =⊕01 K= 10 J X Q =⊕ 1 1 K= 10 () Z X Q Q =⊕? 1 0000010 () n Q J Q K Q X Q Q +=+=⊕ 1 1111101 () n Q J Q K Q X Q Q +=+=⊕?

试题一 气体放电的基本物理过程 一、选择题 1) 流注理论未考虑 的现象。 2) A .碰撞游离 B .表面游离 C .光游离 D .电荷畸变电场 3) 先导通道的形成是以 的出现为特征。 4) A .碰撞游离 B .表面游离 C .热游离 D .光游离 5) 电晕放电是一种 。 6) A .自持放电 B .非自持放电 C .电弧放电 D .均匀场中放电 7) 气体内的各种粒子因高温而动能增加,发生相互碰撞而产生游离的形式称为 。 8) A.碰撞游离 B.光游离 C.热游离 D.表面游离 9) ______型绝缘子具有损坏后“自爆”的特性。 10) A.电工陶瓷 B.钢化玻璃 C.硅橡胶 D.乙丙橡胶 11) 以下哪个不是发生污闪最危险的气象条件 12) A.大雾 B.毛毛雨 C.凝露 D.大雨 13) 污秽等级II 的污湿特征:大气中等污染地区,轻盐碱和炉烟污秽地区,离海岸盐场3km~10km 地区,在污闪季节中潮湿多雾但雨量较少,其线路盐密为 2/cm mg 。 14) A.≤ B.>~ C.>~ D.>~ 15) 以下哪种材料具有憎水性 16) A. 硅橡胶 B.电瓷 C. 玻璃 D 金属 二、填空题 17) 气体放电的主要形式: 、 、 、 、 18) 根据巴申定律,在某一PS 值下,击穿电压存在 值。 19) 在极不均匀电场中,空气湿度增加,空气间隙击穿电压 。 20) 流注理论认为,碰撞游离和 是形成自持放电的主要因素。 21) 工程实际中,常用棒-板或 电极结构研究极不均匀电场下的击穿特性。 22) 气体中带电质子的消失有 、复合、附着效应等几种形式 23) 对支持绝缘子,加均压环能提高闪络电压的原因是 。 24) 沿面放电就是沿着 表面气体中发生的放电。 25) 标准参考大气条件为:温度C t 200 ,压力 0b kPa ,绝对湿度30/11m g h 26) 越易吸湿的固体,沿面闪络电压就越______ 27) 等值盐密法是把绝缘子表面的污秽密度按照其导电性转化为单位面积上________含量 的一种方法

试题C 一、选择题(从每小题的四个备选答案中,选出一个正确答案,并将其号码填在括号内, 每小题2分,共20分) 1.将十进制数(18)10转换成八进制数是[ ] ①20 ②22 ③21 ④23 2. 三变量函数 ()BC A C B A F+ = , ,的最小项表示中不含下列哪项[ ] ①m2 ②m5 ③m3 ④m7 3.一片64k×8存储容量的只读存储器(ROM),有[ ] ①64条地址线和8条数据线②64条地址线和16条数据线 ③16条地址线和8条数据线④16条地址线和16条数据线 4.下列关于TTL与非门的输出电阻描述中,正确的是[ ] ①门开态时输出电阻比关态时大②两种状态都是无穷大输出电阻 ③门关态时输出电阻比开态时大④两种状态都没有输出电阻 5.以下各种ADC中,转换速度最慢的是[ ] ①并联比较型②逐次逼进型 ③双积分型④以上各型速度相同 6. 关于PAL器件与或阵列说法正确的是[ ] ①只有与阵列可编程②都是可编程的 ③只有或阵列可编程④都是不可编程的 7. 当三态门输出高阻状态时,输出电阻为[ ] ①无穷大②约100欧姆 ③无穷小④约10欧姆 8.通常DAC中的输出端运算放大器作用是[ ] ①倒相②放大 ③积分④求和 9. 16个触发器构成计数器,该计数器可能的最大计数模值是[ ] ①16 ②32 ③162④216 10.一个64选1的数据选择器有()个选择控制信号输入端。[ ]

① 6 ② 16 ③ 32 ④ 64 二、填空题(把正确的内容填在题后的括号内。每空1分,共15分。) 1.已知一个四变量的逻辑函数的标准最小项表示为 ()()13,11,9,8,6,4,3,2,0,,,m d c b a F ∑=,那么用最小项标 准表示=* F ,以及=F ,使用最大项 标准表示=F ,以及 =F 。 2.具有典型实用意义的可编程逻辑器件包括 , , , 。 3.为了构成4K ×16bit 的RAM ,需要 块1K ×8bit 的RAM ,地址线的 高 位作为地址译码的输入,地址译码使用的是 译码器。 4.在AD 的量化中,最小量化单位为Δ,如果使用四舍五入法,最大量化误差为 Δ,如果使用舍去小数法,最大量化误差为 Δ。 5.如果用J-K 触发器来实现T 触发器功能,则T,J,K 三者关系为 ;如果要用J-K 触发器来实现D 触发器功能,则D,J,K 三者关系为 。 三、 简答题(每小题5分,共10分) 1.用基本公式和定理证明下列等式: ()ABC BC A C AB B C AB ++=+ 2.给出J-K 触发器的特征方程,状态转移真值表,状态转移图。 四、 分析题(25分) 1.8选1数据选择器CC4512的逻辑功能如表4.1所示。试写出图4.1所示电路输出端 F 的最简与或形式的表达式。(9分) 表4.1 CC4512功能表 2. 如图4.2电路由CMOS 传输门构成。试写出输出端的逻辑表达式。(8分)

数字电子技术基础考题 」、填空题:(每空3分,共15分) 辑表达式 )和( 卡诺图 路,称为全加器。 等° 17. 根据不同需要,在集成计数器芯片的基础上,通过采用 进位输出置最小数法 等方法可以实现任意进制的技术器。 18. 4. 一个JK 触发器有_2_个稳态,它可存储_J — 位二进制数。 19. 若将一个正弦波电压信号转换成 同一频率的矩形波,应采用 多谐振荡器 _______ 电路。 20. __________________________________________ 把JK 触发器改成T 触发器的方法是J=k=t __________________________________________________ 。 21. N 个触发器组成的计数器最多可以组成 _^n 进制的计数 器。 1逻辑函数有四种表示方法,它们分别是( 真值表 )、( 逻辑图 2. 将2004个“ 1 ”异或起来得到的结果是( 3. 由555定时器构成的三种电路中, )和( 是脉冲的整形电路。 4. TTL 器件输入脚悬空相当于输入( 电平。 5. 基本逻辑运算有:(and not )和(or )运算。 6. 采用四位比较器对两个四位数比较时, 先比较 最咼 位。 7. 触发器按动作特点可分为基本型、 (同步型 主从型 )和边沿型; 如果要把一宽脉冲变换为窄脉冲应采用 积分型单稳态 触发器 9. 目前我们所学的双极型集成电路和单极型集成电路的典型电路分别是 TTL )电路和 CMOS )电路。 10. 施密特触发器有( 2 )个稳定状态?,多谐振荡器有(0 )个稳定状态。 11.数字系统按组成方式可分为 功能扩展电路、功能综合电路 两种; 12?两二进制数相加时,不考虑低位的进位信号是 加器。 13?不仅考虑两个 本位 .相加,而且还考虑来自 低位进位 _______ 相加的运算电 14.时序逻辑电路的输出不仅和 该时刻输入变量的取值 有关,而且还与_电路原来 的状态 有关。 15?计数器按CP 脉冲的输入方式可分为 同步计数器和 异步计数器。 16?触发器根据逻辑功能的不同,可分为 rs jk 反馈归零法 置数法

考试试题纸(A卷) 课程名称数字电子技术基础专业班级 题号一二三四五六七八九十总分 题分16 12 12 12 12 12 12 12 备注: 学生不得在试题纸上答题(含填空题、选择题等客观题) 一、填空题(每空1分,共16分) 1.将十进制数63.75分别转换为二进制、八进制、十六进制和8421BCD码,则有(63.75)D=()B=()O =()H=()8421BCD。 2.已知某函数F AB BC =+,该函数的反函数F=(),对偶函数'F=()。 3.函数F AB BC =+在输入变量取值为()时可能出现竞争与冒险,若将表达式变换为 F=()则可消除竞争与冒险。 4.相对于CMOS电路,TTL电路的最主要优点是()。 5.有一八位“R-2R”T型电阻网络DAC,已知REF U=10V,当输入10000000时输出的电压值为()V。 6.容量为1K×8的ROM存储器需要()根地址线,()根数据线,需要由()片容量为256×4的ROM构成。 7.多谐振荡器、单稳态触发器及施密特触发器分别有()、()及()个稳态。 二、化简(每小题6分,共12分) 1.用代数法化简:F A B ABC A(B AB) =?+++ 2.用卡诺图法化简:Y(A,B,C,D)=(0,2,3,4,6,12)(1,7,8,10,14,15) ∑+∑ m d 三、写输出的逻辑表达式(每小题4分,共12分) 1.2. & & & A B C F1 +V CC 1 1 CS CS A B C F2

74LS290集成二-五-十进制计数器功能表 R 0(1) R 0(2) R 9(1) R 9(2) CP Q A Q B Q C Q D 1 1 0 X X 0 0 0 0 1 1 X 0 X 0 0 0 0 0 0 0 1 X 1 1 0 X X ↓ 计 数 0 X X 0 ↓ 计 数 X 0 0 X ↓ 计 数 X 0 X 0 ↓ 计 数 74LS151八选一数据选择器功能表 G A 2 A 1 A 0 Y 1 X X X 0 0 0 0 0 D 0 0 0 0 1 D 1 0 0 1 0 D 2 0 0 1 1 D 3 0 1 0 0 D 4 0 1 0 1 D 5 0 1 1 0 D 6 0 1 1 1 D 7 CP Q A Q B Q C Q D R 9(1) R 9(2) R 0(1) R 0(2) A 2 A 1 A 0 D 0 D 1 D 2 D 3 D 4 D 5 D 6D 7 & CP A CP B CP Y G “1” 74LS290 74LS151 Y

C. 000 D. 1 0 1 A. A+B B. A+C C. (A+B ) (A+C ) D. B+C 标准答案及评分标准 适用专业(班级): 是否可携带(填写计算器、词典等):计算器 学科部主任: 一 ?选择题(每小题2分,共20分) 1?一位8421BCD 码译码器的数据输入线与译码输出线的组合是 【C 】 A. 4:6 B.1:10 C.4:10 D.2:4 2 ?若输入变量 A 、B 全为1时,输出F=1,则其输入与输出的关系是 【B 】 A.异或 B. 同或 C. 或非 D. 与或 3?在下列逻辑电路中,不是组合逻辑电路的是 【D 】 A.译码器 B. 加法器 C. 编码器 D. 寄存器 6 ?同步计数器和异步计数器比较,同步计数器的最显著优点是 A 工作速度高 B.触发器利用率高 C.电路简单 D.不受时钟CP 控制 7?—位8421BCD 码译码器的数据输入线与译码输出线的组合是 A. 4:6 B.1:10 C.4:10 D.2:4 8 ?组合逻辑电路通常由【 】组合而成。 A.触发器 B.门电路 C.计数器 D.锁存器 A. 1 11 B. 010 10.逻辑表达式 A+BC= 课程名称:数字电路 课程归属:理工学科部 开卷、闭卷:闭卷 出卷人: 4 . 一个8选一的数据选择器,其地址输入 (选择控制输入)端的个数是 A. 4 B. 2 C. 3 5?最小项ABCD 的逻辑相邻最小项是 D. 1 6 【A 】 A. ABCD B . ABCD C. ABCD D. ABCD 9.8线一3线优先编码器的输入为 I0 —17,当优先级别最高的 I7有效时,其输出 的值是 【C 】

重庆大学《数字电子技术(Ⅱ)》课程 试卷 A卷 B卷 2012 ~2013 学年第 2 学期 开课学院:电气工程学院课程号:考试日期: 2013-6 考试方式: 开卷闭卷 其他考试时间: 120 分钟 一、设计题(20分): 采用同步置数的方式,利用74LS160设计365进制的计数器,各位之间为十进制关系。 解: 二、分析题(20分): 下图为16×4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。在CLK信号作用下,输出波形如 图所示。计算ROM中的数据表。 解: 三、设计题(10分): 用D触发器设计一个同步串行数据检测电路,当连续输入3个或3个以上1时,电路的输出为1,其它情况下输 出为0。例如: 输入A 101100111011110 输出Y 000000001000110 解:1)画出原始状态图 2)状态化简 3)状态编码 原始状态图化简以后的状态图 1/0 A/Y 0/0 1/0 0/0

由状态图可得到复合卡诺图图: n AQ Y 1 = n n n n n n Q Q A Q AQ AQ Q 0 110 1011?=+=++ D 触发器的特性方程为1,01 ==+i D Q i n i 得: n n n n Q Q A D AQ AQ D 010101?=+= 5) 检查自启动: 可以自启动。 6)画逻辑图 四、分析题(10分): 试分析下图时序电路的功能。 解: 1)) () () (2 10120111 0210↓=↓=↓?=+++CP Q Q Q Q Q Q Q CP Q Q Q n n n n n n n n n 2) 画出波形图:(略) 3) 画出状态图 异步五进制加法计数器 1D Q FF 1 C1 & CP A Y 1D Q FF 0 C1 ≥1 11 011 00 1/1 0/0 11+n Q 的卡诺图 n n Q Q 01 00 01 11 10 A 0 0 0 ╳ 0 1 0 1 ╳ 1 n n Q Q 01 00 01 11 10 A 0 0 0 ╳ 0 1 1 ╳ 10+n Q 的卡诺图 二进制状态图 00 01 10 1/0 A/Y 1/0 1/1 0/0 0/0 0/0 复合卡诺图 n n Q Q 01 00 01 11 10 A 0 00 0 00 0 ╳ 00 0 1 01 0 10 0 ╳ 10 1 n n Q Q 0 1 00 01 11 10 A 0 0 0 ╳ 0 1 0 ╳ 1 输出Y 的卡诺图 000 /0 001 010 011 100 111 110 101 /0 /0 /0 /1 /1 /1 /1