主从JK触发器设计同步计数器

- 格式:doc

- 大小:151.50 KB

- 文档页数:13

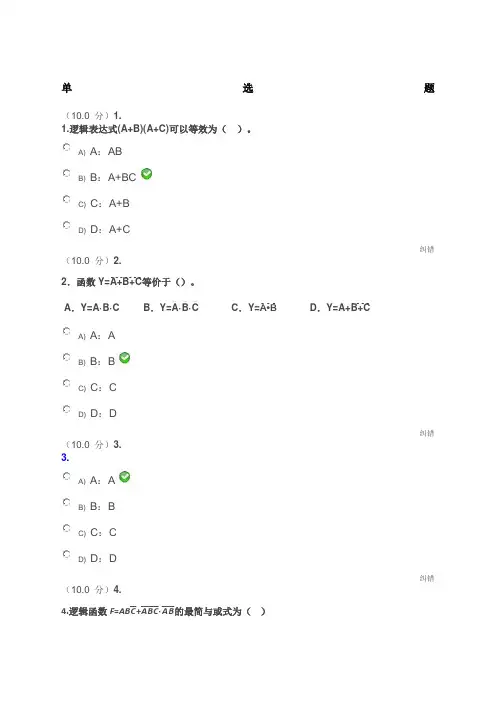

期末考试试卷(A)卷课程名称:适用年级/专业:试卷类别开卷()闭卷(√)学历层次本科考试用时120分钟《考生注意:答案要全部抄到答题纸上,做在试卷上不给分》...........................一、填空题(每空2分,共20分)1.逻辑代数中三个最基本的运算是①、②和③。

2.逻辑函数F=A+B+C D的反函数F= ①,对偶式为②。

3.D触发器的特征方程为①,JK触发器的特征方程为②。

4. 型触发器克服了空翻现象。

5.构造一个模10计数器需要①个状态,②个触发器。

二、单项选择(每小题2分,共20分)(A)1、最小项AB C D的逻辑相邻最小项是A. ABC DB. ABC DC. ABC DD.A BC D()2、若所设计的编码器是将31 个一般信号转换成二进制代码,则输出应是一组N=(C )位的二进制代码。

A.3 B. 4 C. 5 D. 6(A)3、时序逻辑电路中一定是含A. 触发器B. 组合逻辑电路C. 移位寄存器D. 译码器(D )4、在何种输入情况下,“或非”运算的结果是逻辑0。

A.全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为1(B )5、同步时序逻电路和异步时序逻电路比较,其差别在于后者A.没有触发器B. 没有统一的时钟脉冲控制C .没有稳定状态 D. 输出只与内部状态有关()6、某移位寄存器的时钟脉冲频率为100KH Z,欲将存放在该寄存器中的数左移8位,完成该操作需要()时间。

A.10μSB.80μSC.100μSD.800ms(D )7、没有置0功能的触发器是A.RS-FFB.JK-FFC.D-FFD.T-FF( )8、一个4位二进制同步加法计数器用作分频器时,若计数脉冲的频率为=CPf160KHZ ,现需要20KHZ 的信号,取自A 、0Q 端的信号 B 、1Q 端的信号;C 、2Q 端的信号 D 、3Q 端的信号( D )9、为实现将D 触发器转换为T 触发器,图(一)的虚框内应是A. 或非门B. 与非门C. 异或门D. 同或门 图一( D )10、以下表达式中符合逻辑运算法则的是 A.C ·C=C 2 B.1+1=10 C.0<1 D.A+1=1三、证明与化简:(每小题5分,共15分)1、用公式法证明等式A B A B A AB +++B=1成立。

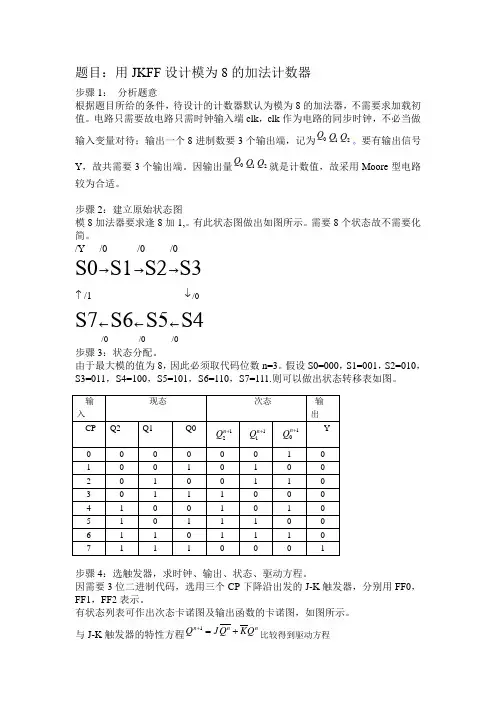

题目:用JKFF 设计模为8的加法计数器步骤1: 分析题意 根据题目所给的条件,待设计的计数器默认为模为8的加法器,不需要求加载初值。

电路只需要故电路只需时钟输入端clk ,clk 作为电路的同步时钟,不必当做输入变量对待;输出一个8进制数要3个输出端,记为0Q 1Q 2Q 。

要有输出信号Y ,故共需要3个输出端。

因输出量0Q 1Q 2Q 就是计数值,故采用Moore 型电路较为合适。

步骤2:建立原始状态图 模8加法器要求逢8加1,。

有此状态图做出如图所示。

需要8个状态故不需要化简。

/Y /0 /0 /0S0→S1→S2→S3 ↑/1 ↓/0 S7←S6←S5←S4/0 /0 /0步骤3:状态分配。

由于最大模的值为8,因此必须取代码位数n=3。

假设S0=000,S1=001,S2=010,S3=011,S4=100,S5=101,S6=110,S7=111.则可以做出状态转移表如图。

步骤4:选触发器,求时钟、输出、状态、驱动方程。

因需要3位二进制代码,选用三个CP 下降沿出发的J-K 触发器,分别用FF0,FF1,FF2表示。

有状态列表可作出次态卡诺图及输出函数的卡诺图,如图所示。

与J-K 触发器的特性方程nn n QK Q J Q+=+1比较得到驱动方程输入 现态 次态输 出CP Q2 Q1 Q0 12+n Q11+n Q1+n QY 0 0 0 0 0 0 1 0 1 0 0 1 0 1 0 0 2 0 1 0 0 1 1 0 3 0 1 1 1 0 0 0 4 1 0 0 1 0 1 0 5 1 0 1 1 1 0 0 6 1 1 0 1 1 1 0 71111nn Q Q 01=+10=J 10=Knn n n n Q Q Q Q Q 101011+=+ nQ J 01=nQ K 01=nn n n n n n n Q Q Q Q Q Q Q Q 122012012++=+nn n Q Q Q Y 210=nnQ Q K J 1022==步骤5:画出逻辑电路图nQ 0nnQ Q 1200 01 11 100 1 1 1 1 1nQ 0nnQ Q 1200 01 11 100 0 1 1 0 11nQ 0nn Q Q 120001 11100 0 0 1 1111nQ 0nnQ Q 12000111100 0 0 0 0 11。

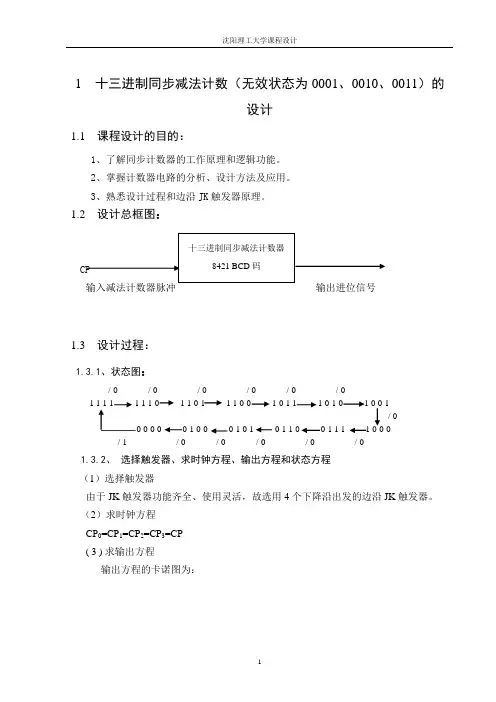

1 十三进制同步减法计数(无效状态为0001、0010、0011)的设计1.1 课程设计的目的:1、了解同步计数器的工作原理和逻辑功能。

2、掌握计数器电路的分析、设计方法及应用。

3、熟悉设计过程和边沿JK 触发器原理。

1.2 设计总框图:CP输入减法计数器脉冲 输出进位信号1.3 设计过程:1.3.1、状态图:/0 /0 /0 /0 /0 /0 1111 1110 1101 1100 1011 1010 1001/00000 0100 0101 0110 0111 1000/1 /0 /0 /0 /0 /01.3.2、选择触发器、求时钟方程、输出方程和状态方程(1)选择触发器由于JK 触发器功能齐全、使用灵活,故选用4个下降沿出发的边沿JK 触发器。

(2)求时钟方程 CP 0=CP 1=CP 2=CP 3=CP (3)求输出方程输出方程的卡诺图为:十三进制同步减法计数器8421 BCD 码00 01 11 1000011110输出方程: Y =Q n3Q n2(4)状态方程:次态卡诺图:00 01 11 1000011110所以:Q3n+1 的卡诺图为:00 01 11 10000111101 ×××0 0 0 00 0 0 00 0 0 01111 ××××××××××××0000 0001 0110 01011011 1100 1110 11010111 1000 1010 10011 ×××0 0 0 01 1 1 10 1 1 1Q 2n+1的卡诺图为:00 01 11 1000 01 11 10Q 1n+1的卡诺图为:00 01 11 1000 01 11 10Q 0n+1 的卡诺图为:00 01 11 1000 01 11 10状态方程:Q 3n+1= Q n 3Q n 2 + Q n 3Q n 0 + Q n 3Q n 1+ Q ——n 3Q _——n 2=Q ——n 3Q _——n 2 + (Q n 0+Q n 1+Q n 2)Q n 3 Q 2n+1=Q ——n 2Q ——n 1Q ——n 0+ (Q n 0+Q n 1)Q n 3Q 1n+1=Q ——n1Q ——n 0Q n 3 + Qn1Q n 0 +Q ——n1Q ——n3Q _——n 2Q 0n+1 =Q ——n 0(Q n 3+Q n 1+Q ——n 2)1 × × × 0 1 1 1 0 1 1 1 11 × × × 0 0 1 0 1 0 1 0 111 × × × 0 0 0 1 1 0 0 1 11驱动方程为:J3=Q_——n2 K3=Q_——2Q——0Q——1J2=Q——n1Q——n0 K2=Q——n1Q——n0J1==Q——n0Q n2 Q n2Q——n3Q——n0Q n3 K1=Q——n0J0=Q n1Q n2Q n3K0=1(6) 检验能否自启动(无效状态0001,0010,0011)0011 0010 10010001 1010所以能自启动1.4逻辑接线图:1.5 电路接线图1.6实验仪器74LS112芯片2块,74LS08芯片1块74LS00芯片2块开关导线若干1.7实验结论(分析实验中出现的故障及产生的原因)实验正常,个芯片运行正常。

同步计数器的设计实验报告同步计数器的设计实验报告篇一:实验六同步计数器的设计实验报告实验六同步计数器的设计学号:姓名:一、实验目的和要求1.熟悉JK触发器的逻辑功能。

2.掌握用JK触发器设计同步计数器。

二、实验仪器及器件三、实验预习1、复习时序逻辑电路设计方法。

⑴逻辑抽象,得出电路的状态转换图或状态转换表①分析给定的逻辑问题,确定输入变量、输出变量以及电路的状态数。

通常都是取原因(或条件)作为输入逻辑变量,取结果作输出逻辑变量。

②定义输入、输出逻辑状态和每个电路状态的含意,并将电路状态顺序编号。

③按照题意列出电路的状态转换表或画出电路的状态转换图。

通过以上步骤将给定的逻辑问题抽象成时序逻辑函数。

⑵状态化简①等价状态:在相同的输入下有相同的输出,并且转换到同一次态的两个状态。

②合并等价状态,使电路的状态数最少。

⑶状态分配①确定触发器的数目n。

因为n个触发器共有2n种状态组合,所以为获得时序电路所需的M个状态,必须取2n1<M2n②给每个电路状态规定对应的触发器状态组合。

⑷选定触发器类型,求出电路的状态方程、驱动方程和输出方程①根据器件的供应情况与系统中触发器种类尽量少的原则谨慎选择使用的触发器类型。

②根据状态转换图(或状态转换表)和选定的状态编码、触发器的类型,即可写出电路的状态方程、驱动方程和输出方程。

⑸根据得到的方程式画出逻辑图⑹检查设计的电路能否自启动①电路开始工作时通过预置数将电路设置成有效状态的一种。

②通过修改逻辑设计加以解决。

⑺设计步骤简图图3 设计步骤简图2、按实验内容设计逻辑电路画出逻辑图。

设计思路详情见第六部分。

电路图如下:四、实验原理1.计数器的工作原理递增计数器----每来一个CP,触发器的组成状态按二进制代码规律增加。

递减计数器-----按二进制代码规律减少。

双向计数器-----可增可减,由控制端来决定。

2.集成J-K触发器74LS73⑴符号:图1 J-K触发器符号⑵功能:表1 J-K触发器功能表⑶状态转换图:图2 J-K触发器状态转换图⑷特性方程:Qn1JQnKQn⑸注意事项:①在J-K触发器中,凡是要求接“1”的,一定要接高电平(例如5V),否则会出现错误的翻转。

Verilog HDL实验报告Verilog 实验报告题目:JK触发器、同步计数器系部名称:通信工程专业名称:通信工程班级:班内序号:学生姓名:时间:2010.11.28一、实验内容:用JK触发器构成同步计数器:设计一个同步计数器,其逻辑图和JK触发器的逻辑图所示。

清零信号clear低电平有效,输入数据在时钟信号clock的上升沿被锁存,触发器在clock的下降沿输出,当count_enable信号为低电平时停止计数。

写出同步计数器的verilog描述和激励模块,在激励模块中使用clear和count_enable对计数器进行测试,并显示输出计数Q[3:0]。

二、实验原理图:JK触发器构成同步计数器源代码://主模块module synchronous_counter(clear,clock,count_enable,Q);input clear,clock,count_enable;output [3:0] Q;wire qbar1,qbar2,qbar3,qbar0;wire a,b,c;assign a = Q[0] & count_enable;assign b = a & Q[1];assign c = b & Q[2];JK_flip_flop myJK(count_enable,count_enable,clock,clear,Q[0],qbar0);JK_flip_flop myJK1(a,a,clock,clear,Q[1],qbar1);JK_flip_flop myJK2(b,b,clock,clear,Q[2],qbar2);JK_flip_flop myJK3(c,c,clock,clear,Q[3],qbar3);endmodule//调用的JK触发器模块module JK_flip_flop(j,k,clock,clear,q,qbar);input j,k,clock,clear;output q,qbar;wire a,b,y,ybar,c,cbar,d,q,qbar;assign a = ~ (((qbar & j)& clock) & clear);assign b = ~ ((clock & k) & q);assign y = ~ (a & ybar);assign ybar = ~ ((y & clear) & b);assign c = ~(y & cbar);assign cbar = ~ clock;assign d = ~ (cbar & ybar);assign q = ~ (c & qbar);assign qbar = ~ ((q & clear) & d);endmodule测试文件源代码:module count_test;reg count_enable=1,clock=0,clear=0;wire [3:0]Q;synchronous_counter myCount(clear,clock,count_enable,Q);initial #10 clear=1;always@(negedge clock)begin$monitor($time," clear=%b,count_enable=%b,Q=%b%b%b%b\n",clear,count_enable,Q[3],Q[2],Q[1],Q[0]);endalways clock = #5 ~clock;always count_enable= #170 ~count_enable; endmodule实验结果:波形图:三、实验心得:这次实验比上一次顺利多了,可能是因为有了前一次的铺垫,我对软件的熟悉度有了一定的提高。

长沙学院课程设计说明书题目同步五进制加法计数器系(部) 电子与通信工程专业(班级) 电气工程及其自动化姓名黄明发学号***********指导教师瞿瞾起止日期 5.21-5.25数字电子技术课程设计任务书(5)系(部):电子与通信工程系专业:电气工程及其自动化指导教师:瞿曌长沙学院课程设计鉴定表目录课程设计的目的 (4)课程设计内容及要求 (4)课程设计原理 (4)课程设计方案步骤 (4)建立状态图 (5)建立状态表 (5)状态图化简、分配,建立卡诺图 (5)确定状态方程以及激励方程 (5)绘制逻辑图,检查自启动能力 (6)绘制逻辑电路图并仿真 (6)观察时序电路逻辑分析仪,调节频率 (6)课程设计的思考与疑问 (7)课程设计总结 (8)参考文献 (8)其主要目的是通过本课程,培养、启发学生的创造性思维,进一步理解数字系统的概念,掌握小型数字系统的设计方法,掌握小型数字系统的组装和调试技术,掌握查阅有关资料的技能。

课程设计内容及要求设计一个小型数字电子系统——同步五进制加法计数器电路。

试用触发器设计一个同步五进制加法计数器。

应检查是否具有自启动能力。

设置一个复位按钮和一个启动按钮。

采用数码管显示计数器的数值。

课程设计原理计数器对时钟脉冲进行计数,每来一次上升沿时钟脉冲,计数器状态改变一次,每五个时钟脉冲完成一个计数周期。

原理图如A-1示,信号源同时接入三个D 触发器(74LS74N )的,开关键1J 作为启动按钮和暂停按钮,开关键3J 则作为复位键,即数据清零按钮。

各驱动点210D D D 由三个D 触发器输出端Q 的组合驱动。

nnQ Q 10驱动触发器D0,nnQ Q 10 驱动触发器D1,01Q Q 则驱动触发器D2。

三个触发器的输出端都连接到数码管的接口上,信号源截一开关启动,PR 端接一双键开关用来复位清零。

同步五进制加法计数器图A-1建立状态表无进制计数器共有5个状态,需要3个触发器构成,按照状态图,写出加法计数器的状态表,如图加法计数器状态表A-3状态图化简、分配,建立卡诺图D2的卡诺图B-3确定状态方程以及激励方程nn Q Q D 100==1+n Q …………………………①)(101nnQ Q D ⊕==11+n Q ……………………②nn Q Q D 012==12+n Q …………………………③绘制逻辑图,检查自启动能力三个触发器有823=种情况,那么检验5、6、7是否能进入自启动的循环状态图中,将5、6、7的BCD 码带入激励方程中,看能否进入循环圈内,分析如下:5——101 代入方程 Q0=0 Q1=1 Q2=0 那么上升沿脉冲后为 010 6——110 代入方程 Q0=0 Q1=1 Q2=0 那么上升沿脉冲后为 010 7——111代入方程Q0=0Q1=0Q2=1那么上升沿脉冲后为 100由此可知,此计数器具有自启动功能,所以可以绘制逻辑电路图了;若是,代入激励方程后,不能进入循环状态图中,那么就得改变卡诺图中,取任意状态的5、6、7的状态值,重新书写激励方程,知道能够自启动为止。

数字电路第四章答案【篇一:数字电路答案第四章时序逻辑电路2】p=1,输入信号d被封锁,锁存器的输出状态保持不变;当锁存命令cp=0,锁存器输出q?d,q=d;当锁存命令cp出现上升沿,输入信号d被封锁。

根据上述分析,画出锁存器输出q及 q的波形如习题4.3图(c)所示。

习题4.4 习题图4.4是作用于某主从jk触发器cp、j、k、 rd及 sd 端的信号波形图,试绘出q端的波形图。

解:主从jk触发器的 rd、且为低有效。

只有当rd?sd?1 sd端为异步清零和复位端,时,在cp下降沿的作用下,j、k决定输出q状态的变化。

q端的波形如习题4.4图所示。

习题4.5 习题4.5图(a)是由一个主从jk触发器及三个非门构成的“冲息电路”,习题4.5图(b)是时钟cp的波形,假定触发器及各个门的平均延迟时间都是10ns,试绘出输出f的波形。

cpf cp100ns10nsq(a)f30ns10ns(b)(c)习题4.5图解:由习题4.5图(a)所示的电路连接可知:sd?j?k?1,rd?f。

当rd?1时,在cp下降沿的作用下,且经过10 ns,状态q发生翻转,再经过30ns,f发生状态的改变,f?q。

rd?0时,经过10ns,状态q=0。

根据上述对电路功能的分析,得到q和f的波形如习题4.5图(c)所示。

习题4.6 习题4.6图(a)是一个1检出电路,图(b)是cp及j端的输入波形图,试绘出 rd端及q端的波形图(注:触发器是主从触发器,分析时序逻辑图时,要注意cp=1时主触发器的存储作用)。

cpj(a)qd(c)cp j(b)习题图解:分析习题4.6图(a)的电路连接:sd?1,k?0,rd?cp?q;分段分析习题4.6图(b)所示cp及j端信号波形。

(1)cp=1时,设q端初态为0,则rd?1。

j信号出现一次1信号,即一次变化的干扰,且k=0,此时q端状态不会改变;(2)cp下降沿到来,q端状态变为1,rd?cp,此时cp=0,异步清零信号无效;(3)cp出现上升沿,产生异步清零信号,使q由1变为0,在很短的时间里 rd又恢复到1;(4)同理,在第2个cp=1期间,由于j信号出现1信号,在cp下降沿以及上升沿到来后,电路q端和 rd端的变化与(2)、(3)过程的分析相同,其波形如习题4.6图(c)所示。

verilog 三进制计数器设计每输入三个时钟信号,输出一个进位信号(JK触发器主要用来保持,翻转等作用)利用上边沿JK触发器和门电路组成三进制计数器(Q1,Q0),进位信号为COJK触发器:具有置0、置1、保持和翻转功能,通过控制输入信号J,K的不同来实现不同的功能首先设计JK触发器,描述其功能module jkcfq(Q,J,CLK,RD);iuput J,K,CLK,RD;//输入信号J,K,时钟信号CLK,复位信号RD(低电平有效)output Q;//输出为Qreg Q;//把输出定义为寄存器变量always @(posedge CLK or negedge RD)//只要时钟上升沿来了或者复位信号来了,执行下面语句beginif (!RD)//判断是否为复位信号Q <= 1'b0;elsecase({J,K})//J,K触发器的功能选择,通过JK的值来选择2'b00:Q <= Q;//保持2'b00:Q <= 1'b0; //置02'b00:Q <= 1'b1; //置12'b00:Q <= ~Q; //翻转default : Q <=1'bx;//高阻态endcaseendendmodule设计顶层的计数模块module count3(Q1,Q0,CO,CLK,CR)ouput Q1,Q0,CO;//输出信号Q1,Q0,进位输出信号COinput CLK,CR;//输入时钟信号CLK,输入复位信号CRwire CR,Q1F,Q0F,CLKF;定义四根线,其中复位信号为wire类型wire VCC,GND;//定义电源线和接地线assign VCC = 1;//给电源线和接地线赋值assign GND = 0;//调用JK触发器jkcfq u1(.Q(Q0),.J(Q1F),.K(VCC),.CLK(CLK),.RD(CR));/*第一个JK触发器,输出Q端和顶层输出Q0端相连,j端和线Q1F相连,K端和VCC相连,即接高电平,CLK和系统时钟相连,复位端和复位端连*/jkcfq u2(.Q(Q1),.J(Q0),.K(VCC),.CLK(CLK),.RD(CR));/*第二个JK触发器,输出Q端和顶层输出Q1端相连,j端和顶层输出Q0相连,K端和VCC 相连,即接高电平,CLK和系统时钟相连,复位端和复位端连*/not u4(Q1F,Q1);//将输入的Q1取反赋给线Q1Fnot u5(Q0F,Q0);//将输入的Q0取反赋给线Q0Fnot u3(CLKF,CLK);//将系统的时钟信号取反赋给线CLKFnand u6(CO,Q1,QOF,CLKF);//输出进位CO的值为输入Q1和线Q0F,CLKF的与非值endmodule。

毕业设计论文同步八进制加法计数器吴彬指导老师姓名: 张睿专业名称:微电子技术班级学号: 08138110论文提交日期:2010年11月21日论文答辩日期:2010年11月17日2010年11月 21 日摘要计数器是数字系统中应用最广泛的时序逻辑部件之一,所谓计数器就是计算输入脉冲的个数。

本设计是在LINUX环境下采用Cadence软件对同步八进制加法计数器进行芯片原理图设计、输入、仿真以及版图设计、DRC验证和LVS验证。

【关键词】:计数器版图设计 DRC LVSAbstractCounter is a digital system,the most widely used one of sequential logic components,the so-called counter is to calculate the number of input pulses. This design is used in LINUX Cadence software environment,synchronous counter chip octal addition schematic design entry, simulation and layout, DRC and LVS verification verification.【Key words】Counter Layout design Design Rule Check Layout Versus Schematic目录绪论 (1)第一章 Cadence软件介绍 (2)1.1Cadence软件简介 (2)第二章同步八进制加法计数器原理图 (3)2.1同步八进制加法计数器原理图设计过程 (3)2。

2 D触发器原理图设计 (4)2.3 JK触发器原理图设计 (5)2。

3 同步八进制加法计数器原理 (5)第三章原理图仿真 (6)3。

1 D触发器仿真波形图 (6)3。

《数字逻辑实验报告》学号:139074131姓名:吴桂春班级:计134班指导老师:申元霞日期:2018.6.10实验一名称: 3-8译码设计一、实验任务设计一个3-8译码器。

二、实验原理1、列出真值表、写出逻辑函数三、实验原理图:三八译码器由三个输入端编码,输出有八个输出端。

用与门以及非门通过“导线”连接而成。

四、实验步骤:1)打开软件max+plus2,建立新目标文件开始画图。

并保存原图,设置工程指向。

2)选择芯片类型本实验选择EPF10K10LC84-3芯片3)编译配置4)时序仿真:由仿真结果可以看出,本实验仿真成功。

五、实验结果六、实验分析1、结合本次实验,简述原理图输入法设计组合电路的步骤。

设计输入原理图→电路的编译与适配→电路仿真与时序分析→管脚的重新分配与定位→器件的下载编程与硬件实现2、时序仿真波形中,输出波形与输入波形是否同步变化?如何解释输出波形中存在的毛刺?不完全同步变化,存在延迟。

3、连线时,线条不能连接到器件内部,否则会出现编译错误。

同时,添加激励脉冲时a,b,c分别为2倍的关系。

加错激励信号结果也将不正确。

b5E2RGbCAP实验二名称:全加全减器设计一、实验任务设计并实现一个一位全加全减器。

二、实验原理图1.列出真值表、写出逻辑函数。

a,b,c为三个输入端,分别输入0或者1,m为控制端当m=1是全减器,m=0时是全加器,输出端s表示结果,y代表进位或借位。

p1EanqFDPw三、实验步骤:1)打开软件max+plus2,建立新目标文件开始画图。

并保存原图,设置工程指向。

2)选择芯片类型本实验选择EPF10K10LC84-3芯片3)编译配置4)时序仿真:由仿真结果可以看出,全加全减器仿真成功。

实验三名称:七段显示译码器一、实验任务设计并实现一个七段显示译码器。

二、实验原理图1. 列出真值表、写出逻辑函数8421BCD输入代码数字A3A2A1A0a b c d e f g 000000000010 000110011111 001000100102 001100001103 010********* 010*********011011000006011100011117 100000000008 1001000010092、数字显示是由0—9共有十个数字所以有四个输入端,输出端分别编码为a—g,每一个字母代表一个笔画。

文档编号:WX_HW_0003文档分类:硬件技术文档(AA.硬件设计技术文档主从JK触发器设计同步计数器方案Version 1.1目录目录 21.概述 32.总体描述 32.1.功能描述 32.2.顶层框图 32.3.引脚描述 42.4.接口时序 43.模块划分 53.1 概述(叙述一下划分的几个大的模块) 53.2模块A 53.2.1功能定义 53.2.2信号描述 63.2.3时序描述(包含必要的时序图以及文字说明) 63.2.3 祥细设计 63.3模块B 73.4模块C 8……错误!未定义书签。

4.模块分述(设计比较复杂的时候,根据需要对模块进行细化说明,需要加上模块分述这一部分。

)84.1模块A 84.1.1.模块A_1(这部分的内容与模块化分中模块的说明相同)错误!未定义书签。

4.2.2模块A_2 错误!未定义书签。

4.2模块B 84.3模块C 85.验证方案96.测试方案127.设计开发环境128.设计开发计划121.概述本设计采用主从JK触发器设计同步计数器。

2.总体描述主从JK触发器由一个钟控D_FF和一个钟控T_FF组成,利用主从JK触发器实现一个同步计数器。

2.1.功能描述本设计清零信号clear低电平有效,输入数据在时钟信号clock的上升沿被锁存,触发器在clock的下降沿输出,当count_enable信号为低电平时停止计数。

2.顶层框图图2.1计数器顶层框图2.3.引脚描述表2.1 顶层接口信号描述2.4.接口时序清零信号clear低电平有效,输入数据在时钟信号clock的上升沿被锁存,触发器在clock的下降沿输出,当count_enable信号为高电平时计数器计数,Q自动加1。

具体时序关系如图2.1所示图2.2计数器接口时序图3.模块划分本设计分为三个模块。

A:顶层模块B:D_FF模块.C:T_FF 模块3.1 概述(叙述一下划分的几个大的模块)3.2模块Amodule counter(Q , clock, clear);// I/O portsoutput [3:0] Q;input clock, clear;// Instantiate the T flipflopsT_ff tff0(Q[0], clock, clear);T_ff tff1(Q[1], Q[0], clear);T_ff tff2(Q[2], Q[1], clear);T_ff tff3(Q[3], Q[2], clear);endmodule3.2.1功能定义本模块采用主从JK触发器设计一个同步计数器。

3.2.2信号描述表3.1 模块A信号描述3.2.3时序描述(包含必要的时序图以及文字说明)图3.1 计数器的序图3.2.3 祥细设计3.1 计数器详细结构.3.3模块Bmodule edge_dff(q, qbar, d, clk, clear);// Inputs and outputsoutput q,qbar;input d, clk, clear;// Internal variableswire s, sbar, r, rbar,cbar;// Data flow statements//Create a complement of signal clearassign cbar = ~clear;// Input latchesassign sbar = ~(rbar & s),s = ~(sbar & cbar & ~clk),r = ~(rbar & ~clk & s),rbar = ~(r & cbar & d);// Output latchassign q = ~(s & qbar),qbar = ~(q & r & cbar);endmodule// Edge triggered T-flipflop. Toggles every clock// cycle.3.4模块Cmodule T_ff(q, clk, clear);// I/O portsoutput q;input clk, clear;// Instantiate the edge triggered DFF// Complement of output q is fed back.// Notice qbar not needed. Empty port.edge_dff ff1(q, ,~q, clk, clear);endmodule// Ripple counter4.模块分述(设计比较复杂的时候,根据需要对模块进行细化说明,需要加上模块分述这一部分。

)4.1模块A4.2模块B4.3模块C.4.4模块D5.验证方案给出对于整个设计的验证方法,详见《xxxx总体仿真验证方案》。

源程序:// Edge triggered D flipflopmodule edge_dff(q, qbar, d, clk, clear);// Inputs and outputsoutput q,qbar;input d, clk, clear;// Internal variableswire s, sbar, r, rbar,cbar;// Data flow statements//Create a complement of signal clearassign cbar = ~clear;// Input latchesassign sbar = ~(rbar & s),s = ~(sbar & cbar & ~clk),r = ~(rbar & ~clk & s),rbar = ~(r & cbar & d);// Output latchassign q = ~(s & qbar),qbar = ~(q & r & cbar);endmodule// Edge triggered T-flipflop. Toggles every clock// cycle.module T_ff(q, clk, clear);// I/O portsoutput q;input clk, clear;// Instantiate the edge triggered DFF// Complement of output q is fed back. // Notice qbar not needed. Empty port. edge_dff ff1(q, ,~q, clk, clear);endmodule// Ripple countermodule counter(Q , clock, clear);// I/O portsoutput [3:0] Q;input clock, clear;// Instantiate the T flipflopsT_ff tff0(Q[0], clock, clear);T_ff tff1(Q[1], Q[0], clear);T_ff tff2(Q[2], Q[1], clear);T_ff tff3(Q[3], Q[2], clear);endmodule// Top level stimulus modulemodule stimulus;// Declare variables for stimulating inputreg CLOCK, CLEAR;wire [3:0] Q;initial$monitor($time, " Count Q = %b Clear= %b", Q[3:0],CLEAR);initial$gr_waves( "clk", CLOCK,"Clear", CLEAR,"Q", Q[3:0],"Q0", Q[0],"Q1", Q[1],"Q2", Q[2],"Q3", Q[3]);// Instantiate the design block countercounter c1(Q, CLOCK, CLEAR);// Stimulate the Clear SignalinitialbeginCLEAR = 1'b1;#34 CLEAR = 1'b0;#200 CLEAR = 1'b1;#50 CLEAR = 1'b0;end// Setup the clock to toggle every 10 time unitsinitialbeginCLOCK = 1'b0;forever #10 CLOCK = ~CLOCK;end// Finish the simulation at time 200initialbegin#400 $finish;endendmodule仿真图:6.测试方案(这个只对整个完整的电路功能的测试需要给出测试方案,对于模块设计不需要给出测试方案。

)采用FPGA进行硬件测试。

使用Xilinx的ISE进行综合。

开发板采用Xilinx的ML403,FPGA型号为Virtex-4 XC4VFX12。

详见《xxxx总体测试方案》。

7.设计开发环境综合工具:Xilinx ISE 10.1FPGA设计和仿真工具:Modelsim ,Active HDL 8.18.设计开发计划。