3门电路

- 格式:ppt

- 大小:4.29 MB

- 文档页数:93

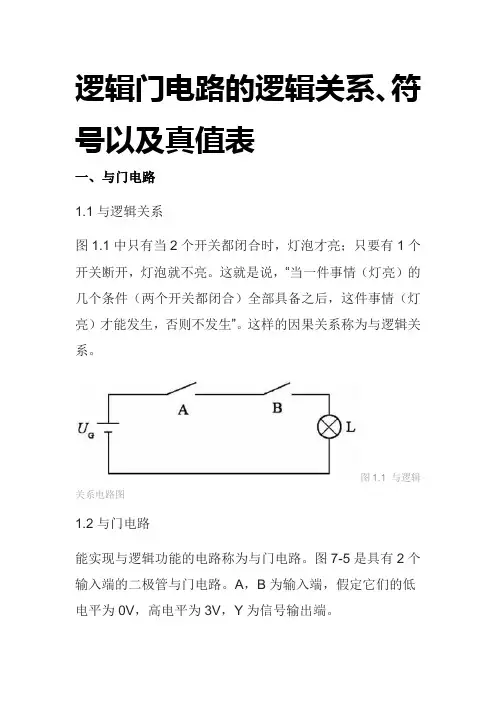

逻辑门电路的逻辑关系、符号以及真值表一、与门电路1.1与逻辑关系图1.1中只有当2个开关都闭合时,灯泡才亮;只要有1个开关断开,灯泡就不亮。

这就是说,“当一件事情(灯亮)的几个条件(两个开关都闭合)全部具备之后,这件事情(灯亮)才能发生,否则不发生”。

这样的因果关系称为与逻辑关系。

图1.1 与逻辑关系电路图1.2与门电路能实现与逻辑功能的电路称为与门电路。

图7-5是具有2个输入端的二极管与门电路。

A,B为输入端,假定它们的低电平为0V,高电平为3V,Y为信号输出端。

图1.2与门电路(1) 当A,B都处于低电平0V时,二极管VD1,VD2同时导通,Y=0V,输出低电平。

(忽略二极管的正向压降,下同)。

(2) 当A=0V,B=3V时,VD1优先导通,Y被箝位在0V,VD2反偏而截止。

(3) 当A=3V,B=0V时,VD2优先导通,Y被箝位在0V,VD1反偏而截止。

(4) 当A,B都处在高电平3V时,VD1与VD2均截止,Y 端输出高电平(即3V)。

与逻辑关系的逻辑函数表达式为Y=A*B。

表1.1是与门真值表,从真值表可以看出,与门电路的逻辑功能是“有0出0,全1出1”。

与门的逻辑符号如图1.3所示。

表1.1 与门真值表图1.3与门的逻辑符二、或门电路2.1或逻辑关系图2.1中电路由2个开关和灯泡组成。

由图可知,在决定一件事情的各种条件中,至少具备一个条件,这件事情就会发生,这种因果关系称为或逻辑关系。

图2.1 或逻辑关系电路图2.2或门电路能实现或逻辑关系的电路称为或门电路。

图2.2所示为具有2个输入端的二极管或门电路。

图2.2 或门电路真值表见表2.1,从真值表可以看出,或门的逻辑功能为“有1出1,全0出0”。

或门的逻辑符号如图2.3所示。

表2.1 或门真值表图2.3 或门逻辑符号三、非门电路(反相器)3.1非逻辑关系如图3.1开关与灯泡并联,当开关断开时,灯亮;开关闭合时,灯不亮。

这就是说,“事情(灯亮)和条件(开关)总是呈相反状态”,这种关系称为非逻辑关系。

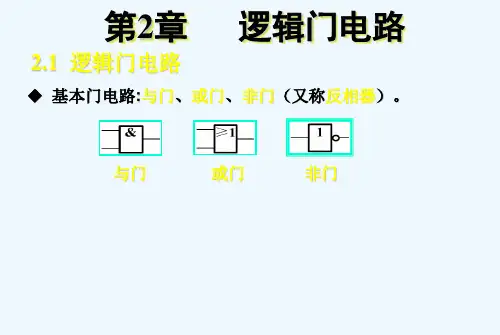

1、基本门电路逻辑符号:1与门(And)或门(OR)非门(not)与非门(nand)或非门(nor)与或非(xor)2、Quartus II是Altera公司新一代的EDA设计工具,由该公司早先的MAXPLUSII演变而来,3、Quartus II集成开发环境的设计流程设计输入约束输入综合布局布线时序分析仿真器件编程与配置4、可编程逻辑器件PLD:低密度可编程逻辑器件(LDPLD)高密度可编程逻辑器件(HDPLD)5、EDA中文意思:电子设计自动化,由Electronic、Design、Automation。

6、HDL中文意思:硬件描述语言,由Hardware、Description、Language。

7、一个电路的HDL模块定义由:关键字module+名字开始,以endmodule结束8、一个电路的HDL模块声明由:模块名字和模块输入输出端口列表。

9、模块的端口类型有:输入端口(input)、输出端口(output)、输入/输出双向端口(inout)。

10、变量类型:wire线网型、 reg寄存器型、 memory寄存器型。

11、由持续赋值语气Assign赋值的变量必须定义:Wire类型12、在Always过程语句中被赋值变量必须定义为:reg类型13、在模块的端口声明部分如何说明总线型多位信号的位宽。

Wire[7:0] data;//说明一个8位数据总线data为wire型;Wire[31:0]adder;//说明一个32位地址总线adder为wire型。

14、wire类型变量和reg类型变量差别是什么?除了表示组合逻辑电路中的连接线,reg型变量还可以在时序电路中对应具有状态保持作用电路元件,根本区别就在于:reg型变量在定义时默认的初始值为不定值x,在设计时要求放在always过程语句内部通过过程赋值语句赋予明确的值。

如果寄存器变量没有得到新的赋值,它将一直保持原有的值不变。

15、LED数码管中分为:共阴极和共阳极。

2.2 三态门1.基本原理在数字系统中,常常需要把多个门电路的输出端连接在一起,比如接到数据总线上。

但一般的门电路都只有两个输出状态:输出高电平状态与输出低电平状态。

把这些门电路的输出端连接在一起,在某一个时刻,可能会出现一个以上的门电路的输出同时为高电平状态或者低电平状态,这样就会引起逻辑电平的不确定。

使用三态门可以很好地解决这个问题。

三态门电路有三个输出状态:输出高电平状态、输出低电平状态,以及输出高阻状态。

当三态门电路输出为高阻状态时,三态门的输出端相当于开路,对总线上连接的其它器件没有影响。

我们可以利用三态门的这个优点对需要通过总线的数据进行分时传送,这样数据的传送就不会出现混乱了。

简单的三态门电路如图2.2.1a所示,图2.2.1b是它的代表符号。

其中EN为片选信号输入端,A为数据输入端,L为数据输出端。

图2.2.1 三态门电路(a) 电路图(b) 代表符号当EN=0时,TP2和TN2同时导通,为正常的非门,输出L=-A;当EN=1时,TP2和TN2同时截止,输出为高阻状态。

所以,这是一个低电平有效的三态门。

三态门的真值表如表2.2.1所示。

由真值表可以得出逻辑表达式:当EN=0时,L=-A;当EN=1时,L=Z。

其中Z表示高阻状态。

表2.2.1 三态门的真值表2.实现方案通过FPGA来实现三态门的功能有以下几种方式:(1) 用case语句和if….else语句来实现。

先判断EN是否等于1,如果EN 等于1,则输出端L=Z;如果不等于1,再判断A是否等于0,如果等于0,则输出端L=1,如果不等于0,则输出端L=0。

(2) 用if….else语句来实现。

先判断EN是否等于1,如果EN等于1,则输出端L=Z;如果不等于1,则输出L=~A。

(3) 用“?:”语句来实现,输出端L=EN ? 1’bZ : (~A)。

3.FPGA的实现下面以第三种方案为例来进行FPGA的实现。

(1) 创建工程并设计输入①在E:\project\目录下,新建名为notif的新工程器件族类型(Device Family)选择“Virtex2P”,器件型号(Device)选“XC2VP30 ff896 -7”,综合工具(Synthesis Tool)选“XST (VHDL/Verilog)”,仿真器(Simulator)选“ISE Simulator(VHDL/Verilog)”。

山东大学2018年《906-数字电路(专)》考研大纲906-数字电路(专)一、考试性质《数字电路》是电子与通信工程(专业学位)、集成电路工程(专业学位)专业学位研究生入学考试的科目之一。

《数字电路》考试力求反映信息学科相关专业的特点,科学、公平、准确、规范地测评考生的基本素质和综合能力,以利用选拔具有发展潜力的优秀人才入学,为我国快速发展的信息产业培养出具有良好职业道德、国际化视野、较强分析与解决实际问题能力的高层次、应用型、复合型的专业人才。

二、考试要求《数字电路》是信息类学科的一门重要的基础课。

通过本课程测试考生对本专业的基本概念、基础知识的掌握情况和运用能力。

三、考试形式和试卷结构1.试卷满分及考试时间本试卷满分为150分,考试时间为180分钟2.答题方式答题方式为闭卷、笔试。

试卷由试题和答题纸组成。

3.考试题型试卷由题库组题,题型主要有填空题、选择题、简答题、综合分析题、综合设计题等。

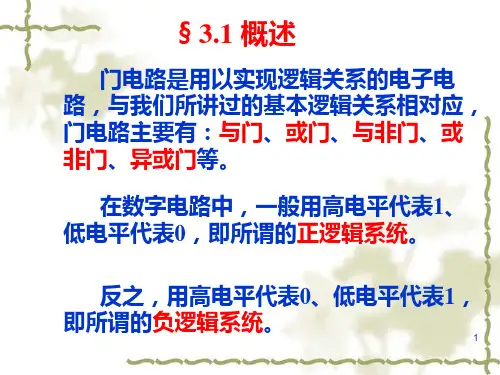

四、考试内容(一)数制与码制1.概述2.几种常见的数制3.不同数制间的转换4.二进制算术运算1)二进制算术运算的特点2)反码、补码和补码运算5.几种常用的编码(二)逻辑代数基础1.概述2.逻辑代数中的三种基本运算3.逻辑代数的基本公式和常用公式1)基本公式2)若干常用公式4.逻辑代数的基本定理1)代入定理2)反演定理3)对偶定理5.逻辑函数及其表示方法1)逻辑函数2)逻辑函数的表示方法3)逻辑函数的两种标准形式4)逻辑函数形式的变换6.逻辑函数的化简方法1)公式化简法2)卡诺图化简法7.具有无关项的逻辑函数及其化简1)约束项、任意项和逻辑函数式中的无关项2)无关项在化简逻辑函数中的应用(三)门电路1.概述2.半导体二极管门电路1)半导体二极管的开关特性2)二极管与门3)二极管或门3.CMOS门电路1)MOS管的开关特性2)CMOS反相器的电路结构和工作原理3)CMOS反相器的静态输入特性和输出特性4)CMOS反相器的动态特性5)其他类型的CMOS门电路6)CMOS电路的正确使用7)CMOS数字集成电路的各种系列4.其他类型的MOS集成电路1)PMOS电路2)NMOS电路5.TTL门电路1)双极型三极管的开关特性2)TTL反相器的电路结构和工作原理3)TTL反相器的静态输入特性和输出特性4)TTL反相器的动态特性5)其他类型的TTL门电路6)TTL数字集成电路的各种系列6.其他类型的双极型数字集成电路1)ECL电路2)电路7.TTL电路与CMOS电路的接口(四)组合逻辑电路1.概述2.组合逻辑电路的分析方法和设计方法1)组合逻辑电路的分析方法2)组合逻辑电路的设计方法3.若干常用的组合逻辑电路1)编码器2)译码器3)数据选择器4)加法器5)数值比较器4.组合逻辑电路中的竞争——冒险现象1)竞争——冒险现象及其成因2)检查竞争——冒险现象的方法3)消除竞争——冒险现象的方法(五)触发器1.概述2.SR锁存器3.电平触发的触发器4.脉冲触发的触发器5.边沿触发的触发器6.触发器的逻辑功能及其描述方法1)触发器按逻辑功能的分类2)触发器的电路结构和逻辑功能、触发方式的关系(六)时序逻辑电路1.概述2.时序逻辑电路的分析方法1)同步时序逻辑电路的分析方法2)时序逻辑电路的状态转换表、状态转换图、状态机流程图和时序图3)异步时序逻辑电路的分析方法3.若干常用的时序逻辑电路1)寄存器和移位寄存器2)计数器3)顺序脉冲发生器4)序列信号发生器4.时序逻辑电路的设计方法1)同步时序逻辑电路的设计方法2)时序逻辑电路的自启动设计(七)半导体存储器1.概述2.只读存储器(ROM)1)掩模只读存储器2)可编程只读存储器(PROM)3)可擦除的可编程只读存储器(EPROM)3.随机存储器(RAM)1)静态随机存储器(SRAM)2)动态随机存储器(DRAM)4.存储器容量的扩展1)位扩展方式2)字扩展方式5.用存储器实现组合逻辑函数(八)脉冲波形的产生和整形1.概述2.施密特触发器1)用门电路组成的施密特触发器2)集成施密特触发器3)施密特触发器的应用3.单稳态触发器1)用门电路组成的单稳态触发器2)集成单稳态触发器4.多谐振荡器1)对称式多谐振荡器2)非对称式多谐振荡器3)环形振荡器4)用施密特触发器构成的多谐振荡器5)石英晶体多谐振荡器5.555定时器及其应用1)5555定时器的电路结构与功能2)用555定时器接成的施密特触发器3)用555定时器接成的单稳态触发器4)用555定时器接成的多谐振荡器(九)数-模和模-数转换1.概述2.D/A转换器1)权电阻网络D/A转换器2)倒T形电阻网络D/A转换器3)权电流型D/A转换器4)开关树型D/A转换器5)权电容网络D/A转换器6)具有双极性输出的D/A转换器7)D/A转换器的转换精度和转换速度3.A/D转换器1)A/D转换的基本原理2)采样-保持电路3)并联比较型A/D转换器4)反馈比较型A/D转换器5)双积分型A/D转换器6)V—F变换型A/D转换器文章来源:文彦考研。

什么是三态门? 三态逻辑与非门电路以及三态门电路2008年05月26日 12:48 互联网作者:佚名用户评论(1)关键字:什么是三态门?三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路高阻态相当于隔断状态。

三态门都有一个EN控制使能端,来控制门电路的通断。

可以具备这三种状态的器件就叫做三态(门,总线,......).举例来说:内存里面的一个存储单元,读写控制线处于低电位时,存储单元被打开,可以向里面写入;当处于高电位时,可以读出,但是不读不写,就要用高电阻态,既不是+5v,也不是0v计算机里面用 1和0表示是,非两种逻辑,但是,有时候,这是不够的,比如说,他不够富有但是他也不一定穷啊,她不漂亮,但也不一定丑啊,处于这两个极端的中间,就用那个既不是+也不是―的中间态表示,叫做高阻态。

高电平,低电平可以由内部电路拉高和拉低。

而高阻态时引脚对地电阻无穷,此时读引脚电平时可以读到真实的电平值.高阻态的重要作用就是I/O(输入/输出)口在输入时读入外部电平用.1. 三态门的特点三态输出门又称三态电路。

它与一般门电路不同,它的输出端除了出现高电平、低电平外,还可以出现第三个状态,即高阻态,亦称禁止态,但并不是3个逻辑值电路。

2. 三态逻辑与非门三态逻辑与非门如图Z1123所示。

这个电路实际上是由两个与非门加上一个二极管D2组成。

虚线右半部分是一个带有源泄放电路的与非门,称为数据传输部分,T5管的u I1、u I2称为数据输入端。

而虚线左半部分是状态控制部分,它是个非门,它的输入端C称为控制端,或称许可输入端、使能端。

当C端接低电平时,T4输出一个高电平给T5,使虚线右半部分处于工作状态,这样,电路将按与非关系把u I1,u I2接受到的信号传送到输出端,使u o或为高电平,或为低电平。

当C端接高电平时,T4输出低电平给T5,使T6、T7、T10截止。

另一方面,通过D2把T8的基极电位钳在1v左右,使T9截止。

简单的逻辑电路教案一、课题:简单的逻辑电路二、教学目标:知识和技能:1、知道数字电路和模拟电路的概念,了解数字电路的优点。

2、知道“与”门、“或”门以及“非”门电路的特征、逻辑关系及表示法。

3、初步了解“与”门、“或”门以及“非”门电路在实际问题中的应用。

过程与方法:以实验教学为主体的媒体教学为辅的课堂教学模式;以对比教学为主线、联系生活实际为辅线开展课堂教学活动。

情感、态度和价值观:感受数字技术对现代生活的巨大改变;体验物理知识与实践的紧密联系。

三、教学重、难点:三种门电路的逻辑关系以及门电路的实际应用。

四、教学过程:演示实验引入课题火警报警装置用火柴点燃放在图示位置,结果听到喇叭鸣叫。

问:1、为什么会有这样的实验现象?2、中间的“黑盒子”是什么元件?实验装置图:我们今天的这节课就是要来探究实验现象产生的原因以及“黑盒子”里的元件。

为此让我们从稳恒电路的模拟世界进入实用的数字世界。

一、数字电路和模拟电路电子电路中的信号:1、模拟信号:幅度随时间连续变化的信号例:正弦波信号、锯齿波信号等。

2、数字信号:幅度不随时间连续变化,而是跳跃变化阅读材料(见附页)点燃的火柴引:数字电路的基本单元是逻辑电路,逻辑电路中最基本的电路叫做“门”电路, (门电路是一种有一个或多个输入端,只有一个输出端的开关电路,是数字电路的基本单元。

门电路就像一扇门,当具备开门条件时,输出端就有一个信号输出;反之,门关闭)。

它们在工作时输入端和输出端的电势只有两种情况:一种为高电势(如12V),另一种为低电势(如0V), 电路工作好像处在一种“是”和“非”的判断之中,因此叫做逻辑电路。

首先来认识一下逻辑电路的种类:二、逻辑电路的种类“与”门、“或”门、“非”门以及“与非”门、“或非”门和“异或”门(符号略)今天我们主要的任务是了解“与”门、“或”门和“非”门的特点及其应用。

三、逻辑电路的特点1、“与”逻辑电路(and)演示实验(利用积件模拟教材演示实验)这是一个搭积木的过程,教师在电脑屏幕上将积木(元件)准备好,学生上讲台操作鼠标,按下其中任意一个T o gg le Sw itch(键),LED(灯)不亮;当按下两个T o gg le Switch(键),LED(灯)亮。

如何看懂电路图6--数字逻辑电路2008/12/17 13:21数字电子电路中的后起之秀是数字逻辑电路。

把它叫做数字电路是因为电路中传递的虽然也是脉冲,但这些脉冲是用来表示二进制数码的,例如用高电平表示“ 1 ”,低电平表示“ 0 ”。

声音图像文字等信息经过数字化处理后变成了一串串电脉冲,它们被称为数字信号。

能处理数字信号的电路就称为数字电路。

这种电路同时又被叫做逻辑电路,那是因为电路中的“ 1 ”和“ 0 ”还具有逻辑意义,例如逻辑“ 1 ”和逻辑“ 0 ”可以分别表示电路的接通和断开、事件的是和否、逻辑推理的真和假等等。

电路的输出和输入之间是一种逻辑关系。

这种电路除了能进行二进制算术运算外还能完成逻辑运算和具有逻辑推理能力,所以才把它叫做逻辑电路。

由于数字逻辑电路有易于集成、传输质量高、有运算和逻辑推理能力等优点,因此被广泛用于计算机、自动控制、通信、测量等领域。

一般家电产品中,如定时器、告警器、控制器、电子钟表、电子玩具等都要用数字逻辑电路。

数字逻辑电路的第一个特点是为了突出“逻辑”两个字,使用的是独特的图形符号。

数字逻辑电路中有门电路和触发器两种基本单元电路,它们都是以晶体管和电阻等元件组成的,但在逻辑电路中我们只用几个简化了的图形符号去表示它们,而不画出它们的具体电路,也不管它们使用多高电压,是 TTL 电路还是 CMOS 电路等等。

按逻辑功能要求把这些图形符号组合起来画成的图就是逻辑电路图,它完全不同于一般的放大振荡或脉冲电路图。

数字电路中有关信息是包含在 0 和 1 的数字组合内的,所以只要电路能明显地区分开 0 和 1 , 0 和 1 的组合关系没有破坏就行,脉冲波形的好坏我们是不大理会的。

所以数字逻辑电路的第二个特点是我们主要关心它能完成什么样的逻辑功能,较少考虑它的电气参数性能等问题。

也因为这个原因,数字逻辑电路中使用了一些特殊的表达方法如真值表、特征方程等,还使用一些特殊的分析工具如逻辑代数、卡诺图等等,这些也都与放大振荡电路不同。