《数 字 逻 辑》模拟试题3

班级 姓名 学号 成绩

一、填空题

1. 某电路有4个开关,当其中任意3个开关或3个以上开关接通时(设开关接通为1,断开为0,则电路接通,F=1,否则 F=0。若用最小项标准表达式表示,则

F (A ,B ,C ,D )= 。

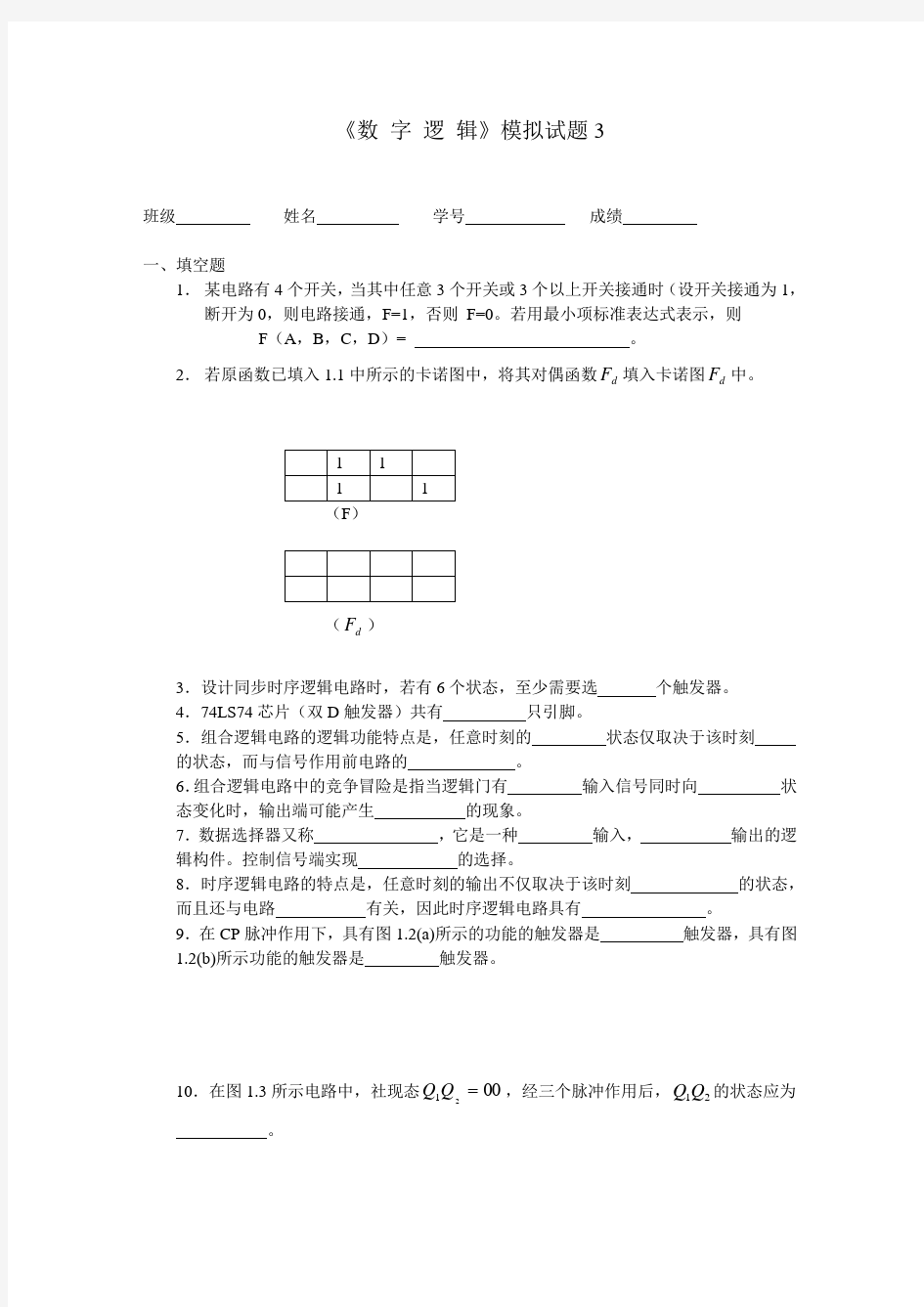

2. 若原函数已填入1.1中所示的卡诺图中,将其对偶函数d F 填入卡诺图d F 中。

(F )

(d F )

3.设计同步时序逻辑电路时,若有6个状态,至少需要选 个触发器。

4.74LS74芯片(双D 触发器)共有 只引脚。

5.组合逻辑电路的逻辑功能特点是,任意时刻的 状态仅取决于该时刻 的状态,而与信号作用前电路的 。

6.组合逻辑电路中的竞争冒险是指当逻辑门有 输入信号同时向 状态变化时,输出端可能产生 的现象。

7.数据选择器又称 ,它是一种 输入, 输出的逻辑构件。控制信号端实现 的选择。 8.时序逻辑电路的特点是,任意时刻的输出不仅取决于该时刻 的状态,而且还与电路 有关,因此时序逻辑电路具有 。

9.在CP 脉冲作用下,具有图1.2(a)所示的功能的触发器是 触发器,具有图1.2(b)所示功能的触发器是 触发器。

10.在图1.3所示电路中,社现态0021 Q Q ,经三个脉冲作用后,21Q Q 的状态应为 。

二、单项选择题

1.十进制数33的余3码为( )。

A. 00110110

B. 110110

C. 01100110

D. 100100

2.二进制小数-0.0110的补码表示为( )。

A .0.1010

B .1.1001

C .1.0110

D .1.1010

3.两输入与非门输出为0时,输入应满足( )。

A .两个同时为1

B .两个同时为0

C .两个互为相反

D .两个中至少有一个为0

4.下列电路中属于同步时序逻辑电路的是 。

属于组合逻辑电路的是 。

属于脉冲异步时序逻辑电路的是 。

属于电平异步时序逻辑电路的是 。

5.根据反演规则可知,逻辑函数C B B A F +=的反函数为( )。

A .C

B B A F +?+= B .

C B B A F +?+=

C .)()(C B B A F +?+=

D .)()(C B B A F +?+=

6.设i m 和j m 是n 个变量构成的两个最小项,若j i ≠,则( )。

A .0=?i j m m

B . 0=+j i m m

C .1=?j i m m

D .1=+j i m m

7.某4变量卡诺图中有9个“0”方格7个“1”方格,则相应的标准与或表达式中共有多少个与项( )?

A . 9

B .7

C .16

D .不能确定

三、多项选择题

1.n 个变量的最小项是 。

A . n 个变量的积项,它包含全部n 个变量

B . n 个变量的和项,它包含全部n 个变量

C . 每个变量都以原变量或者反变量的形式出现,且仅出现一次。

D . n 个变量的和项,它不包含全部变量。

2.逻辑函数C B AB C A F ++=,当变量的取值为 时,将出现冒险现象。

A .B=C=1

B .B=C=0

C .A=1,C=0

D .A=B=0

3.若i m 和i M 分别表示n 个变量的最小项和最大项,则有( )。

A . 1=+i i M m

B .0=?i i M m

C .1=⊕i i M m

D .i i M m =

4.当描述同步时序电路的最简状态表中含又 个状态时,需要两个触发器。

A . 3

B . 4

C . 2

D . 5

5.组合逻辑电路的结构特点,表现为( )。

A .有记忆功能

B .有反馈回路

C .不含记忆元件

D .无反馈回路

四、判断改错题

1.若逻辑变量x 和y 满足xy=x+y ,则x=y 。( )

2.若(A ,B )为相容状态时,(B ,C )也为相容状态对,则(A ,B ,C ,)构成一个相容类。( )

3.时序逻辑电路均包含有触发器。( )

4.米里型电路状态表的读法是,处于状态y 的同步时序电路,输出为Z ;当输入为x 时,在时钟脉冲作用下,电路进入次态)1(+n y 。( )

5.脉冲异步时序逻辑电路与同步时序逻辑电路的主要区别是输入为脉冲信号。( )

五、用代数法化简CD D AC ABC C A F +++=

六、用卡诺图化简法求F 的最简与或和最简或与表达式

F (A ,B ,C ,D )=∑m(0,2,7,13,15)+ ∑d(1,3,4,5,6,8,10)

七、四路数据选择器的选择控制变量01A A 分别接A ,B ,数据输入端3210,,,D D D D 依次接

c ,o,o,c ,试分析该电路实现何功能?

八、分析图7.1所示同步计数电路,作出状态转移表和状态图。计数器是n 进制计数器?能

否自启动?并画出在时钟作用下的各触发器输出波形。

九、化简表9.1同步时序电路的原始状态表。

1. 作出隐含表。

2. 找出等效对。

3. 列出最大等效类。

4. 求出最小化状态表。

5. 实现该电路功能,至少需要几个出发器。

十、用一片T138译码器和适当的与非门实现如下真值表所示的电路功能。