与门、或门及非门之间的关系

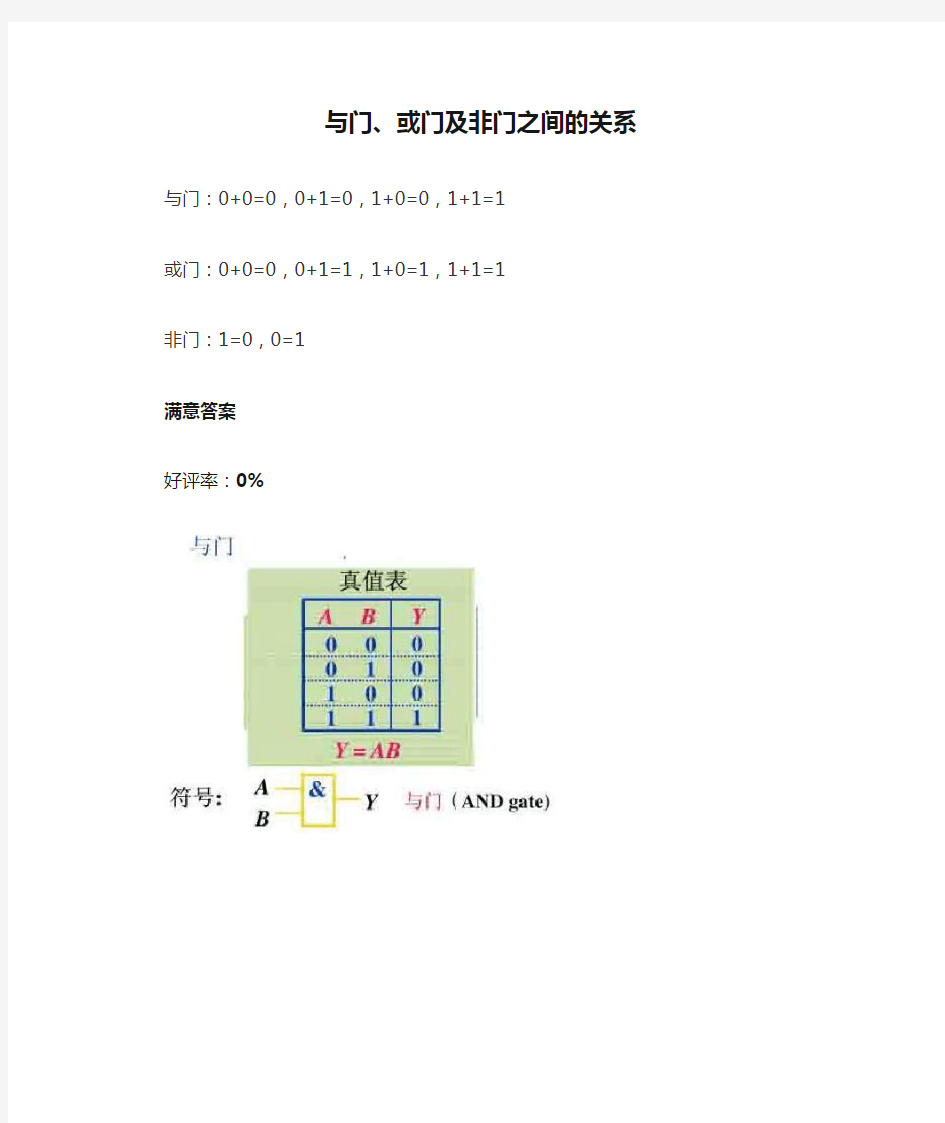

与门:0+0=0,0+1=0,1+0=0,1+1=1

或门:0+0=0,0+1=1,1+0=1,1+1=1

非门:1=0,0=1

满意答案

好评率:0%

43121556423156实验三:基本门电路及触发器 实 验 室: 实验台号: 日 期: 2016.10.7 专业班级: 姓 名: 学 号: 一、 实验目的 1.了解TTL 门电路的原理,性能好使用方法,验证基本门电路逻辑功能。 2.掌握门电路的设计方法。 3.验证J-K 触发器的逻辑功能。 4.掌握触发器转换的设计方法。 二、实验内容 (一)验证以下门电路的逻辑关系 1. 用与非门(00)实现与门逻辑关系:F=AB 2. 异或门(86): (二):门电路的设计(二选一) 1.用74LS00和74LS86 设计半加器. 2.用TTL 与非门设计一个三人表决电路。 A B C 三个裁判,当表决某个提案时,多数人同意提案为通过。 (1为同意,0为不同意) 要求:用74LS00和 74LS10芯片。 (三)验证JK 触发器的逻辑关系 1.J-K 触发器置位端、复位端及功能测试。 图3-1 JK 触发器(74LS112)和D 触发器(74LS74) 2、设计J-K 触发器转化成D 触发器的电路 利用与非门和J-K 触发器设计并测试逻辑功能。 B A B A B A F ⊕=+=n n n n n n n B A B A B A S ⊕=+=' n n n B A C ='

A B F 三、实验原理图 图3-2与门电路 图3-3 异或门电路 图3-4半加器 四、实验结果及数据处理 1. 直接在实验原理图上标记芯片的引脚。 2. 写出实验结果。 (1)与门、异或门实验结果表(用数字万用表测量高低电平1、0的电压值。) (2)半加器实验结果 (3) 表决电路结果 =1A B F

Duffing 方程及其在信号检测中的应用 李禹锋 (西安交通大学电力设备电气绝缘国家重点实验室,陕西西安710049) 摘要:在工程领域中,在噪声环境下对信号进行检测一直都是研究的重点课题。混沌理论表明一类混沌系统在一定条件下对小信号具有参数敏感性,同时对噪声具有免疫力,因此使得它在信号检测中非常具有发展潜力。为此,本文分析了Duffing 方程的动力学特性,研究了利用Duffing 方程来进行微弱信号检测的原理和过程,并在Matlab 平台下进行了仿真实验。结果表明,可以利用Duffing 方程在噪声背景下进行信号的检测。 关键词:混沌理论;信号检测; Duffing 方程;仿真研究 1 引言 在噪声背景中检测微弱的有用信号是工程应用中的一个重要内容,前人已经开展了大量的研究工作。传统的基于线性理论的信号检测方法由于对噪声背景下的输出信噪比难以提高而存在一定局限性,尤其在对强噪声背景下的微弱信号检测更是受到了限制。然而很多研究证明,利用“混沌振子对周期小信号具有敏感依赖性,而对噪声具有免疫性”的特点,从噪声背景中提取微弱的周期信号是一种行之有效的方法,引起了人们极大的兴趣[1]。 在众多的信号检测中,正弦或余弦信号的检测占有极其重要的地位,在许多领域中有着极其广泛的应用。本文采用余弦小信号作为检测对象,在Matlab 平台下,对Duffing 方程及其在信号检测中的应用进行了初步探讨。 2 基于Duffing 方程的信号检测 2.1 Duffing 方程的数学模型及分析 Duffing 方程已被证明是混沌系统,大量学者对其进行过许多研究,研究它的动力学行为可以揭示系统的各种性质。Duffing 系统所描述的非线性动力学系统表现出丰富的非线性动力学特性,目前已成为研究混沌现象的常用模型[2]。 霍尔姆斯型Duffing 方程为: 232()()cos()d x dx k x t x t t dt dt γω+-+=(1) 式中,cos()t γ为周期策动力;k 为阻尼比;-x (t )+x 3(t )为非线性恢复力[3]。其状态方程为: dx y dt =(2) 3cos()dy ky x x t dt γω=-+-+(3) 在k 固定的情况下,系统状态随γ的变化出现变化,具体分析如下: (1)当策动力γ为0时,计算得到相平面中结点为(0,0)和鞍点为(±1,0)。系统

) 课程设计任务书 学生姓名:王伟专业班级:电子1001班 指导教师:刘金根工作单位:信息工程学院题目: 基于CMOS的二输入与门电路 初始条件: 计算机、Cadence软件、L-Edit软件 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求) & 1、课程设计工作量:2周 2、技术要求: (1)学习Cadence IC软件和L-Edit软件。 (2)设计一个基于CMOS的二输入的与门电路。 (3)利用Cadence和L-Edit软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 | 学习Cadence IC和L-Edit软件,查阅相关资料,复习所设计内容的基本理论知识。 对二输入与门电路进行设计仿真工作,完成课设报告的撰写。 提交课程设计报告,进行答辩。 指导教师签名:年月日系主任(或责任教师)签名:年月日

目录 # 摘要 (2) 绪论…....………………………………………….………………….. ..3 一、设计要求 (4) 二、设计原理 (4) 三、设计思路 (4) 3.1、非门电路 (4) 3.2、二输入与非门电路 (6) 、二输入与门电路 (8) } 四、二输入与门电路设计 (9) 4.1、原理图设计 (9) 4.2、仿真分析 (10) 4.3、生成网络表 (13) 五、版图设计........................ (20) 、PMOS管版图设计 (20) 、NMOS管版图设计 (22) 、与门版图设计 (23)

非线性电路中的混沌现象实验报告 篇一:非线性电路混沌实验报告 近代物理实验报告 指导教师:得分: 实验时间: XX 年 11 月 8 日,第十一周,周一,第 5-8 节 实验者:班级材料0705学号 XX67025 姓名童凌炜 同组者:班级材料0705学号 XX67007 姓名车宏龙 实验地点:综合楼 404 实验条件:室内温度℃,相对湿度 %,室内气压实验题目:非线性电路混沌 实验仪器:(注明规格和型号) 1. 约结电子模拟器约结电子模拟器的主要电路包括: 1.1, 一个压控震荡电路, 根据约瑟夫方程, 用以模拟理想的约结 1.2, 一个加法电路器, 更具电路方程9-1-10, 用以模拟结电阻、结电容和理想的约结三者相并联的关系 1.3, 100kHz正弦波振荡波作为参考信号 2. 低频信号发生器 用以输出正弦波信号,提供给约结作为交流 信号 3. 数字示波器 用以测量结电压、超流、混沌特性和参考信号等各个

物理量的波形 实验目的: 1. 了解混沌的产生和特点 2. 掌握吸引子。倍周期和分岔等概念 3. 观察非线性电路的混沌现象 实验原理简述: 混沌不是具有周期性和对称性的有序,也不是绝对的无序,而是可以用奇怪吸引子等来描述的复杂有序——混沌而呈现非周期性的有序。混沌的最本质特征是对初始条件极为敏感。 1. 非线性 线性和非线性,首先区别于对于函数y=f(x)与其自变量x的依赖关系。除此之外,非线性关系还具有某些不同于线性关系的共性: 1.1 线性关系是简单的比例关系,而非线性是对这种关系的偏移 1.3 线性关系保持信号的频率成分不变,而非线性使得频率结构发生变化 1.4 非线性是引起行为突变的原因 2. 倍周期,分岔,吸引子,混沌 借用T.R.Malthas的人口和虫口理论,以说明非线性关系中的最基本概念。 虫口方程如下:xn?1???xn(1?xn)

成绩评定表

课程设计任务书

目录 1 绪论 (1) 1.1设计背景 (1) 1.2设计目标 (1) 2 四输入与非门电路 (2) 2.1电路原理图 (2) 2.2四输入与非门电路仿真观察波形 (2) 2.3四输入与非门电路的版图绘制 (3) 2.4四输入与非门版图电路仿真观察波形 (4) 2.5LVS检查匹配 (5) 总结 (7) 参考文献 (8) 附录一:电路原理图网表 (9) 附录二:版图网表 (10)

1 绪论 1.1 设计背景 tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。 Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。 L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。 1.2设计目标 1.用tanner软件中的原理图编辑器S-Edit编辑四输入与非门电路原理图。 2.用tanner软件中的W-Edit对四输入与非门电路进行仿真,并观察波形。 3.用tanner软件中的L-Edit绘制四输入与非门版图,并进行DRC验证。 4.用W-Edit对四输入与非门的版图电路进行仿真并观察波形。 5.用tanner软件中的layout-Edit对四输入与非门进行LVS检验观察原理图与版图的匹配程度。

实验报告实验课题:门电路 实验目的: 常用腔I ri m路邂样功能扯其精试n也. 订件电路蔓圖实脸箱的结构、茶本功能和僅用有氐 掌握电路连接、排除故障和调试的方法。 实验仪器与器材: 1、数字电子技术实验系统 2、741^00典2输入与非门「I片 74LSI1三3输入与门1片 74LS04反和器 1片 741SH6 V^2输人异或门1片74LS32四2输入界或门1片 实验内容及步骤: TTL门电路逻辑功能验证 按图1-1在实验系统(箱)上找到相应的门电路。并把输入端按实验箱的逻辑开关,输出端按发光二极管如图1-2所示TTL与门电路逻辑功能验证接线图。 按状态表1-1中“与门”一栏输入A、B(0,1信号,观察输出结果()看LED备用发光二极管,如灯亮为1,灯灭为0)填入表1-1中,并用万用表测量0、1电平值。 按同样的方法,验证“或门” 74LS32…等的逻辑功能,并把结果填入表1-1中

图1-2TTL门电路实验流程图 实验数据记录及处理结果: 数据了记录自行完成 理论知识挺弄拐的.们实劭实行起來的确密纠斛的*做了好爭次总定有轲題?焉来

懂得了从电路图到真实电路的基 发現电线育 廉足坏抻的.做电蹬实检.还a 需啖多些经检呐? 五、实验总结 通过这次试验,我了解了用仪器拼接电路的基本情况。 本过程。在连接的时候,很容易因为线或者门出现问题。 H 次实验除珅下杲很豆杂”程是线路tt 较離连?实验所用到的关锭器件也不龙好找。 理论知识挺容易的+ (I 」实际实杠血來时例侥纠塔的.做了好茲挟总是育何遥*门来 发现电线件一棍呈坏抻的.做电賂实龄T 还定斋味幸映绅輪呐=

非线性电路混沌及其同步控制 【摘要】 本实验通过测量非线性电阻的I-U特性曲线,了解非线性电阻特性,,从而搭建出典型的非线性电路——蔡氏振荡电路,通过改变其状态参数,观察到混沌的产生,周期运动,倍周期与分岔,点吸引子,双吸引子,环吸引子,周期窗口的物理图像,并研究其费根鲍姆常数。最后,实验将两个蔡氏电路通过一个单相耦合系统连接并最终研究其混沌同步现象。 【关键词】 混沌现象有源非线性负阻蔡氏电路混沌同步费根鲍姆常数 一.【引言】 1963年,美国气象学家洛伦茨在《确定论非周期流》一文中,给出了描述大气湍流的洛伦茨方程,并提出了著名的“蝴蝶效应”,从而揭开了对非线性科学深入研究的序幕。非线性科学被誉为继相对论和量子力学之后,20世界物理学的“第三次重大革命”。由非线性科学所引起的对确定论和随机论、有序和无序、偶然性与必然性等范畴和概念的重新认识,形成了一种新的自然观,将深刻的影响人类的思维方法,并涉及现代科学的逻辑体系的根本性问题。 迄今为止,最丰富的混沌现象是非线性震荡电路中观察到的,这是因为电路可以精密元件控制,因此可以通过精确地改变实验条件得到丰富的实验结果,蔡氏电路是华裔科学家蔡少棠设计的能产生混沌的最简单的电路,它是熟悉和理解非线性现象的经典电路。 本实验的目的是学习有源非线性负阻元件的工作原理,借助蔡氏电路掌握非线性动力学系统运动的一般规律性,了解混沌同步和控制的基本概念。通过本实

验的学习扩展视野、活跃思维,以一种崭新的科学世界观来认识事物发展的一般规律。 二.【实验原理】 1.有源非线性负阻 一般的电阻器件是有线的正阻,即当电阻两端的电压升高时,电阻内的电流也会随之增加,并且i-v呈线性变化,所谓正阻,即I-U是正相关,i-v曲线的 斜率 u i ? ? 为正。相对的有非线性的器件和负阻,有源非线性负阻表现在当电阻两 端的电压增大时,电流减小,并且不是线性变化。负阻只有在电路中有电流是才会产生,而正阻则不论有没有电流流过总是存在的,从功率意义上说,正阻在电路中消耗功率,是耗能元件;而负阻不但不消耗功率,反而向外界输出功率,是产能元件。 一般实现负阻是用正阻和运算放大器构成负阻抗变换器电路。因为放大运算器工作需要一定的工作电压,因此这种富足成为有源负阻。本实验才有如图1所示的负阻抗变换器电路,有两个运算放大器和六个配置电阻来实现。 图1 有源非线性负阻内部结构 用电路图3以测试有源非线性负阻的i-v特性曲线,如图4示为测试结果曲线,分为5段折现表明,加在非线性元件上的电压与通过它的电流就行是相反的,

目录 1绪论 (2) 1.1 设计背景 (2) 1.2设计目标 (2) 2与门电路设计 (3) 2.1电路原理 (3) 2.2电路结构 (3) 2.3与门电路仿真波形 (4) 2.4与门电路的版图绘制及DRC验证 (5) 2.5与门电路版图仿真 (6) 2.6 LVS检查匹配 (6) 总结 (8) 参考文献 (9) 附录一版图网表: (10) 附录二电路图网表 (12)

1绪论 1.1 设计背景 Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。 L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。 1.2设计目标 1.用MOS场效应管实现二输入与门电路。 2.用tanner软件中的原理图编辑器S-Edit编辑反相器电路原理图。 3.用tanner软件中的W-Edit对反相器电路进行仿真,并观察波形。 4.用tanner软件中的L-Edit绘制反相器版图,并进行DRC验证。 5.用W-Edit对反相器的版图电路进行仿真并观察波形。 6.用tanner软件中的layout-Edit对反相器进行LVS检验观察原理图与版图的 匹配程度。

数字电路实验报告

实验一 组合逻辑电路分析 一.试验用集成电路引脚图 74LS00集成电路 74LS20集成电路 四2输入与非门 双4输入与非门 二.实验内容 1.实验一 自拟表格并记录: 2.实验二 密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开。否则,报警信号为“1”,则接通警铃。试分析密码锁的密码ABCD 是什么? X1 2.5 V A B C D 示灯:灯亮表示“1”,灯灭表示“0” ABCD 按逻辑开关,“1”表示高电平,“0”表示低电平

ABCD 接逻辑电平开关。 最简表达式为:X1=AB ’C ’D 密码为: 1001 A B C D X1 X2 A B C D X1 X2 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 1 1 0 0 1 1 0 0 0 1 0 0 1 1 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 0 1 0 1 0 0 0 1 1 1 0 0 0 1 0 1 0 1 0 1 1 1 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 1 0 1 1 1 1 1 1 1 1 1 三.实验体会: 1.分析组合逻辑电路时,可以通过逻辑表达式,电路图和真值表之间的相互转换来到达实验所要求的目的。 2.这次试验比较简单,熟悉了一些简单的组合逻辑电路和芯片 ,和使用仿真软件来设计和构造逻辑电路来求解。 实验二 组合逻辑实验(一) 半加器和全加器 一.实验目的 1. 熟悉用门电路设计组合电路的原理和方法步骤 二.预习内容 1. 复习用门电路设计组合逻辑电路的原理和方法步骤。 2. 复习二进制数的运算。 3. 用“与非门”设计半加器的逻辑图。 4. 完成用“异或门”、“与或非”门、“与 非”门设计全加器的逻辑图。 5. 完成用“异或”门设计的3变量判奇 电路的原理图。 三.元 件参考 U1A 74LS00D U1B 74LS00D U1C 74LS00D U1D 74LS00D U2A 74LS00D U2B 74LS00D U2C 74LS00D U3A 74LS20D X1 2.5 V X2 2.5 V VCC 5V A B C D

实验一电路元件伏安特性的测试 一、实验目的 1.学会识别常用电路元件的方法 2.掌握线性电阻、非线性电阻元件伏安特性的测试方法 3.熟悉实验台上直流电工仪表和设备的使用方法 二、原理说明 电路元件的特性一般可用该元件上的端电压U 与通过该元件的电流I之间的函数关系I=f(U)来表示,即用I-U平面上的一条曲线来表征,这条曲线称为该元件的伏安特性曲线。电阻元件是电路中最常见的元件,有线性电阻和非线性电阻之分。实际电路中很少是仅由电源和线性电阻构成的“电平移动”电路,而非线性器件却常常有着广泛的使用,例如非线性元件二极管具有单向导电性,可以把交流信号变换成直流量,在电路中起着整流作用。 万用表的欧姆档只能在某一特定的U和I下测出对应的电阻值,因而不能测出非线性电阻的伏安特性。一般是用含源电路“在线”状态下测量元件的端电压和对应的电流值,进而由公式R=U/I求测电阻值。 1.线性电阻器的伏安特性符合欧姆定律U=RI,其阻值不随电压或电流值的变化而变化,伏安特性曲线是一条通过坐标原点的直线,如图1-1(a)所示,该直线的斜率等于该电阻器的电阻值。 图1-1 元件的伏安特性 2.白炽灯可以视为一种电阻元件,其灯丝电阻随着温度的升高而增大。一般灯泡的“冷电阻”与“热电阻”的阻值可以相差几倍至十几倍。通过白炽灯的电流越大,其温度越高,阻值也越大,即对一组变化的电压值和对应的电流值,所得U/I不是一个常数,所以它的伏安特性是非线性的,如图1-1(b)所示。 3.半导体二极管也是一种非线性电阻元件,其伏安特性如图1-1(c)所示。二极管的电阻值随电压或电流的大小、方向的改变而改变。它的正向压降很小(一般锗管约为0.2~0.3V,硅管约为0.5~0.7V),正向电流随正向压降的升高而急剧上升,而反向电压从零一直增加到十几至几十伏时,其反向电流增加很小,粗略地可视为零。发光二极管正向电压在0.5~2.5V 之间时,正向电流有很大变化。可见二极管具有单向导电性,但反向电压加得过高,超过管子的极限值,则会导致管子击穿损坏。 4.稳压二极管是一种特殊的半导体二极管,其正向特性与普通二极管类似,但其反向特性较特殊,如图1-1(d)所示。给稳压二极管加反向电压时,其反向电流几乎为零,但当电压增加到某一数值时,电流将突然增加,以后它的端电压将维持恒定,不再随外加反向电压的升高而增大,这便是稳压二极管的反向稳压特性。实际电路中,可以利用不同稳压值的稳压管来实现稳压。注意:流过二极管或稳压二极管的电流不能超过管子的极限值,否则管子会被烧坏。

课程名称Course 集成电路设计技术 项目名称 Item 二输入与非门、或非门版图设 计 与非门电路的版图: .spc文件(瞬时分析): * Circuit Extracted by Tanner Research's L-Edit / Extract ; * TDB File: E:\cmos\yufeimen, Cell: Cell0 * Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\ * Extract Date and Time: 05/25/2011 - 10:03 .include H:\ VPower VDD GND 5 va A GND PULSE (0 5 0 5n 5n 100n 200n) vb B GND PULSE (0 5 0 5n 5n 50n 100n) .tran 1n 400n .print tran v(A) v(B) v(F) * WARNING: Layers with Unassigned AREA Capacitance. *

*

* * WARNING: Layers with Unassigned FRINGE Capacitance. * * * 《集成电路CAD》课程设计报告》 ——两输入或非门的设计 班级: 学号: 姓名: 指导教师: 一、设计要求 (1)绘制电路图 a、明确电路结构; b、明确电路中器件的类型、数目; c、明确电路中端口的数目以及所联接的信号类型; d、确定MOS的宽长比,确定MOS管的尺寸,沟长采用所用工艺规定的最 小条宽的整数倍。 (2)根据电路结构绘制版图 在正确的电路结构基础上,绘制版图: a、要求版图中电路的元件数目、类型以及尺寸与所画电路结构保持一致; b、要求元件之间连接正确,并与所确定电路结构保持一致; c、要求版图中电路的端口数目、位置与所确定电路保持一致; (3)DRC验证 绘制版图后要进行DRC验证: a、采用DRC规则文件对绘制版图进行DRC校验; b、根据校验提示语句修改版图直至正确为止,提交正确的DRC校验结果。 (4)撰写课程设计报告 按以下要求书写: a、报告严格按照以下提供模板格式书写; b、报告内容要含有原电路电路图以及所绘制版图的截图; c、报告内容要含有DRC校验结果(相关截图以及文件)。 二、设计目的 1、熟悉candence软件,并掌握其各种工具的使用方法。 2、用cadence设计一个三输入或非门,并画出仿真电路、版图、并验证其特性。 三、设计的具体实现 1.电路概述 二输入或非门有两个输入端A和B以及一个输出端Q,当A端或B端为高电平时输出为低电平,当两个输入都为低电平输出才为高,表达式如下所示: = Y+ A B 或非门的电路符号和真值表如图1所示: 图2 由于此次是用CMOS管构建的二输入或非门,而CMOS管的基本门电路有非门、与非门、或非门等,所以直接用CMOS管搭建出二输或非门电路。原理图如图二所示。 2.cadence简介: Cadence公司的电子设计自动化(Electronic Design Automation)产品涵盖了电子设计的整个流程,包括系统级设计,功能验证,IC综合及布局布线,模拟、混合信号及射频IC设计,全定制集成电路设计,IC物理验证,PCB设计和硬件仿真建模等。本次设计是基于cadence工具的三输入或非门的电路和版图设计。 电路实验报告1-叠加原理的验证 所属栏目:电路实验- 实验报告示例发布时间:2010-3-11 实验三叠加原理的验证 一、实验目的 验证线性电路叠加原理的正确性,加深对线性电路的叠加性和齐次性的认识和理解。 二、原理说明 叠加原理指出:在有多个独立源共同作用下的线性电路中,通过每一个元件的电流或其两端的电压,可以看成是由每一个独立源单独作用时在该元件上所产生的电流或电压的代数和。 线性电路的齐次性是指当激励信号(某独立源的值)增加或减小K 倍时,电路的响应(即在电路中各电阻元件上所建立的电流和电压值)也将增加或减小K倍。 三、实验设备 高性能电工技术实验装置DGJ-01:直流稳压电压、直流数字电压表、直流数字电流表、叠加原理实验电路板DGJ-03。 四、实验步骤 1.用实验装置上的DGJ-03线路, 按照实验指导书上的图3-1,将两路稳压电源的输出分别调节为12V和6V,接入图中的U1和U2处。 2.通过调节开关K1和K2,分别将电源同时作用和单独作用在电路中,完成如下表格。 表3-1 3.将U2的数值调到12V,重复以上测量,并记录在表3-1的最后一行中。 4.将R3(330 )换成二极管IN4007,继续测量并填入表3-2中。 表3-2 五、实验数据处理和分析 对图3-1的线性电路进行理论分析,利用回路电流法或节点电压法列出电路方程,借助计算机进行方程求解,或直接用EWB软件对电路分析计算,得出的电压、电流的数据与测量值基本相符。验证了测量数据的准确性。电压表和电流表的测量有一定的误差,都在可允许的误差范围内。 验证叠加定理:以I1为例,U1单独作用时,I1a=8.693mA,,U2单独作用时,I1b=-1.198mA,I1a+I1b=7.495mA,U1和U2共同作用时,测量值为7.556mA,因此叠加性得以验证。2U2单独作用时,测量值为-2.395mA,而2*I1b=-2.396mA,因此齐次性得以验证。其他的支路电流和电压也可类似验证叠加定理的准确性。 对于含有二极管的非线性电路,表2中的数据不符合叠加性和齐次性。 六、思考题 1.电源单独作用时,将另外一出开关投向短路侧,不能直接将电压源短接置零。 2.电阻改为二极管后,叠加原理不成立。 * * * WARNING: Layers with Unassigned FRINGE Capacitance. * * * 1绪论 1.1 设计背景 随着集成电路技术的日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少的有力工具[1]。国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。CAD技术的发展使得电子线路设计的速度、质量和精度得以保证。在众多的CAD工具软件中,Spice程序是精度最高、最受欢迎的软件工具,tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。 Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。 L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案[2]。L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。 虽然SPICE开发至今已超过20年,然而其重要性并未随着制程的进步而降低。就国内的设计环境而言,商用的SPICE模拟软件主要有Hspice、Pspice、SBTspice、SmartSpice与Tspice等。 HSpice是Spice程序应用在PC上的程序,它的主要算法与Spice相同。 门电路逻辑功能及测试实验报告记录 ————————————————————————————————作者:————————————————————————————————日期: 深圳大学实验报告实验课程名称:数字电路实验 实验项目名称:门电路逻辑功能及测试学院:信息工程学院 报告人:许泽鑫学号:201 班级:2班同组人: 指导教师:张志朋老师 实验时间:2016-9-27 实验报告提交时间:2016-10-11 一、实验目的 (1)熟悉门电路逻辑功能,并掌握常用的逻辑电路功能测试方法。 (2)熟悉RXS-1B数字电路实验箱。 二、方法、步骤 1.实验仪器及材料 1)RXS-1B数字电路实验箱 2)万用表 3)器件 74LS00四2输入与非门1片 74LS86四2输入异或门1片 2.预习要求 1)阅读数字电子技术实验指南,懂得数字电子技术实验要求和实验方 法。 2)复习门电路工作原理及相应逻辑表达式。 3)熟悉所用集成电路的外引线排列图,了解各引出脚的功能。 4)学习RXB-1B数字电路实验箱使用方法。 3.说明 用以实现基本逻辑关系的电子电路通称为门电路。常用的门电路在逻辑功能上有非门、与门、或门、与非门、或非门、与或非门、异或门等几种。 非逻辑关系:Y=A 与逻辑关系:Y=A B + 或逻辑关系:Y=A B 与非逻辑关系:Y=A B + 或非逻辑关系:Y=A B + 与或非逻辑关系:Y=A B C D ⊕ 异或逻辑关系:Y=A B 三、实验过程及内容 任务一:异或门逻辑功能测试 集成电路74LS86是一片四2输入异或门电路,逻辑关系式为1Y=1A ⊕1B ,2Y=2A ⊕2B , 3Y=3A ⊕3B ,4Y=4A ⊕4B ,其外引线排列图如图1.3.1所示。它的1、2、4、5、9、10、12、13号引脚为输入端1A 、1B 、2A 、2B 、3A 、3B 、4A 、4B ,3、6、8、11号引脚为输出端1Y 、2Y 、3Y 、4Y ,7号引脚为地,14号引脚为电源+5V 。 (1)将一片四2输入异或门芯片74LS86插入RXB-1B 数字电路实验箱的任意14引脚的IC 空插座中。 (2)按图1.3.2接线测试其逻辑功能。芯片74LS86的输入端1、2、4、5号引脚分别接至数字电路实验箱的任意4个电平开关的插孔,输出端3、6、8分别接至数字电路实验箱的电平显示器的任意3个发光二极管的插孔。14号引脚+5V 接至数字电路实验箱的+5V 电源的“+5V ”插孔,7号引脚接至数字电路实验箱的+5V 电源的“⊥”插孔。 (3)将电平开关按表1.3.1设置,观察输出端A 、B 、Y 所连接的电平显示器的发光二极管的状态,测量输出端Y 的电压值。发光二极管亮表示输出为高电平(H ),发光二极管不亮表示输出为低电平(L )。把实验结果填入表1.3.1中。 图1.3.1 四2输入异或门74LS86外引线排列图 1A 1B 1Y 2A 2B 74LS86 V CC 4B 4A 4Y 3B 4A 3Y 1 2 3 4 5 14 13 12 11 HUBEI NORMAL UNIVERSITY 电工电子实验报告 电路设计与仿真—Multisim 课程名称 逻辑门电路 实验名称 2009112030406 陈子明 学号姓名 电子信息工程 专业名称 物理与电子科学学院 所在院系 分数 实验逻辑门电路 一、实验目的 1、学习分析基本的逻辑门电路的工作原理; 2、学习各种常用时序电路的功能; 3、了解一些常用的集成芯片; 4、学会用仿真来验证各种数字电路的功能和设计自己的电路。 二、实验环境 Multisim 8 三、实验内容 1、与门电路 按图连接好电路,将开关分别掷向高低电平,组合出(0,0)(1,0)(0,1)(1,1)状态,通过电压表的示数,看到与门的输出状况,验证表中与门的功能: 结果:(0,0) (0,1) (1,0) (1,1) 2、半加器 (1)输入/输出的真值表 输入输出 A B S(本位和(进位 数)0000 0110 1010 1101 半加器测试电路: 逻辑表达式:S= B+A=A B;=AB。 3、全加器 (1)输入输出的真值表 输入输出 A B (低位进 位S(本位 和) (进位 数) 0 0 0 0 0 00110 01010 01101 10010 10101 11001 11111(2)逻辑表达式:S=i-1;C i=AB+C i-1(A B) (3)全加器测试电路: 4、比较器 (1)真值表 A B Y1(A>B Y2(A Y3(A=B 0 0 0 0 1 0 1 0 1 0 1 0 1 0 0 1 1 0 0 1 (2)逻辑表达式: Y1=A;Y2=B;Y3=A B。 (3)搭接电路图,如图: 1位二进制数比较器测试电路与结果: 创作编号: GB8878185555334563BT9125XW 创作者:凤呜大王* 叠加原理实验报告范文 一、实验目的 验证线性电路叠加原理的正确性,加深对线性电路的叠加性和齐次性的认识和理解。 二、原理说明 叠加原理指出:在有多个独立源共同作用下的线性电路中,通过每一个元件的电流或其两端的电压,可以看成是由每一个独立源单独作用时在该元件上所产生的电流或电压的代数和。 线性电路的齐次性是指当激励信号(某独立源的值)增加或减小K倍时,电路的响应(即在电路中各电阻元件上所建立的电流和电压值)也将增加或减小K倍。 三、实验设备 高性能电工技术实验装置DGJ-01:直流稳压电压、直流数字电压表、直流数字电流表、叠加原理实验电路板DGJ-03。 四、实验步骤 1.用实验装置上的DGJ-03线路,按照实验指导书上的图3-1,将两路稳压电源的输出分别调节为12V和6V,接入图中的U1和U2处。 2.通过调节开关K1和K2,分别将电源同时作用和单独作用在电路中,完成如下表格。 表3-1 3.将U2的数值调到12V,重复以上测量,并记录在表3-1的最后一行中。 4.将R3(330 )换成二极管IN4007,继续测量并填入表3-2中。 表3-2 五、实验数据处理和分析 对图3-1的线性电路进行理论分析,利用回路电流法或节点电压法列出电路方程,借助计算机进行方程求解,或直接用EWB软件对电路分析计算,得出的电压、电流的数据与测量值基本相符。验证了测量数据的准确性。电压表和电流表的测量有一定的误差,都在可允许的误差范围内。 验证叠加定理:以I1为例,U1单独作用时,I1a=8.693mA,,U2单独作用时, I1b=-1.198mA,I1a+I1b=7.495mA,U1和U2共同作用时,测量值为7.556mA,因此叠加性得以验证。2U2单独作用时,测量值为-2.395mA,而2*I1b=-2.396mA,因此齐次性得以验证。其他的支路电流和电压也可类似验证叠加定理的准确性。 对于含有二极管的非线性电路,表2中的数据不符合叠加性和齐次性。 二或门电路的设计 一.实验目的 1.熟悉Schematic,Virtuoso设计环境,掌握或门电路原理图输入方法。 2.熟悉仿真参数设置,掌握仿真步骤 3.掌握画版图步骤,了解版图设计规则 4.掌握版图的验证。 二.实验内容 2.1原理图设计 ①建立库文件 在CIW窗口中建立or库文件与or视图,打开电路原理图设计窗口。 ②添加元件 在gpdk180中选择3个pmos和3个nmos,在analoglib库中选择vcc和gnd各一个,按图1添加所需文件。 ③连线:按图1完成连线。 图1 二或门电路原理图 ④添加输入pin为A,B;输出pin为Y。 ⑤检查 检查电路结构与连线如图1所示,使用Check and Save图标进行差错修改并保存。 2.2二输入或门仿真 仿真电路如图1所示。对输入信号进行设值。 A输入信号设值如图2所示: 图2 Setup Analog Stimuli窗口 B输入信号设值如图3所示: 图3 Setup Analog Stimuli窗口电源电压设置如图4所示: 图4 Setup Analog Stimuli窗口对二输入或门进行瞬态分析,仿真设值窗口如图5所示: 图5 Choosing Analyses窗口 输出显示信号在原理图中选择A、B、Y三端。如图6所示: 图6 Analog Design Environment 窗口运行仿真,仿真曲线如图7所示: 图7 或门tran仿真曲线 2.3或门版图设计 启动版图设计环境Virtuoso layout Editor,完成or版图设计。 ①创建视图 在CIW窗口中建立Design库的or视图,打开Virtuoso layout Editor设计窗口。 ②添加元件 选择并添加3个pmos和3个nmos的单元版图。 ③布局布线 参考电路结构的特点,直接调用设计好的单元版图,按照MOS管版图设计规则,考虑所有布线所需要的几何尺寸以及所在的版层,可以选择先画出或非门版图,再画反相器版图,然后再将两者相连从而完成布线。 ④按照电路图1进行连线检查,连线无误后保存。cad设计二输入讲解

电路实验报告1--叠加原理

二输入与非门、或非门版图设计

三输入或门版图设计的

门电路逻辑功能及测试实验报告记录

逻辑门电路实验报告(精)

叠加原理 实验报告范文(含数据处理)

二或门电路的设计