Atomic Layer Deposition for Advanced DRAM Applications

By M. Gutsche, Infineon Technologies

Harald Seidl, Infineon Technologies

Thomas Hecht, Infineon Technologies

Stephan Kudelka, Infineon Technologies

Uwe Schroeder, Infineon Technologies

DRAM technology has been a major driver of innovations in process technology and manufacturing equipment in the microelectronics industry. As the semiconductor industry migrates to ever smaller device geometries, new deposition process technologies will be required to meet the challenges posed by the demand for novel materials, the need to work with ever thinner films, and the necessity to deposit conformal films into structures with increasingly high aspect ratios (AR). Atomic Layer Deposition (ALD) is a very attractive new technology which will open up great opportunities for next generation

Introduction

Over the last decades the semiconductor industry has witnessed an unprecedented trend in miniaturization of silicon-based devices and integrated circuits. Semiconductor technology is now entering the sub-100nm regime. As feature sizes approach ever smaller dimensions, process control at the atomic level will become increasingly important. This is true for both removal and deposition of material. Attempts to etch material with atomic level control, so-called Atomic Layer Etching (ALET), have been reported[1]. This technology, however, is still in its infancy and may not be utilized for some time to come. On the other hand, Atomic Layer Deposition (ALD) as a technique which allows film deposition with monolayer precision has matured substantially and is now being introduced into semiconductor processing[2]. Key ALD applications include the deposition of high-k dielectrics, metal electrodes, barriers, and spacers. Other novel and innovative ALD applications are on the drawing-board. This article will focus on the use of ALD in advanced DRAM technology.

The Basics of Atomic Layer Deposition

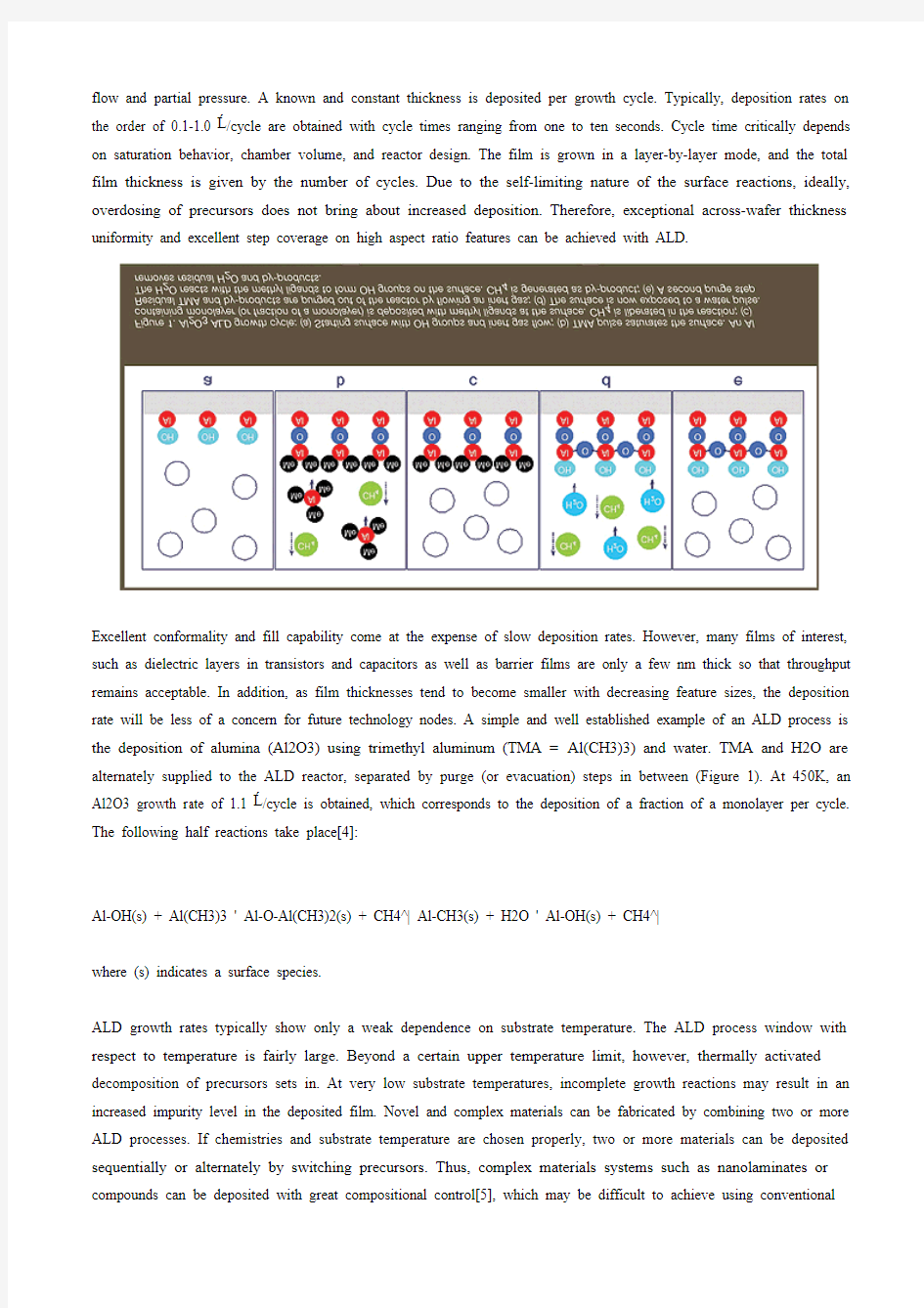

As opposed to conventional CVD which is characterized by continuous deposition and concurrent flow of precursors, Atomic Layer Deposition is based on the sequential deposition of individual monolayers or fractions of a monolayer in a well controlled manner[3]. In ALD, the growth surface is alternately exposed to only one of two complementary chemical environments, i.e. individual precursors are supplied to the reactor one at a time. Exposure steps are separated by inert gas purge or pump-down steps in order to remove any residual chemically active source gas or by-products before another precursor is introduced into the reactor. Thus, ALD consists of a repetition of individual growth cycles. Each cycle is made up of a typical sequence: Flow of precursor 1 ' Purge ' Flow of Precursor 2 ' Purge (Figure 1). During each exposure step, precursor molecules react with the surface until all available surface sites are saturated. Precursor chemistries and process conditions are chosen such that no further reaction takes place once the surface is completely saturated. Surface saturation guarantees the self-limiting nature of ALD. Precursors are preferably overdosed so that process results become independent of potential slight variations in the amount of precursor supplied to the surface. Thus, surface chemistry governs film growth rather than a precise control of tool specific process parameters such as precursor

flow and partial pressure. A known and constant thickness is deposited per growth cycle. Typically, deposition rates on the order of 0.1-1.0 ?/cycle are obtained with cycle times ranging from one to ten seconds. Cycle time critically depends on saturation behavior, chamber volume, and reactor design. The film is grown in a layer-by-layer mode, and the total film thickness is given by the number of cycles. Due to the self-limiting nature of the surface reactions, ideally, overdosing of precursors does not bring about increased deposition. Therefore, exceptional across-wafer thickness uniformity and excellent step coverage on high aspect ratio features can be achieved with ALD.

Excellent conformality and fill capability come at the expense of slow deposition rates. However, many films of interest, such as dielectric layers in transistors and capacitors as well as barrier films are only a few nm thick so that throughput remains acceptable. In addition, as film thicknesses tend to become smaller with decreasing feature sizes, the deposition rate will be less of a concern for future technology nodes. A simple and well established example of an ALD process is the deposition of alumina (Al2O3) using trimethyl aluminum (TMA = Al(CH3)3) and water. TMA and H2O are alternately supplied to the ALD reactor, separated by purge (or evacuation) steps in between (Figure 1). At 450K, an Al2O3 growth rate of 1.1 ?/cycle is obtained, which corresponds to the deposition of a fraction of a monolayer per cycle. The following half reactions take place[4]:

Al-OH(s) + Al(CH3)3 ' Al-O-Al(CH3)2(s) + CH4^| Al-CH3(s) + H2O ' Al-OH(s) + CH4^|

where (s) indicates a surface species.

ALD growth rates typically show only a weak dependence on substrate temperature. The ALD process window with respect to temperature is fairly large. Beyond a certain upper temperature limit, however, thermally activated decomposition of precursors sets in. At very low substrate temperatures, incomplete growth reactions may result in an increased impurity level in the deposited film. Novel and complex materials can be fabricated by combining two or more ALD processes. If chemistries and substrate temperature are chosen properly, two or more materials can be deposited sequentially or alternately by switching precursors. Thus, complex materials systems such as nanolaminates or compounds can be deposited with great compositional control[5], which may be difficult to achieve using conventional

deposition techniques. Figure 2 shows a nanolaminate fabricated by alternately depositing thin layers of Al2O3 and Hf aluminate into high aspect ratio trenches using ALD. ALD is considered to be a promising thin film deposition technology and has found widespread acceptance in the field of high-k dielectrics for both DRAM storage capacitor and CMOS gate applications. HfO2 and ZrO2 based materials are extensively being studied as potential replacement for existing SiO2 and SiON gate dielectrics[6]. HfO2, Al2O3, and Ta2O5 are well suited for DRAM capacitors[7,8]. Due to the high aspect ratios encountered in storage capacitors, ALD is a particularly attractive deposition technique. ALD also addresses the need for metal electrode deposition in DRAM capacitor and transistor gate applications. In the interconnect area, ALD is extremely useful for scaling of barrier and seed layers. DRAM tungsten contacts are expected to reach aspect ratios of = 12:1 in the sub-100nm regime. Aspect ratios are less demanding for CMOS applications, but seamless fills are required to prevent copper from diffusing through dimple holes after CMP. ALD TiN barrier films can be employed to cope with increasing aspect ratios. Moreover, ALD W nucleation layers have been reported which result in greatly improved film conformality and serve as an excellent starting surface for the subsequent W bulk fill. In addition, TaN ALD and W based ALD films are under consideration as barrier layers in Cu metallization. ALD is well suited for these applications, as it allows the deposition of very thin and defect-free layers.

Spacer applications are another area where ALD may be advantageous. Al2O3 based diffusion barriers for FeRAM have also been reported. Etch stop layers consisting of highly etch resistant materials can likewise be deposited by ALD.

ALD Step Coverage Performance

Aspect ratios in DRAM capacitors will continue to increase as the industry moves into the sub-100nm regime. Values of AR=60:1 and higher are expected for trench DRAM capacitor structures in future technology generations. Excellent step coverage performance of deposition processes at small ground rules will thus be an essential asset. A fundamental understanding of the dependence of ALD step coverage on process conditions is required to assess the extendibility of

ALD to smaller ground rules and higher aspect ratios[9]. In order to saturate the entire surface of a high aspect ratio structure with one of the ALD reactants, a sufficient amount of precursor has to be delivered to the wafer surface within a given time. Thus, the degree of conformality critically depends on precursor pulse time and precursor concentration or partial pressure. The exposure, which is the product of precursor partial pressure and time, is a useful measure of the number of precursor molecules available for absorption. The amount of precursor to which a specific location on the side wall of a feature on the wafer is exposed depends on gas transport in the reactor and gas transport inside the feature. Species transport inside high aspect ratio features with lateral dimension on the order of 100nm at pressures <100 Torr is in the Knudsen regime where the mean free path of the gas molecules is larger than the feature size. It turns out that the time required for species transport inside high aspect ratio structures actually makes up a significant portion of the overall saturation or pulse time. When precursor molecules enter a trench-like structure from the top, they diffuse into it and start saturating the side walls in a self-limiting zipper-like manner from top to bottom. By choosing appropriate exposure conditions, perfect step coverage can be obtained. Figure 3 demonstrates close to 100% step coverage of an 18 nm thick Al2O3 film in trenches with a minimal width of 80nm at an aspect ratio of ~ 60:1. This result and additional simulations[9] show that ALD is exceptionally well suited for deposition into high aspect ratio features at ground rules well below 100nm.

DRAM Requirements

DRAM technology with its 1-transistor/1-capacitor concept has long been at the leading edge of integrated circuit miniaturization. DRAM capacitor scaling has played a central role in this effort. In order to assure sufficient data retention time, a charge storage capacitance of 25-35fF/cell and cell leakage currents <1fA/cell are required and have to be maintained over the coming technology generations. Small cell size is crucial to allow minimal chip size and thus reduce chip cost. Three-dimensional capacitor structures with high aspect ratios are therefore commonly used in the DRAM industry. Infineon, Nanya, Winbond, and ProMOS as well as IBM and Toshiba for embedded DRAM utilize deep trench capacitors etched into the silicon substrate before the transistors are fabricated. Trench capacitors can endure a high thermal budget with temperatures in excess of 1000 . Stacked capacitors are used by companies such as Samsung, Micron, Elpida and Hynix. They are built above the transistor level either over or under bitline. Crown and cup shaped capacitors are widespread. The thermal budget linked to stacked capacitor fabrication is much lower than that for trench capacitors. With decreasing minimum feature size F there is less silicon real estate available for the capacitor. At constant capacitor aspect ratio, cell capacitance scales with 1/F2. The aspect ratio is primarily limited by etch constraints, geometrical limitations, and mechanical stability issues. Nonetheless, every effort will be made to maximize the capacitor surface area at a given ground rule. In trench DRAM technology, the capacitor surface area can be further increased by enlarging the trench circumference using silicon wet etch techniques. Surface roughening by growing hemispherical grain silicon (HSG) is another well established method to achieve area and thus capacitance increase[7].

High-k Dielectrics for DRAM Capacitors

Once the geometrical options to maintain sufficient capacitance at smaller ground rules have been exhausted, capacitor dielectrics with higher dielectric constant k offer an attractive path to achieving enhanced capacitance per area. Ta2O5 is the most widely studied high k material with applications in the DRAM industry. The material is used in MIS capacitors in conjunction with a suitable top electrode such as TiN. Both CVD and ALD processes are known for the deposition of Ta2O5. Ta2O5 is suitable for stacked capacitor applications but does not withstand the thermal budget required for trench DRAMs. The class of materials which are suitable for trench DRAMs includes pure Al2O3, HfO2-Al2O3 compounds or laminates, and Hf silicates. These dielectrics are stable up to high temperatures in contact with silicon and are being studied for CMOS applications as well. HfO2-Al2O3 also has attracted the attention of the stacked capacitor community[8]. Suitable ALD processes are available for both Al2O3 and HfO2. For implementation into trench capacitors, it is most straightforward to use a standard silicon-insulator-silicon (SIS) structure and replace the conventional nitride-oxide by a suitable high k material. In a second step, the inner or top electrode may be replaced by a metal (MIS structure) in an effort to eliminate the poly silicon depletion layer. A long-term option would be to implement a metal-insulator-metal (MIM) structure in order to get rid of any interfacial layers with low dielectric constant at the silicon-dielectric interface in SIS or MIS capacitors. MIM structures such as Ru/Ta2O5/Ru have been reported for stacked capacitors. For trench DRAMs, there is no immediate need to look into the MIM option.

Integration of Al2O3 into Fully Functional Trench DRAM Chips

Infineon has successfully integrated Al2O3 SIS trench capacitors into 128 Mb DRAM chips exhibiting full functionality.

A 170nm technology was used. ALD is an indispensable tool to achieve conformal coverage of the high aspect ratio trench structures with high quality Al2O3. The following process flow was used in the capacitor fabrication (Figure 4): After formation of the trench, Al2O3 was deposited by ALD. A post-deposition anneal was performed to densify the Al2O3 film. Then, poly silicon was filled into the trench. Following a poly recess, the Al2O3 film was removed in the

upper portion of the trench and an isolation collar was formed. Finally, poly silicon was once again filled into the trench.

A cross-sectional view of a fully integrated trench DRAM cell with Al2O3 SIS capacitor is shown in the TEM image of Figure 5. The insert (a) confirms the stability of the ~ 5nm thick Al2O3 layer. Al2O3 is extremely inert in contact with silicon. The image also demonstrates the polycrystalline nature of the Al2O3 after it has been subjected to the full thermal budget of the trench DRAM process. Insert (b) shows the intersection of the Al2O3 film and the SiO2 isolation collar. The image demonstrates that the Al2O3 was successfully removed prior to collar formation. A cell capacitance enhancement of 20% was achieved while leakage currents remained below 1fA/cell. Interestingly, the fact that the Al2O3 is in a polycrystalline phase does not lead to any drastic increase in leakage current and demonstrates that amorphicity is not a prerequisite for excellent electrical properties. The retention characteristics of Al2O3 based DRAM cells was significantly improved over that of NO based cells (Figure 6). Reliability measurements on trench capacitors at package level revealed an extrapolated lifetime of more than 10 years (Figure 7). The wafer map in Figure 8 represents the test yield for 128 Mb chips with Poly-Si/ Al2O3/Si capacitors fabricated in 170nm technology and demonstrates excellent wafer level yield. Excellent package level yields have also been achieved. Electrical results depend to a large degree on the pre-treatment of the silicon surface before ALD deposition and on the post-treatment applied after Al2O3 deposition. Poly-Si deposition conditions also play an important role. Various interface preparation techniques were compared including wet and RTP treatments. It is known that a suitable starting surface is required in order to achieve uninhibited layer-by-layer growth at the start of the ALD deposition. A thin oxide or nitride layer is required at the interface. Si surfaces prepared by an HF last clean show a long incubation time and lead to inferior film quality[10]. Naturally, leakage current and dielectric film thickness are directly related. Figure 9 shows a plot of leakage current versus capacitance equivalent thickness (CET) for a series of Al2O3 films of various thicknesses. The exponential dependence of leakage current on CET is clearly visible. The high-k film thickness has to be chosen such that the leakage current specification of <1 fA/cell is met.

Integration of Metal into Trench DRAM Capacitors

Metal electrodes or metal fills are anticipated for ? 70nm ground rules. A metal fill would significantly reduce series

resistance of the inner electrode of a trench capacitor. The use of a metal electrode would eliminate the poly silicon depletion effect and help to further reduce CET. Thermal stability of the metal in contact with adjacent layers is crucial.

The integrity of a TiN/Poly-Si/NO/Si MSIS structure upon annealing was investigated. The TiN layer was deposited by ALD on top of a thin Poly-Si buffer layer which is in direct contact with the NO dielectric layer inside a high aspect ratio trench. This MSIS trench structure was subjected to various post anneals. Both capacitance and leakage current remained stable even after annealing at 1000°C demonstrating the high thermal integrity of the TiN MSIS material system. Small resistivity values of <100 μOhmcm were observed after high temperature annealing. 80% step coverage was achieved for 20nm TiN deposited by ALD into trenches with AR >40. This is in perfect agreement with the metal fill requirements for trench DRAM. 70-80% step coverage is adequate to guarantee sufficiently low series resistance down to the bottom of the trench.

ALD Equipment Issues ALD equipment is now being adopted by the semiconductor industry for a number of applications. ALD system maturity has been advanced significantly in recent years. Commercially available systems at Infineon have shown good overall process repeatability, excellent thickness uniformity, low particle counts, and reasonable throughput. Nonetheless, there are areas that require improvement. The number of wafers between cleans has to be increased. Likewise, the chamber cleaning procedures need to be optimized. Ideally, in-situ cleaning capability for ALD chambers should be made available. However, isotropic removal of materials such as Al2O3 and HfO2 from the reactor walls may not be straightforward and needs to be studied in detail.

Summary

Atomic Layer Deposition is gaining increasing momentum in the semiconductor industry. ALD offers significant advantages over conventional deposition processes with respect to step coverage, uniformity, film thickness control, and film quality.

Infineon is actively pursuing ALD for a number of applications, among them high-k dielectric and metal electrode deposition for DRAM storage capacitors. For the first time, fully functional 128 Mb DRAM chips with ALD Al2O3 trench capacitors have successfully been fabricated in 170nm technology. The excellent step coverage control achieved with ALD will be an essential asset as trench capacitors are scaled to ever smaller dimensions and higher aspect ratios.

References

[1] PD Agnello, Process requirements for continued scaling of CMOS - the need and prospects for atomic-level manipulation, IBM J. Res. & Dev., 46 (2002) 317

[2] H Seidl et al, A fully integrated Al2O3 trench capacitor DRAM for sub-100nm technology, IEDM (2002)

[3] Mikko Ritala and Markku Leskela, Atomic Layer Deposition, Handbook of Thin Film Materials, V ol. 1: Deposition and Processing of Thin Films, ed. H.S. Nalwa (2002) 103

[4] AW Ott et al, Al2O3 thin film growth on Si(100) using binary reaction sequence chemistry, Thin Solid Films 292 (1997) 135

[5] O Sneh et al, Thin film atomic layer deposition equipment for semiconductor processing, Thin Solid Films 402 (2002) 248

[6] GD Wilk et al, High k gate dielectrics: Current status and materials properties considerations, J. Appl. Phys. 89 (2001) 5243

[7] M Gutsche et al, Capacitance enhancement techniques for sub-100nm trench DRAMs, IEDM (2001) 411

[8] J-H Lee et al, Practical next generation solution for stand-alone and embedded DRAM capacitor, VLSI (2002) 114

[9] U Schroeder et al, Experimental and theoretical investigation of ALD step coverage in high aspect ratio trenches,

A VS ALD Conference 2002, Seoul

[10] H Bender et al, Physical characterization of high k gate stacks deposited on HF-last surfaces, IWGI (2001) 86

*2003.7 FutureFAB

SD高达G世纪攻略:全角色可习得技能(1) 原创系 マーク 熟练统制机敏冷徹豪杰统率力威风必杀历战の勇士エース ラナロウ 好战恶运解放空中战斗适应气合 操舰センス对空炮火佣兵历战の勇士ペテラン エリス 真面目强固幸运热血補佐刻苦统制空间认识能力战场の女神ペテラン ゼノソ 统率力熟练解放威风豪杰集中力铁壁勇将历战の勇士ペテラン ケレア ムードメイカー素人空间认识能力好战ポジティブカリスマ幸运必杀战场の女神练达 ジュナス 情报解析气合解放怒り集中力射击管制强固底力历战の勇士ファイター エルソスト 操舰センス气分屋解放熟练底力对空炮火豪杰地上战斗适应历战の勇士ペテラン ケイ 机械技术豪杰解放气合威压器用熟练恶运战场の女神练达 レィチェル カリスマ铁壁身轻集中力底力气合幸运空间认识能力战场の女神スナイパー ツェルド 热血真面目解放铁壁气合机械技术器用底力历战の勇士エース ピリー

单独行动挑拨解放冷徹威压操舰センス对空炮火底力历战の勇士必杀 ニキ 補佐寡默解放冷徹集中力统率力威风勇将战场の女神ペテラン ラ·ミラ 情报解析素人解放怒り恐怖 射击管制强固单独行动战场の女神必杀 マリア 集中力エリート解放强固热血操舰センス对空炮火统制战场の女神练达 フローレソス 威压狡猾怒り豪杰恐怖 情报解析射击管制冷徹战场の女神必杀 エルフリーデ 骑士道エリート解放铁壁气合统率力威风必杀战场の女神ファイター イワソ ニュータイプムードメイカー恶运挑拨机敏隐密豪杰プレッシャー历战の勇士见切 エターナ 慈爱机敏真面目空间认识能力身轻 カリスマ幸运集中力战场の女神スナイパー エイブラム 豪杰统制解放威压怒り 机械技术器用斗将历战の勇士ペテラン ブラッド 冷徹单独行动解放怒り恐怖補佐统制豪杰历战の勇士佣兵 ブランド 恐怖统率力解放挑拨威风熟练好战怒り历战の勇士练达 カチュア サイキッカーポジティブ身轻热血好战 カリスマ幸运ムードメイカー战场の女神ファイター ツス 强化人间寡默真面目单独行动冷徹刻苦補佐プレッシャー战场の女神スナイパー ジェネレーション 见切刻苦慈爱熟练气合统制练达必杀ペテランエース

底框结构设计规范 一.一般规定 1.根据《抗规》7.1.2表中所述底框结构上部砌体最小厚度为240mm,房屋最高限值及层数: 6,7度 22m 7层;8度19m 6层;9度区不容许采用这种形式。 2.底框层高不得大于4.5m。 3.底部框架-抗震墙房屋的结构布置,应符合下列要求: 1)上部的砌体抗震墙与底部的框架梁或抗震墙应对齐或基本对齐。 2)房屋的底部,应沿纵横两方向设置一定数量的抗震墙,并应均匀对称布置或基本均匀对称布置。6、7度且总层数不超过五层的底层框架-抗震墙房屋,应允许采用嵌砌于框架之间的砌体抗震墙,但应计入砌体墙对框架的附加轴力和附加剪力;其余情况应采用钢筋混凝土抗震墙。 3)底层框架-抗震墙房屋的纵横两个方向,第二层与底层侧向刚度的比值,6、7度时不应大于2.5,8度时不应大于2.0,且均不应小于1.0。 4)底部两层框架-抗震墙房屋的纵横两个方向,底层与底部第二层侧向刚度应接近,第三层与底部第二层侧向刚度的比值,6、7 度时不应大于2.0 ,8度时不应大于1.5,且均不应小于1.0。 5)底部框架-抗震墙房屋的抗震墙应设置条形基础、筏式基础或桩基。 4.底部框架-抗震墙房屋的框架和抗震墙的抗震等级,6、7、8度可分别按三、 二、一级采用。 5.底框层砼等级不得低于C30。 二.计算方法及要点 1.计算方法:底部框架房屋可采用底部剪力法,并应按第2点规定调整地震作用效应。 2.底部框架-抗震墙房屋的地震作用效应,应按下列规定调整: 1)对底层框架-抗震墙房屋,底层的纵向和横向地震剪力设计值均应乘以增大系数,其值应允许根据第二层与底层侧向刚度比值的大小在1.2~1.5范围内选用。 2)对底部两层框架-抗震墙房屋,底层和第二层的纵向和横向地震剪力设

A线 01:刚大木起动(0079) Break1:骡子(阿姆罗)击破面前的扎古 Challenge1:骡子(阿姆罗)用光束军刀击破面前的大叔 游戏开始:阿姆罗出现在地图中央,下方为扎古。 话说大家都是新存档,除了个系统配置的机体就只有Master是自选的。 江口是个鸡神迷,因为世界里脉冲很快就能开发出SF,所以果断选了飞鸟,然后买了73鸡(题外话) 其实第一个Break很容易能完美完成,利用两台旋风攻击下方的一台扎古,凤凰零式打另一台,打残了就让Master出来捡。第一回合骡子不攻击,向下走,然后收了两台扎古的Master 可以拉上来,做好跟阿姆罗汇合的准备。然后回合结束,大叔砍阿姆罗,用光束军刀反击,第二轮再用光束军刀攻击,Master作支援。然后果断地秒了大叔。挑战成功。 Break2:AGE1击破UE一台机体 Challenge2:AGE1用光束军刀击破UE一台机体 Break1后,AGE出现在阿姆罗上方,UE机体出现在扎古下方。 AGE1跑了出来(挑战任务是某个运气一流的傻子,无视掉)同样是AGE1用光束军刀击破,

但目标是一部UE(貌似是吧,我对AGE表示毫不知情)的机体即可。 类似第一次进行作业即可。各机体残血就会战舰,不要觉得浪费时间。 Over:4个回合内基拉击破阿斯兰 Break2后,基拉会驾驶者强袭高达出现在AGE上方,阿斯兰则驾驶者圣盾高达连同小弟等出现在UE下方。 要完成还是不难,强袭高达想下方走,,同时大天使号跟上,AGE1、元祖靠近强袭高达,然后用战舰引诱阿斯兰上来(这个就要说到江口的Master了,其实没有也没什么危险,但C.E.73基拉的Master技能刚好是100%miss,不用白不用,给战舰加一个,上去勾引敌人一流) 不断引诱圣盾高达上来,同时强袭高达下去,理论上第三回合就会遭遇上,但可能强袭高达攻击不到圣盾高达,然后在第三回合将Master、元祖、AGE都放在基拉旁边,第四回合,支援攻击,圣盾高达被击破,Over成功。对于有人说Over后很难打,其实不是。只要一开始大天使号跟着强袭高达拉下来,在Over之前放到自己的母舰附近,然后Over成功,全部机体秒着大天使号的弱点来攻击,加上战舰的援护,必要时Master插一刀,绝对没问题。大天使号废了,那么强袭就可以没收了。然后要杀死元祖、AGE1,和剩下的杂兵,其实不难。 编者在这里刷了四次,把Basic脉冲刷到10级,换了台脉冲命运。 02:另一对好基友的诞生(0083) Break1:高达试作1号机与高达试作2号机交战 Challenge1:高达试作1号机用光束军刀与高达试作2号机交战 游戏开始,宏和战舰在地图中央,卡多和四个基友在宏的右方。 其实是很简单的,一出来直接GP01冲前激光枪就可以了。如果要挑战的话就不用那么急,卡多会逃走的,让他逃,慢慢追。直到右边沙漠,此时卡多会跑不了的(等基友过来)。然后用GP01的光束军刀一砍,KO。

1 建筑设计 1.1设计依据 (1)建设单位认可de总体规划及单体初步设计方案; (2)建设单位提供de设计任务书; (3)建设单位提供de基础设计资料 (4)国家及地方现行de有关设计规范、标准及规程、规定 (5)结构、给水排水、通风空调、电气燃气、通讯信息等专业队建筑专业de各项技术要求 (6)有关规范: 《民用建筑设计通则》JGJ37-83 《建筑设计防火规范》GBJ16-87 《屋面工程质量验收规范》GB50207-2002 《砌体结构设计规范》GB50003-2001 《建筑结构荷载规范》GB50009-2001 《混凝土结构设计规范》GB50010-2002 《建筑抗震设计规范》GB50011-2001 《建筑地基基础设计规范》GB50007-2002 1.2设计要求 本工程建筑耐久等级为二级..耐久年限为50年..抗震设防烈度为7度..内部功能主要满足居住及商业用房功能、防火、疏散等要求..建筑外形简洁明快..体现建筑特征及建筑风格。 1.3工程概况 本工程为句容市农贸街东侧C地块住宅..地上五层..一层为框架..以上为砖混结构..建筑高度为17.9m..总建筑面积为3053.7m....一层层高为 4.2..以上层高均为 2.9m..室内外高差0.15m。二类建筑..建筑耐火等级为二级..火灾危险性为轻危险级..屋面防水等级为三级..地震设防烈度为七度..抗震等级为二级..砌体施工质量控制等级为B级..地震设计加速度为0.1g。

图1-1建筑正立面图 图1-2底层平面建筑图:1.4具体设计内容 (1)各层平面设计(2)楼梯剖面设计(3)楼梯放大图、节点详图 2 结构设计 2.1设计依据及要求 2.1.1设计依据 (1)工程设计使用年限为50年

首先,开始的第一话(Area-X 第一关)本人日文比较低,标题翻译水平有限,免得献丑,大家看图认关吧。 游戏开始说完一大推对白后,我们可以见到上方有3只数码暴龙,下面有3只OO剧场版的杂兵(ELS) HP8000,很水皮的,他们旁边的墨镜男也能够一招一只),这里不截图了。 看一下胜败条件 胜:敌军机体全灭 败:1.母舰沉没2.AGE主角机体坠毁(本人对日文仅有少少认识,别见怪。) 再是世纪破碎(打破?)的条件 蓝色是:2回合内,AGE主角(下面用A表示)与蓝色数码暴龙交战。 橙色是:1回合内,A与蓝色数码暴龙交战。 见见三只数码暴龙(EU)吧 灰色HP12500 应该要2台援助才能一下打死;蓝色(下面那两只)HP10000,装甲比较弱,1台机援助就可以干掉。 注意了,如果想赚经验的,就先干掉蓝色,再打灰色,不然干掉灰色后蓝色会一起逃跑;还有一点,灰色大约剩下1/3血的时候也会带着兄弟一同逃跑。 1回合与蓝色EU交战非常容易,只要将A开至最上就可以了。只要不像我那样用一道机体墙把他们分开,橙色破碎是非常容易的。 当A与蓝色EU交战后克瓦多罗会开着百式带着两个手下从右边角落出来。这里只要击落百式,就可以不抓他的两个手下,要机要经验,就看自己了。 然后是新的破碎条件 蓝色:墨镜男与百式交战 然后由于打破了橙色破碎,会有特殊单位出场 正如上图所见,Mr武士道,由于第一关,即便是特殊单位,也是很水皮的。 幹掉Mr.武士道會掉一個移動+1的OP(感谢楼下提示) 另外,如果、一旦、万一手贱走错了,错过了A第一回合与蓝色EU交战的话,也不怕,只要第二回合交战,虽然第一个橙色失败了,但也会出现一个新的橙色破碎。这样也能3星完成任务的。 新的破碎条件: 蓝色:墨镜男与百式交战(- -!突然发现,原来是两个墨镜男的战斗....) 橙色:击毁3台ELS(下面尖头的3只)后,墨镜男与百式交战

底框结构注意问题 ▲ 底框结构上部砖混荷载? ●底框结构里程序自动会把上部砖混荷载传至底框,不用自己再加 ●用STAWE算底框是,砌体方面有一个选项: 1.按PM主菜单8算法; 2.有限元整体算法. 此处应该选1!!!有限元整体算法对底框不太准,只供参考(PKPM技术人员说的) ▲ sat-8计算底框时,结构体系选什么? ●引用《pkpm新天地》2004年第5期咨询台的信息: 计算砖混底框时,satwe第一项中的结构体系参数已经失效。 所以在计算底框时,satwe第一项中的结构体系参数无论选框架还是框剪结构都是无用的。▲ 底框建模问题: (1)建模时在底层砼抗震墙处我同时输入砼抗震墙和框架梁是否正确?有开洞的墙处我将洞口直接开到框架梁底,这样对吗? ●可以同时输入抗震墙和框架梁,框架梁作为边框梁。若是底部二层框架时,中间一层可以不用输入抗震墙。洞口可以直接开到框梁底。 (2)在PM楼层组装里面的设计参数里,总信息里结构主材应填什么?材料信息里主要墙体材料又该怎样填? ●在PM地设计参数应当填“底框”,结构主材可以填混凝土。在SATWE-8中的材料信息中应当填砌体。 (3)SATWE-8算完后,发现连梁超筋,而在墙洞上方有框梁,这是怎么回事? ●底框主梁直接可按规范要求计算,应考虑荷载直接作用在梁上,超筋就调整梁断面尺寸。(4)平法绘图时,应该将框架柱旁的墙肢与柱一起画配筋吗? ●既然柱与墙肢接在一起,那柱是构造边缘构件,应当查计算结果中抗震墙中的计算结果,按边缘构件配筋并画在一起。 ▲ 新规范中第7.1.8条1款要求底部框架-抗震墙房屋结构布置中,上部砌体抗震墙与底部框架梁或抗震墙对齐或基本对齐,在定量上如何把握? ●底框房屋是一种不利于抗震的结构类型。为提高其抗震能力,《建筑抗震设计规范》(GB50011-2001)中7.1.8条1款要求,上部砌体抗震墙与底部的框架梁或抗震墙的轴线对齐或基本对齐,即大部分砌体抗震墙由下部的框架主梁或钢筋混凝土抗震墙支承,每单元砌体抗震墙最多有二道不落在框架主梁或钢筋混凝土抗震墙上,而是由次梁支托上部抗震墙。

底框结构设计规范 一、一般规定 1、根据《抗规》7、1、2表中所述底框结构上部砌体最小厚度为240mm,房屋最高限值及层数:6,7度22m 7层;8度19m 6层;9度区不容许采用这种形式。 2、底框层高不得大于4、5m。 3、底部框架-抗震墙房屋得结构布置,应符合下列要求: 1)上部得砌体抗震墙与底部得框架梁或抗震墙应对齐或基本对齐。 2)房屋得底部,应沿纵横两方向设置一定数量得抗震墙,并应均匀对称布置或基本均匀对称布置。6、7度且总层数不超过五层得底层框架-抗震墙房屋,应允许采用嵌砌于框架之间得砌体抗震墙,但应计入砌体墙对框架得附加轴力与附加剪力;其余情况应采用钢筋混凝土抗震墙。 3)底层框架-抗震墙房屋得纵横两个方向,第二层与底层侧向刚度得比值,6、7度时不应大于2、5,8度时不应大于2、0,且均不应小于1、0。 4)底部两层框架-抗震墙房屋得纵横两个方向,底层与底部第二层侧向刚度应接近,第三层与底部第二层侧向刚度得比值,6、7度时不应大于2、0,8度时不应大于1、5,且均不应小于1、0。 5)底部框架-抗震墙房屋得抗震墙应设置条形基础、筏式基础或桩基。 4、底部框架-抗震墙房屋得框架与抗震墙得抗震等级,6、7、8度可分别按三、 二、一级采用。 5、底框层砼等级不得低于C30。 二、计算方法及要点

1、计算方法:底部框架房屋可采用底部剪力法,并应按第2点规定调整地震作用效应。 2、底部框架-抗震墙房屋得地震作用效应,应按下列规定调整: 1)对底层框架-抗震墙房屋,底层得纵向与横向地震剪力设计值均应乘以增大系数,其值应允许根据第二层与底层侧向刚度比值得大小在1、2~1、5范围内选用。 2)对底部两层框架-抗震墙房屋,底层与第二层得纵向与横向地震剪力设计值亦均应乘以增大系数,其值应允许根据侧向刚度比在1、2~1、5范围内选用。 3)底层或底部两层得纵向与横向地震剪力设计值应全部由该方向得抗震墙承担,并按各抗震墙侧向刚度比例分配。 3、底部框架-抗震墙房屋中,底部框架得地震作用效应宜采用下列方法确定:1)底部框架柱得地震剪力与轴向力,宜按下列规定调整: a、框架柱承担得地震剪力设计值,可按各抗侧力构件有效侧向刚度比例分配确定;有效侧向刚度得取值,框架不折减,混凝土墙可乘以折减系数0、30,砖墙可乘以折减系数0、20。 b、框架柱得轴力应计入地震倾覆力矩引起得附加轴力,上部砖房可视为刚体,底部各轴线承受得地震倾覆力矩,可近似按底部抗震墙与框架得侧向刚度得比例分配确定。 2)底部框架-抗震墙房屋得钢筋混凝土托墙梁计算地震组合内力时,应采用合适得计算简图。若考虑上部墙体与托墙梁得组合作用,应计入地震时墙体开裂对组合作用得不利影响,可调整有关得弯矩系数、轴力系数等计算参数。 4、如底框中抗震墙采用嵌砌于框架之间得普通砖抗震墙,符合《抗规》第7、 5、6条得构造要求时,其抗震验算应符合下列规定: 1)底层框架柱得轴向力与剪力,应计入砖抗震墙引起得附加轴向力与附加剪力,其值可按下列公式确定:

A 01 木马出航ス! 胜利条件: 击破敌方所有所有机体。 失败条件: Master击破或者我方全灭。 白色木马被击破。 世纪爆发: 爆发1 爆发条件:用阿姆罗的高达击破夏亚的扎古。 挑战任务:一回合内用阿姆罗的高达击破夏亚的扎古。 爆发2 爆发条件:用卡缪的高达MK-II击破杰利多的高扎古。 敌方初期ACE 夏亚.阿兹纳布尔机体 MS 夏亚专用扎古F 捕获机体 扎古F 本关简述: 系列的惯例,一上来就是阿姆罗与夏亚...对于初次进行游戏的玩家,挑战任务估计有些困难,不过没关系,这个到后面再打也是可以的。开始的扎古性能不是很高,所以还算比较轻松。第一次世纪爆发后,地图下方出现我方的卡缪与敌方的杰利多。虽说机体性能看起来挺强(对比初始机体),不过也是一群纸老虎罢了,如果不考略经验问题,用卡缪可以轻松应付。第二次世纪爆发后,地图上方出现大叔和桃子的铁人部队,实力中上,尽量用主力去迎击。 A 02 崩壊の大地 胜利条件: 击破敌方所有所有机体。 失败条件: Master击破或者我方全灭。 大天使号被击破。 世纪爆发: 爆发1 爆发条件:基拉与阿斯兰交战。 挑战任务:两回合内让基拉与阿斯兰交战。 爆发2 爆发条件:用罗的Astray击破两台金恩。 敌方初期ACE 阿斯兰.萨拉机体 MS 圣盾高达 捕获机体 金恩镇暴型吉姆 本关简述: SEED的经典一幕,小基基与阿斯兰的打情骂俏...SEED的量产机体能力不是,所以金恩几乎不是威胁。爆发1的条件很好达到,能过就尽量过吧。爆发1后罗开着捡来的Astray 出现在地图右方。如果挑战任务完成,那么在左方0083凯利会开着MA瓦尔出现,能力有些让人头痛,所以最好多在右方多布置些兵力。爆发2开始后地图的左方有会出现Z的经典反派三人众,能力中上,但也很好对付,多利用战舰与队友援护可以更容易的对付他们。

A线 01:01是0079的第一集剧情,也就是我们的第一台刚大木起动的时候。 第一个Break的条件是骡子击破面前的扎古。 话说大家都是新存档,除了个系统配置的机体就只有Master是自选的。 编者是个鸡神迷,因为世界里脉冲很快就能开发出SF,所以果断选了飞鸟,然后买了73鸡(题外话) 挑战任务则是骡子用光束军刀击破面前的大叔。 其实第一个Break很容易能完美完成,一开始,两台旋风打下面的一台扎古,凤凰零式打一台,打残了就让Master出来捡。第一回合骡子不攻击,向下走,然后收了两台扎古的Master 可以拉上来,做好跟骡子汇合的准备。然后回合结束,大叔砍骡子,用光束军刀反击,第二轮再用光束军刀攻击,Master作支援。然后果断地秒了大叔。挑战成功。 第二次Break,AGE1跑了出来(挑战任务是某个运气一流的傻子,无视掉)同样是AGE1用光束军刀击破,但目标是一部EU(貌似是吧,我对AGE表示毫不知情)的机体即可。 类似第一次进行作业即可。各机体残血就会战舰,不要觉得浪费时间。

第二次Break之后,出来了Over(不上图了),同时71鸡、大天使、71狼跑出来,继续上演基情无限的呀灭罗!!!! Over条件为四个回合鸡杀狼。 要完成还是不难,将71鸡拉下来,同时大天使号跟上,AGE1、元祖靠近71鸡,然后用战舰引诱狼上来(这个就要说到编者的Master了,其实没有也没什么危险,但73鸡的Master 技能刚好是100%miss,不用白不用,给战舰加一个,上去勾引人一流) 不断引诱狼上来,同时鸡下去,理论上第三回合就会遭遇上,但可能71鸡攻击不到狼,然后在第三回合将Master、元祖、AGE都放在71鸡旁边,第四回合,攻击围观,狼死,Over 成功。对于有人说Over后很难打,其实不是。只要一开始大天使号跟着71鸡拉下来,在Over之前放到自己的母舰附件,然后Over成功,全部机体秒着大天使号的弱点来攻击,加上战舰的援护,必要时Master插一刀,绝对没问题。大天使号废了,那么强袭就可以没收了。然后要杀死元祖、AGE1,和剩下的杂兵,其实不难。 编者在这里刷了四次,把Basic脉冲刷到10级,换了台脉冲命运。 02:02是0083,另一对好基友的诞生场景。 Break1:基友交战,如果不想挑战任务的话,其实是很简单的,一出来直接GP01冲前激光枪就可以了。如果要挑战的话就不用那么急,卡多会逃走的,让他逃,慢慢追。直到右边沙

游戏系统: 本次SD高达在战场方面和PS的《吉伦的野望》相近,MS可以最大三部组成一个小队,而大型(L型)的MS或是MA就只能一队一部了。小队还可以合并,比如A小队有两部小型MS,而B小队只有一部小型MS,这时B小队就可以移动到A小队上合并成一个小队。 战斗中的小队指令菜单: 移动:分为单体移动和全体移动,顾名思义,单体移动就是只移动小队中某一部机体,而全体移动就是全小队一起移动,注意这时的移动力是按移动力最低的单位来算的。 队列:编成小队的队列,小队的一号队员只能攻击敌方小队的一号队员,二号和三号依此类推,但是当敌人小队的战斗单位小于我方小队战斗单位的时候,我方多出来的小队成员会向敌小队一号队员进攻(例如我方有三名队员,而敌方只有两名,这时我方的第三名队员就会攻击敌方的第一名队员)。利用队列的战术也很多,比如敌小队二号队员的实弹武器攻击力很高,而我方小队里恰好有SEED系的高达,这时候就可以将我方SEED系的高达调至二号,然后就可以利用SEED系高达的PS装甲来防御住敌人的实弹攻击了。 攻击:直接攻击只能攻击邻接的敌人,有六方向,选定攻击目标小队后进入设置画面,此时可以选择武器攻击,回避和ID。射击攻击有残弹限制,格斗武器无限制,有些武器是消耗机师的SP的;选择回避的话,选择回避的机体本次不参与攻击但是回避率得到提升。ID相

当于机器人大战中的精神指令,就是原作中该机师比较著名的台词,使用后可以提升机师或是机体的能力,有SP限制。攻击时射击攻击会先制于格斗攻击,即攻方射击->守方射击->攻方格斗->守方格斗,不过有时机师也能发动先制攻击。 间接:此指令一般为母舰或是炮击型MS单位所有(比如钢加农等),选择此指令后可以选择长距离炮击型武器对敌小队实施远程打击,被攻击的敌小队无法反击,但是可以选择“散开”指令来躲过攻击,但是散开后可能因为落单而被各个击破,且当四周围都有小队在的时候无法散开(总不能站人家头上去吧……),有的机师拥有阻止散开的ID,这种机师一定要给他分配具有强力远程武器的机体啊。 ID:在战斗地图画面的菜单里的ID一般是使用对我方大范围有效的ID,例如主舰的舰长可以使用散布米粒子的ID来增强指挥范围内我方机体的回避能力。 变形:某些MS具有变形能力,可变成MA等。 捕获:机体和资金的重要来源,要想得到好的机体或是抢来敌人机体拿去卖钱的话,就要靠这一着了。当我方有将敌人包围时(三个小队与敌人邻接,位置不限定,包围的小队越多,成功率越高)出现,还会有成功率提示(BOSS机无法捕捉),是抓是杀全在于玩家了,有的机师拥有可以提升捕获率的ID,一定要善加应用。 交信:相当于机器人大战里的“说得”选项,当战场中可以发生对话的两名机师所在小队邻接的时候就会出现,此时可以对敌方角色进行说得等。熟悉原作的玩家应该记得在什么情节

[整理版]SD高达G世纪超越世界流程攻略A线 01:01是0079的第一集剧情,也就是我们的第一台刚大木起动的时候。 第一个Break的条件是骡子击破面前的扎古。 话说大家都是新存档,除了个系统配置的机体就只有Master是自选的。编者是个鸡神迷,因为世界里脉冲很快就能开发出SF,所以果断选了飞鸟,然后买了73鸡(题外话) 挑战任务则是骡子用光束军刀击破面前的大叔。 其实第一个Break很容易能完美完成,一开始,两台旋风打下面的一台扎古,凤凰零式打一台,打残了就让Master出来捡。第一回合骡子不攻击,向下走,然后收了两台扎古的Master可以拉上来,做好跟骡子汇合的准备。然后回合结束,大叔砍骡子,用光束军刀反击,第二轮再用光束军刀攻击,Master作支援。然后果断地秒了大叔。挑战成功。

第二次Break,AGE1跑了出来(挑战任务是某个运气一流的傻子,无视掉)同样是AGE1用 光束军刀击破,但目标是一部EU(貌似是吧,我对AGE表示毫不知情)的机体即可。类似第一次进行作业即可。各机体残血就会战舰,不要觉得浪费时间。第二次Break之后,出来了Over(不上图了),同时71鸡、大天使、71狼跑出来,继续上演基情无限的呀灭罗~~~~ Over条件为四个回合鸡杀狼。 要完成还是不难,将71鸡拉下来,同时大天使号跟上,AGE1、元祖靠近71鸡,然后用战舰引诱狼上来(这个就要说到编者的Master了,其实没有也没什么危险,但73鸡的Master技能刚好是100%miss,不用白不用,给战舰加一个,上去勾引人一流) 不断引诱狼上来,同时鸡下去,理论上第三回合就会遭遇上,但可能71鸡攻击不到狼,然后在第三回合将Master、元祖、AGE都放在71鸡旁边,第四回合,攻击围观,狼死,Over成功。对于有人说Over后很难打,其实不是。只要一开始大天使号跟着71鸡拉下来,在Over之前放到自己的母舰附件,然后Over 成功,全部机体秒着大天使号的弱点来攻击,加上战舰的援护,必要时Master插一刀,绝对没问题。大天使号废了,那么强袭就可以没收了。然后要杀死元祖、AGE1,和剩下的杂兵,其实不难。 编者在这里刷了四次,把Basic脉冲刷到10级,换了台脉冲命运。

底框结构的计算 过去,PKPM对底层框架上部砖房结构的设计过程是: 1. 用PMCAD主菜单8作整体结构分析并得出底框的地震力; 2. 用PMCAD主菜单4对底层框架部分逐个提取每榀框架; 3. 用PK的平面杆系有限元分析功能逐个计算每榀框架,并用PK其它菜单画底框施工图。 以上的方法对底框部分的计算及绘图效率都较低,SA TWE软件新增了底框结构空间分析功能,并提供了两种分析方法: 方法一,接PMCAD主菜单8的规范算法,即“建筑抗震设计规范GB50011-2001”规定的简化方法。它将计算分为两步,第一,仍用PMCAD主菜单8的基底剪力法作整体结构分析并得出底框层的地震力,其次,将上部砖房与底部框架分离开,并使底部框架接收上部砖房传来的恒荷载、活荷载及地震力〔包括倾覆力矩〕,最后,仅对底框部分用SA TWE进行空间分析。 方法二,有限元整体算法。将上部砖房和底框作为一个整体,考虑砖混底框结构的特点,采用空间组合结构有限元方法进行分析,这种方法也适用于其它各种砌体结构。 用以上两种方法计算后,对底框部分的画图可以用SA TWE接力PK画图方式,即全楼归并后的成批挑选梁柱画图。对梁的画图程序自动加上底框构造。比以前的底框画图方式要灵活的多了。 下面就SA TWE软件的应用作如下归纳: 一、操作流程 在PKPM系列CAD软件中,PMCAD是结构部分的基础模块,通过PMCAD的建模功能(主菜单1、2、3)形成结构的几何数据和荷载数据文件,其它软件模块均要读取上述两组文件。 1.PMCAD主菜单8的砖混底框抗震验算 对于底框结构,完成结构建模以后,首先要执行PMCAD主菜单8,进行砖混底框结构的抗震验算,其主要是完成以下两项工作: l 按基底剪力法计算结构的地震作用(地震剪力和倾覆力矩),并对上部砖房进行抗震验算。 l 竖向导荷计算,把上部砖房的恒、活荷载和自重按支承几何关系传递到底框部分,作为底框部分空间分析的外荷载。 在PMCAD的这步操作中,有关参数的含义和作用可参见PMCAD说明书,其中“考虑墙梁

【SD高达G世纪超越世界】各强力机体开发路线 量子型00高达:凤凰高达LV4--能天使(basic)LV6 --能天使高达LV4--00高达 LV4--00 Raiser LV4--00 Raiser(决战装) LV5--量子型00高达 能天使高达可以在B05关卡中的OVER阶段可以捕获 (不过打到B05前早可以开发出来) 强袭自由高达:凤凰高达LV4--强袭高达(basic) LV5--强袭嫣红LV4--拂晓LV4--自由高达LV4--强袭自由高达 无限正义高达:凤凰高达LV4-- 强袭高达(basic) LV5-- 强袭嫣红LV4-- 拂晓LV4-- 正义高达 LV4--无限正义高达 强袭高达可以在A01关卡中的OVER阶段可以捕获强袭高达LV3--强袭嫣红 Hi-ν高达(海牛):凤凰高达LV6--凤凰高达(能力解放) LV4--RX-93 ν(basic) LV10--RX-93 ν LV5--Hi-ν高达(海牛) V2ab高达:凤凰·零 LV4--V高达(basic) LV8--V高达 LV5--V2高达 LV4--V2ab高达 命运高达:凤凰高达(能力解放) LV4--脉冲高达(basic)LV8 --脉冲高达LV4--命运脉冲高达LV4--命运高达 凤凰高达(能力解放) LV4-- 脉冲高达(basic)LV10 -- 命运脉冲高达LV4-- 命运高达 脉冲高达可以在A03关卡中的OVER阶段可以捕获 飞翼高达零式改(EW) :凤凰高达(能力解放) LV4-- 飞翼高达(basic) LV8-- 飞翼高达(EW) LV5-- 飞翼高达零式改(EW) 凤凰高达(能力解放) LV4--飞翼高达(basic) LV5--飞翼高达LV3--飞翼高达(EW) LV5--飞翼高达零式改(EW)

过去,PKPM对底层框架上部砖房结构的设计过程是:1.用PMCAD主菜单8作整体结构分析并得出底框的地震力;2.用PMCAD主菜单4对底层框架部分逐个提取每榀框架;3.用PK的平面杆系有限元分析功能逐个计算每榀框架,并用PK其它菜单画底框施工图。 以上的方法对底框部分的计算及绘图效率都较低,SATWE软件新增了底框结构空间分析功能,并提供了两种分析方法: 方法一,接PMCAD主菜单8的规范算法,即“建筑抗震设计规范GB50011-2001”规定的简化方法。它将计算分为两步,第一,仍用PMCAD主菜单8的基底剪力法作整体结构分析并得出底框层的地震力,其次,将上部砖房与底部框架分离开,并使底部框架接收上部砖房传来的恒荷载、活荷载及地震力〔包括倾覆力矩〕,最后,仅对底框部分用SATWE进行空间分析。 方法二,有限元整体算法。将上部砖房和底框作为一个整体,考虑砖混底框结构的特点,采用空间组合结构有限元方法进行分析,这种方法也适用于其它各种砌体结构。 用以上两种方法计算后,对底框部分的画图可以用SATWE接力PK画图方式,即全楼归并后的成批挑选梁柱画图。对梁的画图程序自动加上底框构造。比以前的底框画图方式要灵活的多了。 下面就SATWE软件的应用作如下归纳:一、操作流程 在PKPM系列CAD软件中,PMCAD是结构部分的基础模块,通过PMCAD的建模功能(主菜单1、2、3)形成结构的几何数据和荷载数据文件,其它软件模块均要读取上述两组文件。 1.PMCAD主菜单8的砖混底框抗震验算 对于底框结构,完成结构建模以后,首先要执行PMCAD主菜单8,进行砖混底框结构的抗震验算,其主要是完成以下两项工作: l按基底剪力法计算结构的地震作用(地震剪力和倾覆力矩),并对上部砖房进行抗震验算。 l竖向导荷计算,把上部砖房的恒、活荷载和自重按支承几何关系传递到底框部分,作为底框部分空间分析的外荷载。 在PMCAD的这步操作中,有关参数的含义和作用可参见PMCAD说明书,其中“考虑墙梁作用的上部荷载折减系数”是一个重要系数,在底框部分空间分析中还要用到。 2.底层框架结构空间分SATWE的析 SATWE软件的操作步骤,有关参数的含义和作用可参见SATWE说明书,其中有三个控制参数应特别注意,第一个是“总信息”中的“结构材料信息”,在进行底框结构空间分析时应将其设定为“砌体结构”;第二个是“砌体结构信息”中的“底部框架层数”,若为零则程序隐含认为该结构不是底框结构;第三个参数是“砌体结构信息”中的“底框结构空间分析方法”,这是一个控制开关,可选择“接PMCAD主菜单8的规范算法”或“有限元整体算法”,若选择“接PMCAD主菜单8的规范算法”,则程序仅对底框部分进行空间分析,在生成SATWE数据文件时,程序只形成底框部分(一层或两层)的几何信息和荷载信息,自动虑掉上部砖房部分信息;在结构分析时,自动读取PMCAD主菜单8为SATWE形成的底框部分的地震剪力,上部砖房传递给底框部分的地震剪力、倾覆弯矩、竖向荷载,以及考虑墙梁作用的上部荷载折减系数信息。

(底框-)砖混结构设计总结 一、分析建筑条件,准备初步工作: 1. 底框部分: (1)根据建筑条件图布置框架柱轴网,由抗震概念设计,尽量不要出现单根柱而不能形成一榀框架的情况,柱距一般为6米; (2)柱截面初步设计;单层商铺部分的框架柱截面设为350X350,底框部分的框架柱设为400X400;(3)根据柱轴网确定剪力墙的分布(长度和距离); (4)剪力墙一般分布在楼梯间处,与电信专业协调,预留电表箱位置; (5) (6)根据底层店面部分的墙厚确定框架梁、柱偏心; (7)根据框架柱的设置和柱距,确定框架梁的高度和宽度(一般上面有出承重墙的框架梁宽度不小于350,其它墙梁宽度不小于300,高度不小于净跨的1/5);(框架结构梁截面尺寸控制办法:计算时用TAT,看计算结果配筋图内的配筋率图;要求全截面配筋率1.5-1.7之间) (8)其框架和抗震墙的抗震等级,6、7度可分别按三、二级采用; 2. 砖混部分: (1)根据纵横墙的布置及可能会有的屋面构架,确定构造柱的位置和种类,(最外围的构造柱直接升到女儿墙,门窗洞口处的构造柱尺寸最好与门洞处的短墙吻合) (2)根据户型布置设置梁,包括其宽度和高度(其位置应把楼板分成规则的矩形,在阳台较大窗洞处或门窗连续设置处应设置过梁,且其高度加上门窗的高度应等于楼层高度?); (3)根据户型布置确定板厚,一般取短向跨度的1/35,但是最好不要小于100,客厅不小于120,否则影响使用;阳台、厨卫一般为90,屋面板厚120,楼梯梯板厚度为板跨的1/28,且平台梁高度与其下的窗高之和要等于建筑标高; (4)根据墙体外立面的腰线做法,确定外围圈梁的高度和做法; (5)根据总体要求,设置不同的结构标准层与荷载标准层; (6)阳台处的挑梁高度为挑出长度的1/3~1/6; 二、输入计算模型,进行程序计算: 1. 底框部分: (1) SAT-8计算底框时不能考虑风荷载。若在“底框结构空间分析方法”中选取“有限元整体算法”可计算风荷载,但结果偏小建议不使用; (2)上部承受墙荷载的墙梁宽度不小于300; (3)过渡层如果开洞大于800,需要设边梁; (4)抗震墙厚度不小于净高的1/20,且宜开设洞口形成若干墙段,其高宽比不宜小于2; (5)注意:梁和柱的偏心,应根据建筑要求与砌体外墙平齐,且上部的砌体抗震墙与底部的框架梁或抗震墙应对齐或基本对齐; (6)注意:剪力墙材料为混凝土及其强度等级; (7)材料等级:整个工程钢筋等级应统一为II级或III级,楼板、梁为C30混凝土,柱为C30混凝土,剪力墙为C30混凝土; (8)在SATWE中进入底框模型后选取荷载时,选取上部砖混荷载的标准组合来计算配筋,这样可以不用单独建立砖混的计算模型 (9)在模型中,应输入底层的砖墙?,并计算出二层砖混结构与底框结构的抗侧刚度之比,为保证房屋的整体抗震性能较好,最好在1.3-1.8之间(1.5左右),以此确定剪力墙的是否开洞和增减长度;

底框结构过程分析 一 结构布置 1、平面布置宜对称,尽量避免L形等凸凹墙体,避免困难时,应满足t/d小于等于0.3否则应设防震缝。使底层纵横向刚心尽可能与整栋房屋的质心重合。 2、 7度设防时,允许7层且高度小于21m,对教学楼等横墙少的6层19m,对砖抗震墙为5层16m。 3、 上面砖墙应按轴线上下对齐或基本对齐(每单元砌体抗震墙最多有二道不落在框架主梁,或砼抗震墙上, 而是由次梁支托上部抗震墙。托墙的次梁应按3.4.3条考虑地震作用的计算和内力调整。次梁的重力和弯矩应作为主梁的集中力和集中扭矩,并应传递到主梁两端的竖向支承构件,形成附加的地震作用效应;北京市的结构设计技术细则中要求:“允许有1/3道墙体可以不与下部框架梁或抗震墙对齐。同时,不对齐的墙不能连续超过两道。有些地方规定墙总长度是75%~80%要对齐等等)。落在托梁或抗震墙上,纵横墙应竖向连续。 4、 底层应布置纵、横向尽量连成一体的抗震墙,横墙间距应小于18m。抗震墙布置原则:均匀、分散、对 称、周边。其他的一些细节诸如:最好在上部砖墙下布墙、宜布在楼梯间周围等。总层数不超过5层的底层,可以采用嵌砌于框架之间的砌体抗震墙,当采用砖时应先砌墙后浇梁柱(要防止底层商铺随意打墙)。纵横向抗震墙宜保持一定的距离,最好布置在外围或靠近外墙处,并应尽量避免出现一字形墙体。为防止角柱的破坏最好在转角处布置混凝土抗震墙,如不能布置则应在该处嵌砌砖围护墙,而且该墙不宜开设门窗洞口;抗震墙基础应应与框架柱基础联合考虑成一体。 5、二层楼盖应现浇且不小于120厚,当150厚时,应配双层筋,以承担部分水平剪力 6、梁高跨比应在1/4-1/8之间,梁宽应300以上,b/h>0.3,柱宜采用方形截面对称配筋。二 底框计算方法 1、 满载法:把梁作为单独的受弯构件,上部墙等全荷均作用梁上(结果偏大)。只有胆小的人采用。 2、 三板两墙法:即只算三层楼板两层墙体的重量,其余层不算(柱和基础算)虽未出过问题,但缺乏科学依据 3、 弹性地基梁法:把墙体视为半无限弹性体,将托梁视为倒过来的弹性地基梁,按三角形竖向荷载计算托梁。 4、 墙梁组合规范算法:考虑墙梁大拱效应规范算法,按墙梁组合计算,虽经济合理,但条件太多见如下各条: (1)梁宽不小于300,净跨不小于梁高的4倍,梁高在1/6-1/8;

游戏系统: 本次SD 高达在战场方面和PS 的《吉伦的野望》相近,MS 可以最大三部组成一个小队,而大型(L 型)的MS 或是MA 就只能一队一部了。小队还可以合并,比如A 小队有两部小型MS,而B小队只有一部小型MS ,这时B小队就可以移动到A小队上合并成一个小队。 战斗中的小队指令菜单: 移动:分为单体移动和全体移动,顾名思义,单体移动就是只移动小队中某一部机体,而全体移动就是全小队一起移动,注意这时的移动力是按移动力最低的单位来算的。 队列:编成小队的队列,小队的一号队员只能攻击敌方小队的一号队员,二号和三号依此类推,但是当敌人小队的战斗单位小于我方小队战斗单位的时候,我方多出来的小队成员会向 敌小队一号队员进攻(例如我方有三名队员,而敌方只有两名,这时我方的第三名队员就会攻击敌方的第一名队员)。利用队列的战术也很多,比如敌小队二号队员的实弹武器攻击力很高,而我方小队里恰好有SEED 系的高达,这时候就可以将我方SEED 系的高达调至二号,然后就可以利用SEED系高达的PS装甲来防御住敌人的实弹攻击了。 攻击:直接攻击只能攻击邻接的敌人,有六方向,选定攻击目标小队后进入设置画面,此时 可以选择武器攻击,回避和ID。射击攻击有残弹限制,格斗武器无限制,有些武器是消耗 机师的SP的;选择回避的话,选择回避的机体本次不参与攻击但是回避率得到提升。ID相当于机器人大战中的精神指令,就是原作中该机师比较著名的台词,使用后可以提升机师或是机体的能力,有SP限制。攻击时射击攻击会先制于格斗攻击,即攻方射击->守方射击->攻方格斗->守方格斗,不过有时机师也能发动先制攻击。 间接:此指令一般为母舰或是炮击型MS 单位所有(比如钢加农等),选择此指令后可以选择长距离炮击型武器对敌小队实施远程打击,被攻击的敌小队无法反击,但是可以选择“散开”指令来躲过攻击,但是散开后可能因为落单而被各个击破,且当四周围都有小队在的时候无法散开(总不能站人家头上去吧……),有的机师拥有阻止散开的ID,这种机师一定要 给他分配具有强力远程武器的机体啊。 ID :在战斗地图画面的菜单里的ID 一般是使用对我方大范围有效的ID ,例如主舰的舰长可 以使用散布米粒子的ID 来增强指挥范围内我方机体的回避能力。 变形:某些MS 具有变形能力,可变成MA 等。 捕获:机体和资金的重要来源,要想得到好的机体或是抢来敌人机体拿去卖钱的话,就要靠这一着了。当我方有将敌人包围时(三个小队与敌人邻接,位置不限定,包围的小队越多,成功率越高)出现,还会有成功率提示(BOSS 机无法捕捉),是抓是杀全在于玩家了,有的机师拥有可以提升捕获率的ID,一定要善加应用。 交信:相当于机器人大战里的“说得”选项,当战场中可以发生对话的两名机师所在小队邻接的时候就会出现,此时可以对敌方角色进行说得等。熟悉原作的玩家应该记得在什么情节里会有哪些人会出现对话吧,那么就赶快试试吧。

SD高达G世纪攻略:全角色可习得技能(6) S リョウ 好战热血解放怒り强固 操舰センス对空炮火气合恶运必杀 ブレイブ 豪杰底力解放怒り威压统率力威风熟练斗将ペテラン ZZ ジェト ジャングリラ魂ニュータイプムードメイカー气合机械技术身轻器用豪杰プレッシャー精神感应 ルー 机敏单独行动解放强固ニュータイプ操舰センス对空炮火身轻幸运スナイパー ビーチャ ジャングリラ魂气分屋解放统率力ニュータイプ隐密狡猾恶运威风练达 エル ジャングリラ魂ポジティブ解放底力ニュータイプ情报解析热血射击管制强固必杀 モソド ジャングリラ魂气分屋解放怒りニュータイプ机械技术器用豪杰集中力ファイター イーノ ジャングリラ魂真面目解放熟练ニュータイプ机械技术器用铁壁補佐练达 リィナ 素人ニュータイプ真面目カリスマ强固集中力幸运身轻慈爱见切 ハマ-ン ニュータイププレッシャー冷徹统制机敏统率力威风空间战斗适应威压练达

マシェマー(容姿) 强化人间冷徹(エリート)气合热血统率力 怒り威风威压(底力)プレッシャー( 斗将)必杀(ファイター) イリア 冷徹真面目集中力補佐ニュータイプ统率力隐密威风勇将スナイパー キヤラ(容姿) 强化人间(气分屋)恐怖空间战斗适应( 豪杰)挑拨底力(单独行动) 统率力怒り威风プレッシャー( 斗将)练达(必杀) グレミー 冷徹威压エリート狡猾统率力 强固威风机敏ニュータイプ练达 プル ニュータイプ气分屋身轻ムードメイカー单独行动 操舰センス对空炮火强固底力スナイパー プルツー 强化人间冷徹身轻好战单独行动 操舰センス对空炮火挑拨恐怖スナイパー ラカン 熟练威压解放狡猾统率力 豪杰威风冷徹斗将ペテラン

PKPM- 砌体与底框结构设计入门第一章PKPM软件在砌体结构设计中的应有概述 1.1 软件结构及功能 1.2 QITI工作环境与快捷键 1.3 文件存取管理信息化 第二章普通砌体结构的设计 2.1 设计条件(工程实例) 2.2 模型建立 2.3 平面荷载显示校核 2.4 砌体信息及计算 2.5 结构平面图绘制 2.6 楼面梁的计算和绘制 2.7 平面布置的详图设计 第三章底框-抗震墙结构的计算与设计 3.1 设计条件(工程实例) 3.2 模型建立 3.3 底框-抗震墙结构的初步计算 3.4 底框-抗震墙结构三维分析 第四章朽筋砌块砌体结构三维分析与设计 4.1 与普通砌体结构建模的对比 4.2 砌体信息输入及三维分析 4.3 配筋砌体结构三维分析

4.4 配筋砌块砌体结构的图设计 第五章砌体结构混凝土构件设计 5.1 雨篷、挑檐、阳台设计 5.2 挑梁设计 5.3 墙梁设计 5.4 圆弧梁设计 第六章结构施工图通用菜单及图形的编辑、打印和转换 6.1 简介 6.2 参数设置 6.3 施工图标注 6.4 大样图 6.5 TCAD图形系统的编辑、打印及转换 本书的使用,可按照三个阶段进行: 1)软件部分的学习:先学习技术条件,然后按照设计步骤,进行一至两遍的基本操作,使自己对软件的全局和基本的操作 流程具备初步的了解。 2)设计知识的学习:根据书中提及的有关设计原理和设计经验,并参照设计过程中的一些体会,结合例题阅读本文的设 计知识部分,以便熟悉设计原理和常用经验,理解软件使用 中各关键参数的意义,加深对软件的认识。 3)结构规范链接对工程实例进行再次演练,明确规范的常识性