VLSI复习

题型:

缩写5题10分

简答12题60分

计算3题30分

Chapter 01

1.How to evaluate performance

?Cost

?Reliability

?Speed (delay, operating frequency)

?Power dissipation

2.Regenerative property

3.Delay :

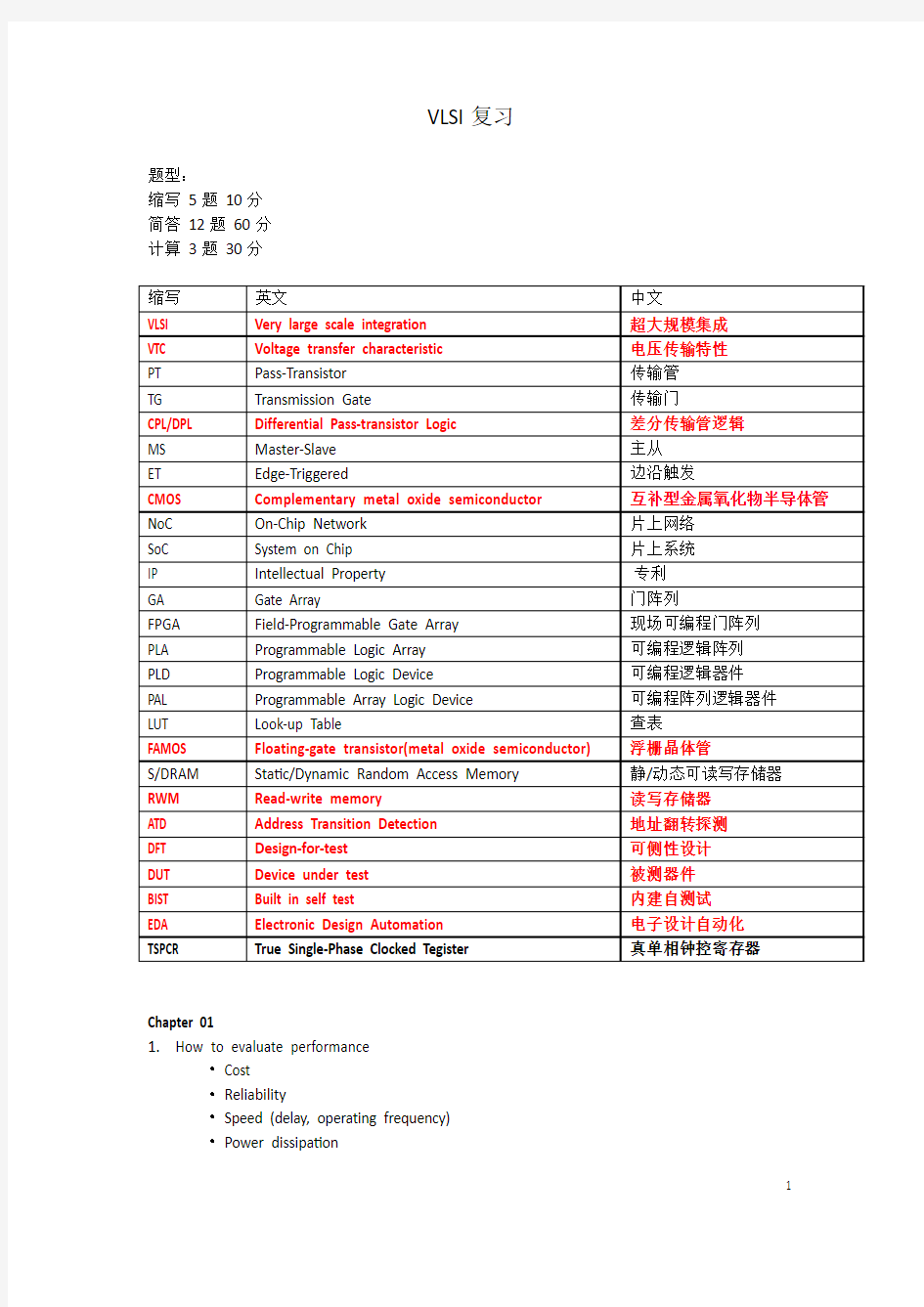

Chapter 02

1.Inverter layout

2.Photolithography process

1)Oxidation layering(氧化层)

2)Pthotoresist coating(涂光刻胶)

3)Stepper exposure(光刻机曝光)

4)Photoresist development and bake(光刻胶的显影和烘干)

5)Acid etching(酸刻蚀)

6)Spin, rinse, and dry(旋转,清洗和干燥)

7)Various process steps:

Ion implantation(离子注入)

Plasma etching(等离子刻蚀)

Metal deposition(金属沉淀)

8)Photoresist removal( or ashing) 去除光刻胶(即“沙洗”)

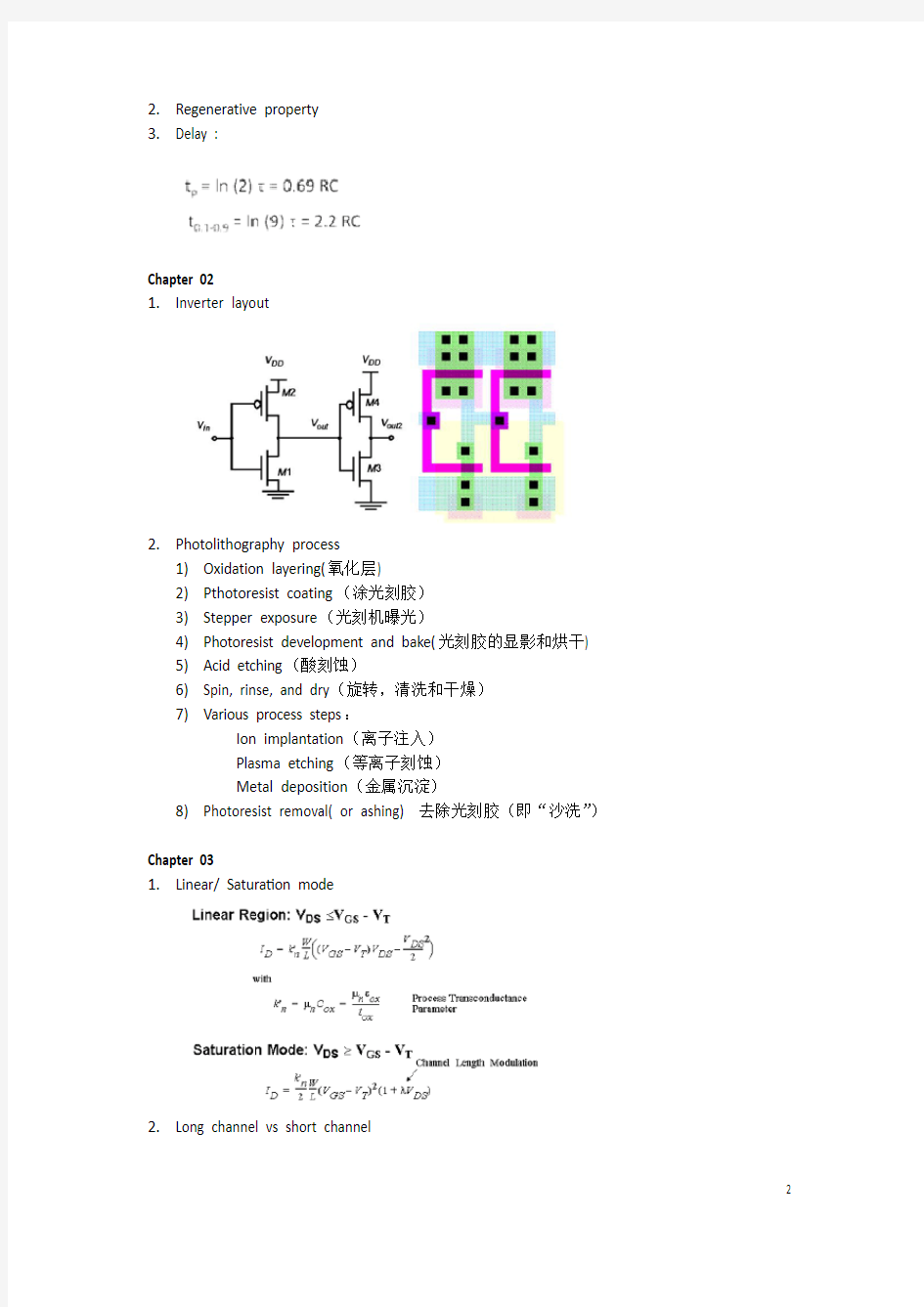

Chapter 03

1.Linear/ Saturation mode

2.Long channel vs short channel

3.Capacitances= structure capacitances+channel capacitances+MOS diffusion capacitances

4.Resistance=MOS sructure resistance+source and drain resistance+cantact resistance+wiring

resistance

With silicidation R方块? is reduced to the range 1 to 4 Ω/方块(source and drain resistance)

Chapter 04

1.C wire = C pp + C fringe + C interwire

2.Dealing with resistance:

1)Use better interconnect materials

2)More interconnect layers

3.RC Mode

?Lumped RC model

–total wire resistance is lumped into a single R and total capacitance into a single C

–good for short wires; pessimistic and inaccurate for long wires

?Distributed RC model

–circuit parasitics are distributed along the length, L, of the wire

4.Delay

Delay of a wire is a quadratic function of its length, L

The delay is 1/2 of that predicted (by the lumped model)

5.Reflection coefficient

【画传输图(or 波形),计算题】

Chapter 05

1.V M∝(W/L)p/(W/L)n

Increasing the width of the PMOS moves V M towards V DD,‰

Increasing the width of theNMOS moves V M towards GND.

2.Delay

3.Power in CMOS

1.Dynamic power consumption: charging and discharging capacitors;

Not a function of transistor sizes;

Need to reduce C L,Vdd,and f to reduce power.

2.Short circuit currents: short circuit path supply rails during switching;

Keep the input and output rise/fall times the same;

If Vdd 3.Leakage: leaking diodes and transistors 4.Technology scaling models Full scaling Fixed voltage scaling General scaling Chapter 06 1.Static CMOS- output connected to either Vdd or GND via a low-resistance path ?High noise margins ?Low output impedance, high input impedance ?No steady state path between Vdd and GND ?Delay is a function of load capacitance and transistor resistance Dynamic CMOS--relies on temporary storage of signal values on capacitance of high-impedance circuit nodes. ?Simpler, faster gates ?Increased sensitivity to noise 2.Static vs dynamic circuit ?In static circuit at every point in time (except when switching) the output is connected to either GND or V DD via a low resistance path. --fan-in of N requires 2N devices ?Dynamic circuits rely on the temporary storage of signal values on the capacitance of high impedance nodes --requires only N+2 transistors --takes a sequence of precharge and conditional evaluation phases to realize logic functions. ●conditions on output 1) once the optput of a dynamic gate is discharged, it cannot be charged again until the next precharge opreation. 2) Inputs to the gate can make at most one transition during evaluation. 3) Output can be in the high impedance state during and after evaluation(PDN off), state is stored in C L. ●Properties of Dynamic Gates 1)Logic function is implemented by the PDN only –number of transistors is N + 2 (versus 2N for static complementary CMOS) –should be smaller in area than static complementary CMOS 2)Full swing outputs (VOL = GND and VOH = VDD) 3)Nonratioed --sizing of the devices is not important for proper functioning (only for performance) 4) Faster switching speeds 5) Power dissipation should be better - consumes only dynamic power –no short circuit power consumption since the pull - up path is not on when evaluating -lower C L--both C int(since there are fewer transistors connected to the drain outpu t) and C ext(since there the output load is one per connectedgate, not two) -by construction can have at most one transition per cycle – no glitching 6) Needs a percharge clock https://www.doczj.com/doc/2d4483864.html,binational vs Sequential logic 4.Why PMOS in PUN and NMOS in PDN? Threshold drops 5.Ratioed logic: Pseudo-NMOS→Small area and load, but static power dissipation Chapter 07 https://www.doczj.com/doc/2d4483864.html,tch vs Register ?Latch: level sensitive---- As for positive: passes inputs to Q when the clock is high----transparent mode; When clock is low----hold mode ?Flip-flop: edge sensitive 2.Bistable circuit: The cross coupling of two inverters results in a bistablecircuit (a circuit with two stable states) ?Have to be able to change the stored value by making A (or B) temporarily unstable by increasing the loop gain to a value larger than 1 Done by applying a trigger pulse at Vi1 or Vi2 the width of the trigger pulse need be only a little larger than the total propagation delayaround the loop circuit (twice the delay of an inverter) ?Two approaches used 1.cutting the feedback loop (mux based latch) 2.overpowering the feedback loop (as used in SRAMs) 3.MS ET timing properties ?Set-up time: time before rising edge of clk that D must be valid ?Propagation delay: time for QM to reach Q ?Hold time: time D must be stable after rising edge of clk 4.Pipelining 5.Schmitt Trigger (rise—P; fall—N) Chapter 09 1.Cross Talk: An unwanted coupling from a neighboring signal wire to a network node introduces an interference that is generally called cross talk. 2.Dealing with Capacitive Cross Talk ?Avoid floating nodes ?Protect sensitive nodes ?Make rise and fall times as large as possible ?Differential signaling ?Do not run wires together for a long distance ?Use shielding wires ?Use shielding layers 3.Cross Talk and Performance: when neighboring lines switch in opposite direction of victim line, delay increases. 4.Impact of resistance is commonly seen in power supply distribution: –IR drop –Voltage variations Chapter 10 1.Clock Nonidealities: ?Clock skew: Spatial variation in temporally equivalent clock edges; ?Clock jitter: Temporal variations in consecutive edges of the clock signal ?Variation of the pulse width 2.Clock Uncertainties----Source of clock uncertainty (图形填空)(重点)简答题: ?Clock‐Signal Generation (1) ?Manufacturing Device Variations (2) ?Interconnect Variations (3) ?Environmental Variations (4 and 5) ?Capacitive Coupling (6 and 7) 3.Impact of Positive/Negative Clock Skew and Clock jitter (重点) 1.Positive clock skew:Clock and data flow in the same direction 2.Negative clock skew: Clock and data flow in opposite directions 3.Jitter cause T to vary on a cycle-by-cycle basis Combined impact of skew and jitter: Constraints on the minimum clock period (positive) 4.To reduce dynamic power, the clock network must support clock gating (shutting down(disabling the clock ) units) 5. Clock distribution techniques --Balanced paths(H-tree network, matched RC trees) --Clock grids: minimize absolute delay 6.Matched RC trees, represents a floor plan that distributes the clock signal so that the interconnections carrying the clock signals to the functional subblocks are of equal length. 7. 彩图9:The unbalanced load creates a large skew, by careful tuning of the wire width, the load is balanced, minimizing the skew. 8. Dealing with Clock Skew and Jitter ?To minimize skew, balance clock paths using H-treeor matched-tree clock distribution structures. ?If possible, route data and clock in opposite directions; eliminates races at the cost of performance. ?The use of gated clocks to help with dynamic power consumption make jitter worse. ?Shield clock wires (route power lines –VDD or GND –next to clock lines) to minimize/eliminate coupling with neighboring signal nets. ?Use dummy fills to reduce skew by reducing variations in interconnect capacitances dueto interlayer dielectric thickness variations. ?Beware of temperature and supply rail variations and their effects on skew and jitter. ?Power supply noise fundamentally limits the performance of clock networks. Chapter 11 1.Full adder (P=A+B) 2.Static vs dynamic Manchester Carry Chain Static dynamic 3.Square Root Carry Select Adder (PPT 24) 4.Wallace‐Tree Multiplier(PPT 32) 5.Logarithmic Shifter Chapter 12 1.Semiconductor Memory Classification 2.Bit line & word line 3.Memory Timing(DRAM vs SRAM) DRAM: Multiplexde Addressing SRAM: Self-timed Address Switching/Changing 4.MOS OR ROM 5. SRAM vs DRAM 6. DRAM Timing 7. SRAM ATD(Address Transition Detection) Chapter 13 1.Two Important Test Properties ?Controllability ‐measures the ease of bringing a node to a given condition using only the input pins ?Observability ‐measures the ease of observing the value of a node at the output pins 2.Test Approaches ?Ad‐hoc testing ?Scan based test ?Self test 3.Scan Register 集成电路设计基础 2010-11年第一学期试题 一、填空题(20分) 1、目前,国内已引进了12英寸0.09um 芯片生产线,由此工艺线生产出来的集成 电路特征尺寸是0.009um (大 小),指的是右图中的W (字 母)。 2、CMOS工艺可分为p阱、n阱、双阱 三种。 在CMOS工艺中,N阱里形成的晶体管是p (PMOS,NMOS)。 3、通常情况下,在IC中各晶体管之间是由场氧来隔离的;该区域的形成用到的制造工艺是氧化工艺。 4.集成电路制造过程中,把掩膜上的图形转换成晶圆上器件结构一道工序是指光 刻,包括晶圆涂光刻胶、曝光、显影、烘干四个步骤; 其中曝光方式包括①接触式、②非接触式两种。 5、阈值电压V T是指将栅极下面的si表面从P型Si变成N型Si所必要的电压,根据阈值电压的不同,常把MOS区间分成耗尽型、增强型两种。降低V T 的措施包括:降低杂质浓度、增大Cox 两种。 二、名词解释(每词4分,共20分) ①多项目晶圆(MPW) ②摩尔定律 ③掩膜 ④光刻 ⑤外延 三、说明(每题5分共10分) ①说明版图与电路图的关系。 ②说明设计规则与工艺制造的关系。 四、简答与分析题(10分) 1、数字集成电路设计划分为三个综合阶段,高级综合,逻辑综合,物理综合;解释这 三个综合阶段的任务是什么? 2、分析MOSFET尺寸能够缩小的原因。 五、综合题(共4小题,40分) 1、在版图的几何设计规则中,主要包括各层的最小宽度、层与层之间的最小间距、各 层之间的最小交叠。把下图中描述的与多晶硅层描述的有关规则进行分类: (2)属于层与层之间的最小间距的是: (3)属于各层之间的最小交叠是: 2.请提取出下图所代表的电路原理图。画出用MOSFET构成的电路。 建设工程项目流程概述 流程图 项目概述 一、项目类型:房屋建筑工程 二、项目建筑安装工程费金额:4亿元 第一阶段:项目决策阶段 一、项目建议书 政府投资的工程项目,编报项目建议书是项目建设最初阶段工作,其主要作用是为了推荐建设项目,以便在一个确定的地区或部门内,以自然资源和市场预测为基础,选择建设项目。项目建议书的编制由具有工程咨询资质的单位编制。 选定方式:委托或比选或公开招标 收费标准:《国家计委关于印发建设项目前期工作咨询收费暂行规定的通知》(计价格[1999]1283号)文件已于2016年国家发改委31号令中宣布废止。 收费估算:可向供应商询价或参照计价格[1999]1283号文件,估算约14至37万元。 二、可行性研究报告 可行性研究是在项目建议书被批准后,对项目在技术上和经济上是否可行所进行的科学分析和论证。根据《国务院关于投资体制改革的决定》(国发[2004]20号),对于政府投资项目须审批项目建议书和可行性研究报告。《国务院关于投资体制改革的决定》指出,对于企业不使用政府资金投资建设的项目,一律不再实行审批制,区别不同情况 实行核准制和登记备案制。对于《政府核准的投资项目目录》以外的企业投资项目,实行备案制。可行性研究报告的编制由具有工程咨询资质的单位编制。 选定方式:委托或比选或公开招标 收费标准:《国家计委关于印发建设项目前期工作咨询收费暂行规定的通知》(计价格[1999]1283号)文件已于2016年国家发改委31号令中宣布废止。 收费估算:可向供应商询价或参照计价格[1999]1283号文件,估算约28至75万元。 三、项目立项 工程建设项目立项主要包括审批项目建议书和项目可行性研究报告。属国家审批的项目以及旅游宾馆、高档写字楼、别墅渡假村项目,由地级市发改委和行业主管部门报省发改委、再由省发改委转报国家审批。工程建设项目立项流程:项目建议书审批→项目可行性研究报告审批→项目投资计划申报。 第二阶段:设计前准备阶段 一、确定全过程同步跟踪审计单位 根据佛山市委《重大工程廉洁风险同步预防工作指引》的规定,由佛山市国资控股或财政投资建设的超1亿元路桥及轨道交通工程项目、超5000万元房屋建筑工程项目以及超3000万元环保、水利工程项目,均要开展重大工程廉洁风险同步预防。委托具有会计师事务所执业证书的单位进行项目全过程同步跟踪审计服务。 1、描述集成电路工艺技术水平的五个技术指标及其物理含义 ⑴集成度(Integration Level):以一个IC芯片所包含的元件(晶体管或门/数)来衡量,(包括有源和无源元件)。 ⑵特征尺寸 (Feature Size) /(Critical Dimension):特征尺寸定义为器件中最小线条宽度(对MOS器件而言,通常指器件栅电极所决定的沟道几何长度),也可定义为最小线条宽度与线条间距之和的一半。 ⑶晶片直径(Wafer Diameter):当前的主流晶圆的尺寸为12寸(300mm),正在向18寸(450mm)晶圆迈进。 ⑷芯片面积(Chip Area):随着集成度的提高,每芯片所包含的晶体管数不断增多,平均芯片面积也随之增大。 ⑸封装(Package):指把硅片上的电路管脚,用导线接引到外部接头处,以便于其它器件连接。封装形式是指安装半导体集成电路芯片用的外壳。 2、简述集成电路发展的摩尔定律。 集成电路芯片的集成度每三年提高4倍,而加工特征尺寸缩小倍,这就是摩尔定律。当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍 3、集成电路常用的材料有哪些? 集成电路中常用的材料有三类:半导体材料,如Si、Ge、GaAs?以及InP?等;绝缘体材料,如SiO2、SiON?和Si3N4?等;金属材料,如铝、金、钨以及铜等。 4、集成电路按工艺器件类型和结构形式分为哪几类,各有什么特点。 双极集成电路:主要由双极晶体管构成(NPN型双极集成电路、PNP型双极集成电路)。优点是速度高、驱动能力强,缺点是功耗较大、集成度较低。 CMOS集成电路:主要由NMOS、PMOS构成CMOS电路,功耗低、集成度高,随着特征尺寸的缩小,速度也可以很高。 BiCMOS集成电路:同时包括双极和CMOS晶体管的集成电路为BiCMOS集成电路,综合了双极和CMOS器件两者的优点,但制作工艺复杂。 5、解释基本概念: 微电子、集成电路、集成度、场区、有源区、阱、外延 微电子:微电子技术是随着集成电路,尤其是超大型规模集成电路而发展起来的一门新的技术。微电子技术包括系统电路设计、器件物理、工艺技术、材料制备、自动测试以及封装、组装等一系列专门的技术,微电子技术是微电子学中的各项工艺技术的总和。微电子学是研究在固体(主要是半导体)材料上构成的微小型化电路、电路及微电子系统的电子学分支。 集成电路:通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻、电容等无源器件,按照一定的电路互连,“集成”在一块半导体单晶片(如硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能。 集成度:集成电路的集成度是指单块芯片上所容纳的元件数目。 《模拟集成电路设计原理》期末考试 一.填空题(每空1分,共14分) 1、与其它类型的晶体管相比,MOS器件的尺寸很容易按____比例____缩小,CMOS电路被证明具有_ 较低__的制造成本。 2、放大应用时,通常使MOS管工作在_ 饱和_区,电流受栅源过驱动电压控制,我们定义_跨导_来 表示电压转换电流的能力。 3、λ为沟长调制效应系数,对于较长的沟道,λ值____较小___(较大、较小)。 4、源跟随器主要应用是起到___电压缓冲器___的作用。 5、共源共栅放大器结构的一个重要特性就是_输出阻抗_很高,因此可以做成___恒定电流源_。 6、由于_尾电流源输出阻抗为有限值_或_电路不完全对称_等因素,共模输入电平的变化会引起差动输 出的改变。 7、理想情况下,_电流镜_结构可以精确地复制电流而不受工艺和温度的影响,实际应用中,为了抑制 沟长调制效应带来的误差,可以进一步将其改进为__共源共栅电流镜__结构。 8、为方便求解,在一定条件下可用___极点—结点关联_法估算系统的极点频率。 9、与差动对结合使用的有源电流镜结构如下图所示,电路的输入电容C in为__ C F(1-A)__。 10、λ为沟长调制效应系数,λ值与沟道长度成___反比__(正比、反比)。 二.名词解释(每题3分,共15分) 1、阱 解:在CMOS工艺中,PMOS管与NMOS管必须做在同一衬底上,其中某一类器件要做在一个“局部衬底”上,这块与衬底掺杂类型相反的“局部衬底”叫做阱。 2、亚阈值导电效应 解:实际上,V GS=V TH时,一个“弱”的反型层仍然存在,并有一些源漏电流,甚至当V GS 第1章建设项目评估概述 本章综合介绍了建设项目评估的基本问题,包括项目发展周期与项目的前期研究;可行性研究的含义及其意义、主要作用与编写要求;项目评估的内容、程序以及在开展项目评估时应遵循的基本原则等。 1.1项目发展周期与项目前期研究 1.1.1 建设项目发展周期 1.工程项目建设程序:是指项目从策划、评估、决策、设计、施工到竣工验收、投入生产或交付使用的整个建设过程中,各项工作必须遵循的先后工作次序。 ⒉建设项目发展周期:一个建设项目从开始构想、施工建设、建成投产、直到最终报废所经过的时间。 项目周期的阶段划分:投资前期、投资建设期和建成投产期。 1.1.2西方国家的项目前期研究 机会研究(项目设想) 谈判与签订合同 投产阶段 图1-1 西方国家项目周期各阶段及主要工作示意图 按基础资料占有程度,研究内容、研究深度及可信度不同,可将投资前期研究分为机会 研究、初步可行性研究、详细可行性研究、项目评估与决策四个阶段。 1. 机会研究:亦称投资鉴定或项目设想。它是可行性研究的第一阶段。任务是研究和确 定合理的投资方向、投资规模和投资结构。也就是在了解掌握国民经济和社会发展的长远规划和行业,地区规划、经济建设方针,建设任务和技术经济政策的基础上,通过对拟投资领域相关条件及环境背景的调查分析,为建设项目的投资方向和投资时机提出设想和策划。 所需时间约用1—3个月,所需费用约占投资总额0.2%—1%,估算投资额和成本效益 的精度在±30% 2. 初步可行性研究:又称预可行性研究,是指在投资机会研究已确定了大致的投资方向 和投资时机的基础上,通过对投资项目的初步概算和经济效果评价,进一步判断投资机会研究的结论是否正确,并做出是否有必要进行下一步详细可行性研究的结论。主要内容: 1)判定项目有无生命力和发展前景; 2)市场供求的预测,生产工艺和设备等方面的研究; 3)判断项目是否可行。 这一阶段决定是否进行下一步。估算额精度误差一般要求不超过±20%左右,所需费用约占投资总额0.25%—1.5%,需耗时约4—6个月。 3. 详细可行性研究:亦称最终可行性研究,是指通过一定方法对项目的技术可行性和经 一般机会研究(地区研究、部门研究、资源研究) 项目机会研究 1.国家 2.某一部门或地区 3.某 一特定产品 4.产品进出口情况 5.分析企业 6.机会研究 集成电路设计复习题 绪论 1.画出集成电路设计与制造的主要流程框架。 2.集成电路分类情况如何? 集成电路设计 1.层次化、结构化设计概念,集成电路设计域和设计层次 2.什么是集成电路设计?集成电路设计流程。 (三个设计步骤:系统功能设计逻辑和电路设计版 图设计) 3.模拟电路和数字电路设计各自的特点和流程 4.版图验证和检查包括哪些内容?如何实现? 5.版图设计规则的概念,主要内容以及表示方法。为什么需要指定版图设计规则? 6.集成电路设计方法分类? (全定制、半定制、PLD) 7.标准单元/ 门阵列的概念,优点/缺点,设计流程 8.PLD设计方法的特点,FPGA/CPLD的概念 9.试述门阵列和标准单元设计方法的概念和它们之间的异同点。 10.标准单元库中的单元的主要描述形式有哪些?分别在IC设计的什么阶段应用? 11.集成电路的可测性设计是指什么? Soc设计复习题 1. 什么是SoC? 2. SoC设计的发展趋势及面临的挑战? 3. SoC设计的特点? 4. SoC设计与传统的ASIC设计最大的不同是什么? 5. 什么是软硬件协同设计? 6. 常用的可测性设计方法有哪些? 7. IP 的基本概念和IP分类 8. 什么是可综合RTL代码? 9. 么是同步电路,什么是异步电路,各有什么特点? 10. 逻辑综合的概念。 11. 什么是触发器的建立时间( Setup Time ),试画图进行说明。 12. 什么是触发器的保持时间( Hold Time ),试画图进行说明。 13. 什么是验证,什么是测试,两者有何区别? 14. 试画图简要说明扫描测试原理。 绪论 1、画出集成电路设计与制造的主要流程框架。 2、集成电路分类情况如何? 双极型 数字模拟混合电路按应用领域分类 集成电路设计 1.层次化、结构化设计概念,集成电路设计域和设计层次分层分级设计和模块化设计.将一个复杂的集成电路系统的设计问题分解为复杂性较低的设计级别,集成电路MSI 按规模分 LSI 类VLSI ULSI GSI 数字电 按功能分类模拟电 路组合逻辑电路 路时序逻辑电路 路线性电路 路非线性电路 单片集成 按结构分类 混合集 成 SSI PMOS 电M路OS 型NMOS CMOS B iMOS B iMOS 型 B iCMOS 电 厚路膜混合集 成 电路 薄路膜混合集 成 电路 集成电路设计方法的发展历史 、发展现状、及未来主流设 计方法报告 集成电路是一种微型电子器件或部件,为杰克·基尔比发明,它采用一定的工艺,把一个电路中所需的晶体管、二极管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;其中所有元件在结构上已组成一个整体,使电子元件向着微小型化、低功耗和高可靠性方面迈进了一大步。集成电路具有体积小,重量轻,引出线和焊接点少,寿命长,可靠性高,性能好等优点,同时成本低,便于大规模生产。它不仅在工、民用电子设备如收录机、电视机、计算机等方面得到广泛的应用,同时在军事、通讯、遥控等方面也得到广泛的应用。用集成电路来装配电子设备,其装配密度比晶体管可提高几十倍至几千倍,设备的稳定工作时间也可大大提高。 一、集成电路的发展历史: 1947年:贝尔实验室肖克莱等人发明了晶体管,这是微电子技术发展中第一个里程碑; 1950年:结型晶体管诞生; 1950年: R Ohl和肖特莱发明了离子注入工艺; 1951 年:场效应晶体管发明; 1956年:C S Fuller发明了扩散工艺; 1958年:仙童公司Robert Noyce与德仪公司基尔比间隔数月分别发明了集成电路,开创了世界微电子学的历史; 1960年:H H Loor和E Castellani发明了光刻工艺;1962年:美国RCA公司研制出MOS场效应晶体管; 1963年:和首次提出CMOS技术,今天,95%以上的集成电路芯片都是基于CMOS工艺; 1964年:Intel摩尔提出摩尔定律,预测晶体管集成度将会每18个月增加1倍; 1966年:美国RCA公司研制出CMOS集成电路,并研制出第一块门阵列; 1967年:应用材料公司成立,现已成为全球最大的半导体设备制造公司; 1971年:Intel推出1kb动态随机存储器,标志着大规模集成电路出现; 1971年:全球第一个微处理器4004Intel公司推出,采用的是MOS工艺,这是一个里程碑式的发明; 1974年:RCA公司推出第一个CMOS微处理器1802; 1976年:16kb DRAM和4kb SRAM问世; 1978年:64kb动态随机存储器诞生,不足平方厘米的硅片上集成了14万个晶体管,标志着超大规模集成电路时 实验一 EDA软件实验 一、实验目的: 1、掌握Xilinx ISE 9.2的VHDL输入方法、原理图文件输入和元件库的调用方法。 2、掌握Xilinx ISE 9.2软件元件的生成方法和调用方法、编译、功能仿真和时序仿真。 3、掌握Xilinx ISE 9.2原理图设计、管脚分配、综合与实现、数据流下载方法。 二、实验器材: 计算机、Quartus II软件或xilinx ISE 三、实验内容: 1、本实验以三线八线译码器(LS74138)为例,在Xilinx ISE 9.2软件平台上完成设计电 路的VHDL文本输入、语法检查、编译、仿真、管脚分配和编程下载等操作。下载芯片选择Xilinx公司的CoolRunner II系列XC2C256-7PQ208作为目标仿真芯片。 2、用1中所设计的的三线八线译码器(LS74138)生成一个LS74138元件,在Xilinx ISE 9.2软件原理图设计平台上完成LS74138元件的调用,用原理图的方法设计三线八线译 码器(LS74138),实现编译,仿真,管脚分配和编程下载等操作。 四、实验步骤: 1、三线八线译码器(LS 74138)VHDL电路设计 (1)三线八线译码器(LS74138)的VHDL源程序的输入 打开Xilinx ISE 6.2编程环境软件Project Navigator,执行“file”菜单中的【New Project】命令,为三线八线译码器(LS74138)建立设计项目。项目名称【Project Name】为“Shiyan”,工程建立路径为“C:\Xilinx\bin\Shiyan1”,其中“顶层模块类型(Top-Level Module Type)”为硬件描述语言(HDL),如图1所示。 图1 点击【下一步】,弹出【Select the Device and Design Flow for the Project】对话框,在该对话框内进行硬件芯片选择与工程设计工具配置过程。 《模拟集成电路设计》复习 答疑安排: 第13周星期二(5月29日),上午9:00-11:30,下午14:30-17:00,工三310 考试题型: 七道大题:第2章一题,第3、4章各两题,第5章一题,第6、7章共一题 考试注意事项: 所有题目采用课本P32表2.1的数据,V DD=3V,C OX=3.84 10-7F/cm2,忽略漏/源横向扩散长度L D。试题会给出所需参数值。 时刻区分大信号、小信号。 时刻注意是否考虑二级效应。 题目有“推导”两字时,需给出求解过程。 必考:画小信号等效电路 复习题 例2.2补充问题:(1)分析MOS工作区间变化情况;(2)画出I D-V DS 曲线;(3)推导线性区跨导表达式。 习题2.2注意:跨导的单位。 习题2.3补充问题:给定参数值,计算本征增益的数值。注意:画曲线时需考虑λ与L的关系。 例3.5 补充问题:画出图3.21(b)电路的小信号等效电路,推导增益表达式。 习题3.2问题(b)删去。补充问题:求R out。 习题3.12解题思路:I1→V out→V GS2→(W/L)2→A v 习题3.14 输出摆幅=V DD-V OD1-|V OD2|。 解题思路:A v,R out→g m1→(W/L)1→V OD1→|V OD2|→(W/L)2 第4章课件第49页的题目差模增益-g m1(r o1||r o3),共模增益0,共模抑制比+∞ 例4.6 习题4.18 只要求图4.38(a)-(d)。补充问题:画出半边电路。注意:画半边电路时去掉电流源M5。 习题4.25 计算过驱动电压V OD时忽略沟道长度调制效应。注意双端输出摆幅为单端时的2倍。 习题5.1问题(e)删去。问题(c)和(d)有简单的计算方法。 习题5.5问题(b)(c)删去。λ=0。 例6.4补充问题:画出低频小信号等效电路,推导低频小信号增益;写出C D、C S分别包含哪些MOS电容。 习题6.9 只要求图6.39(a)(b)(c)。 例7.11只计算热输入参考噪声电压。 习题7.11补充问题:推导小信号增益。 1、解释基本概念:集成电路,集成度,特征尺寸 参考答案: A、集成电路(IC:integrated circuit)是指通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻、电容等无源器件,按照一定的电路互连,“集成”在一块半导体晶片(如硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能的集成块。 B、集成度是指在每个芯片中包含的元器件的数目。 C、特征尺寸是代表工艺光刻条件所能达到的最小栅长(L)尺寸。 2、写出下列英文缩写的全称:IC,MOS,VLSI,SOC,DRC,ERC,LVS,LPE 参考答案: IC:integrated circuit;MOS:metal oxide semiconductor;VLSI:very large scale integration;SOC:system on chip;DRC:design rule check;ERC:electrical rule check;LVS:layout versus schematic;LPE:layout parameter extraction 3、试述集成电路的几种主要分类方法 参考答案: 集成电路的分类方法大致有五种:器件结构类型、集成规模、使用的基片材料、电路功能以及应用领域。根据器件的结构类型,通常将其分为双极集成电路、MOS集成电路和Bi-MOS集成电路。按集成规模可分为:小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路、特大规模集成电路和巨大规模集成电路。按基片结构形式,可分为单片集成电路和混合集成电路两大类。按电路的功能将其分为数字集成电路、模拟集成电路和数模混合集成电路。按应用领域划分,集成电路又可分为标准通用集成电路和专用集成电路。 4、试述“自顶向下”集成电路设计步骤。 参考答案: “自顶向下”的设计步骤中,设计者首先需要进行行为设计以确定芯片的功能;其次进行结构设计;接着是把各子单元转换成逻辑图或电路图;最后将电路图转换成版图,并经各种验证后以标准版图数据格式输出。 5、比较标准单元法和门阵列法的差异。 参考答案: 标准单元方法设计与门阵列法基本的不同点有:(1) 在门阵列法中逻辑图是转换成门阵列所具有的单元或宏单元,而标准单元法则转换成标准单元库中所具有的标准单元。(2) 门阵列设计时首先要选定某一种门复杂度的基片,因而门阵列的布局和布线是在最大的门数 集成电路设计方法--复习提纲 2、实际约束:设计最优化约束:建立时钟,输入延时,输出延时,最大面积 设计规则约束:最大扇出,最大电容 39.静态时序分析路径的定义 静态时序分析通过检查所有可能路径上的时序冲突来验证芯片设计的时序正确性。时序路径的起点是一个时序逻辑单元的时钟端,或者是整个电路的输入端口,时序路径的终点是下一个时序逻辑单元的数据输入端,或者是整个电路的输出端口。 40.什么叫原码、反码、补码? 原码:X为正数时,原码和X一样;X为负数时,原码是在X的符号位上写“1”反码:X为正数是,反码和原码一样;X为负数时,反码为原码各位取反 补码:X为正数时,补码和原码一样;X为负数时,补码在反码的末位加“1” 41.为什么说扩展补码的符号位不影响其值? SSSS SXXX = 1111 S XXX + 1 —— 2n2n12n1例如1XXX=11XXX,即为XXX-23=XXX+23-24. 乘法器主要解决什么问题? 1.提高运算速度2.符号位的处理 43.时钟网络有哪几类?各自优缺点? 1. H树型的时钟 网络: 优点:如果时钟负载在整个芯片内部都很均衡,那么H 树型时钟网络就没有系统时钟偏斜。缺点:不同分支上的叶节点之间可能会出现较大的随机偏差、漂移和抖动。 2. 网格型的时钟网络 优点:网格中任意两个相近节点之间的电阻很小,所以时钟偏差也很小。缺点:消耗大量的金属资源,产生很大的状态转换电容,所以功耗较大。 3.混合型时钟分布网络优点:可以提供更小的时钟偏斜,同时,受负载的影响比较小。缺点:网格的规模较大,对它的建模、自动生成可能会存在一些困难。 总线的传输机制? 1. 早期:脉冲式机制和握手式机制。 脉冲式机制:master发起一个请求之后,slave在规定的t时间内返回数据。 握手式机制:master发出一个请求之后,slave在返回数据的时候伴随着一个确认信号。这样子不管外设能不能在规定的t时间内返回数据,master都能得到想要的数据。 2. 随着CPU频率的提高,总线引入了wait的概念 如果slave能在t时间内返回数据,那么这时候不能把wait信号拉高,如果slave不能在t时间内返回数据,那么必须在t时间内将wait信号拉高,直到slave将可以返回 集成电路设计流程 . 集成电路设计方法 . 数字集成电路设计流程 . 模拟集成电路设计流程 . 混合信号集成电路设计流程 . SoC芯片设计流程 State Key Lab of ASIC & Systems, Fudan University 集成电路设计流程 . 集成电路设计方法 . 数字集成电路设计流程 . 模拟集成电路设计流程 . 混合信号集成电路设计流程 . SoC芯片设计流程 State Key Lab of ASIC & Systems, Fudan University 正向设计与反向设计 State Key Lab of ASIC & Systems, Fudan University 自顶向下和自底向上设计 State Key Lab of ASIC & Systems, Fudan University Top-Down设计 –Top-Down流程在EDA工具支持下逐步成为 IC主要的设计方法 –从确定电路系统的性能指标开始,自系 统级、寄存器传输级、逻辑级直到物理 级逐级细化并逐级验证其功能和性能 State Key Lab of ASIC & Systems, Fudan University Top-Down设计关键技术 . 需要开发系统级模型及建立模型库,这些行 为模型与实现工艺无关,仅用于系统级和RTL 级模拟。 . 系统级功能验证技术。验证系统功能时不必 考虑电路的实现结构和实现方法,这是对付 设计复杂性日益增加的重要技术,目前系统 级DSP模拟商品化软件有Comdisco,Cossap等, 它们的通讯库、滤波器库等都是系统级模型 库成功的例子。 . 逻辑综合--是行为设计自动转换到逻辑结构 设计的重要步骤 State Key Lab of ASIC & Systems, Fudan University A/D转换器的设计 一.实验目的: (1)设计一个简单的LDO稳压电路 (2)掌握Cadence ic平台下进行ASIC设计的步骤; (3)了解专用集成电路及其发展,掌握其设计流程; 二.A/D转换器的原理: A/D转换器是用来通过一定的电路将模拟量转变为数字量。 模拟量可以是电压、电流等电信号,也可以是压力、温度、湿度、位移、声音等非电信号。但在A/D转换前,输入到A/D转换器的输入信号必须经各种传感器把各种物理量转换成电压信号。符号框图如下: 数字输出量 常用的几种A/D器为; (1):逐次比较型 逐次比较型AD由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB 开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。其电路规模属于中等。其优点是速度较高、功耗低,在低分辩率(<12位)时价格便宜,但高精度(>12位)时价格很高。 (2): 积分型 积分型AD工作原理是将输入电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值。其优点是用简单电路就能获得高分辨率,但缺点是由于转换精度依赖于积分时间,因此转换速率极低。初期的单片AD转换器大多采用积分型,现在逐次比较型已逐步成为主流。 (3):并行比较型/串并行比较型 并行比较型AD采用多个比较器,仅作一次比较而实行转换,又称FLash(快速)型。由于转换速率极高,n位的转换需要2n-1个比较器,因此电路规模也极大,价格也高,只适用于视频AD转换器等速度特别高的领域。 串并行比较型AD结构上介于并行型和逐次比较型之间,最典型的是由2个n/2位的并行型AD转换器配合DA转换器组成,用两次比较实行转换,所以称为Half flash(半快速)型。还有分成三步或多步实现AD转换的叫做分级型AD,而从转换时序角度又可称为流水线型AD,现代的分级型AD中还加入了对多次转换结果作数字运算而修正特性等功能。这类AD速度比逐次比较型高,电路规模比并行型小。 一.A/D转换器的技术指标: (1)分辨率,指数字量的变化,一个最小量时模拟信号的变化量,定义为满刻度与2^n的比值。分辨率又称精度,通常以数字信号的位数来表示。 (2)转换速率,是指完成一次从模拟转换到数字的AD转换所需的时间的倒数。积分型AD的转换时间是毫秒级属低速AD,逐次比较型AD是微秒级,属中速AD,全并行/串并行型AD可达到纳秒级。采样时间则是另外一个概念,是指两次转换的间隔。为了保证转换的正确完成,采样速率必须小于或等于转换速率。因此有人习惯上将转换速率在数值上等同于采样速率也是可以接受的。常用单位ksps 和Msps,表示每秒采样千/百万次。 (3)量化误差,由于AD的有限分辩率而引起的误差,即有限分辩率AD的阶梯状转移特性曲线与无限分辩率AD(理想AD)的转移特性曲线(直线)之间的最大偏差。通常是1 个或半个最小数字量的模拟变化量,表示为1LSB、1/2LSB。(4)偏移误差,输入信号为零时输出信号不为零的值,可外接电位器调至最小。(5)满刻度误差,满度输出时对应的输入信号与理想输入信号值之差。 (6)线性度,实际转换器的转移函数与理想直线的最大偏移,不包括以上三种误差。 三、实验步骤 此次实验的A/D转换器用的为逐次比较型,原理图如下: 集成电路设计基础复习提纲 一EDA常用命令 ls 显示当前目录下的文件和路径。Pwd显示当前文件的绝对路径.。Cd进入指定目录。More显示文件内容。Cp拷贝。Mkdir创建目录。tar 打包。zip压缩。unzip解压。ftp传送文件。 二基本概念 1版图设计 CIW命令解释窗口, Library 库,Reference Library相关库, Library Path库路径,Cell单元,View视图,Techfiler.tf工艺文件, cds.lib库管理文件, techfile.cds ASCII 文件,LSW图层选择窗口,display.drf图层显示文件。LayerPurpose Pair层次用途配对,Cellview Attributes and Properties单元视图属性,Instance单元,Snap Mode 光标按钮画线条或图形的模型。Stream。数据流(一个标准数据格式用在cad系统间传递物理设计数据) parameterized cells,参数化单元。Flatten,打平 设计方法 1 CIC设计流程 ①设计规划。②建库。③原理图输入。④电路仿真。⑤单元模块版图。⑥TOP 版图。⑦验证。⑧输出GDSII。⑨制掩膜。⑩流片封装测试。 2CIC建库的步骤,工艺文件和显示文件的使用。 建库进入设计项目所在的文件夹,打开名利窗口输入icfb,在ciw菜单栏中选择file-creat-creat new library,选择要连接的Techfiler.tf或者选择相应库作为链接库,后根据指示完成余下的操作 工艺文件p1-40说明图层连接,等效连接,不可被重叠,自动布线,设计规则等情况 ciw-technology-file-dump ,design,layout definations,ascll 命名.Tf,ok;/techpurposes /techlayers;/techdisplays;/techlayerpurposepriorities(图层目的优先);:q!(保存退出):wq!(写后保存退出);/ptap File-load 显示文件的使用:在显示资源编辑窗口里编辑并保存(display。drf)长期有效 添加新包,先编辑显示文件再在显示资源编辑窗口里编辑其填充等;file—save;tools-display resources-mergefile;分配图层目的配对。 3单元版图绘图方法及编辑基本方法, 新建,根据设计要求选择图层用不同的绘图命令绘制和按参数编辑、连接,测试4绘图及编辑常用命令的使用: Create— Rectangle 。create-rectangle left点拉升点 Instance、create-instance(名字不可改)填写库cell view 坐标等 Path、create-path 1点2点+回车/双击 Pcell、edit-hierarchy(分层)-make cell 填写,画长方形区域,ok Polygon、create- Polygon(F3),选择图层,点,点等,回车 Conics create-arc,点,点,点回车 1、 研究模拟集成电路的重要性:(1)首先,MOSFET 的特征尺寸越来越小,本征速度越来 越快;(2)SOC 芯片发展的需求。 2、 模拟设计困难的原因:(1)模拟设计涉及到在速度、功耗、增益、精度、电源电压等多 种因素间进行折衷,而数字电路只需在速度和功耗之间折衷;(2)模拟电路对噪声、串扰和其它干扰比数字电路要敏感得多;(3)器件的二级效应对模拟电路的影响比数字电路要严重得多;(4)高性能模拟电路的设计很少能自动完成,而许多数字电路都是自动综合和布局的。 3、 鲁棒性就是系统的健壮性。它是在异常和危险情况下系统生存的关键。所谓“鲁棒性”, 是指控制系统在一定的参数摄动下,维持某些性能的特性。 4、 版图设计过程:设计规则检查(DRC )、电气规则检查(ERC )、一致性校验(LVS )、RC 分布参数提取 5、 MOS 管正常工作的基本条件是:所有衬源(B 、S )、衬漏(B 、D )pn 结必须反偏 6、 沟道为夹断条件: ?GD GS DS T DS GS TH H V =V -≤V V V -V ≥V 7、 (1)截止区:Id=0;Vgs 1.什么叫IC 的集成度?目前先进的IC规模有多大? 集成度就是一块集成电路芯片中包含晶体管的数目,或者等效逻辑门数 2012年5月 71亿晶体管的NVIDIA的GPU 28nm 2.什么叫特征尺寸? 特征尺寸通常是指是一条工艺线中能加工的最小尺寸,反映了集成电路版图图形的精细程度,如MOS晶体管的沟道长度,DRAM结构里第一层金属的金属间距(pitch)的一半。 3.目前主流的硅圆片直径是多少? 12英寸 4.什么叫NRE(non-recurring engineering)成本? 支付给研究、开发、设计和测试某项新产品的单次成本。在集成电路领域主要是指研发人力成本、硬件设施成本、CAD工具成本以及掩膜、封装工具、测试装置的成本,产量小,费用就高。 5.什么叫recurring costs? 重复性成本,每一块芯片都要付出的成本,包括流片费、封装费、测试费。也称可变成本,指直接用于制造产品的费用,因此与产品的产量成正比。包括:产品所用部件的成本、组装费用以及测试费用。 6.什么叫有比电路? 靠两个导通管的宽长比不同,从而呈现的电阻不同来决定输出电压,它是两个管子分压的结果,电压摆幅由管子的尺寸决定。 7.IC制造工艺有哪几种? 双极型模拟集成电路工艺、CMOS工艺、BiCMOS工艺 8.什么叫摩尔定律?摩尔定律面临什么样的挑战? 当价格不变时,积体电路上可容纳的电晶体数目,约每隔24个月(现在普遍流行的说法是“每18个月增加一倍”)便会增加一倍,性能也将提升一倍;或者说,每一美元所能买到的电脑性能,将每隔18个月翻两倍以上。 面临面积、速度和功耗的挑战。 9.什么叫后摩尔定律?后摩尔定律下IC设计面临哪些挑战?解决方案? 多重技术创新应用向前发展,即在产品多功能化(功耗、带宽等)需求下,将硅基CMOS和非硅基等技术相结合,以提供完整的解决方案来应对和满足层出不穷的新市场发展。 挑战:a单芯片的处理速度越来越快,主频越来越高,热量越来越多b.互联线延迟增大解决方案:1.多核、低功耗设计2.3D互联、无线互联、光互连 延续摩尔定律“尺寸更小、速度更快、成本更低”,还会利用更多的技术创新:节能、环保、舒适以及安全性 架构:多核散热:研发新型散热器更薄的材料:用碳纳米管组装而成的晶体管速度更快的晶体管:超薄石墨烯做的晶体管纳米交叉线电路元件:忆阻器 光学互联器件分子电路、分子计算、光子计算、量子计算、生物计算 10. IC按设计制造方法不同可以分为哪几类? 全定制IC:硅片各掩膜层都要按特定电路的要求进行专门设计 半定制IC:全部逻辑单元是预先设计好的,可以从单元苦衷调用所需单元来掩模图形,可使用相应的EDA软件,自动布局布线 集成电路的设计方法探讨 摘要:21世纪,信息化社会到来,时代的进步和发展离不开电子产品的不断进步,微电子技术对于各行各业的发展起到了极大的推进作用。集成电路(integratedcircuit,IC)是一种重要的微型电子器件,在包括数码产品、互联网、交通等领域都有广泛的应用。介绍集成电路的发展背景和研究方向,并基于此初步探讨集成电路的设计方法。 关键词集成电路设计方法 1集成电路的基本概念 集成电路是将各种微电子原件如晶体管、二极管等组装在半导体晶体或介质基片上,然后封装在一个管壳内,使之具备特定的电路功能。集成电路的组成分类:划分集成电路种类的方法有很多,目前最常规的分类方法是依据电路的种类,分成模拟集成电路、数字集成电路和混合信号集成电路。模拟信号有收音机的音频信号,模拟集成电路就是产生、放大并处理这类信号。与之相类似的,数字集成电路就是产生、放大和处理各种数字信号,例如DVD重放的音视频信号。此外,集成电路还可以按导电类型(双极型集成电路和单极型集成电路)分类;按照应用领域(标准通用集成电路和专用集成电路)分类。集成电路的功能作用:集成电路具有微型化、低能耗、寿命长等特点。主要优势在于:集成电路的体积和质量小;将各种元器件集中在一起不仅减少了外界电信号的干扰,而且提高了运行 速度和产品性能;应用方便,现在已经有各种功能的集成电路。基于这些优异的特性,集成电路已经广泛运用在智能手机、电视机、电脑等数码产品,还有军事、通讯、模拟系统等众多领域。 2集成电路的发展 集成电路的起源及发展历史:众所周知,微电子技术的开端在1947年晶体管的发明,11年后,世界上第一块集成电路在美国德州仪器公司组装完成,自此之后相关的技术(如结型晶体管、场效应管、注入工艺)不断发展,逐渐形成集成电路产业。美国在这一领域一直处于世界领先地位,代表公司有英特尔公司、仙童公司、德州仪器等大家耳熟能详的企业。集成电路的发展进程:我国集成电路产业诞生于六十年代,当时主要是以计算机和军工配套为目标,发展国防力量。在上世纪90年代,我国就开始大力发展集成电路产业,但由于起步晚、国外的技术垄断以及相关配套产业也比较落后,“中国芯”始终未能达到世界先进水平。现阶段我国工业生产所需的集成电路主要还是依靠进口,从2015年起我国集成电路进口额已经连续三年比原油还多,2017年的集成电路进口额超过7200亿元。因此,在2018年政府工作报告中把推动集成电路产业发展放在了五大突出产业中的首位,并且按照国家十三五规划,我国集成电路产业产值到2020年将会达到一万亿元。中国比较大型的集成电路设计制造公司有台积电、海思、中兴等,目前已在一些技术领域取得了不错的成就。集成电路的发展方向:提到集成电路的发展,就必须要说到摩尔定律:集成度每18个月翻一番。而现今正处在 建设工程概述 (一)建设工程概念 (二)建设项目分类(新内容) (三)建设项目的组成 (四)基本建设的一般程序 (五)建筑工程分类 (六)建筑工程技术经济指标 (七)建设法规 (八)建设法规体系 (九)城市规划 (十)建筑工程招标与投标 (十一)建设工程质量管理条例 (十二)工程建设监理 (一)建设工程概念 建设工程属于固定资产投资对象。包括以下内容 1、建筑工程。 建筑工程包括建筑物和构筑物的建造。建筑物为房屋。构筑物有桥梁、隧道、水力及园林化工程等。 2、安装工程 3土木工程 桥梁、公路、铁路、隧道、水利工程、给排水工程等。 固定资产建设活动是通过具体项目建设实施。建设项目应该在技术上、构成上及建设过程上满足三个要求,具体参见教材 (二)建设项目分类(新内容) 一个具体的基本建设工程,通常就是一个建设项目。 1.按建设性质分:新建项目、扩建项目、拆建项目、重建项目 2.按建设规模分:大型、中型、小型项目 3、按国民经济各行业性质和特点分:竞争性项目、基础性项目、公益性项目 (三)建设项目的组成 1、单项工程 单项工程是指在一个建设项目中,具有独立的设计文件,竣工后可以独立发挥生产能力或效益的工程。 2、单位工程 单位工程是竣工后一般不能独立发挥生产能力或效益,但具有独立设计,可以独立组织施工的工程。 单位工程一般是进行工程成本核算的对象。单位工程产品价格是通过编制单位工程施工图概预算来确定的 3、分部工程 分部工程是单位工程的组成部分。按照工程部位、设备种类和型号、使用材料的不同,可将一个单位工程分解为若干个分部工程。 4、分项工程 分项工程是分部工程的组成部分。按照不同的施工方法、不同的材料、不同的规格,可将一个分部工程分解为若干个分项工程。分项工程是计算工、料及资金消耗的最基本的构造要素。建筑工程预算的编制就是从最小的分项工程开始,由小到大逐步汇总而完成的。 (四)基本建设的一般程序集成电路设计基础_期末考试题

建设工程项目流程概述

集成电路版图复习课答案总结

模拟集成电路设计期末试卷

建设项目评估概述

(完整版)集成电路设计复习题及解答

集成电路设计方法的发展历史

专用集成电路

《模拟集成电路设计》复习

集成电路设计基础复习分析

集成电路设计方法--复习提纲

集成电路设计流程

专用集成电路AD的设计

集成电路设计基础

模拟集成电路复习

集成电路设计方法--复习提纲

集成电路的设计方法探讨

建设工程概述