硬件描述语言范例

- 格式:doc

- 大小:80.50 KB

- 文档页数:13

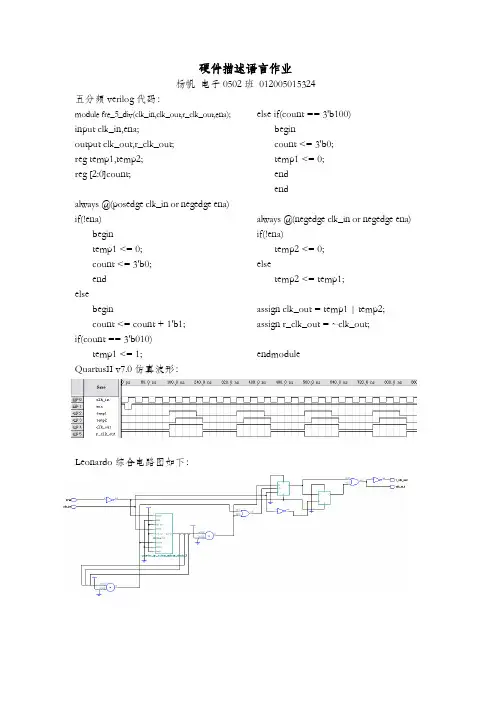

硬件描述语言作业杨帆电子0502班012005015324 五分频verilog代码:module fre_5_div(clk_in,clk_out,r_clk_out,ena); input clk_in,ena;output clk_out,r_clk_out;reg temp1,temp2;reg [2:0]count;always @(posedge clk_in or negedge ena) if(!ena)begintemp1 <= 0;count <= 3'b0;endelsebegincount <= count + 1'b1;if(count == 3'b010)temp1 <= 1; else if(count == 3'b100)begincount <= 3'b0;temp1 <= 0;endendalways @(negedge clk_in or negedge ena) if(!ena)temp2 <= 0;elsetemp2 <= temp1;assign clk_out = temp1 | temp2; assign r_clk_out = ~clk_out;endmoduleQuartusII v7.0仿真波形:Leonardo综合电路图如下:1101序列检测器verilog代码:module Moorefsm (clk,rst,a,z); input clk,rst;input a;output z;reg z;reg [3:0] currentstate,nextstate; parameter s0=4'b0000; parameter s1=4'b0001; parameter s2=4'b0010; parameter s3=4'b0011; parameter s4=4'b0100;always@(posedge clk or negedge rst) if(!rst)currentstate<=0;elsecurrentstate<=nextstate;always@(currentstate or a) case(currentstate)s0:nextstate=(a==1)?s1:s0;s1:nextstate=(a==0)?s2:s1;s2:nextstate=(a==1)?s3:s0;s3:nextstate=(a==1)?s4:s2;s4:nextstate=(a==1)?s1:s2;default:nextstate=s0; endcasealways@(rst or currentstate) if(!rst)z=0;else case (currentstate)s4:z=1;default:z=0;endcaseendmoduleQuartusII v7.0仿真波形如下:Leonardo 综合电路图如下:12小时计数器verilog代码如下:module clock(clk,rst,sec,mini,hour);input clk,rst;output [5:0]sec,mini,hour;reg [5:0]sec,mini,hour;reg [5:0]temp1,temp2,temp3;always@(posedge clk or negedge rst)if(!rst)begintemp1<=6'b0;temp2<=6'b0;temp3<=6'b0;endelsebegintemp1<=temp1+6'b1;if(temp1==6'b111011)begintemp1<=0; temp2<=temp2+6'b1;if(temp2==6'b111011)begintemp2<=0;temp3<=temp3+6'b1;if(temp3==6'b001011)temp3<=0;endendendalways@(temp1 or temp2 or temp3)beginsec=temp1;mini=temp2;hour=temp3;endendmoduleLeonardo综合电路图如下:。

硬件PRD模板范文硬件产品PRD模板1.产品概述:在这一部分,简要介绍硬件产品的名称、功能和主要特点。

包括产品的定位、主要用户群体以及产品的核心竞争力。

2.需求背景:简要描述市场需求和用户需求,阐明为什么需要这款硬件产品。

可以结合数据分析市场规模、用户反馈等。

3.目标用户:详细描述产品的目标用户群体,包括用户的特征、使用场景和需求。

这部分需求与产品功能设计有密切关联。

4.产品功能:在这一部分,详细列出硬件产品的各项功能。

注意要细化功能,并与需求背景和目标用户保持一致。

5.产品规格:列出硬件产品的具体规格,包括尺寸、重量、材质等。

6.系统架构:描述硬件产品的系统架构,包括硬件组成和各部分之间的关系。

可以使用图表和示意图进行展示。

7.界面设计:描述硬件产品的界面设计,包括显示屏、按键、接口等。

可以结合视觉设计进行展示。

8.用户交互:详细描述用户和硬件产品之间的交互方式,包括按钮操作、手势识别等。

9.使用场景:描述用户在不同场景下使用硬件产品的情况,包括室内、户外、工作环境等。

10.系统要求:列出硬件产品的运行环境要求,包括操作系统、处理器、内存等。

11.安全防护:阐述硬件产品的安全防护措施,包括数据加密、指纹识别等。

12.故障排除:介绍硬件产品发生故障时的排查和解决办法。

13.售后服务:详细描述售后服务内容和方式,包括维修、退换货政策等。

14.附录:包括产品原理图、尺寸图、电路图等相关附件。

以上是硬件产品PRD的主要内容和模板。

根据具体产品的特点和需求,可以适当增减相关内容。

在编写PRD时,要结合市场调研和用户需求,确保产品的功能和特点能够满足用户的需求,提升产品竞争力。

计算机硬件介绍英语作文## What is computer hardware?##。

Computer hardware is the physical components of a computer system. It includes all the electronic devicesthat make up the computer, as well as the physical devices that allow the computer to function. The hardware components of a computer system can be divided into two main categories: internal components and external components.Internal components are the components that are located inside the computer case. These components include the motherboard, processor, memory (RAM), storage devices (hard drives and solid-state drives), and graphics card. The motherboard is the main circuit board of the computer andit connects all of the other internal components. The processor is the brain of the computer and it is responsible for executing instructions. Memory (RAM) stores the instructions and data that are being processed by theprocessor. Storage devices store the operating system, applications, and files. The graphics card is responsiblefor displaying images on the monitor.中文回答:计算机硬件是计算机系统中的物理组件,它包括组成计算机的所有电子设备以及实现计算机功能的物理设备,计算机系统的硬件组件可分为: 内部组件和外部组件。

介绍PC硬件的英语作文Title: An Overview of PC Hardware Components。

Introduction:In the realm of computing, understanding the fundamental components of a personal computer (PC) is crucial. These components work in harmony to execute tasks efficiently. In this essay, we will delve into the various hardware components that constitute a typical PC.Central Processing Unit (CPU):The CPU serves as the brain of the computer, executing instructions and performing calculations. It comprises arithmetic logic units (ALUs), control units, and registers. Modern CPUs have multiple cores, allowing for parallel processing and improved performance.Random Access Memory (RAM):RAM is temporary storage used to store data and instructions that the CPU needs to access quickly. It is volatile memory, meaning it loses its contents when the power is turned off. RAM capacity significantly impacts a computer's multitasking ability and overall responsiveness.Motherboard:The motherboard is the main circuit board that connects all other components of the PC. It houses the CPU, RAM, storage devices, and expansion cards. It also facilitates communication between these components via buses and ports.Storage Devices:Storage devices store data permanently or semi-permanently. Hard Disk Drives (HDDs) use spinning magnetic disks to store data, while Solid State Drives (SSDs)utilize flash memory for faster read/write speeds. SSDs are becoming increasingly popular due to their speed and reliability.Graphics Processing Unit (GPU):The GPU is responsible for rendering images, videos, and animations. It offloads graphical tasks from the CPU, improving overall system performance, especially in gaming and multimedia applications. GPUs have their dedicated memory called Video RAM (VRAM).Power Supply Unit (PSU):The PSU converts electrical power from the outlet into a form suitable for the computer's internal components. It provides stable voltages to ensure the proper functioning of the CPU, GPU, and other hardware components.Cooling System:To prevent overheating, PCs utilize cooling systems such as fans, heat sinks, and liquid cooling solutions. These components dissipate heat generated by the CPU, GPU, and other high-power hardware, ensuring stable operationand prolonging component lifespan.Input and Output Devices:Input devices like keyboards, mice, and touchscreens allow users to interact with the computer, while output devices such as monitors, printers, and speakers display information or produce output generated by the computer.Expansion Cards:Expansion cards are additional circuit boards inserted into expansion slots on the motherboard. Common expansion cards include graphics cards, sound cards, and network interface cards, which enhance the capabilities of the computer.Conclusion:Understanding the various hardware components of a PC is essential for anyone interested in computing. Each component plays a vital role in the overall performance andfunctionality of the system. By comprehending these components and their functions, users can make informed decisions when building or upgrading their PCs.。

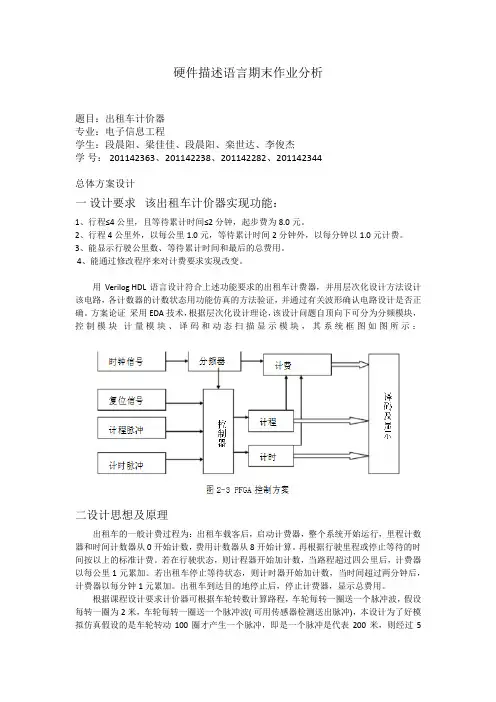

硬件描述语言期末作业分析题目:出租车计价器专业:电子信息工程学生:段晨阳、梁佳佳、段晨阳、栾世达、李俊杰学号: 201142363、201142238、201142282、201142344总体方案设计一设计要求该出租车计价器实现功能:1、行程≤4公里,且等待累计时间≤2分钟,起步费为8.0元。

2、行程4公里外,以每公里1.0元,等待累计时间2分钟外,以每分钟以1.0元计费。

3、能显示行驶公里数、等待累计时间和最后的总费用。

4、能通过修改程序来对计费要求实现改变。

用Verilog HDL语言设计符合上述功能要求的出租车计费器,并用层次化设计方法设计该电路,各计数器的计数状态用功能仿真的方法验证,并通过有关波形确认电路设计是否正确。

方案论证采用EDA技术,根据层次化设计理论,该设计问题自顶向下可分为分频模块,控制模块计量模块、译码和动态扫描显示模块,其系统框图如图所示:二设计思想及原理出租车的一般计费过程为:出租车载客后,启动计费器,整个系统开始运行,里程计数器和时间计数器从0开始计数,费用计数器从8开始计算。

再根据行驶里程或停止等待的时间按以上的标准计费。

若在行驶状态,则计程器开始加计数,当路程超过四公里后,计费器以每公里1元累加。

若出租车停止等待状态,则计时器开始加计数,当时间超过两分钟后,计费器以每分钟1元累加。

出租车到达目的地停止后,停止计费器,显示总费用。

根据课程设计要求计价器可根据车轮转数计算路程,车轮每转一圈送一个脉冲波,假设每转一圈为2米,车轮每转一圈送一个脉冲波( 可用传感器检测送出脉冲),本设计为了好模拟仿真假设的是车轮转动100圈才产生一个脉冲,即是一个脉冲是代表200米,则经过5分频器后是每1Km送一个脉冲到里程计算模块,这样方便在软件里面仿真观察,若要下载到实物应用中去,通过实际车轮周长自己设置不同的分频电路来达到产生任意精度的计程距离模块。

而当车停止的时候通过分频模块产生秒脉冲,通过计时要求来产生计费,本设计重点就在计费控制模式模块和计费模块这两大模块的设计,则根据出租车计费器的工作过程,本系统采用分层次、分模块的方式设计。

电脑硬件介绍范文电脑硬件是指构成电脑主体的各个组成部分,包括中央处理器(CPU)、主板、内存、硬盘、显卡、显示器、键盘、鼠标等。

在这篇文章中,我将为您详细介绍每个硬件组件的功能和作用。

首先,让我们来看看中央处理器(CPU)。

中央处理器是电脑的大脑,它负责执行和控制整个计算机系统的各种操作。

CPU的速度决定了计算机的运行速度和处理能力。

现在流行的CPU厂商有英特尔和AMD,它们生产了各种不同型号和系列的处理器,以满足不同用户的需求。

接下来是主板,也称为系统板或母板。

主板是电脑系统的核心组件,它提供了连接各种硬件设备的接口和插槽。

主板上有集成电路、追踪线路和连接器,用来连接中央处理器、内存、硬盘、显卡等各个硬件组件。

主板的质量和性能直接影响着计算机的稳定性和速度。

内存是存储数据和程序的地方,它是电脑中的临时存储器。

内存通常分为主内存和辅助内存,主内存是CPU直接访问的存储器,辅助内存是用来存储大容量数据和程序的设备,如硬盘、固态硬盘等。

内存的大小决定了计算机可以同时处理的任务数量和运行程序的速度。

硬盘是用来存储数据的设备,它通常是计算机中最大容量的存储器。

硬盘有机械硬盘(HDD)和固态硬盘(SSD)两种类型。

机械硬盘使用磁性材料和机械运动的方式来存储和访问数据,而固态硬盘则使用闪存存储器来实现数据的存储和访问。

固态硬盘的读写速度比机械硬盘快很多,因此越来越受到用户的青睐。

显卡是负责显示图像和图形的设备,它的性能直接影响计算机的图像处理能力和游戏性能。

显卡有独立显卡和集成显卡两种类型。

独立显卡是一种独立于主板的显卡,它有自己的显存和处理器,可以提供更好的图像处理性能。

集成显卡则是集成在主板上的显卡,它的性能比较低,适合一般办公和娱乐使用。

显示器是电脑输出图像和文字的设备,它通过显示技术将计算机处理的数据转化为可视化的图像。

显示器通常由液晶显示屏或LED显示屏组成,其尺寸和分辨率决定了显示效果的清晰度和细腻程度。

计算机硬件介绍英语作文Title: Introduction to Computer Hardware.In the modern era of technology, computer hardware serves as the backbone of all digital devices, enabling them to perform various tasks efficiently. Computer hardware refers to the physical components that constitute a computer system, including the input/output devices, central processing unit (CPU), memory, storage devices, and other internal components. This article aims to provide a comprehensive introduction to computer hardware, exploring its various components, functions, and significance in today's digital world.Firstly, let's delve into the central processing unit (CPU), the brain of the computer. The CPU is responsiblefor executing instructions and performing calculations, ensuring the smooth operation of the computer. It consists of the arithmetic logic unit (ALU), which performs arithmetic and logical operations, and the control unit(CU), which manages the flow of instructions. The speed and performance of a CPU are determined by its clock speed, cache memory, and the number of cores it possesses. Modern CPUs often feature multi-core architectures, allowing them to handle multiple tasks simultaneously, enhancing overall computing efficiency.Memory, also known as RAM (Random Access Memory), serves as the temporary storage space for data and instructions required by the CPU. RAM is.。

硬件概要设计范文一、硬件概述本硬件概要设计针对某具体项目或产品,对硬件系统进行全面的概述和描述。

设计目标是在满足项目或产品功能需求的基础上,确保硬件系统的性能、可靠性、成本等各方面达到最佳状态。

二、硬件需求分析通过对项目或产品的功能需求进行分析,明确硬件系统的基本功能、性能要求和扩展性等方面的需求。

具体包括输入输出接口、存储容量、数据处理速度、电源供应等方面。

三、硬件架构设计根据硬件需求分析,设计硬件系统的整体架构。

包括中央处理器、内存、存储设备、输入输出接口等主要组件的选择和配置。

同时,需要考虑系统的扩展性和可维护性,为未来升级和扩展预留空间。

四、硬件模块划分将硬件系统划分为若干个模块,每个模块负责实现特定的功能。

模块之间的接口定义清晰,便于模块间的集成和调试。

模块划分应遵循高内聚、低耦合的原则,提高代码可维护性和可复用性。

五、硬件接口定义详细定义各个模块之间的接口,包括物理接口、电气接口和软件接口。

物理接口包括连接方式、传输介质等;电气接口包括信号类型、电平范围等;软件接口包括通信协议、数据格式等。

确保各个模块之间的协调工作。

六、硬件性能指标根据项目或产品的性能要求,设定硬件系统的性能指标。

包括处理速度、存储容量、功耗等关键性能指标,确保系统在正常运行情况下能够满足要求。

同时,考虑到未来扩展性需求,设定可扩展性指标。

七、硬件可靠性设计采取一系列措施提高硬件系统的可靠性。

包括采用高可靠性的器件和材料、实施冗余设计、进行故障预测和预防等。

同时,建立完善的故障检测和处理机制,确保系统在出现故障时能够及时恢复运行。

八、硬件成本预算根据硬件设计方案和器件选型,进行成本预算。

包括器件采购成本、制造成本、测试成本等各方面费用。

在保证系统性能和可靠性的前提下,尽可能降低成本,提高项目的经济效益。

九、总结与展望本硬件概要设计为项目或产品的硬件系统提供了全面的设计方案。

在满足功能需求的基础上,注重性能、可靠性和成本的平衡考虑。

硬件描述语言基础——层次结构硬件描述语言,这个名字听起来就很高大上对吧?听上去像是高科技的神秘领域,感觉只属于那些戴着眼镜,手指在键盘上飞舞的工程师们。

不过别担心,我保证今天不谈深奥的数学公式,也不谈复杂的电路图,我们就聊聊它的层次结构,嗯,听起来也许有点复杂,但它并没有想象中的那么让人头疼。

说到层次结构啊,咱们可以把它理解成搭积木。

你玩过吧?就是先搭一个底座,再慢慢地往上堆,最后堆得高高的,牢牢地站在那儿不倒。

硬件描述语言中的层次结构也是这么回事。

你首先定义一些基本的“积木”,这些积木就像是模块,简单又清晰。

然后你再把这些模块组合起来,组合成更大的模块,最终构建出一个完整的硬件系统。

你想象一下,最底层的积木是最简单的,像是一个电路门或者寄存器,它们的功能也比较简单,可能只是开关状态的控制。

可是,随着你逐渐堆积,那个复杂的大系统就慢慢显现出来了。

这就是硬件描述语言的层次结构。

它让你在编写代码的时候,能够把复杂的事情拆解成一个个小块,然后按需要组合。

就像是做饭一样,一开始你只是拿了些原材料,然后你把这些原材料按照一定的顺序,做成一道美味的菜肴。

如果没有这些层次化的设计,整个电路就会像是一锅乱炖,什么东西都有,但是没法吃。

咱们再说说硬件描述语言里最基础的那些东西。

最小的组成单位通常就是“模块”。

嗯,模块呢,可以理解为一种功能单元。

你可以用它来表示一个简单的加法器,一个寄存器,甚至是一个时钟信号的生成器。

每个模块都可以做特定的事,简简单单。

把这些模块像拼图一样组合到一起,就能实现更复杂的功能。

比方说,你想设计一个处理器,你可能会用到加法器、寄存器、存储器、控制单元……这些模块加在一起,就能组成一个完整的处理器。

是不是觉得有点意思?不过啊,光有这些模块还不够。

它们之间的连接也很重要。

你得告诉这些模块怎么互相沟通,怎么把数据从一个模块传到另一个模块。

就好比你邀请了一堆朋友来参加派对,他们各自都有自己的任务。

硬件描述语言实验题目:四位加法器实验

学院数学与计算机学院

学科门类电气信息类

专业xxxxxxxxxx

学号xxxxxxxxxxx

姓名xxxx

指导教师xxxx

201x年x 月x 日

硬件描述语言

一、实验题目

四位加法器实验

二、实验环境

PC个人计算机、Windows XP操作系统、Quartus II集成开发环境软件。

三、实验目的和要求

进一步练习VHDL语言设计工程的建立与仿真的步骤和方法、熟悉VHDL语言三种描述方法。

设计一个四位加法器,实体名称为“adder4_3”,其引脚及其功能如下表。

要求应用一位全加器(实验二中所实现的)按如下电路图通过结构描述方式构造四位加法器。

本实验用实验二“full_adder”的实体作为元件,用port map语句描述出来将下图的电路,实现四位加法器,并与实验三、实验四的加法器进行比较。

四、实验内容

五、实验结果

六、实验总结

七、附录。

硬件销售范本尊敬的客户:感谢您选择我们公司作为您的硬件设备供应商。

为了更好地满足您的需求并确保合作顺利进行,我们特别为您准备了以下硬件销售范本,请您参考。

1. 产品介绍我们公司提供各类高质量、可靠性强的硬件设备,涵盖计算机硬件、网络设备以及外部设备等。

我们工作人员经过专业培训,具备丰富的产品知识和销售经验,为您提供最优质的服务。

2. 产品特点与优势(这部分根据不同的硬件设备进行描述,可以列举几个代表性的产品进行介绍,并突出其特点和优势)3. 技术支持与售后服务我们公司拥有一支经验丰富、技术过硬的客户支持团队,他们将全程协助您解决硬件设备使用过程中的各种问题和疑虑。

无论是技术支持、产品维修还是软件安装,我们将为您提供及时高效的售后服务,确保您的设备运行顺畅。

4. 价格与付款方式为了给您提供最具竞争力的价格,我们公司与多家供应商建立了密切的合作关系,并严格控制成本。

我们可以根据您的需求提供个性化的价格方案,并提供多样化的付款方式以便您选择。

5. 订单流程(在这里描述订单的整个流程,包括提交订单、确认合同、支付定金、产品发货等。

具体内容可以根据实际情况进行调整)6. 合作协议为了确保双方的权益,我们将遵循合作协议的规定进行合作。

合作协议将明确规定合作期限、产品交付时间、售后服务等条款,以确保双方权益得到有效保障。

7. 合作案例我们公司已经与众多客户建立了长期稳定的合作关系,成功完成了大量的项目。

以下是我们与某客户合作的案例简介:(描述合作案例,包括客户需求、我们提供的解决方案、客户满意度等)尊敬的客户,我们衷心希望能够与您合作,并为您提供优质的硬件设备和完善的服务。

我们相信,我们公司的产品将能够满足您的需求,并成为您的长期合作伙伴。

如有任何疑问或需进一步讨论,请随时联系我们的销售团队。

我们期待与您的合作!谢谢!此为500字提纲,具体内容可根据实际情况进行扩展和修改。

形容硬件的词-回复什么是形容硬件的词?硬件是指计算机系统中可触及和可见的实体部分,包括了计算机主机、显示器、键盘、鼠标等等。

形容硬件的词可以用来描述硬件的特性、功能、性能和外观等方面。

在以下的文章中,我将使用“高性能”作为主题来描述硬件的特点。

第一步:介绍高性能硬件的意义和重要性(约200-300字)高性能硬件是解决计算机系统处理速度和效率的重要手段。

随着科技的不断发展,我们对于计算机的要求也越来越高,特别是在处理大数据、进行复杂计算和执行高负载任务时。

高性能硬件可以提升计算机系统的响应速度、加快数据传输和处理速度,并提供更好的用户体验。

它不仅可以满足专业用户和高负载任务的需求,也可以提升日常办公和娱乐的效率和体验。

第二步:介绍高性能硬件的不同类型及其功能特点(约500-600字)高性能硬件可以涉及到计算机系统中的多个组件,包括中央处理器(CPU)、图形处理器(GPU)、内存、硬盘以及其他外设等。

这些硬件组件的不同类型和性能特征决定了计算机的整体性能。

首先,中央处理器(CPU)是计算机系统中的核心部件,它负责执行计算和逻辑操作。

高性能的CPU具有更高的时钟频率和更多的核心数量,这样就可以更快地执行指令并处理数据。

高性能CPU能够提供更快的计算速度,从而加快软件的运行和响应速度。

其次,图形处理器(GPU)在处理图形和图像方面具有独特的优势。

高性能GPU能够处理大量的图形数据和渲染效果,提供更流畅的游戏画面和图像处理能力。

对于需要进行复杂图形计算和3D渲染的应用程序和游戏来说,高性能GPU尤为重要。

内存是计算机系统中的高速存储器,用于存储正在运行的程序和数据。

高性能内存具有更高的数据传输速度和更大的容量,可以提供更快的数据访问和处理能力。

特别是在多任务处理和运行大型应用程序时,高性能内存可以显著提升计算机的速度和稳定性。

硬盘是用于存储数据的设备,它的性能对于启动速度和文件读写速度有着重要影响。

高性能硬盘通常使用固态硬盘(SSD),它具有更快的数据传输速度和更低的读写延迟。

硬件描述语言VHDL实例程序整理目录硬件描述语言VHDL实例程序整理 (1)1.动态扫描显示程序 (2)2.分频器设计程序 (4)3. 8位移位寄存器 (6)4.BCD计数器设计(任意进制) (7)5.基于状态机的计数器设计 (8)6.LED灯控制 (10)7.BCD显示译码器 (12)8.100M频率计设计 (13)1.动态扫描显示程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DTSM_XS ISPORT(CLK:IN STD_LOGIC;B14,B13,B12,B11,B10,B9,B8,B7,B6,B5,B4,B3,B2,B1:IN STD_LOGIC_VECTOR(3 DOWNTO 0);X:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);LED_SELECT: OUT STD_LOGIC_VECTOR(13 DOWNTO 0));END;ARCHITECTURE BEHA VE OF DTSM_XS ISSIGNAL BCD_IN: STD_LOGIC_VECTOR (3 DOWNTO 0);SIGNAL CNT2: INTEGER RANGE 0 TO 13;BEGINP1:PROCESS(CLK)BEGINIF CLK'EVENT AND CLK='1' THEN --升沿触发IF CNT2>=13 THEN –CONTROL LOOPCNT2<=0;ELSECNT2<=CNT2+1;END IF;END IF;END PROCESS;P2:PROCESS(CNT2,B14,B13,B12,B11,B10,B9,B8,B7,B6,B5,B4,B3,B2,B1)BEGINCASE CNT2 ISWHEN 0=>LED_SELECT<="11111111111110";BCD_IN<=B1;WHEN 1=>LED_SELECT<="11111111111101";BCD_IN<=B2;WHEN 2=>LED_SELECT<="11111111111011";BCD_IN<=B3;WHEN 3=>LED_SELECT<="11111111110111";BCD_IN<=B4;WHEN 4=>LED_SELECT<="11111111101111";BCD_IN<=B5;WHEN 5=>LED_SELECT<="11111111011111";BCD_IN<=B6;WHEN 6=>LED_SELECT<="11111110111111";BCD_IN<=B7;WHEN 7=>LED_SELECT<="11111101111111";BCD_IN<=B8;WHEN 8=>LED_SELECT<="11111011111111";BCD_IN<=B9;WHEN 9=>LED_SELECT<="11110111111111";BCD_IN<=B10;WHEN 10=>LED_SELECT<="11101111111111";BCD_IN<=B11;WHEN 11=>LED_SELECT<="11011111111111";BCD_IN<=B12;WHEN 12=>LED_SELECT<="10111111111111";BCD_IN<=B13;WHEN 13=>LED_SELECT<="01111111111111";BCD_IN<=B14;END CASE;END PROCESS;P3:PROCESS(BCD_IN)BEGINCASE BCD_IN ISWHEN "0000"=>X<="1111110";WHEN "0001"=>X<="0110000";WHEN "0010"=>X<="1101101";WHEN "0011"=>X<="1111001";WHEN "0100"=>X<="0110011";WHEN "0101"=>X<="1011011";WHEN "0110"=>X<="1011111";WHEN "0111"=>X<="1110000";WHEN "1000"=>X<="1111111";WHEN "1001"=>X<="1111011";WHEN OTHERS=>X<="0000000";END CASE;END PROCESS;END;2.分频器设计程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY DIVIDER_1M ISPORT(CLK: IN STD_LOGIC;CLK_1HZ: OUT STD_LOGIC;CLK_500HZ:BUFFER STD_LOGIC);END DIVIDER_1M;ARCHITECTURE RTL OF DIVIDER_1M ISSIGNAL CNT1:INTEGER RANGE 0 TO 1999; SIGNAL CNT2:INTEGER RANGE 0 TO 499;BEGINP1:PROCESS(CLK)BEGINIF CLK'EVENT AND CLK='1' THENIF CNT1=CNT1'HIGH THENCNT1<=0;ELSECNT1<=CNT1+1;END IF;END IF;END PROCESS;P2:PROCESS(CLK,CNT1)BEGINIF CLK'EVENT AND CLK='1' THENIF CNT1>=999 THENCLK_500HZ<='1';ELSECLK_500HZ<='0';END IF;END IF;END PROCESS;P3:PROCESS(CLK_500HZ)BEGINIF CLK_500HZ'EVENT AND CLK_500HZ='1' THEN IF CNT2=CNT2'HIGH THENCNT2<=0;ELSECNT2<=CNT2+1;END IF;END IF;END PROCESS;P4:PROCESS(CLK_500HZ,CNT2)BEGINIF CLK_500HZ'EVENT AND CLK_500HZ='1' THEN IF CNT2>=249 THENCLK_1HZ<='1';ELSECLK_1HZ<='0';END IF;END IF;END PROCESS;END RTL;3. 8位移位寄存器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY REG8 ISPORT(LOAD,CLR,DIRE,EN,CLK:IN STD_LOGIC;DA TA :IN STD_LOGIC_VECTOR(7 DOWNTO 0);DOUT :BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0)); END REG8;ARCHITECTURE A OF REG8 ISBEGINPROCESS(LOAD,CLR,DIRE,EN,CLK)V ARIABLE X:STD_LOGIC;BEGINIF LOAD='1' THEN DOUT<=DATA;ELSIF CLR='1' THEN DOUT<="00000000";ELSIF EN='1' THEN DOUT<=DOUT;ELSIF CLK'EVENT AND CLK='1' THENIF DIRE='1'THENX:=DOUT(7);DOUT(7 DOWNTO 1)<=DOUT(6 DOWNTO 0);DOUT(0)<=X;ELSEX:=DOUT(0);DOUT(6 DOWNTO 0)<=DOUT(7 DOWNTO 1);DOUT(7)<=X;END IF;END IF;END IF;END PROCESS;END A;4.BCD计数器设计(任意进制)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT365 ISPORT(CLK,RESET:IN STD_LOGIC;DAOUT:OUT STD_LOGIC_VECTOR (9 DOWNTO 0)); END;ARCHITECTURE FUN OF CNT365 ISSIGNAL COUNT: STD_LOGIC_VECTOR(9 DOWNTO 0); BEGINDAOUT <= COUNT;P1:PROCESS(CLK,RESET)BEGINIF (RESET='1') THENCOUNT <= "0000000000";ELSIF (CLK'EVENT AND CLK='1') THENIF COUNT(9 DOWNTO 0)="1101100100"THENCOUNT(9 DOWNTO 0)<="0000000000";ELSIF COUNT(7 DOWNTO 0)="10011001" THENCOUNT<=COUNT + "01100111";ELSIF COUNT(3 DOWNTO 0)="1001" THENCOUNT<=COUNT + "0111";ELSECOUNT <= COUNT + 1;END IF;END IF;END PROCESS P1;END FUN;5.基于状态机的计数器设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY STATEMACHINE_COUNTER ISPORT(CLR,CLK: IN STD_LOGIC;Q:OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); END;ARCHITECTURE A OF STA TEMACHINE_COUNTER IS TYPE STA TE_TYPE IS (S0,S1,S2,S3,S4,S5,S6);SIGNAL PRESENT_STATE,NEXT_STA TE: STATE_TYPE;BEGINP1:PROCESS(CLK,CLR)BEGINIF CLR='1' THENPRESENT_STATE<=S0;ELSIF CLK'EVENT AND CLK='1' THENPRESENT_STA TE<=NEXT_STATE;END IF;END PROCESS P1;P2:PROCESS(CLK,PRESENT_STA TE)BEGINCASE PRESENT_STATE ISWHEN S0=>NEXT_STA TE<=S1;WHEN S1=>NEXT_STA TE<=S2;WHEN S2=>NEXT_STA TE<=S3;WHEN S3=>NEXT_STA TE<=S4;WHEN S4=>NEXT_STA TE<=S5;WHEN S5=>NEXT_STA TE<=S6;WHEN S6=>NEXT_STA TE<=S0;END CASE;END PROCESS P2;P3:PROCESS(CLR,PRESENT_STATE)BEGINIF CLR='1' THENQ<="000";ELSECASE PRESENT_STATE ISWHEN S0=>Q<="000";WHEN S1=>Q<="001";WHEN S2=>Q<="010";WHEN S3=>Q<="011";WHEN S4=>Q<="100";WHEN S5=>Q<="101";WHEN S6=>Q<="110";END CASE;END IF;END PROCESS P3;END A;6.LED灯控制--设计一个循环彩灯控制器--该控制器控制红,绿,黄三个发光二极管循环发亮--要求红发光管亮2秒,绿亮3秒,黄亮1秒。

硬件描述语言语言设计实例1、8-3编码器module encode_verilog ( a ,b );input [7:0] a ; //编码器输入wire [7:0] a ;output [2:0] b ; //编码器输出reg [2:0] b;always @ ( a )begincase ( a ) //编码器某一输入端口为高电平输出相应的3位二进制数8'b0000_0001 : b<=3'b000; //08'b0000_0010 : b<=3'b001; //18'b0000_0100 : b<=3'b010; //28'b0000_1000 : b<=3'b011; //38'b0001_0000 : b<=3'b100; //48'b0010_0000 : b<=3'b101; //58'b0100_0000 : b<=3'b110; //68'b1000_0000 : b<=3'b111; //7default : b<= 3'b000; //其他情况编码器输出3’b000endcaseendendmodule2、8-3优先编码器module p_encode_verilog ( A ,I ,GS ,EO ,EI ); //编码器以低为有效input [7:0] I ; //编码器输入wire [7:0] I ;input EI ; //输入使能,EI=0时,编码器正常工作wire EI ;output [2:0] A ; //编码器输出reg [2:0] A ;output GS ; //优先编码器工作状态标志,编码器的八个输入端有信号输入时,GS=0 reg GS ;output EO ; //输出使能,reg EO ;always @ ( I or EI )if ( EI ) //使用if、else if表明条件的优先级顺序beginA <= 3'b111;GS <= 1;EO <= 1;endelse if ( I[7] == 0 )beginA <= 3'b000;GS <= 0;EO <= 1;endelse if ( I[6] == 0 )beginA <= 3'b001;GS <= 0;EO <= 1;endelse if ( I[5] == 0 )beginA <= 3'b010;GS <= 0;EO <= 1;endelse if ( I[4] == 0 )beginA <= 3'b011;GS <= 0;EO <= 1;endelse if ( I[3] == 0 )beginA <= 3'b100;GS <= 0;EO <= 1;endelse if ( I[2] == 0 )beginA <= 3'b101;GS <= 0;EO <= 1;endelse if ( I[1] == 0 )beginA <= 3'b110;GS <= 0;EO <= 1;endelse if ( I[0] == 0 )beginA <= 3'b111;GS <= 0;EO <= 1;endelse if ( I == 8'b11111111)beginA <= 3'b111;GS <= 1;EO <= 0;endendmodule3、3-8译码器module decoder_verilog ( G1 ,Y ,G2 ,A ,G3 ); input G1 ; //使能输入,高有效wire G1 ;input G2 ; //使能输入,低有效wire G2 ;input [2:0] A ; //3位译码器输入,为高有效wire [2:0] A ;input G3 ; //使能输入wire G3 ; //使能输入,低有效output [7:0] Y ; //8位译码器输出,为低有效reg [7:0] Y ;reg s;always @ ( A ,G1, G2, G3)begins <= G2 | G3 ;if ( G1 == 0) //G1为低有效Y <= 8'b1111_1111;else if ( s)Y <= 8'b1111_1111;elsecase ( A )3'b000 : Y<= 8'b1111_1110;3'b001 : Y<= 8'b1111_1101;3'b010 : Y<= 8'b1111_1011;3'b011 : Y<= 8'b1111_0111;3'b100 : Y<= 8'b1110_1111;3'b101 : Y<= 8'b1101_1111;3'b110 : Y<= 8'b1011_1111;3'b111 : Y<= 8'b0111_1111;endcaseendendmodule4、数据选择器module mux8_1_verilog ( Y ,A ,D0, D1,D2, D3, D4, D5, D6, D7 ,G );input [2:0] A ; //地址输入端wire [2:0] A ;input D0 ; //数据输入端input D1 ; //数据输入端input D2 ; //数据输入端input D3 ; //数据输入端input D4 ; //数据输入端input D5 ; //数据输入端input D6 ; //数据输入端input D7 ; //数据输入端input G ; //使能端,当G=1时Y=0,当G=0时数据选择器正常工作wire G ;output Y ; //数据输出端reg Y ;always @(G or A or D0 or D1 or D2 or D3or D4 or D5 or D6 or D7 )beginif (G == 1) //使能端的优先级高Y <= 0;elsecase (A ) //根据输入的地址A确定数据选择器输出哪路输入数据3'b000 : Y = D0 ;3'b001 : Y = D1 ;3'b010 : Y = D2 ;3'b011 : Y = D3 ;3'b100 : Y = D4 ;3'b101 : Y = D5;3'b110 : Y = D6 ;3'b111 : Y = D7 ;default : Y = 0;endcaseendendmodule5、多位数值比较器module compare_verilog ( Y ,A ,B );input [3:0] A ; //4位二进制数Awire [3:0] A ;input [3:0] B ; //4位二进制数Bwire [3:0] B ;output [2:0] Y ; //A与B大小的比较结果reg [2:0] Y ;always @ ( A or B )beginif ( A > B )Y <= 3'b001; //A > B时Y输出3'b001 else if ( A == B)Y <= 3'b010; //A = B时Y输出3'b010 elseY <= 3'b100; //A < B时Y输出3'b100 endendmodule6、全加器module sum_verilog ( A ,Co ,B ,S ,Ci );input A ; //输入加数Awire A ;input B ; //输入加数Bwire B ;input Ci ; //相邻低位的进位输入信号wire Ci ;output Co ; //向相邻高位的进位输出信号reg Co ;output S ; //相加和数输出reg S ;always @ ( A or B or Ci)beginif ( A== 0 && B == 0 && Ci == 0 )beginS <= 0;Co <= 0;endelse if ( A== 1 && B == 0 && Ci == 0 )beginS <= 1;Co <= 0;endelse if ( A== 0 && B == 1 && Ci == 0 )beginS <= 1;Co <= 0;endelse if ( A==1 && B == 1 && Ci == 0 )beginS <= 0;Co <= 1;endelse if ( A== 0 && B == 0 && Ci == 1 )beginS <= 1;Co <= 0;endelse if ( A== 1 && B == 0 && Ci == 1 )beginS <= 0;Co <= 1;endelse if ( A== 0 && B == 1 && Ci == 1 )beginS <= 0;Co <= 1;endelsebeginS <= 1;Co <= 1;endendendmodule7、D触发器module Dflipflop ( Q ,CLK ,RESET ,SET ,D ,Qn );input CLK ; //D触发器输入时钟wire CLK ;input RESET ; //D触发器清零输入wire RESET ;input SET ; //D触发器预置数输入wire SET ;input D ; //D触发器输入wire D ;output Q ; //D触发器输出reg Q ;output Qn ;wire Qn ;assign Qn = ~Q ; //将D触发器输出取反always @ ( posedge CLK or negedge SET or negedge RESET ) beginif ( !RESET) //RESET下降沿将D触发器输出清零Q <= 0 ;else if ( ! SET) //SER下降沿将D触发器输出置1 Q <= 1;else Q <= D; //CLK上升沿D触发器输出等于输入endendmodule8、寄存器module reg8 ( clr ,clk ,DOUT ,D );input clr ; //异步清零信号,高有效wire clr ;input clk ; //时钟输入wire clk ;input [7:0] D ; //寄存器数据输入wire [7:0] D ;output [7:0] DOUT ; //寄存器数据输出reg [7:0] DOUT ;always @ ( posedge clk or posedge clr)beginif ( clr == 1'b1)DOUT <= 0;else DOUT <= D ;endendmodule9、双向移位寄存器module shiftdata ( left_right ,load ,clr ,clk ,DIN ,DOUT );input left_right ; // 左移右移控制信号wire left_right ;input load ; //异步置数信号,有效时将DIN输入wire load ;input clr ; //异步清零信号,高有效wire clr ;input clk ; //时钟输入wire clk ;input [3:0] DIN ; //并行输入wire [3:0] DIN ;output [3:0] DOUT ; //并行输出wire [3:0] DOUT ; // DOUT是一个wire型变量,不能在always块中被赋值reg [3:0] data_r; //所以定义一个寄存器型变量data_r作为中间变量assign DOUT = data_r ;always @ ( posedge clk or posedge clror posedge load )beginif ( clr == 1) //异步清零data_r <= 0;else if (load ) //异步置数data_r <= DIN;else beginif ( left_right) //left_right=1,信号左移begindata_r <= (data_r<<1);data_r[0] <= 0; //移出位补0endelse begin //left_right=0,信号右移data_r <= (data_r>>1);data_r[3] <= 0; //移出位补0endendendendmodule10、4位二进制加减法计数器module counter4 ( load ,clr ,c ,DOUT ,clk, up_down ,DIN);input load ; //异步预置数input clk; //输入时钟wire load ;input clr ; //异步清零wire clr ;input up_down ; //加减计数,up_dpwn=1加计数,up_down=0减计数wire up_down ;input [3:0] DIN ; //预置数输入wire [3:0] DIN ;output c ; //进位/借位输出,可以用于计数器的级联reg c ;output [3:0] DOUT ; //计数输出wire [3:0] DOUT ;reg [3:0] data_r;assign DOUT = data_r;always @ ( posedge clk or posedge clror posedge load)beginif ( clr == 1) //异步清零data_r <= 0;else if ( load == 1) //异步预置data_r <= DIN;else begin if ( up_down ==1) //加计数beginif ( data_r == 4'b1111) begindata_r <= 4'b0000;c = 1;endelse begindata_r <= data_r +1;c = 0 ;endendelse //减计数beginif ( data_r == 4'b0000) begindata_r <= 4'b1111;c = 1;endelse begindata_r <= data_r -1;c = 0 ;endendendendendmodule11、十进制加减法计数器module counter10 ( load ,clr ,c ,DOUT ,clk,up_down ,DIN ,seven_seg);input load ; //异步预置数input clk; //输入时钟wire load ;input clr ; //异步清零wire clr ;input up_down ; //加减计数,up_dpwn=1加计数,up_down=0减计数wire up_down ;input [3:0] DIN ; //预置数输入wire [3:0] DIN ;output c ; //进位/借位输出,可以用于计数器的级联reg c ;output [3:0] DOUT ; //计数输出output [7:0] seven_seg; //7段数码管wire [3:0] DOUT ;reg [3:0] data_r;assign DOUT = data_r;always @ ( posedge clk or posedge clror posedge load)beginif ( clr == 1) //异步清零data_r <= 0;else if ( load == 1) //异步预置data_r <= DIN;else if ( up_down ==1 & data_r == 9) //加进位beginc = 1;data_r <= 4'b0000;endelse if ( up_down ==0 & data_r == 0) //减借位beginc = 1;data_r <= 9;endelsebeginif (up_down ==1) begin //加计数data_r <= data_r +1;c = 0 ;endelse begin //减计数data_r <= data_r -1 ;c = 0 ;endendend/************数码管***************/assign seven_seg =Y_r;reg [7:0] Y_r;always @(data_r ) //用7段数码管显示计数输出beginY_r =8'b11111111;case (data_r )4'b0000: Y_r = 8'b00000011; //显示04'b0001: Y_r = 8'b10011111; //显示14'b0010: Y_r = 8'b00100101; //显示24'b0011: Y_r = 8'b00001101; //显示34'b0100: Y_r = 8'b10011001; //显示44'b0101: Y_r = 8'b01001001; //显示54'b0110: Y_r = 8'b01000001; //显示64'b0111: Y_r = 8'b00011111; //显示74'b1000: Y_r = 8'b00000001; //显示84'b1001: Y_r = 8'b00001001; //显示9default: Y_r = 8'b11111111; //默认数码管不发光endcaseendendmodule12、顺序脉冲发生器module pulsegen ( Q ,clr ,clk);input clr ; //异步预置数wire clr ;input clk ; //时钟输入wire clk ;output [7:0] Q ;//顺序脉冲输出wire [7:0] Q ;reg [7:0] temp ;reg x;assign Q =temp;always @ ( posedge clk or posedge clr )beginif ( clr==1)begintemp <= 8'b00000001; //temp寄存预定的序列x= 0 ;endelsebeginx<= temp[7] ; //序列最高位输出temp <= temp<<1 ; //temp左移一位temp[0] <=x; //将输出的结果赋给序列最低位,实现序列的循环输出endendendmodule13、序列信号发生器module xlgen ( Q ,clk ,res);input clk ; //时钟输入wire clk ;input res ; //异步预置数wire res ;output Q ; //序列信号输出reg Q ;reg [7:0] Q_r ;always @( posedge clk or posedge res)beginif (res ==1)beginQ <= 1'b0;Q_r <= 8'b11100100 ;//Q_r寄存预定的序列endelsebeginQ <= Q_r[7]; //序列最高位输出Q_r <= Q_r<<1; //Q_r左移一位Q_r[0] <=Q; //将输出的结果赋给序列最低位,实现序列的循环输出endend endmodule14、分频器module clockdiv ( Q ,rst ,sysclk ,sel );input rst ; //系统复位wire rst ;input sysclk ; //系统时钟输入wire sysclk ;input [1:0] sel ; //分频倍数选择wire [1:0] sel ;output Q ; //分频器输出wire Q ;reg [2:0] q;reg [31:0] cnt ;reg clk ;//时钟分频模块always @( posedge sysclk or negedge rst)beginif ( !rst ) begincnt <= 0 ;clk <= 1'b1 ;endelse begincnt <= cnt + 1'b1 ;if (cnt >= 32'd2500000 ) begin /clk时钟周期是系统时钟周期的5000000倍clk <= ~clk;cnt <= 0 ;endendend//分频器模块always @ ( posedge clk or negedge rst )if ( !rst ) q[0] <= 0;else q[0] <= ~q[0] ; // q[0]是clk的2分频always @ ( posedge q[0] or negedge rst )if ( !rst ) q[1] <= 0;else q[1] <= ~q[1] ; // q[1]是clk的4分频always @ ( posedge q[1] or negedge rst )if ( !rst ) q[2] <= 0;else q[2] <= ~q[2] ; // q[2]是clk的8分频assign Q = (sel== 2'd0) ? clk : //分频器输出clk(sel== 2'd1) ? q[0] : //分频器输出clk的二分频(sel== 2'd2) ? q[1] : //分频器输出clk的四分频(sel== 2'd3) ? q[2] : 0; //分频器输出clk的八分频endmodule。