The core clock system on the next generation Itanium microprocessor

- 格式:pdf

- 大小:521.57 KB

- 文档页数:9

开机自检时出现咨询题后会出现各种各样的英文短句,短句中包含了特不重要的信息,读明白这些信息能够自己解决一些小咨询题,然而这些英文难倒了一局部朋友,下面是一些常见的BIOS短句的解释,大伙儿能够参考一下。

〔1〕.CMOSbatteryfailed中文:CMOS电池失效。

解释:这讲明CMOS电池差不多快没电了,只要更换新的电池即可。

〔2〕.CacheMemoryBad,DoNotenableCache解决方法:主板高速缓存损坏导致,寻售后解决〔3〕.CMOSchecksumerror-Defaultsloaded中文:CMOS执行全部检查时发现错误,要载进系统预设值。

解释:一般来讲出现这句话根基上讲电池快没电了,能够先换个电池试试,要是咨询题依旧没有解决,那么讲明CMOSRAM可能有咨询题,要是没过一年就到经销商处换一块主板,过了一年就让经销商送回生产厂家修一下吧!〔4〕.CMOSChecksumErrordefaultsloaded解决方法:也有可能是电池没有电所致,然而更换后还出现那个咨询题,有可能是CMOS数据错误或主板电容咨询题,寻售后〔5〕.解决方法:Boot.ini文件中的代码被更改,能够将下面的代码保持到c:\boot.ini 中[bootloader]-timeout=10/default=multi(0)disk(0)rdisk(0)partition(1)\WINDOWS[operatingsystems]multi(0)disk(0)rdisk(0)partition(1)\WINDOWS="MicrosoftWindowsXPPro fessional"/NOEXECUTE=OPTIN/FASTDETECT〔6〕.PressESCtoskipmemorytest中文:正在进行内存检查,可按ESC键跃过。

解释:这是因为在CMOS内没有设定跃过存储器的第二、三、四次测试,开机就会执行四次内存测试,因此你也能够按ESC键结束内存检查,只是每次都要如此太苦恼了,你能够进进COMS设置后选择BIOSFEATURSSETUP,将其中的QuickPowerOnSelfTest设为Enabled,储存后重新启动即可。

2023届辽宁省锦州市渤海大学附属高级中学高三第六次模拟考试英语试题学校:___________姓名:___________班级:___________考号:___________一、阅读理解Stuck at home with nothing to watch? Curious about China, but don’t know where to begin? Well, we’ve got you covered with this brand-new video series exploring Chinese culture. All you have to do is press play.● Dazu Rock CarvingsOne of China’s UNESCO World Heritage sites is hidden among the mountains on the outskirts of the southwestern city of Chongqing. Here, tens of thousands of sculptures collectively make up the Dazu Rock Carvings — considered one of the finest examples of China’s cave art, exhibiting the most sophisticated craftsmanship of Dazu Rock Carvings. The delicate Dazu Rock Carvings tell ancient, mystical stories.● Bamboo CarvingThe art of bamboo carving originated at the Qing imperial court. Today, the art lives on, appreciated for its historical value and elegance.Just 100 kilometers southwest of Beijing, in the Xiong’an New Area, a group of skilled artists are keeping this art alive. Carving bamboo requires focus, precision and elbow grease (重活). Watch the video and feast your eyes on the bamboo masterpieces.● Peach-stone CarvingIn the small town of Siyang in Jiangsu Province in eastern China, craftsmen create art on the tiny cores of the peaches.While most people think nothing of peach stones and just throw them away, they are a source of inspiration for these artists. The artist goes to great length to find the perfect core to fit his concept. Using tiny tools, they chip away at the cores to create intricate designs,Chinese people in the near future.4.Why does the author quote Leung Long-kong in Paragraph 2?A.To call on Chinese women to wear qipao in everyday life.B.To introduce the development of qipao in China.C.To emphasize the importance of qipao in China nowadays.D.To show that qipao is no longer as popular as it was.5.Which of the following best describes Mary Yu?A.Creative.B.Conservative.C.Cautious.D.Considerate 6.What does the underlined word “evolving” in Paragraph 7 refer to?A.passing B.withdrawing C.developing D.following 7.What can we infer from the passage about qipao?A.Qipao is an iconic sign in the fashion industry.B.Qipao is on its way back to the daily life of Chinese.C.Qipao enjoys a good reputation in the world.D.Qipao is seen as a symbol of wealth in modern China.What’s more important in determining life success-book smarts or street smarts? This question gets at the heart of an important debate contrasting the relative importance of cognitive(认知的)intelligence (CI) and emotional intelligence (EI).Cognitive intelligence is still recognized as an important element of success, particularly when it comes to academic achievements. People with high cognitive intelligence typically do well in school, often earn more money, and tend to be healthier in general.But today experts recognize that cognitive intelligence is not the only determining factor of life success. Instead, it is part of a complex range of influences-one that includes emotional intelligence. Many companies now provide emotional intelligence training and use emotional intelligence tests as part of the hiring process. Research has found that individuals with strong leadership potential also tend to be more emotionally intelligent, suggesting that high emotional intelligence is an important equality for business leaders and managers. According to a survey of hiring managers, almost 75% of the responders suggested that they valued an employee’s emotional intelligence more than his cognitive intelligence.Now that emotional intelligence is so important, can it be taught or strengthened? According to one meta-analysis that looked at the results of social and emotional learningprogrammes, the answer to that question is definitely yes. Strategies for teaching emotional intelligence include character education, modeling positive behaviours, encouraging people to think about how others are feeling, and finding ways to be more empathetic(感同身受的)towards others.All in all, life success is a result of many factors. Both cognitive intelligence and emotional intelligence play roles in overall success, as well as health, wellness, and happiness. Rather than focusing on which factors have a prior influence, the greatest benefit may lie in learning to improve skills in multiple areas. In addition to strengthening cognitive abilities, such as memory and mental focus, you can also acquire and improve social and emotional skills.8.What can we know about people with book smarts?A.They can debate with other people.B.They can deal with various situations.C.They can be outstanding in academic research.D.They can be good at gaining real life experience.9.Why does the author mention the data in Paragraph 3?A.To indicate the strictness of the hiring process.B.To prove the importance of emotional intelligence.C.To explain the result of emotional intelligence tests.D.To show the influence of cognitive intelligence on success.10.What can be learned concerning emotional intelligence?A.Evaluating how others feel.B.One’s extreme behavioursC.One’s academic performance.D.Controlling others’ emotions. 11.Which of the following is a suitable title for the text?A.Does book smarts matter?B.Is CI or El more important?C.What counts most in life?D.Mental health or physical health?New research suggests that a gene that governs the body’s biological (circadian) clock acts differently in males versus females and may protect females from heart disease. The study is the first to analyse circadian blood pressure rhythms(节奏)in female mice.The body’s circadian clock-the biological clock that organizes bodily activities over a 24-hour period—contributes to normal variations in blood pressure and heart function overthe course of the day. In most healthy humans, blood pressure dips(下降)at night. People who do not experience this temporary drop, called “non-dippers”, are more likely to develop heart disease. The circadian clock is made up of four main proteins (encoded by “clock genes”) that regulate close to half of all genes in the body, including those important for blood pressure regulation.Previous research has shown that male mice that are missing one of the four clock genes (PER1) become non-dippers and have a higher risk for heart and kidney disease. A research team studied the circadian response and blood pressure of female mice that lack PERI and compared them with a healthy female control group. On both low-and high-salt diets, both groups “kept an apparent circadian rhythm” of blood pressure, the researchers explained. Unlike the male mice in previous research, the females without PERI showed normal dips in blood pressure overnight.These results suggest that the lack of PER1 acts differently in males and females. The findings are consistent with research showing that women are less likely to be non-dippers than men of the same age. “This study represents an important step in understanding sex differences in the regulation of cardiovascular(心血管的)function by the circadian clock,” the researchers wrote.12.What does the new research find?A.Biological clock may protect males from heart disease.B.Biological blood pressure rhythms in female mice act normally.C.Biological clock organizes bodily activities over a 24-hour period.D.A gene controlling biological clock works differently between sexes.13.What role can circadian clock play according to the text?A.Helping males cure heart disease.B.Helping blood pressure vary normally.C.Contributing to abnormal variations in blood pressure.D.Making up four main proteins regulating almost half of all genes.14.The lack of PRRI ______A.has the same impact on males and femalesB.makes no difference to malesC.does harm to male’s healthD.is more likely to affect female’s health15.What would be a suitable title for the text? A.One clock gene is importantB.Women may benefit from body clock C.New study analyses blood pressure rhythms D.Blood pressure of healthy humans dips at night二、七选五E.Most universities are considered to perform better in at least one academic field.F.Therefore, research each university and its course guide in as much detail as possible.G.One of the biggest deciding factors in choosing a university is where you want to study.三、完形填空27.A.target B.turn C.block D.appointment 28.A.happens B.remains C.offers D.works 29.A.celebrating B.communicating C.arguing D.competing 30.A.encourage B.help C.defeat D.please 31.A.college B.destination C.business D.competition 32.A.next to B.behind C.around D.ahead of 33.A.beautiful B.grateful C.careful D.successful 34.A.advantage B.competitor C.position D.challenge 35.A.Live B.Drive C.Run D.Ride五、其他应用文46.你校将举办英语演讲比赛。

Airlines, trading floors and technology companies are braced for chaos today as world timekeepers prepare to add a leap secondto global clocks.世界钟表今天要给全球的钟表加一“闰秒”,因此航班、交易所、科技公司正在为即将到来的混乱备战。

Immediately before midnight, dials will read 11:59:60 as clocks hold their breath for a second to allow the Earth's rotationto catch up with atomic time.为了使地球自转和原子时间吻合,午夜的前一刻,时钟将会凝滞一秒,表盘将会因此显示出11:59:60。

When the last leap second was added in 2012, Mozilla, Reddit, Foursquare, Yelp, LinkedIn, and StumbleUpon all reported crashesand there were problems with the Linux operating system and programs written in Java. In Australia, more than 400 flights weregrounded as the Qantas check-in system crashed.上一次添加闰秒是在2012年,当时Mozilla, Reddit, Foursquare, Yelp, LinkedIn和StumbleUpon 都有故障报告,Linux操作系统和Java编程也出现了问题。

澳洲航空的安检系统崩溃导致澳大利亚超过400架航班取消。

湖南大学硕士学位论文拟南芥中与蓝光受体CRY2相互作用蛋白的生化分析姓名:***申请学位级别:硕士专业:分析化学指导教师:***20091101硕上学位论文摘要隐花色素CRY2(cryptochrome2)是植物感受蓝光的光受体之一,它介导了蓝光调节植物的光形态建成反应,如抑制下胚轴的伸长、调节昼夜节律、激活基因转录和调节开花等。

Cashmore等人1993年就确定CRY2是植物的蓝光受体,但是直到现在,在蓝光受体CRY2信号传导方面的研究一直没有重大突破;因此,首先有必要通过各种分子生物学与遗传学的方法找到与蓝光受体CRY2相互作用的蛋白,为进一步研究CRY2介导的信号传导途径奠定基础。

本研究首先构建了酵母双杂交载体pBridge—CRY2,然后以pBridge·CRY2作为Bait对构建在Prey载体PACTl中的酵母双杂交文库进行了筛选。

通过筛选酵母双杂交文库发现蓝光下CRY2可能与多种蛋白发生相互作用。

其中包括生物钟核心振荡器组分蛋白LHY与CCAl,翻译起始因子EIF4E,磷酸酶AT3G51370,以及激酶CKA2和CKI。

本课题重点对CRY与生物钟相关蛋白的相互作用进行了深入研究。

通过RT-PCR克隆了CKA2,£日】,,CCAl基因,并成功构建了pGADT7.CKA2,pGADT7.LHY,pGADT7.CCAl载体。

我们通过营养缺陷型培养试验,滤纸显色反应和液相显色反应检测了在蓝光和黑暗条件下pBridge.CRY2与pGADT7.CKA2,pGADT7.LHY,pGADT7.CCAl在酵母体内的相互作用。

结果发现:CRY2蛋白在蓝光条件下与CKA2有较强的相互作用,而与LHY,CCAl的相互作用较弱,而且CRY2与CKA2,LHY,CCAl的相互作用强度与蓝光光强呈正相关;而在黑暗条件下CRY2与所检测蛋白均无相互作用。

成功构建了pColdTF.CKA2,pColdTF.LHY,pColdTF.CCAl原核表达载体,并采用大肠杆菌BL21表达得到了可溶的重组蛋白。

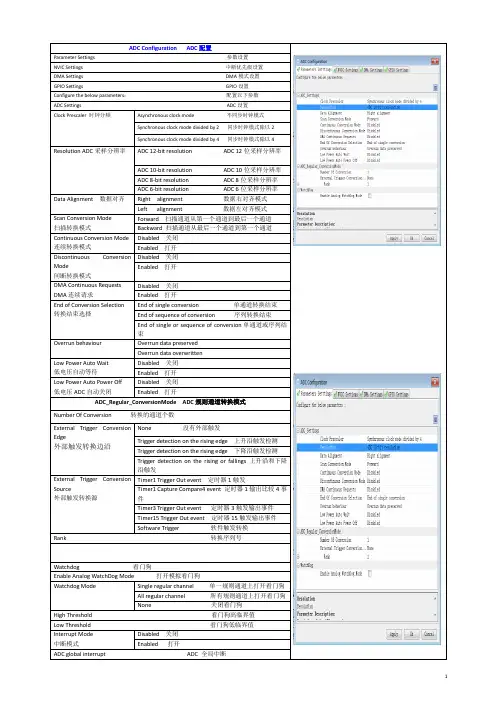

ADC Configuration ADC配置Parameter Settings 参数设置NVIC Settings 中断优先级设置DMA Settings DMA模式设置GPIO Settings GPIO设置Configure the below parameters:配置以下参数ADC Settings ADC设置Clock Prescaler 时钟分频Asynchronous clock mode 不同步时钟模式Synchronous clock mode divided by 2 同步时钟模式除以2Synchronous clock mode divided by 4 同步时钟模式除以4 Resolution ADC采样分辨率ADC 12-bit resolution ADC 12位采样分辨率ADC 10-bit resolution ADC 10位采样分辨率ADC 8-bit resolution ADC 8位采样分辨率ADC 6-bit resolution ADC 6位采样分辨率Data Alignment 数据对齐Right alignment 数据右对齐模式Left alignment 数据左对齐模式Scan Conversion Mode 扫描转换模式Forward 扫描通道从第一个通道到最后一个通道Backward 扫描通道从最后一个通道到第一个通道Continuous Conversion Mode 连续转换模式Disabled 关闭Enabled 打开Discontinuous Conversion Mode间断转换模式Disabled 关闭Enabled 打开DMA Continuous Requests DMA连续请求Disabled 关闭Enabled 打开End of Conversion Selection 转换结束选择End of single conversion 单通道转换结束End of sequence of conversion 序列转换结束End of single or sequence of conversion单通道或序列结束Overrun behaviour Overrun data preservedOverrun data overwrittenLow Power Auto Wait 低电压自动等待Disabled 关闭Enabled 打开Low Power Auto Power Off 低电压ADC自动关闭Disabled 关闭Enabled 打开ADC_Regular_ConversionMode ADC规则通道转换模式Number Of Conversion 转换的通道个数External Trigger Conversion Edge外部触发转换边沿None 没有外部触发Trigger detection on the rising edge 上升沿触发检测Trigger detection on the rising edge 下降沿触发检测Trigger detection on the rising or fallings 上升沿和下降沿触发External Trigger Conversion Source外部触发转换源Timer1 Trigger Out event 定时器1触发Timer1 Capture Compare4 event 定时器1输出比较4事件Timer3 Trigger Out event 定时器3触发输出事件Timer15 Trigger Out event 定时器15触发输出事件Software Trigger 软件触发转换Rank 转换序列号Watchdog 看门狗Enable Analog WatchDog Mode 打开模拟看门狗Watchdog Mode Single regular channel 单一规则通道上打开看门狗All regular channel 所有规则通道上打开看门狗None 关闭看门狗High Threshold 看门狗高临界值Low Threshold 看门狗低临界值Interrupt Mode 中断模式Disabled 关闭Enabled 打开ADC global interrupt ADC 全局中断TIM1 Configuration TIM1 配置Prescaler 时钟分频数Counter Mode 计数模式UP 向上计数Down 向下计数Center Aligned mode1 中间对齐模式1 Center Aligned mode2 中间对齐模式2 Center Aligned mode3 中间对齐模式3Counter Period 计数周期Internal Clock Division (CKD) 内部时钟分割No Division 内部时钟不分频Division by 2 时钟除以2 Division by 4 时钟除以4Repetition Counter 重复计数Slave Mode Controller 从模式控制器Slave mode disable 关闭从模式Trigger Output(TRGO) Parameters 触发输出参数设置Master/Slave Mode 主从模式Disable(no sync between this TIM(Master)and its slaves) Enable(sync between this TIM(Master)and its slaves)Trigger Event Selection 触发事件选择Reset(UG bit from TIMx_EGR)复位Enable(CNT_EN) 使能从定时器Update Event 更新事件Compare Pulse(OC1) 比较脉冲Output Compare(OC1REF) 输出比较1 Output Compare (OC2REF) 输出比较2 Output Compare (OC3REF) 输出比较3 Output Compare (OC4REF) 输出比较4Break and dead time management 刹车死区时间管理BRK State 刹车状态Disable 关闭Enable 打开BRK Polarity 刹车极性High 高电平Low 低电平Automatic Output State 自动输出状态Disabled 关闭Enabled 打开Off State Selection for Run Mode (OSSR) Disabled 关闭Enabled 打开Off State Selection for Idle Mode (OSSI) Disabled 关闭Enabled 打开Lock Configuration 定时器锁定配置Off 关闭Lock Level 1 锁定1 Lock Level 2 锁定2 Lock Level 3 锁定3Output compare no output channel 2 输出比较输出通道2N Mode 模式Frozen(used for Timing base) 冻结Active Level on match 匹配输出高电平Inactive Level on match 匹配输出低电平Toggle Level on match 匹配翻转电平Forced Active 强制输出高电平Forced Inactive 强制输出低电平Pulse (16 bits value) 脉冲宽度(16位)CH Polarity输出通道极性High 高Low 低CH Idle State输出通道闲置状态Set 置高Reset 复位低Output compare channel 3 输出比较通道3Mode 模式Frozen(used for Timing base) 冻结Active Level on match 匹配输出高电平Inactive Level on match 匹配输出低电平Toggle on match 匹配翻转电平Forced Active 强制输出高电平Forced Inactive 强制输出低电平Pulse (16 bits value) 脉冲宽度(16位)CH Polarity输出通道极性High 高Low 低CH Idle State输出通道闲置状态Set 置高Reset 复位低USART1 Configuration 串口1 配置Baud Rate 波特率Word Length 数据长度8bits(including parity)8位(包含校验位)9bits(including parity)9位(包含校验位)Parity 检验位None 没有校验Even 偶校验Odd 奇校验Stop Bits 停止位1 1个停止位2 2个停止位Advanced Parameters 高级参数设置Data Direction 数据传输方向Receive and Transmit 接收和发送Receive Only 仅接收Transmit Only 仅发送Over Sampling 过采样16 Samples 采样16次8 Samples 采样8次Single Sample Disable 关闭Enable 打开Advanced Features 高级特性Auto Baudrate 自动波特率Disabled 关闭Enabled 打开TX Pin Active Level Is Inverted Disabled 关闭Enabled 打开RX Pin Active Level Is Inverted Disabled 关闭Enabled 打开Data Are Inverted Disabled 关闭Enabled 打开TX and RX Pins Are Swapped 发送和接收引脚交换Disabled 关闭Enabled 打开Overrun Disable 关闭数据覆盖Disabled 关闭Enabled 打开DMA Disable on RX Error RX脚错误关闭DMA Disabled 关闭Enabled 打开MSB Is Sent First 最高位先发送Disabled 关闭Enabled 打开SPI1 Configuration SPI1 配置Frame Format 帧格式MotorolaData Size传输数据大小4 Bits 4位5 Bits 5位6 Bits 6位7 Bits 7位8 Bits 8位9 Bits 9位10 Bits 10位11 Bits 11位Clock Parameters(时钟参数)Prescaler (for Baud Rate) 分频(针对波特率)2 2分频4 4分频8 8分频16 16分频Baud Rate 波特率Clock Polarity (CPOL) 数据采样时时钟极性Low 低High 高Clock Phase (CPHA) 数据采样时时钟相位1 Edge 第一个边沿2 Edge 第二个边沿Advanced Parameters 高级参数设置CRC Calculation CRC 计算Disabled 关闭Enabled 打开I2C1 Configuration I2C1 配置I2C Speed Mode Standard Mode 标准模式Fast Mode 快速模式Fast Mode Plus 快速模式+ I2C Speed Frequency (KHz) I2C速度Rise Time (ns) 上升时间Fall Time (ns) 下降时间Coefficient of Digital FilterAnalog Filter 模拟滤波器Disabled 关闭Enabled 打开Slave features 从模式特性Clock No Stretch Mode 时钟没有扩展模式Clock Stretch Disabled 关闭时钟扩展Clock Stretch Enabled 打开时钟扩展General Call Address Detection通用呼叫检测Disabled 关闭Enabled 打开Primary Address Length selection原始地址长度检测7-bit 7位10-bit 10位Primary slave address 原始从地址Dual Address Acknowledged 双地址确认Disabled 关闭Enabled 打开IWDG Configuration 独立看门狗设置IWDG counter clock prescaler 独立看门狗计数时钟分频器4 8 16 32 64 128 256IWDG window value 独立看门狗值IWDG down-counter reload value 独立看门狗向下重装载值Pin Configuration GPIO口配置GPIO Mode GPIO模式analog mode 模拟输入端口No pull-up and no pull-down 既不上拉也不下拉Alternate Function Open Drain 复用开漏输出Alternate Function Push Pull 复用推挽Maximum output speed 最大输出速度Low 低Medium 中High 高。

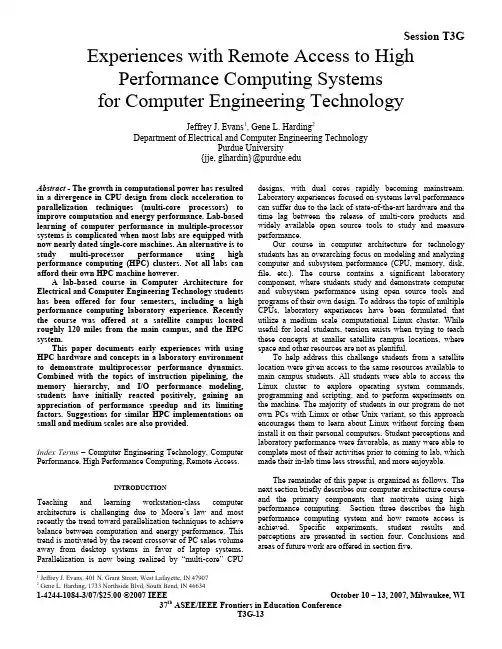

Experiences with Remote Access to HighPerformance Computing Systems for Computer Engineering TechnologyJeffrey J. Evans 1, Gene L. Harding 2Department of Electrical and Computer Engineering TechnologyPurdue University {jje, glhardin}@1 Jeffrey J. Evans, 401 N. Grant Street, West Lafayette, IN 47907 2Gene L. Harding, 1733 Northside Blvd, South Bend, IN 46634Abstract - The growth in computational power has resultedin a divergence in CPU design from clock acceleration to parallelization techniques (multi-core processors) to improve computation and energy performance. Lab-based learning of computer performance in multiple-processor systems is complicated when most labs are equipped with now nearly dated single-core machines. An alternative is tostudy multi-processor performance using high performance computing (HPC) clusters. Not all labs can afford their own HPC machine however.A lab-based course in Computer Architecture for Electrical and Computer Engineering Technology studentshas been offered for four semesters, including a high performance computing laboratory experience. Recently the course was offered at a satellite campus located roughly 120 miles from the main campus, and the HPC system.This paper documents early experiences with using HPC hardware and concepts in a laboratory environmentto demonstrate multiprocessor performance dynamics. Combined with the topics of instruction pipelining, the memory hierarchy, and I/O performance modeling, students have initially reacted positively, gaining an appreciation of performance speedup and its limiting factors. Suggestions for similar HPC implementations on small and medium scales are also provided.Index Terms – Computer Engineering Technology, Computer Performance, High Performance Computing, Remote Access.INTRODUCTION Teaching and learning workstation-class computer architecture is challenging due to Moore’s law and most recently the trend toward parallelization techniques to achieve balance between computation and energy performance. This trend is motivated by the recent crossover of PC sales volume away from desktop systems in favor of laptop systems. Parallelization is now being realized by “multi-core” CPU designs, with dual cores rapidly becoming mainstream. Laboratory experiences focused on systems level performance can suffer due to the lack of state-of-the-art hardware and the time lag between the release of multi-core products and widely available open source tools to study and measure performance.Our course in computer architecture for technology students has an overarching focus on modeling and analyzing computer and subsystem performance (CPU, memory, disk,file, etc.). The course contains a significant laboratory component, where students study and demonstrate computerand subsystem performance using open source tools and programs of their own design. To address the topic of multiple CPUs, laboratory experiences have been formulated that utilize a medium scale computational Linux cluster. While useful for local students, tension exists when trying to teachthese concepts at smaller satellite campus locations, where space and other resources are not as plentiful.To help address this challenge students from a satellite location were given access to the same resources available to main campus students. All students were able to access the Linux cluster to explore operating system commands, programming and scripting, and to perform experiments on the machine. The majority of students in our program do not own PCs with Linux or other Unix variant, so this approachencourages them to learn about Linux without forcing them install it on their personal computers. Student perceptions and laboratory performance were favorable, as many were able to complete most of their activities prior to coming to lab, whichmade their in-lab time less stressful, and more enjoyable.The remainder of this paper is organized as follows. Thenext section briefly describes our computer architecture courseand the primary components that motivate using high performance computing. Section three describes the high performance computing system and how remote access is achieved. Specific experiments, student results and perceptions are presented in section four. Conclusions and areas of future work are offered in section five.C OURSED ESCRIPTIONECET 325, Computer Architecture, Modeling, and Performance Analysis, a junior level course, has been offered in the spring and fall semesters at the main campus since the spring of 2005. The course is an elective for students in the electrical engineering technology (EET) program, and required for students enrolled in the computer engineering technology (CpET) option of the EET program. ECET 325 is a four credit-hour course, with three hours per week devoted to lecture and two hours per week in the laboratory.The course’s primary objective is to motivate students to appreciate the probabilistic nature in which computers operate, and how certain probabilistic tendencies of programs can be taken advantage of in hardware subsystems. The pedagogical approach is illustrated in figure 1. The course begins with the development of how the user (the student) interacts with the machine. This concept is formalized with lectures on probability, random variables, and stochastic processes. In particular, the Poisson arrival process is presented in the context of user input, namely mouse clicks and keyboard input. The exponential service time probability distribution is applied in the context of network access time (the time spent waiting for a web page to materialize). Laboratory exercises reinforce these concepts by having a student “browse” the web while a partner documents mouse click and wait timing.FIGURE1P EDAGOGICAL A PPROACHEach major teaching module attempts to reinforce probabilistic concepts that are developed in the first weeks of the semester. Other modules focus on CPU instructions and pipelining, the memory hierarchy, operating system support, and systems modeling using queuing theory. Another module addresses general computer performance, focusing on Amdahl’s Law, where execution time after some improvement is a function of two things: the amount of time a program spends performing operations affected by the improvement, and the amount of time spent performing operations not affected by it.Students enrolled in ECET 325 spend two-hours each week in the laboratory, under the supervision of the instructor. Lab experiences focus on analyzing system and subsystem performance. This is accomplished by exposing students to software tools that are part of the Linux operating system such as sar, vmstat, and iostat, and similar freeware tools for the Microsoft Windows environment. Students are also expected to create and augment their own tools outside the lab for measuring the performance of basic integer, floating point, and double precision math operations. Moreover, they use these skills to measure and analyze the performance of various sorting algorithms, exposing them to introductory algorithm analysis.R EMOTE A CCESS TO HPC R ESOURCESStudents are granted access to a 128-node computational Linux cluster, part of the author’s Adaptive Computing Systems Laboratory (ACSL) [1]. Figure 2 shows one half of the system including all interconnection network elements (top left). In figure 2, four 16-node cluster segments (a group of nodes physically connected to the same network switch), are shown. Two 16-node cluster segments (32 compute nodes) are located in a separate laboratory and the last pair of 16-node segments is located in a basement storage area. The ACSL cluster consists of Pentium III class 933Mhz machines, each equipped with 512MB of RAM and 40GB of disk storage. A similar machine is used for logging into the system and system control. This machine has 250GB of disk storage. Another machine with 250GB of disk storage is used for data backup purposes.FIGURE 2ACSL C OMPUTATIONAL C LUSTER (64 OF 128N ODES) Students are sent an email during the third week of the semester giving them their user name and initial password. Instructions are provided in the way of a URL that takes them to a comprehensive set of instructions on how to change their password, setup their secure shell (ssh) environment and key, and test their ability to access the protected compute nodes.Remote access to the machine serves a number of objectives. First, students can login to the system and exploreLinux operating system commands, C program development, and scripting at their convenience. The system is generally available on a 24/7 basis. Second, students are exposed to the area of high performance computing (HPC) by way of laboratory experiences where they learn to submit instructor provided parallel programs to the machine, then analyze and visualize (plot) results using techniques previously learned. The HPC experiments are used to re-illustrate and re-emphasize Amdahl’s law, demonstrating those parts of a program that can experience speedup and those that cannot. Students are given a simple parallel program using the Message-Passing Interface (MPI) for interprocess(or) communication [2]. Students focus individually on submitting, running, and evaluating the run time of the program using different numbers of compute nodes. This is different from other approaches to teaching HPC concepts, which have traditionally focused more on the details of parallel programming [3], [4] and architectures [5].In the fall of 2006, ECET 325 was delivered for the first time at a satellite (remote) campus located in South Bend, 120 miles from the main campus. A local faculty member taught the course at South Bend, where the student demographics and lab setup was different. Since this campus has both traditional and non-traditional students (i.e., not immediately out of high school), the course offerings are in the evenings. Moreover, the lab time was three hours instead of two, and the labs were generally also available during the day. Since it was the first time ECET 325 was offered at South Bend, both faculty and students experienced the “growing pains” of a new course offering, and the extra lab time proved useful.Students at the remote location were given the same access to the machine as those at the main (local) campus, using identical means for getting them started. Approximately 85 percent of both local and remote students correctly followed the provided instructions, resulting in “clean” setups. In cases where students struggled, it was generally because they either overlooked some detail(s) in the instructions, or executed the steps out of order. In one case a local student ultimately needed to delete his private ~/.ssh directory and start over; he had resorted to “experimenting” with an assortment of steps and execution orders that he could not remember or repeat.E XPERIMENTS AND S TUDENT P ERCEPTIONSI. ExperimentsThe first few offerings of ECET 325 required students to install two operating systems on an “experimental” machine that would remain theirs in the lab for the duration of the semester. This practice was curtailed at the main campus, in favor of spending the time acquainting them with basic command line operations in Windows and Linux. (Because of limited staffing resources, however, the former approach was adopted at the remote campus.) More recently, student interest has grown to where the instructor has provided the information and means for students to install Linux on their personal computers.Beginning in the fourth week and continuing for the duration of the semester students are assigned laboratory experiences that either encourage the use of or directly exploit the cluster system in some way. Several labs require developing simple software tools to measure CPU performance of basic mathematical operations. Students were required to make their programs portable between Windows, Linux, and Sun Solaris (local students only) operating system environments. Program requirements and the range of portability demands careful consideration of programming language and compilation tools. To accommodate this, students were encouraged to download free ‘C’ compilation tools and use them in a command line environment, which is what they experience when accessing the HPC system.Over time the students add complexity to their tools while also making them easier to use. For example, their initial programs are primarily coded to execute a fixed number of times, compute average execution time, and send output to the screen only. Upgrades include writing their output to a file, then upgrading again to accept command line arguments to specify the output file and number of iterations. Students are required to create help, or usage instructions when command line arguments are improperly entered or omitted. The point of this requirement is to encourage the development of reusable components and to motivate students to develop habits that allow them to “forget” the details of their program by creating useful ways of reminding themselves of program operation. For example, if a well-formed usage page is presented when one omits required command line arguments it becomes straightforward to remind oneself how a program is supposed to function, particularly after it has not been used for an extended period of time. This practice has resulted in students gaining a significant appreciation of the complexities of creating detailed and meaningful command line interfaces and help systems, which helps them in later courses where graphical user interfaces are developed.One of the teaching modules in ECET 325 focuses on developing Amdahl’s law, which quantifies the relationship of program execution time improvement to the portion of the system that is changed, such as a specific hardware improvement. Amdahl’s law quantifies the relationship in terms of aspects of a program that can be improved between those that cannot. The resulting improvement in a program’s execution time can be stated as an overall “speedup” byS=1(1−f)+fa,(1)where S is the speedup, f is the fraction of a program that is improved or enhanced, and a is the amount of the improvement expressed as a number that would be a ratio to one (i.e., a = 10 for a ten times improvement to that portion of the system). Speedup then is also a ratio, and heavily related to execution time, but not expressed as time. This abstractionsometimes confuses students who are accustomed to reporting differences in time using units of time.This concept is easily extended to address sections of a program that can only be executed serially compared to those that can be performed in parallel byS=1s+pn, (2)where s is the portion of the program that can only be performed serially, p is the portion that can be performed in parallel, and n is the number of processors.Near the end of the semester students are given a compiled parallel program and example scripts that they modify in order to execute the parallel program on the HPC machine. Each student runs several iterations of the parallel program on a geometric progression of machines (e.g. 1, 2, 4, … 32). This activity is to take place outside of the organized lab meeting. In the lab run time results are then statistically analyzed and plotted. Since the HPC cluster is a Linux based system students are required to visualize their results using GnuPlot [6]. This is initially met with some resistance; however once they realize the similarities between GnuPlot and more familiar programs such as MatLab, they become more curious. There is also the added motivation of waiving the final laboratory report once their data source and output files have been successfully demonstrated in the lab.II. Student Results and PerceptionsThe educational intent of granting 24/7 accessibility to a HPC cluster is twofold. First, students can work with a Linux system without being required to install the operating system on their home computer. Second, they can gain an appreciation of Amdahl’s law by investigating multiprocessor performance improvement using programs written for parallel execution. Moreover, Amdahl’s law is a critical component of a major learning objective and assessment point for the course, namely “Upon completion of this course each student should be able to demonstrate the ability to identify and performance analyze the CPU component of a computer”, and our assessment threshold is 70 percent.Local students benefit since the HPC machine is close by, and the majority of students living on campus implies a high level of network reliability as provided by the University. Remote students however do not have a HPC machine at their location, and since the student population is more non-traditional (commuter), overall network reliability was a concern. Fortunately the course population at both locations is manageable (roughly 16 per class), and the South Bend campus had very little trouble with remote access. The only significant network problem was caused by a change in a host campus (Indiana University-South Bend) router, and the professor was able to reprogram the local hub, with phone help from the local network administrator, within about a half hour. This event did, however, highlight the importance of having an on-call administrator.As previously mentioned, a two-week HPC lab exercise occurs at the end of the semester reaffirming Amdahl’s law, which is taught earlier in the semester. Student performance of this lab, performance for all labs, the learning objective, and the overall course performance were analyzed. Students located at the main campus scored incrementally lower on the lab than in previous semesters. Surprisingly, nearly half of the class failed to complete all the procedures in order to avoid preparing a final lab report, whereas the remainder of the class not only completed the work, but also gained all available extra credit. The lab score exhibited a definitive bi-modal distribution as the report scores were centered around a value well below the other group.Because of the “first time” challenges involved with executing the lab at the remote campus, the faculty member there was very generous with the lab grading. Most of the students were very diligent about completing the work, and a few made almost heroic efforts on occasion to accomplish the labs. Thus, the lab grades are higher than they will likely be the next time this course is offered. This likewise means the course total is probably three or four points higher than it would otherwise be. On the other hand, the exams, which comprise 50% of the course grade, did not benefit from such generosity in the grading. The learning objective evaluation is based on the final exam grade, and is more consistent with the corresponding evaluation at the main campus. Moreover, it was encouraging to observe that, for this specific objective, the average for questions on the final exam was more than eight points higher than the average for the three mid-course exams. Apparently, the student’s grasp of those concepts did improve during the course.Table 1 shows the variables comparing local (main campus) and remote student performance. It is worth noting that the learning objective figure reflects a combination of knowledge and analysis skills including the determination of cycles per instruction for a program and instruction pipeline performance in addition to applying Amdahl’s law.TABLE IS TUDENT P ERFORMANCE (F ALL 2006)Item Avg, Score (Local) Avg. Score (Remote) Lab 10 - ClustersLab TotalCourse TotalLearning Objective89.276.472.567.995.795.585.371.6The local student learning objective performance was slightly below the desired threshold of 70 percent, and the remote students were just slightly above it. While disappointing, lab performance was encouraging. Those students who successfully completed their work, avoiding the final report, took advantage of using the HPC machine during evenings and weekends. This practice has the advantage of the student obtaining full or nearly full use of the machine. As the remaining students learned, delaying their effort had the ramification of creating longer job queues (student jobswaiting to be executed), thus delaying their output sometimes for hours.C ONCLUSIONS AND F UTURE W ORKThe use of high performance computing (HPC) clusters has been implemented in a junior level computer architecture course for electrical and computer engineering technology students. The use of our Linux HPC cluster serves several purposes and allows students access to Linux based machines without forcing them to install it on their own personal computers. While student performance results were mixed, there were clear indications that the HPC concepts experienced in the lab contributed in positive ways in developing the desired outcome for the assessed learning objective. Moreover, students who were initially reluctant to interact with different machines and operating systems became comfortable with them by the end of the semester.One of the valuable lessons learned related to the need for clear, precise, and timely account setup and lab instructions. Lecture and lab instruction can become out of phase with each other. The courses themselves (local vs. remote) can also become out of phase due to calendar schedule (semester start, end, holidays, etc.). Another reality that cannot be avoided however is that in nearly all cases there are several “correct” methods of obtaining “correct” results, and correct results are not necessarily identical from group to group. To help address this, a web page was developed and improved to provide more accurate details for student account setup and verification. This allows the initial email sent to students to be shorter and less complex. By providing this level of detail on the web page, a student that follows the instructions given is guaranteed that the results are correct and repeatable. A second web page was also developed to encourage students to test remote access to help avoid problems later.The HPC cluster used in our course was constructed using recycled machines. Most institutions implement programs to “rotate” campus computers for labs, etc., and those that are designated “past” their useful life can be useful for this purpose. It uses an open source operating system (Linux), and relies on open source systems and resource management software. There are other, more portable system software options also available that transform any local area network of computers, regardless of operating system into a cluster by simply booting a CD on each machine. A remote access scenario for student learning of HPC concepts was chosen to (1) relieve the remote site instructor of the responsibility of obtaining and maintaining such a machine, and (2) to determine if there were any major obstacles to student learning using remote access.The use of HPC concepts and systems to teach Amdahl’s law has yielded encouraging initial results. Future plans include gradually elevating the sophistication and complexity of the HPC lab experiences by expanding student work so each uses up to 64 nodes (1/2 of the system). In doing so it is envisioned that more sophisticated programs will be used and analyzed. All of these will also come from the open source community.A CKNOWLEDGMENTThe authors wish to thank the Rosen Center of Advanced Computing (RCAC) at Purdue University for their donation of compute nodes, racks, and cabling, enabling us to create our HPC machine for our students. The authors also thank the reviewers for their insightful suggestions to improve the quality of this paper.R EFERENCES[1]Adaptive Computing Systems Laboratory (ACSL), http://m1236-/acsl/. On-line document, 2007.[2]Gropp W., Lusk E., and Skjellum A., Using MPI: parallel programmingwith the message-passing interface, 2nd Edition. MIT Press, 1999.[3]Emilio Luque E., Suppi R., and Sorribes J., A auantitative approach forteaching parallel computing. Proceedings of the twenty-third SIGCSEtechnical symposium on Computer science education, 1992, p 286-298 [4]Prins P. R., Teaching parallel computing using Beowulf clusters: alaboratory approach. Journal of Computing in Small Colleges, 2004, vol 20, no 2, p 55-61.[5]Miller R., Schaller N., The right stuff? Teaching parallel computing.Proceedings from the Eighth International Parallel ProcessingSymposium, 1994, p 956-961.[6]. On-line document. 2007.。

生物钟对小鼠昼夜眼压节律性的影响肖凡;钟笑;吴国福;严璐【摘要】Objective To investigate the influence of the circadian clock genes on 24-hour intraocular pressure (IOP) rhythm. Methods C57BL/6J mice were randomly divided into 6 groups (group1,3 and 5,wild-type;group2,4 and 6,Cry-deficient [Cry1-/-Cry2-/-]). IOP was measured at eight time points daily (circadian time [CT] 0,3,6,9,12,15,18,and 21 hours),During the IOP measurements,mice in groups 1 and 2 were maintained in a 12-hour light-dark cycle (LD),mice in groups 3 and 4 were kept in a constant darkness(DD) that started 48 hours before the measurements,mice in groups5 and 6 were kept in a constant lightness (LL) that started 48 hours before the measurements. Analyze the changes of the IOP rhythm. Results In wild-type mice living in LD conditions,pressures measured in the light phase were significantly lower than those in the dark phase. This daily rhythm was maintained under DD and LL conditions. In contrast,Cry-deficient mice did not show significant circadian changes in IOP,regard-less of environmental light conditions. Conclusion Clock oscillatory mechanisms require the activity of clock genes,and it’s im-portant for the generation of a circadian rhythm of IOP.%目的:研究生物钟对小鼠昼夜眼压的影响。

生物钟基因简要概述昼夜节律是自然界最普遍的一种自然现象, 它的存在使生物体的生理、生化、行为等生命现象表现为以24 h 为周期的振荡。

昼夜节律发生的物质基础是分子计时器, 即昼夜节律生物钟(circadian clock) 。

它由一组特异的核心元件组成, 包括Clock、Bmal1、Pers 、Crys、Tim 等基因及其相关蛋白产物[1]。

生物节律的基本分子机制, 是这些核心元件构成的转录- 翻译负反馈环。

这个机制本质上是内源性的, 但同时会受环境信号, 尤其是光信号的导引。

哺乳动物的主生物钟被定位在下丘脑视交叉上核( suprachiasmatic nuclei, SCN) ,当它受到异常刺激后, 机体的昼夜节律可发生改变, 严重时会导致疾病。

但到目前为止, 维持生物钟运行的确切分子调控过程还不清楚。

人类下丘脑视交叉上部具有特化的神经核团,即SCN,是生命活动的时序控制器,它们通过神经递质内分泌和体液途径影响周围器官和组织,控制和调节着睡眠和觉醒、代谢、内分泌、细胞增殖分裂和凋亡, 以及免疫等各个层面, 使生命活动在时序上协调有序。

[2]而操控这些生命活动有序性进行的正是Clock基因、Bmal1基因、Crys基因等一系列生物钟基因。

其中Clock基因是惟一的, 也是最早用正向遗传法鉴定出的。

它是动物近日节律(circadianrhythm) 的必要调控者, 在节律时钟的组织中起着中心作用。

[3]Clock基因的结构1994年美国西北大学Takahashi教授领导的研究小组发现, 单个的碱基突变可导致小鼠的生物钟节律丧失, 他们将这个半显性突变定位于第5号染色体的Clock基因上[4]1997年5月Cell杂志报道了美国西北大学的Takahashi研究小组成功克隆了小鼠的生物钟基因。

1999年4月Genonics杂志报道了美国西北大学的Takahashi研究小组对人类Clock基因(hCk)的克隆结果。

RESEARCH ARTICLECoupling-induced synchronization in multicellular circadian oscillators of mammalsYing Li •Zengrong Liu •Jinhuo Luo •Hui WuReceived:2July 2012/Revised:13August 2012/Accepted:21August 2012/Published online:21September 2012ÓSpringer Science+Business Media B.V.2012Abstract In mammals,circadian rhythms are controlled by the neurons located in the suprachiasmatic nucleus (SCN)of the hypothalamus.Each neuron in the SCN contains an autonomous molecular clock.The fundamental question is how the individual cellular oscillators,expressing a wide range of periods,interact and assemble to achieve phase synchronization.Most of the studies carried out so far emphasize the crucial role of the periodicity imposed by the light-dark cycle in neuronal synchronization.However,in natural conditions,the interaction between the SCN neurons is non-negligible and coupling between cells in the SCN is achieved partly by neurotransmitters.In this paper,we use a model of nonidentical,globally coupled cellular clocks considered as Goodwin oscillators.We mainly study the synchronization induced by coupling from an analytical way.Our results show that the role of the coupling is to enhance the synchronization to the external forcing.The conclusion of this paper can help us better understand the mechanism of circadian rhythm.Keywords Circadian rhythm ÁClock ÁSynchronization ÁSelf-sustained oscillatorIntroductionMany organisms have endogenous circadian clocks that coordinate physiological and behavioral rhythms and syn-chronize the organisms to daily environmental cycles.In mammals,the circadian rhythms are controlled by a pace-maker located in the suprachiasmatic nucleus (SCN)of the hypothalamus (Reppert and Weaver 2002;Moore et al.2002).The SCN is composed of 20,000neurons arranged in a symmetric bilateral structure,including astrocytes and multiple neuropeptidergic classes of neurons.It has been shown that isolated single neurons are able to produce cir-cadian oscillations,with periods ranging from 20to 28h (Welsh et al.1995;Honma et al.2004).Less well under-stood is how individual cells are assembled to create a whole tissue pacemaker that can govern behavioral and physio-logical rhythmicity.That is to say how these individual clocks achieve phase synchronization.The rhythmicity of the SCN is a product of multiple individual cellular circadian oscillators that are coupled together in a tissue network.The core molecular regulatory mechanism underlying these oscillations of circadian clocks (e.g.,Per1,Per2,Per3,Cry1,Cry2,Bmal1,Re-verba,Clock,Rora )relies on a transcription-translation negative-feedback loop in which the protein products of circadian genes regulate their own transcription (Reppert and Weaver 2001).Because free-running periods of iso-lated neurons are broadly distributed,the self-sustained oscillations indicate that a coupling mechanism is operat-ing among the neurons.The coupling between cells in the SCN is achieved partly by neurotransmitters which are released by each cell (Shirakawa et al.2001;Hastings and Herzog 2004).The multiple synchronized single-cell cir-cadian oscillators produce coordinated circadian outputs,which ultimately regulate overt rhythms.Y.Li (&)ÁJ.LuoCollege of Information Technology,Shanghai Ocean University,Shanghai 201306,China e-mail:leeliying@Z.LiuInstitute of Systems Biology,Shanghai University,Shanghai 200444,ChinaH.WuCollege of Science and Information,Qingdao Agricultural University,Qingdao 266109,Shandong,ChinaCogn Neurodyn (2013)7:59–65DOI 10.1007/s11571-012-9218-9Mathematical modeling can provide insights into potential mechanisms that lead to coordinated cellular oscillations(Benuskova and Kasabov2008;Jiao and Wang 2006;Liu et al.2010;Matsuura et al.2008;Wang et al. 2011a,b).So far there have been a large number of studies on the cellular oscillators’dynamics and synchronization which induce the circadian rhythm generated by the SCN (Aton et al.2005;Maywood et al.2006;Antle et al.2003, 2007;Bush and Siegelman2006;Rougemont and Naef 2006;Indic et al.2007;To et al.2007;Yamaguchi et al 2003;Liu and Reppert2000).Among the previous studies, research works are mainly on either the models of the SCN cellular oscillators or the synchronization of the oscillators. In particular,To and his collaborators presented a multi-cellular molecular model of the mammalian circadian clock,which postulates that synchrony arises among cir-cadian neurons because they release VIP rhythmically on a daily basis and in response to ambient light(To et al. 2007).However,their works are mainly based on numer-ical simulation with little theoretical analysis.In this paper, we aim to study analytically the synchronization of clocks coupled though neurotransmitter.Specifically,in this paper we develop a model of non-identical clocks coupled by neurotransmitter.Then we prove theoretically that the clocks can be synchronized by the neurotransmitter.At last we show the role of coupling in SCN from two aspects with the help of numerical simulation. On one hand,the coupling among neurons can synchronize circadian oscillators.On the other hand,considering envi-ronment cue of daily light-dark cycle,coupling can reduce the threshold of light strength for entrainment.The model of coupled circadian oscillatorsWe model the circadian clocks at the basic genetic level by using a large ensemble of globally coupled noniden-tical Goodwin oscillators.Each of the neurons,when uncoupled from the others,acts as an oscillator with an intrinsic period.A single cell or genetic oscillator model is described by a four-variable model based on the Goodwin oscillator(Goodwin1965).In this model,a clock gene mRNA(X)produces a clock protein(Y)which,in turn, actives a transcriptional inhibitor(Z).The latter inhibits the transcription of the clock gene,closing a negative feedback loop.In both parts of the SCN,the neuro-transmitter gammaaminobutyric acid(GABA)is released (Shirakawa et al.2001).How neurotransmitters interfere with the clock is not completely clear.We introduce a global coupling term depending on the concentration of a synchronizing factor(a neurotransmitter)in the extracel-lular medium,and assume fast dynamics of the small neurotransmitter molecules in the extracellular medium.We assume that cells synthesize a neuropeptide neuro-transmitter denoted by V which is induced by activation of the clock gene(X)(Gonze et al.2005).The strong candi-dates regarding the VL cells and DM cells are respectively VIP and AVP.Here we adopt the model of an individual cell as follows(Gonze et al.2005):_X¼v1K n1K n1þZ nÀv2X;_Y¼k3XÀv4Y;_Z¼k5YÀv6Z;_V¼k7XÀv8V8>>><>>>:ð1Þwhere v1,v2,v4,v6,v8,K1,k3,k5,k7and n are all parameters.The variable X represents mRNA concentration of a clock gene,per or cry;Y is the resulting protein,PER or CRY;Z is the active protein or the nuclear form of the protein(inhibitor);and V is the neurotransmitter.In this model,V can approximately be viewed as neurotransmit-ter’s production or its integrated effect although there are many steps in the life of a neuropeptide like VIP and AVP, such as mRNA’s production and its release process.In our previous work(Li et al.2006),we gave the sufficient conditions for Hopf bifurcation of Eq.(1),showing that the single neuron is a self-sustained oscillator.Although V is induced by the product of X,such a regulation is approx-imately expressed by the concentration of X in the last equation of this model for the purpose of simplification.For the complete model,we take N neuronal oscillators, each one of them described by four variablesðX i;Y i;Z i;V iÞ; i¼1;...;N,satisfying the above evolution equations.The global coupling dependents on the concentration of the synchronization factor(the neurotransmitter)in the extra-cellular medium.Under the fast transmission hypothesis, the extracellular concentration is assumed to equilibrate to the average cellular neurotransmitter concentration.This global variable is referred to as the meanfield,denoted by V,V¼1NX Ni¼1V i:Gonze et al.considered that the clock gene X i was directly activated by the meanfield V(Gonze et al.2005).This coupling mechanism is similar to the one suggested by Ullner et al.(2009).Under these conditions,the resulting model is_Xi¼v1K n1K n1þZ niÀv2X iþv cðKVÞ2K cþðKVÞ2;_Yi¼k3X iÀv4Y i;_Zi¼k5Y iÀv6Z i;_Vi¼k7X iÀv8V iÀgðV iÀQVÞ8>>><>>>:ð2ÞIn this case,the parameter Q describes the influx of external signaling molecule back into the cell(Jordi et al.2004).The fact that the SCN is a relative small and highly dense area with short distances between the cells allows us to simplify the cell-to-cell communication by mean-field coupling.g measures the rate of neurotransmitter V i in-and outflux extracellular medium.The coupling between the individual cell oscillators is determined by g ,Q ,v c and K .For the convenience of analysis in the next section,we rewrite Eq.(2)as follows._X i ¼v 1K n1K n 1þZ n i Àv 2X i þv c ðKV Þ2K c þðÞ2;_Y i ¼k 3X i Àv 4Y i ;_Z i ¼k 5Y i Àv 6Z i ;_V i ¼k 7X i Àv 8V i Àg ðV i ÀQV Þ;_V ¼k 7NP N i ¼1X i Àv 8V Àg ð1ÀQ ÞNV 8>>>>>>><>>>>>>>:ð3ÞResultsSynchronization of the circadian oscillatorsKatriel G.have proved the synchronization of oscillatorscoupled through an environment (Katriel 2008).According to the conclusion of (Katriel 2008),if Eq.(1)has a stable periodic solution,that is to say,the single neuron,placed in the environment,performs periodic oscillations,and the solution of the linear system of Eq.(3)decays to 0at an exponential rate as t !1,then a population of such neurons will synchronize.In the following,we analyze the convergency of the solution of the linear system of Eq.(3).We assume that the system Eq.(1)has a stable periodic solution X (t ),Y (t ),Z (t ),V (t ).To obtain the stability of this solution as a synchronized oscillation of Eq.(3),we need to show that any solution of the following periodic linear system_~X ¼Àv 1nK n 1~Z n À1ðK n 1þZ n Þ2Àv 2~X ;ð4Þ_~Y¼k 3~X Àv 4~Y ;ð5Þ_~Z¼k 5~Y Àv 6~Z ;ð6Þ_~V¼k 7~X Àðv 8þg Þ~V ð7Þdecays to 0at an exponential rate as t !1.Let ~Xðt Þ;~Y ðt Þ;~Z ðt Þ;~V ðt Þbe a solution of the system (4–7).Considering ~Xðt Þ;~Y ðt Þ;~Z ðt Þand ~V ðt Þare all concentrations,one has ~Xðt Þ!0;~Y ðt Þ!0;~Z ðt Þ!0and ~V ðt Þ!0for any t .From Eq.(4),we get that ~Xðt Þ ~X ð0Þe Àv 2t ð8Þso ~Xðt Þdecays exponentially.Rewriting (5),we have_~Yðt Þþv 4~Y ¼k 3~X :ð9ÞThen ~Yðt Þcan be written explicitly as ~Yðt Þ¼exp ÀZ t0v 4ds 0@1A ~Y ð0ÞþZ texp ÀZ tsv 4dr 0@1A k 3~Xðs Þds Therefore,using Eq.(8)we have j ~Yðt Þj e Àv 4t ~Y ð0Þþk 3e Àv 4t ~X ð0ÞZ te ðv 4Àv 2Þs ds¼e Àv 4t ~Yð0Þþk 3~Xð0Þv 4Àv 2ðe Àv 4t Àe Àv 2t Þwhich gives the exponential decay of ~Yðt Þ.That is to say there exist m y ,k y ,so that ~Yðt Þ m y e Àk y t :ð10ÞSimilarly,~Zðt Þand ~Vðt Þalso decays exponentially.Thus,according to the conclusion of (Katriel 2008),the oscillators can achieve synchronization with appropriateparameter values.The role of coupling in SCNIn this section,we will show the role of coupling in SCN from two aspects with the help of numerical simulation.The system of single neuron Eq.(1)has a stable periodic solution,just as Fig.1showing.The concentrations are expressed in nM,and the parameter values in the model are n =10,v 1=0.7nM/h,K 1=1nM,v 2=0.18nM/h,k 3=0.7nM/h,v 4=0.18nM/h,k 5=0.7nM/h,v 6=0.18nM/h,k 7=9nM/h and v 8=0.7nM/h.In the first place,the coupling can induce the synchro-nization of oscillators.We consider a small size of network with N =10neurons,though there are over thousands of neurons in the real SCNs.The concentrations are expressed in nM,and the parameter values in the model are n =10,v 1=0.7nM/h,K 1=1nM,v 2=0.18nM/h,k 3=0.7nM/h,v 4=0.18nM/h,k 5=0.7nM/h,v 6=0.18nM/h,k 7=9nM/h,and v 8=0.7nM/h.The mismatches are randomly distributed in ±2%around the above values.Figure 2gives the time evolution of mRNA (X i )of the uncoupled oscillators.The other variables such as Y i ,Z i and V i are similar with X i ,which are not shown here.It is obvious that the self-sustained oscillators of neurons have different periods.In this situation,the extracellular con-centration V is not periodic just as Fig.3showing.We alsofind that the system follows the same trajectories regardless of initial conditions(data are not shown).When the coupling strength is set appropriately,the oscillators achieve synchronization,as shown in Figs.4,5 and6which is not the complete synchronization but with a little difference between their amplitudes.In Figs.4,5and 6,the parameter values express the coupling among the clocks are K c=1,K=0.4,v c=0.04,Q=0.9,g=0.3. The period of the synchronized oscillators is longer than the single clocks.The initial values for each network neuron dose not affect the synchronization.From the mathematical viewpoint,complete synchronization can be reached only among identical oscillators.However,in our model the oscillators are nonidentical,which means that complete synchronization cannot be reached among these nonidentical oscillators and only the practical or phase synchronization can be expected,i.e.there are differences between their amplitudes.Besides intercellular coupling,in nature conditions,the circadian clock is subject to alternation of days and nights and in response to this cycling environment,phase-locks to the light-dark(LD)cycle,enabling the body to follow a24 h rhythm.which is assumed to act independently from the negative feedback loop and is added as independent terms in the transcription rate of X.Light is incorporated through a periodic time-dependent function L(t),which can be realized in various forms.Here we use a square waveLðtÞ¼L0t2½24k;24kþ12Þ;0t2½24kþ12;24ðkþ1ÞÞ:&and the signal oscillates between the values L(t)=0and L(t)=L0with a period24h.With the help of numerical simulation,wefind that inter-cellular coupling can reduce the threshold of light that makes the oscillators get phase synchronization with period of24h.Specially,Fig.7shows that the oscillators can not get synchronization when L0=0.7without coupling.Theseoscillators have different periods,which is consistent with the biologicalfindings that isolated individual neurons are able to produce circadian oscillations,with periods ranging from20 to28h(Welsh et al.1995;Honma et al.2004).Comparing with Figs.7,8shows that the oscillators can achieve phase synchronization when L0=0.7with coupling and the values of coupling parameters are just the same as in Figs.4,5and 6.These twofigures display that the intercellular coupling is necessary for the oscillators to be entrained with period24h. Conclusion and discussionCircadian rhythm mediated by SCN is an important phe-nomenon in mammals,and many theoretical and experimental works have been carried out to understand its mechanism. However,few works went further to study the synchronization mechanism in an analytical way.In this paper,we proposed a model for coupled neuronal oscillators by neurotransmitter. The model proposed here is a general model based on bio-logical evidences,according to which we demonstrated the role of neurotransmitter.Other models or network configu-rations probably may also give the similar results.From the theoretical analysis in this article,we obtained the conclusion that one major effect of coupling among the neurons in SCN is to increase their synchronizability.With the help of numerical simulation,we show the role of intercellular coupling in two aspects.On one hand,the coupling can make the oscillators get synchronization.On the other hand,the coupling makes it more easy for the oscillators to be entrained with period24h.The results and analytical framework proposed here may provide insight to better understand the mechanism of cir-cadian rhythm,and may also have implication for appli-cations,such as designing interventions to treat circadian disorder.Several aspects of the model are clearly oversimplifica-tions of the known architecture of the SCN.For example, Although there are different transmitters in different parts of the SCN,such as VIP in VL and AVP in DM,we use the same differential equation to describe their dynamical behavior because they are both released rhythmically(Hamada et al. 2001).Actually,there are two basic cell types in different SCN regions,intrinsically rhythmic pacemakers and damped oscillators(Antle et al.2003,2007).However we consider only one type of self-oscillating neurons in this article.As mentioned in(Komin et al.2011),the damped oscillators are more entrainable by the external forcing than the self-oscillating neurons with different periods.The results of this paper show that the coupling makes it more easy for the oscillators be entrained.The simplification may point to a underlying rule that the coupling among neurons perhaps probably makes the self-oscillating neurons dampedfirstly and then the damped oscillators are entrained more easily by LD cycle.Actually,the structure of SCN i.e.intercellular connec-tivity is another factor affecting circadian rhythm.There have been some numerical works to study the effects of circadian oscillator network structure on circadian behavior (Vasalou2009;Vasalou2011;Kori2012).In this article, we didn’t consider the structure of SCN.Under the fast transmission hypothesis,we simplify the cell-to-cell com-munication by mean-field coupling.In our later work,we will try to develop a multicellular SCN model based on the actual structure,in which the synchronization factor V may be a variational factor for different neuron in stead of the mean-field coupling for all neurons.Then the effects of SCN structure on circadian rhythm will be further studied theoretically.Acknowledgments This research is supported by the NNSF of China(Grant No:11102106and11172158).ReferencesAntle MC,Foley DK,Foley NC,Silver R(2003)Gates and oscillators:a network model of the brain clock.J Biol Rhythms 18(4):339–350Antle MC,Foley NC,Foley DK,Silver R(2007)Gates and oscillators II:zeitgebers and the network model of the brain clock.J Biol Rhythms22(1):14–25Aton S,Colwell C,Harmar A,Waschek J,Herzog E(2005) Vasoactive intestinal polypeptide mediates circadian rhythmicity and synchrony in mammalian clock neurons.Nat Neurosci 8:476–483Benuskova L,Kasabov N(2008)Modeling brain dynamics using computational neurogenetic approach.Cogn Neurodyn2(4): 319–334Bush W,Siegelman HT(2006)Circadian synchrony in networks of protein rhythm driven plexity12:67–72Gonze D,Bernard S,Waltermann C,Kramer A,Herzel H(2005) Spontaneous synchronization of coupled circadian oscillators.Biophys J89:120–129Goodwin B(1965)Oscillatory behavior in enzymatic control processes.Adv Enzyme Regul3:524–438Hamada T,LeSauter J,Venuti JM,Silver R(2001)Expression of Period genes:rhythmic and nonrhythmic compartments of the suprach-iasmatic nucleus pacemaker.J Neurosci21(19):7742–7750 Hastings M,Herzog E(2004)Clock genes,oscillators,and cellular networks in the suprachiasmatic nuclei.J Biol Rhythms19: 400–413Honma S,Nakamura W,Shirakawa T,Honma K(2004)Diversity in the circadian periods of single neurons of the rat suprachiasmatic nucleus on nuclear structure and intrinsic period.Neurosci Lett 358:173–176Indic P,Schwartz WJ,Herzog ED,Foley NC,Antle MC(2007) Modeling the behavior of coupled cellular circadian oscilla-tors in the suprachiasmatic nucleus.J Biol Rhythms22(3): 211–219Jiao XF,Wang RB(2006)Synchronization in neuronal population with the variable coupling strength in the presence of external stimulus.Appl Phys Lett88:203901Jordi GO,Michael BE,Steven HS(2004)Modeling a synthetic multicellular clock:repressilators coupled by quorum sensing.PNAS101(30):10955–10960Katriel G(2008)Synchronization of oscillators coupled through an environment.Phys D237:2933–2944Komin N,Murza AC,Hernandez-Garcia E,Toral R(2011) Synchronization and entrainment of coupled circadian oscilla-tors.Biol Phys1:167–176Kori H,Kawamura Y,Masuda N(2012)Structure of cell networks critically determines oscillation regularity.J Theor Biol297: 61–72Li Y,Zhang J,Liu Z(2006)Circadian oscillators and phase synchronization under a light-dark cycle.Int J Nonlinear Sci 1(3):131–138Liu C,Reppert SM(2000)GABA synchronizes clock cells within the suprachiasmatic circadian clock.Neuron25:123–128Liu Y,Wang RB,Zhang ZK,Jiao XF(2010)Analysis on stability of neural network in the presence of inhibitory neurons.Cogn Neurodyn4(1):61–68Matsuura H,Tateno K,Aou S(2008)Dynamical properties of the two-process model for sleep-wake cycles in infantile autism.Cogn Neurodyn2(3):221–228Maywood ES,Reddy AB,Wong GKY,ONeill JS,OBrien JA, McMahon DG,Harmar AJ,Okamura H,Hastings MH(2006) Synchronization and maintenance of timekeeping in suprachias-matic circadian clock cells by neuropeptidergic signaling.Curr Biol16:599–605Moore RY,Speh JC,Leak RK(2002)Suprachiasmatic nucleus organization.Cell Tissue Res309:89–98Reppert S,Weaver D(2001)Molecular analysis of mammalian circadian rhythms.Annu Rev Physiol63:647–676Reppert S,Weaver D(2002)Coordination of circadian timing in mammals.Nature418:935–941Rougemont J,Naef F(2006)Collective synchronization in popula-tions of globally coupled phase oscillators with drifting frequencies.Phys Rev E73:011104(5)Shirakawa T,Honma S,Katsuno Y,Oguchi H,Honma K(2001) Multiple oscillators in the suprachiasmatic nucleus.Chronobiol Int18:371–387To TL,Henson MA,Herzog ED,Doyle FJ III(2007)A molecular model for intercellular synchronization in the mammalian circadian clock.Biophys J92:3792–3803Ullner E,Buceta J,Dı´ez-Noguera A,Garcı´a-Ojalvo J(2009)Noise-Induced coherence in multicellular circadian clocks.Biophys J 96:3573–3581Vasalou C,Herzog ED,Henson MA(2009)Small-world network models of intercellular coupling predict enhanced synchroniza-tion in the suprachiasmatic nucleus.J Biol Rhythms24(3): 243–54Vasalou C,Henson MA(2011)A multicellular model for differential regulation of circadian signals in the core and shell regions of the suprachiasmatic nucleus.J Theor Biol7(288):44–56Wang RB,Zhang ZK,Qu JY,Cao JT(2011)Phase synchronization motion and neural coding in dynamic transmission of neural information.IEEE Trans Neural Netw22(7):1097–1106 Wang RB,Zhang ZK,Tseb CK,Qu JY,Cao JT(2011b)Neuralcoding in networks of multi-populations of neuraloscillators.Math Comput Simul doi:10.1016/j.matcom.2010.10.029Welsh DK,Logothetis DE,Meister M,Reppert SM(1995)Individual neurons dissociated from rat suprachiasmatic nucleus express independently phased circadianfiring rhythms.Neuron14: 697–706Yamaguchi S,Isejima H,Matsuo T,Okura R,Yagita K,Kobayashi M,Okamura H(2003)Synchronization of cellular clocks in the suprachiasmatic nucleus.Science302:1408–1412。