第四章 ISE 6.x 设计工具简介和使用

§4.1概述

本章将详细介绍Xilinx 公司新的高性能设计开发工具ISE(Integrated Software Environment),并以第六版本进行讲解和演示。Xilinx 根据不同的用户,分别提供四种不同功能的设计开发工具:ISE WebPACK,ISE Foundation,ISE BaseX和ISE Alliance。

(1) ISE WebPACK版:

该软件为全免费版,可通过Xilinx网站直接下载。支持包括XC95*/XC95*XL/XC95*XV、CoolRunner XPLA3、CoolRunner-II全系列 CPLD;以及Spartan-II/Spartan-IIE全系列FPGA;Spartan-3系列器件中的XC3S50、XC3S200、XC3S400;Virtex-E部分FPGA(V50E-V300E)器件;Virtex-II部分FPGA(2V40-2V250)器件;Virtex-II Pro部分FPGA(2VP2)器件。集成了XST(Xilinx Synthesis Technology)综合工具。但不支持Core Generator(核生成)工具和PACE(引脚和区域约束编辑器)。

(2) ISE Foundation版:

该软件为完全版。提供了设计开发工具的所有功能.支持Xilinx的全系列逻辑器件产品。并集成了XST(Xilinx Synthesis Technology)综合工具。支持Core Generator(核生成)工具和PACE(引脚和区域约束编辑器)。

(3) ISE BaseX版:

该软件为部分受限版。即支持XC95*/XC95*XL/XC95*XV全系列CPLD; CoolRunner XPLA3全系列CPLD;CoolRunner-II全系列 CPLD;以及Spartan-II/Spartan-IIE全系列FPGA;Spartan-3系列器件中的XC3S50、XC3S200、XC3S400;Virtex/Virtex-E部分FPGA(V50/V50E—V600/V600E)器件;Virtex-II部分FPGA(2V40--2V250)器件;Virtex-II Pro部分FPGA(2VP2、2VP4、2VP7)器件。其他功能与ISE Foundation相同。

(4) ISE Alliance版:

支持Xilinx的全系列逻辑器件产品。但不包含XST(Xilinx Synthesis Technology)综合工具。

此外,在Xilinx最新推出的集成软件环境(ISE)软件ISE 6.1i版和ChipScope Pro 6.1i 版中,可提供比最接近的竞争产品高30%的性能、高25%的逻辑利用率以及低50%的设计成本。并可帮助工程师快速容易地实现时序收敛,从而降低总体设计成本以及整个设计流程所花费的时间。新版本软件允许客户利用Xilinx的下一代增强千兆位 (MultiGigabit)串行I/O 收发器和对采用90nm(纳米)工艺技术的FPGA进行设计。集成了 XPower热能分析软件,能够方便地进行功耗统计和分析。

ISE 6.1i软件还提供了可加强现有可编程设计流程并可适应客户特有设计方法的设计

选项。一种名为高级引脚输出与区域约束编辑器(PACE)的管理工具来简化器件IO规范,包括交互式电压支持和差分对识别指南。ISE Floorplanner(ISE布局规划器)工具中所提供的增量设计、模块化设计、宏生成器和区块规划功能可使设计时间比传统设计方法缩短多达50%。这些都可大大缩短重新编译时间并提供基于小组(team-based)的设计性能优势。ChipScope Pro 6.1i实时验证软件与ISE项目浏览器的集成更为紧密,可更方便地选择和插入验证核心、定义信号监测点,同时为整体设计流程提供实时调试规划能力。新的虚拟

I/O(Virtual I/O)核心允许设计人员仿真DIP开关和按钮调节。集成总线分析仪(IBA)核心在集成有嵌入式PowerPC 405处理器的Virtex-II Pro FPGA器件上则可同时支持IBM CoreConnect处理器局部总线(PLB)和片上外设总线(OPB)。 ISE5还提供了新的结构化设计向导(Architecture Wizard)工具--数字时钟管理(DCM)向导和Rocket IO千兆位比特收发器(MGT)向导。它们允许用户通过ISE项目浏览器(Project Navigator)中的对话框以图形化的方式设置DCM和MGT功能。ISE然后将可编辑的源代码直接写入HDL源文件,以便设置和控制这些高级功能。设计向导还能指导用户进行HDL编码,减轻了学习配置复杂器件功能所需的所有编程属性的负担,从而加快了设计进程。另外一种新功能是宏创建器(Macro Builder)。设计师可以在ISE平面规划器中访问该功能,它允许用户将设计的任何一部分指定为一个内核,再利用此工具在时序和布局信息方面固化这个内核。生成这个内核可以被其他的设计者共享。从而减少重复工作。

在该版本软件中所提供的详细时序报告功能可方便确定高速路径,并提供了可编程设计中最全面的时序约束语言,而ISE时序分析器(Timing Analyzer)则提供了强大的假设分析(what-if)和过滤功能。这些都进一步简化了高速设计分析。丰富的在线帮助功能和每日一贴使用说明,更加方便了设计者的使用和操作。

第六版的ISE6.1 PC软件可在安装有Windows2000 SP2、Windows XP以上操作系统的环境中安全运行。同时,在安装软件过程中,需要关闭“防火墙”等抗病毒软件。

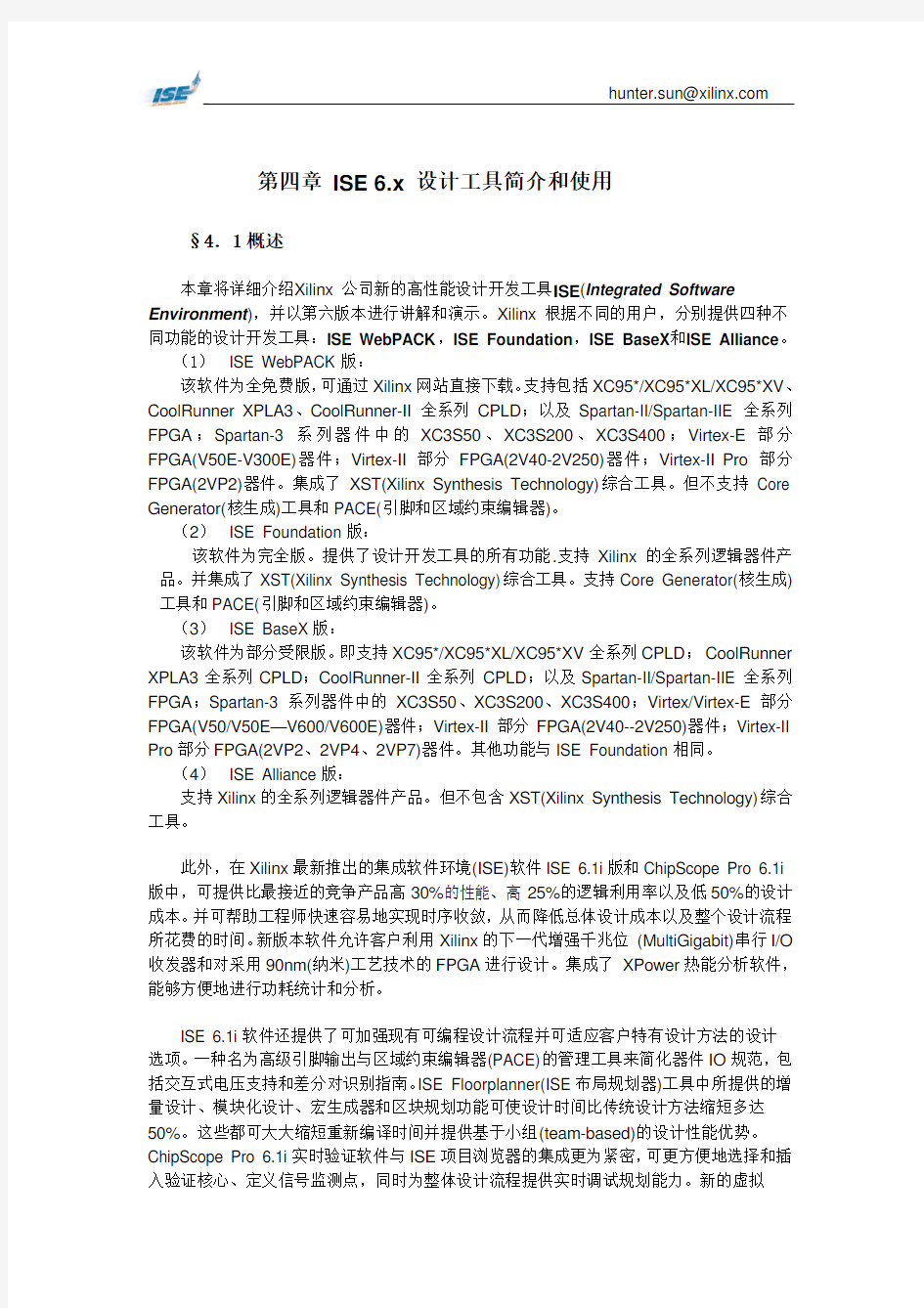

§4.2 Xilinx 设计流程

一个完整的CPLD/FPGA设计流程主要包括电路或模块的设计与输入、设计综合、功能仿真、设计实现、布局布线仿真、时序仿真和下载设计组成。如图4-1所示。

图4-1 Xilinx 设计流程

设计输入阶段:

(1) 设计规划和预算: 设计者规划系统的架构以及器件的选型。

(2) 多种设计输入方式:硬件描述语言(HDL)或原理图。也可利用结构化向到(Architecture Wizard))以及核生成器(Core Generator)可以辅助设计输入。

无论采用何种输入方法,都需要一个工具(综合工具)来生成EDIF网表文件以便对Xilinx的FPGA进行编程。适用的综合工具有:XST(Xilinx Synthesis Technology)、Synplify、Leonardo Spectrum、FPGA Compiler II。

(3)对设计进行仿真使你的设计按照预想的功能工作。

Xilinx的FPGA实现阶段:

一旦建立了网表文件,就可以来实现设计。在实现的过程中将会产生许多输出文件。流程报告、时序仿真网表、平面布局文件、FPGA编辑器文件等。实现包含很多步骤:(1) 转换:将多个设计文件合并为一个网表。

(2) 映射:将网表中的逻辑符号(门)整合到物理元件(CLB和IOB)中。

(3) 布局布线:将元件放到器件中,并将它们连接起来,同时提取出时序数据并生成各种报告。

调试及仿真:

在ISE6.1开发环境中,提供了第三方的仿真工具Modelsim接口。但需要安装ModelSim 或ModelSim XE(ModelSim Xilinx版)。并指定文件执行的路径。利用Edit → Preferences → Integrated Tools来设置调试及仿真工具的路径。在本示例中modelsim.exe执行文件在Modeltech_5.6e\win32中,如图4-2所示。

图4-2 设置文件执行的路径

如果设计者安装了XE(Xilinx)版的Modelsim工具可不用编译Xilinx库。但若安装的是其他版本的Modelsim工具,一定要编译Xilinx库,否则将不能进行仿真。

设计完成及下载:

一旦设计实现并完成后,必须建立一个CPLD/FPGA可以识别的文件。该文件称为位

流文件即BIT文件(FPGA),JTAG文件(CPLD)。这个BIT文件可以被直接下载到FPGA中,或者可以被转换为存储编程信息的PROM文件。

§4.3 ISE 6.1软件的使用

在该节中,主要是向ISE的初学者描述和演示,在XILINX的ISE集成软件环境中,如何用VHDL和原理图的方式进行设计输入;如何用ModelSim仿真工具对设计进行功能仿真和时序仿真;如何实现设计。通过这些设计流程,应该可以对ISE设计工具的使用有一个初步的认识。在这里采用Virtex-II器件作为设计的目标器件。

§4.3.1设计开始

(1) 软件要求:

为了完成本教程,你必须在你的PC机上安装以下软件:

ISE 6.1设计工具和ModelSim 5.6e或ModelSim5.7仿真工具。

软件安装完后,环境变量需作如下修改:

在Windows NT/2000中,通过选择 开始 → 设置 → 控制面板 → 系统 → 高级 →环境变量等选项来设置相应的环境变量。

ISE_PATH C;\XILINX\bin\nt

LM_LICENSE_FILE C:\Modeltech_5.6e\license.dat

MODEL_TECH C:\Modeltech_5.6e\win32

MODELSIM C:\Modeltech_5.6e\modelsim.ini

PATH C:\XILINX\bin\nt; C:\Modeltech_5.6e\win32;

(2) 运行ISE软件:

设计者需要完成的设计都在ISE设计工具的工程管理之下。也就是说,工程管理器(Project Navigator)贯穿ISE操作的始终。它管理并连接ISE所集成的所有设计工具。当软件包安装成功后,在计算机的桌面中,将出现工程管理器(Project Navigator)图标。双击它或选择开始→程序→ Xilnx ISE 6.x → Project Navigator来启动ISE软件。

(3) 使用在线帮助:

你可以在ISE运行过程中,随时获得在线帮助。当你按下F1键时,帮助系统就会显示出正在运行过程的在线帮助。比如说,当你在运行ECS(原理图输入)时按下F1键,那么关于如何使用ECS的在线帮助就会显示出来。

§4.3.2 设计输入(VHDL)

本节中,你将会利用VHDL语言模板来设计一个8位计数器模块。首先,创建一个

新的项目和生成一个计数器模块;然后,参照计数器VHDL语言模板来完成一个8位计数器的VHDL设计。

㈠创建一个新的项目:

按照以下步骤创建一个新项目。

■选择【File】→【New Project】。

■在【New Project】对话框中,分别输入新项目存放的路径,或者点击Project 旁的浏览按钮,选择你想存放新项目的路径;

■在【Project Name】下,键入【demo】。当你在Project Name下键入【demo 后,在Project Location下会自动创建一个【demo】的子目录。如图4-3所示。

图4-3 建立新的设计工程

■点击【Next】,你可以对每种属性进行选择。在下拉菜单列表中,点击并输入所需的属性值如下,如图4-4所示:

·器件系列(Device Family) :Spartan3

·器件(Device) :XC3S200

·器件封装(Package) :PQ208C

·器件速度等级(Speed Grade) :-4

·设计流程(Design Flow) :XST( VHDL/Verilog)

·仿真设计工具Simulator :ModelSim

图4-4 新项目对话框(New Project Dialog Box)

■点击【下一步Next】。

ISE将会在工程项导航器(Project Navigator)中创建和显示一个新的项目。

㈡ 创建一个计数器模块:

按照以下步骤创建一个8位计数器VHDL模块。

■选择【Project】→【New Source】;

■选择VHDL模块(VHDL Module)作为源程序类型,如图4-5所示;

图4-5 选择VHDL模块作为源程序类型

■在文件名中键入‘counter_demo’;

■点击【下一步Next】,编辑输入输出信号。

■点击【下一步Next】;

■点击【下一步Next】,将出现所设置新项目的信息,如图4-6所示。

图4-6 所建立的新项目信息示意图

■点击【Finish】。完成这个新源程序的模板。新源程序模板counter_demo.vhd 将会显示在HDL编辑窗口中,它包括计数器的Library,Use,Entity,Architecture 等语句的描述。见图4-7所示。

图4-7 counter_demo.vhd的HDL编辑窗口

㈢用计数器模板修改你的计数器模块:

要完成这个计数器模块,你将要用到ISE的语言模板(ISE Language Template)工具,选择其中的计数器VHDL描述来完成counter_demo.vhd的设计。

■选择【Edit】→【Language Templates】来打开语言设计模板,或者通过点击工具栏中最右端的灯泡按钮来打开语言模板;

■在语言模板(Language Templates)窗口中,通过点击“+”符号来展开VHDL下的综合模板(Synthesis Templates);如图4-8所示。

图4-8 计数器语言模板(Counter Language Template)

■从VHDL综合模板中选择计数器模板(Counter Template),并把它拖动或粘贴到源程序counter_demo.vhd的begin和end之间;

■关闭语言模板(Language Templates)窗口;

■将带有注释符号(--)的计数器端口定义的语句剪切并粘贴到计数器的实体(entity) 描述中去。计数器端口定义语句如下:

Port (

--CLK:in STD_LOGIC;

--RESET:in STD_LOGIC;

--CE,LOAD,DIR:in STD_LOGIC;

--DIN:in STD_LOGIC_VECTOR(7 downto 0);

--COUNT:inout STD LOGIC_VECTOR(7 downto 0)

);

■去掉counter_demo.vhd源程序中端口定义语句前的注释符号(--);

■去掉COUNT端口定义语句后的分号(;);

COUNT :inout STD_LOGIC_VECTOR(7 downto 0)

■选择【File】→【Save】,保存 counter_demo.vhd 源程序。

■此时,你的counter_demo.vhd源程序应与图4-9中的VHDL描述一样。

图4-9 修改后的计数器模块(Modified Counter Module)

㈣ 对设计进行综合:

在【Processes for Sources】窗口,双击Synthesize-XST,将运行综合工具,如图4-10所示。

图4-10 运行综合工具示意图

双击 View Synthesis Report,阅读综合流程生成的报告。从报告中可以看到在当前所选器件中的资源利用率、总的时序特性等,如图4-11所示。

图4-11 打开综合流程生成的报告示意图

§4.3.3 仿真行为模型(功能仿真)

在本小节中,你将会创建一个测试矢量(testbench)波形,用于定义计数器模块所应有的功能。这个testbench波形将被用于与Modelsim仿真器连接,用来验证该计数器是否达到设计要求的功能和时延需求。

㈠创建一个测试矢量(testbench) 波形源文件:

首先,在【Project Navigator】中创建一个testbench波形源文件,该文件将在HDL Bencher中进行修改。

■在工程项窗口(Project Window)的源文件中选中计数器(counter_demo.vhd)

■选择【Project】→【New Source】;

■在新的对话框中,选择新文件类型为Test Bench Waveform,如图4-12所示;

图4-12 选择波形仿真文件类型

■键入文件名为【counter_tbw】;

■点击【下一步Next】;

■点击【下一步Next】:

■点击【完成Finish】;

此时,HDL Bencher程序自动启动并等候你输入所需的时序需求。

你现在可以设定仿真所需的时间参数。时钟高电平时间和时钟低电平时间一起定义了设计操作必须达到的时钟周期,输入建立时间定义了输入在什么时候必须有效,输出有效延时定义了有效时钟沿到达后多久必须输出有效数据。

在本教程中,不需要改变任何默认的时间约束。默认的初始化时间设置如下:

时钟高电平时间 (Clock high time) :50 ns

时钟低电平时间 (Clock low time) :50 ns

输入建立时间 (Input setup time) :10 ns

输出有效时间 (Output valid delay) :10 ns

如图4-13所示。

图4-13 HDL Bencher设置窗口

■点击【0K】,接受默认的时间设定。

你的测试矢量(testbench)波形显示如图4-14所示:

图4-14 在 HDL Bencher中的 Testbench 波形

㈡ 初始化计数器输入:

在HDL Bencher的波形中,初始化如下计数器输入:

(注:在每个单元的蓝色区域输入激励。) ■在CLK第1周期下点击【RESET】单元直到该单元变为高;

■在CLK第2周期下点击【RESET】单元直到该单元变为低;

■在CLK第3周期下点击【CE】单元直到该单元变为高;

■在CLK第2周期下点击【DIR】单元直到该单元变为高;

你的测试矢量(testbench)波形现在看起来应该如图4-15所示。

图4-15 HDL Bencher激励及响应输入

■在CLK第11周期下,点击鼠标右键,选择【Set end of testbench】。

■将你的testbench文件存盘。选择【File】→【Save Waveform】,或点击工具栏的存盘图标。接下来,HDL Bencheer 会提示你设置你希望仿真的时钟周期数;

■点击【OK】;

■退出HDL Bencher。

新的testbench波形源文件【counter_tbw.tbw】自动加入到该工程项中。在【Processes for Sources】窗口,将出现ModelSim Simulator 的分层运行结构,如图4-16所示。

图4-16 ModelSim Simulator 的分层运行结构示意图

㈢ 生成预期的输出响应:

现在,你可以在已输入初始化激励的基础上,生成时钟模块预期的输出。

■在【Sources in Project】窗口中,选中【counter_tbw.tbw】文件;

■在【Processes for Sources】窗口中,点击【ModelSim Simulator】旁边的

“+”符号展开ModelSim仿真器的层次结构;

■双击【Generate Expected Simulation Results】;

此步骤采用定义好的输入运行一个后台仿真,产生输出值加入到testbench波形中。你的测试矢量(testbench)波形现在看起来应该如图4-17所示。从图中看出,计数器从CLK第3个周期开始计数,并在CLK第11周期结束。

■直接退出HDL Bencher而不选择波形存盘。

图4-17 生成仿真结果

§4. 3. 4 使用 ModelSim 进行仿真:

根据HDL Bencher中产生的预期结果,你现在可以用ModelSim进行仿真。在这部分教程中,你将运行行为仿真(亦即功能仿真)和布局布线后的仿真(时序仿真)。

㈠行为仿真:

用行为仿真以验证计数器模块的功能。

■在【Sources in Project】窗口中,选中【counter_tbw.tbw】文件;

■在【Processes for Sources】窗口中,点击【ModelSim Simulator】旁边的“+”符号展开ModelSim仿真器的层次结构;找到并双击【Simulate Behavioral Model】;

此时,ModelSim 仿真器自动启动。

■对于第一次运行ModelSim 的用户,会显示一个对话框,需要在其中做以下处理:

.选中【Do not show this dialog again】选项

.点击【Run ModelSim】。

此对话框在你重新安装或重新配置ModelSim之前将不再显示。

你的仿真结果现在显示在ModelSim的波形窗口(wave window)。

注意:ISE通过自动创建及运行一个仿真宏文件(.FDO文件)来自动处理仿真过程。虽然用户无法看到,但在本教程中,counter_tbw.fdo文件实现了以下操作:

.创建设计库;

.编译设计源文件和testbench源文件;

.调用仿真器;

.打开所有的观察窗口;

.将所有信号加到wave窗口;

.按照要求的运行时间属性进行仿真,11个时钟周期(1100ns)。

■在波形观察窗口Wave Window中点击【Zoom】→【Zoom Full】,或在工具条点击【Zoom Full】图标;

■点击【Zoom】→【Zoom in】,或在工具条点击【Zoom in】图标;

■拖动波形窗口下端的滚动条至窗口的最左端,仿真输出波形应如图4-18所示。

图4-18 行为仿真波形示意图

■关闭ModelSim主窗口,退出 ModelSim 。

㈡ 布局布线后的仿真:

布局布线后的仿真包括了目标器件的时延信息。counter模块的后仿真操作过程如下:■在【Sources in Project】窗口中,选中【counter_tbw.tbw】文件;

■在【Processes for Source】窗口中,点击【ModelSim Simulator】旁边的“+”

符号展开ModelSim仿真器的层次结构;找到并双击【Simulate Post-Place &

Route VHDL Model】;

注:此步骤会启动设计实现来进行布局布线及启动ModelSim 。

■点击【Zoom】→【Zoom Full】,或在工具条点击【Zoom Full】图标;

■点击【Zoom】→【Zoom in】,或在工具条点击【Zoom in】图标;

■拖动波形窗口下端的滚动条至窗口的最左端,仿真输出波形应如图4-19所示。

图4-19 布局布线后的仿真波形示意图

■关闭ModelSim主窗口,退出 ModelSim 。

§4. 3. 5 设计输入(顶层为原理图Top-Level Schematic)

本小节以一个原理图设计为例,说明了如何创建一个包含有例化的VHDL计数器模块的顶层原理图,描述了如何将若干个模块连接成一个原理图,如何给单根连线命名,如何给总线命名以及如何添加输入/输出管脚标记。

㈠为VHDL模块创建一个原理图符号:

■在工程管理器【Project Navigator】的【Sources in Project】窗口中,选择计数器模块counter_demo.vhd。

■在【Processes for Source】窗口,通过点击【Design Entry Utilities】旁边的“+”符号,并双击【Create Schematic Symbol】来创建一个counter_demo

计数器库。

㈡建立一个新的顶层原理图(Top-Level Schematic):

■在工程管理器【Project Navigator】菜单中,点击【Project】→【New Source】;

■选择Schematic作为文件类型,并命名为‘top’,如图4-20所示。

■点击【下一步Next】;

■点击【完成Finish】:

此时,原理图编辑器(ECS)将自动启动并在其原理图窗口中打开一张空图。

图4-20 选择Schematic作为顶层设计输入

㈢例化VHDL模块(Instantiating VHDL Module):

在原理图编辑器(ECS)中,例化两个VHDL计数器模块--counter

■在菜单中选择【Add】→【Symbol】,或者在工具栏中点击【Add Symbol】图标;

■从元件符号列表(在屏幕左侧)中,选择计数器counter;

注意:在本教程中,不要在类别(Categories)窗口中作任何选择。

■点击左键可将计数器counter放置在光标所在的位置;

请在原理图中放置两个计数器Counter。现在,原理图应该如图4-21所示。

图4-21 例化 VHDL 模块

■按ESC键退出后,添加符号(Add Symbol)模式。

注:可以通过放大缩小功能(【View】→【Zoom】→ In/ out/To Box/Full View)和拖动滚动条来调整视图大小及位置。

㈣原理图中连线(Wiring the Schematic):

在连接元件符号时,一些连线端可以悬空,而另一些连线端需和元件符号相连。

■首先激活划线功能,通过在菜单中选择【Add】→【Wire】,或者在工具栏中点击【Add Wire】图标;

■添加一根悬空线和延展连线

a)在计数器模块的某一管脚单击鼠标;

b)将连线拉伸到需要的长度;

c)在连线端点处双击鼠标;

按照如图4-22所示,给计数器模块的每一管脚添加连线。

■添加两个元件符号之间的连线

a) 在一个计数器模块的管脚处单击鼠标;

b) 在另一个计数器模块的对应管脚处双击鼠标,结果如图4-22所示。

当完成连线后,按ESC键退出添加连线(Add Wire)模式。

图4-22 模块的相应管脚添加连线示意图

㈤为连线添加网络名(Add Net Name to Wires)

画好连线后,你可为相应的连线添加网络名称。

■在菜单中选择【Add】→【Net Name】,或者在工具栏中点击【Add Net Name】

图标;

■创建网络名并放置到连线上的步骤如下:

a) 在工具栏右边的文本对话框中输入网络名〖clock〗;

b) 将鼠标移动到悬空连线的端点处(此时光标处显示出网络名);

c) 点击鼠标左键;

注:按照上面步骤添加其余5个网络名:reset,ce,load,dir1和dir2;

■按ESC键退出添加网络名(Add Net Name)模式。

㈤ 为总线添加网络名:

按照同样的步骤,为计数器模块的din和count管脚添加总线网络名并给总线宽度赋值。

■在菜单中选择【Add】→【Net Name】,或者在工具栏中点击【Add Net Name】图标;