:

一、填空题

1.格雷码的特点是任意两个相邻的代码中仅有___1___位二进制码不同。 2.已知函数

∑==)

5,4,3,1(),,(m C B A Y ,可知使Y = 0 的输入变量最小项有__4 _个。

3.使函数 (,,)Y A B C AB AC =+ 取值为1的最小项有 3 个。

4.函数L (A 、B 、C 、D )=∑m (5、7、13、14)+∑d (3、9、10、11、15)的最简与或表达式为:L = ___ _ _________。

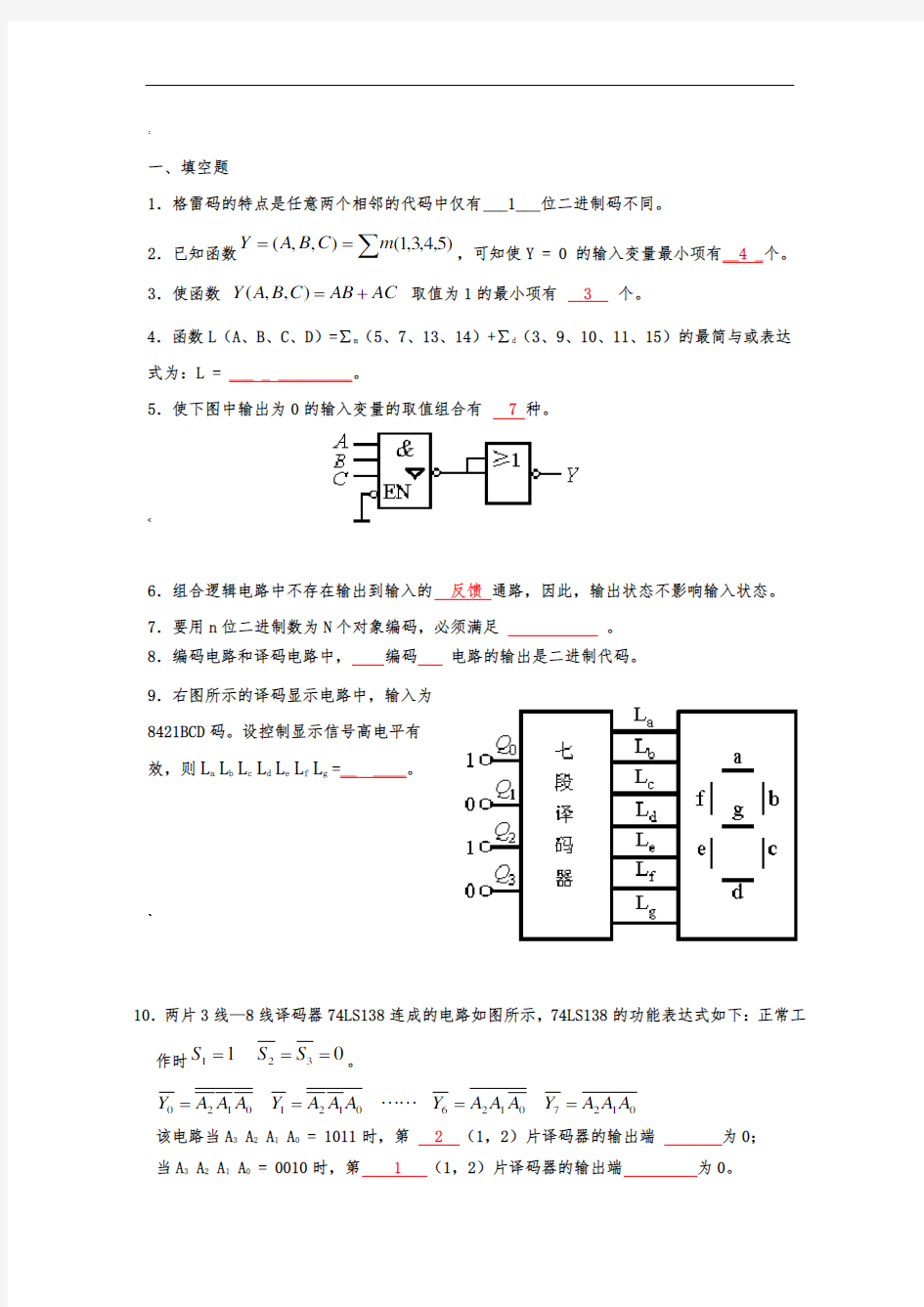

5.使下图中输出为0的输入变量的取值组合有 7 种。

<

6.组合逻辑电路中不存在输出到输入的 反馈 通路,因此,输出状态不影响输入状态。 7.要用n 位二进制数为N 个对象编码,必须满足 。 8.编码电路和译码电路中, 编码 电路的输出是二进制代码。 9.右图所示的译码显示电路中,输入为8421BCD 码。设控制显示信号高电平有效,则L a L b L c L d L e L f L g =__ ____。

、

10.两片3线—8线译码器74LS138连成的电路如图所示,74LS138的功能表达式如下:正常工作时01

321===S S S 。

01270

12601210

120A A A Y A A A Y A A A Y A A A Y ====

该电路当A 3 A 2 A 1 A 0 = 1011时,第 2 (1,2)片译码器的输出端 为0; 当A 3 A 2 A 1 A 0 = 0010时,第 1 (1,2)片译码器的输出端 为0。

#

{

11.异步置位端、异步复位端等符号上面的横线“—”表示____ _____。

12.仅具有“置0”、“置1”功能的触发器叫 D触发器。

13. 时序电路在结构上一定包含存储电路。

{

14. 计数器的基本功能是,它是用电路的输出状态来表示计数值。计数器的模是指。

15.如图所示逻辑电路中已知A为1态。当C时钟脉冲到来后,JK触发器具备功能。

16.要组成模15计数器,需要采用 4 个触发器。

`

17.欲将某时钟频率为32MHz的CP变为16MHz的CP,需要二进制计数器 1 个。

18. 用五个D触发器构成环形计数器,其模为 5 。

19.__只读__存储器在断电后数据不会丢失,而__ 随机__存储器断电后将丢失数据。20.存储器的容量是用___________乘____________来表示。

21. Intel 2716 EPROM 是 8 位存储器,它有 2K 字节,因此,其存储容量为16

KBit ,其中 1K = 1024 。

22. 存储容量为1024×4位RAM ,其地址线有 10 条。

23.PLD 的基本结构由 __与_ 阵列、__或_ 阵列、输入缓冲电路和输入电路构成。 24. 采用输出宏单元的PLD 器件是__GAL__。

【

25.某单稳态触发器在无外触发信号时输出为0态,在外加触发信号时,输出跳变为1态,因此其稳态为 0 态,暂稳态为 1 态。

26.单稳态触发器有__1 _个稳定状态,多谐振荡器有_ 0__个稳定状态。 27.单稳态触发器在外加触发信号作用下能够由 状态翻转到 状态。 28.集成单稳触发器分为可重复触发及不可重复触发两类,其中可重触发指的是在 暂稳态 期间,能够接收新的触发信号,重新开始暂稳态过程。

29. 多谐振荡器的振荡周期为T=tw 1+tw 2,其中tw 1为正脉冲宽度,tw 2为负脉冲宽度,则占空比应为____ __。

30.集成单稳态触发器的暂稳维持时间取决于 外接定时电阻电容 。 31.施密特触发器有__2_个阈值电压,分别称作 ___ ___ 和 _______ 。 32. 施密特 触发器能将缓慢变化的非矩形脉冲变换成边沿陡峭的矩形脉冲。

;

33.施密特触发器具有__回差__特性,定义为参数△U T =__ ____。 34.施密特触发器常用于波形的 与 。

35. 由555构成的施密特触发器,若电源电压U CC =12V ,电压控制端5脚经μF 电容接地,则下限触发电压U T -= __4__V 。 二、选择题

1.下列数码均代表十进制数6,其中按余3码编码的是_________。 【 】

A .0110

B .1100

C .1001

D .1101 2.实现A F 1的电路是 。

(

A

F 1

=1

A

F 1

V CC

【

(A ) (B ) (C )

3.实现AB F 2的电路是 。

)

(B ) (C )

4. 引入( )方法不能消除竞争冒险。

A.锁存脉冲

B.选通脉冲

C.冗余项

D.滤波电容 5. 下列门电路属于双极型的是( )

门 6.每门静态功耗,TTL 与CMOS 门相比较应( )。

A.前者大

B.后者大

:

C.一样大

D.无法比较

7. CMOS 与非门多余输入端应该( )。

A .接地

B .接电源电压

C .悬空 8.能实现总线连接方式的门为( )

A TTL 三态门

B O

C 门 C TTL 与非门

D TTL 或非门 9.以下错误的是( )

A.数值比较器可以比较数值大小

B.实现两个一位二进制数相加的电路叫全加器

C.实现两个一位二进制数和来自低位的进位相加的电路叫全加器

[

D.编码器可分为普通全加器和优先编码器

10. 三极管作为开关时工作区域是( )。

A. 饱和区+放大区

B. 击穿区+截止区

A F 2

F 2

≥1

A

F 2

B

1

1

C. 放大区+击穿区

D. 饱和区+截止区

、B、C、D、E 是五个开关,每个开关有两个状态0 和1,F 为电灯,亮时

为逻辑1,灭时为逻辑0。且开关中出现1 的个数为奇数时灯亮。若在五个不同的地方控制同一个电灯的灭亮,逻辑函数F 表达式应为()

A、ABCDE

B、A+B+C+D+E

C、A⊕ B⊕ C⊕ D⊕E

D、A⊙B⊙C⊙D⊙E :

12. 下列说法不正确的是()

A.集电极开路的门称为OC门

B.三态门输出端有可能出现三种状态(高阻态、高电平、低电平)

门输出端直接连接可以实现正逻辑的线或运算

D.利用三态门电路可实现双向传输

13. 对于JK触发器,若希望其状态由0转变为1,则所加激励信号是( )

=0X =X0

=X1 =1X

!

14. 电路如图所示,D触发器初态为0,则输出波形为( B )。

15. 下列触发器中不能用于移位寄存器的是( )。

触发器触发器

C.基本RS触发器

D.负边沿触发D触发器

16.下面4种触发器中,抗干扰能力最强的是( )

A.同步D触发器

B.主从JK触发器

C.边沿D触发器

D.同步RS触发器

…

17. 触发器是一种()。

A、单稳态电路

B、双稳态电路

C、无稳态电路

18.容量为4K 4位的RAM芯片,其地址线和数据线各为()

A.4和4条B.4和12条

C.12和4条D.4和10条

19.施密特触发器常用于对脉冲波形的( )

A .定时

B .计数

C .整形

D .产生

|

20. 555定时器构成的单稳态触发器,若输入信号是一个宽度比输出脉冲宽度还要宽的负脉冲,这个信号若要加到单稳态触发器输入端,( ) A.可以直接输入

B.须经RC 微分电路输入

C.须经RC 积分电路输入

D.须经电阻分压电路输入

21.能起到定时作用的电路是( ) A .施密特触发器

B .双稳态触发器

C .多谐振荡器

D .单稳态触发器

22.555定时器电源电压为V CC ,构成施密特触发器其回差电压为( )

A. V CC

21

%

32

D.

3

1V CC

23.下列时序电路的状态图中,具有自启动功能的是( B )

;

24.触发器的“1”状态是指( )

A 0=Q ,1=Q

B 0=Q ,0=Q

C 1=Q ,0=Q

D 1=Q ,1=Q 25.用6个触发器设计计数器,则此时计数器最合适的模数范围是( )

A 6

B 12

C 17→32

D 33→64

26.由n 个触发器构成的扭环形计数器,其无效状态数为 ( )

A n

B 2n

C 2n -2n

D 2n

-n 27.以下PLD 中,与、或阵列均可编程的是( )器件。

【

A. PROM

B. PAL C . PLA D. GAL

与PAL 的区别在于( )

A.输入采用缓冲器

B.输出逻辑宏单元(OLMC)

C.输出固定或阵列

D.输入采用可编程与阵列 29. 5G555集成定时器中内部触发器为( )。

A. 基本RS 触发器

B. 主从RS 触发器

C. 同步RS 触发器

D. 边沿RS 触发器 30.在以下各种电路中,属于时序电路的有( )。 —

A .ROM

B .编码器

C .寄存器

D .数据选择器

31. 关于计数器说法,正确的是------------------------------------------( ) A . 按计数功能可分为加法,减法,可逆三种。 B . 按进制分,可分为二进制,十进制及其他进制。 C . 按各触发器的动作步调,可分为同步,异步两种。 D . 以上都对。 三、分析设计题

1.分析图6中所示的逻辑电路,其中74LS151为8选1数据选择器,要求写出输出函数Z 的最简与-或表达式。

A

B C

图6

2.试用门电路设计一个水位报警电路,水位高度用四位二进制数ABCD 表示,二进制数的值即为水位高度,单位为米。当水位高于或等于7米时,白色指示灯W 点亮,否则,白色指示灯熄灭;当水位高于或等于9米时,黄色指示灯Y 开始亮,否则,黄色指示灯熄灭;当水位高于或等于11米时,红色指示灯R 开始亮,否则,红色指示灯熄灭。另外,水位不可能上升至14米。要求:①列出真值表;②写出化简后的“与-或”逻辑表达式;③画出逻辑电路图。 "

3.试分析图

7给定的阵列图,试写出输出表达式Y的最小项表示形式。

&

≥1

Y

A

B

C

D

图7

4、电路如下图所示,74LS48为BCD码七段显示译码器,74LS192为同步十进制可逆计数器,功能表如附表1.1.1所示。K1、K2、K3和K4为常开开关(按下接通,松开断开),不考虑键抖动,执行如下操作后,将数码管显示的内容填入相应的括号内。

1)按下开关K4;()

2)按下开关K3;()

3);

4)按下开关K3后松开,再按3次开关K1;()

5)同时按下开关K3、K4且不松开;()

6)按下开关K3,并保持按下状态,再按5次开关K1;()

5、试分析下图中的计数器在M=1和M=0时各为几进制。(已知74160为同步十进制计数器,异步置零,同步置数)

6.一同步时序电路如图8所示,设各触发器的起始状态均为0态。 (1)作出电路的状态转换表; (2)画出电路的状态图;

¥

(3)画出CP 作用下Q 0、Q 1、Q 2的波形图;

(4)说明电路的逻辑功能。

Q Q 1J 1J 1J C1

C1C11K

1K

1K

1

Q &

&FF 0

FF 1FF 2

图8 分析题参考答案:

1.解:D C AB CD B A D C B A C B A CD B A D C B A Z +++++=

C B A

D C B D B ++= 或者 D C A D C B D B ++=

2.解:(1)真值表为:

【

A

B C D W

Y

R

A

|

B

C

D

W

Y

R

0 0 \

0 0 0

0 0 1 0 0 ;

0 1 0

0 0 0 0 1 \

0 0 0

1 0 0 1 1 。

1 0 0

0 1 0 0 0 ^

0 1 0

1 0 1 1 0 )

0 0 1

1 0 0 0 1 @

0 1 1

1 1 1 0

1

:

0 0

1

1

,

1

1

1

(2)表达式 , 000011110AB CD

00011110000001

111

1

1

1

W

×

×

000011110AB

CD

00011110

000000

110

1

1

1

Y

×

×

BCD A W += AD AC AB Y ++=

000011110AB CD

00011110000000

110

1

R

×

×

ACD AB R +=

(3)逻辑图

A

B C W

Y

D

R

6、解:(1)电路的状态转换表

10=J 01Q J = 102Q Q J =

10=K 01Q K = 102Q Q K = (2)状态方程

n

n n n Q Q K Q J Q 0

000010=+=+ n

n n n n n n Q Q Q Q Q K Q J Q 1010111111+=+=+ n

n n n n n n n n Q Q Q Q Q Q Q K Q J Q 210210222212+=+=+

(3

(4)电路的状态图

Q 2Q 1Q 0

(5)Q 0、Q 1、Q 2的波形图

CP

Q0

Q1

Q2

(4)由状态转换图可看出该电路为同步八进制加法计数器。

数电设计数字钟基于 Q U A R T U S HEN system office room 【HEN16H-HENS2AHENS8Q8-HENH1688】

大连理工大学本科实验报告 题目:数电课设——多功能数字钟 课程名称:数字电路课程设计 学院(系):电信学部 专业:电子与通信工程 班级: 学生姓名: *************** 学号:*************** 完成日期: 成绩: 2010 年 12 月 17 日 题目:多功能数字时钟 一.设计要求 1)具有‘时’、‘分’、‘秒’的十进制数字显示(小时从00~23) 2)具有手动校时校分功能 3)具有整点报时功能,从59分50秒起,每隔2秒钟提示一次 4)具有秒表显示、计时功能(精确至百分之一秒),可一键清零 5)具有手动定时,及闹钟功能,LED灯持续提醒一分钟 6)具有倒计时功能,可手动设定倒计时范围,倒计时停止时有灯光提示,可一键 清零 二.设计分析及系统方案设计 1. 数字钟的基本功能部分,包括时、分、秒的显示,手动调时,以及整点报时部分。基本模块是由振荡器、分频器、计数器、译码器、显示器等几部分组成。利用DE2硬件中提供的50MHZ晶振,经过分频得到周期为1s的时钟脉冲。将该信号送入计数器进行计算,并把累加结果以“时”“分”“秒”的形式通过译码器由数码管显示出来。

进入手动调时功能时,通过按键改变控制计数器的时钟周期,使用的时钟脉冲进行调时计数(KEY1调秒,LOAD2调分,LOAD3调时),并通过译码器由七位数码管显示。 从59分50秒开始,数字钟进入整点报时功能。每隔两秒提示一次。(本设计中以两个LED灯代替蜂鸣器,进行报时) 2. 多功能数字钟的秒表功能部分,计时范围从00分秒至59分秒。可由输入信号(RST1)异步清零,并由按键(EN1)控制计时开始与停止。 将DE2硬件中的50MHZ晶振经过分频获得周期为秒的时钟脉冲,将信号送入计数器进行计算,并把累计结果通过译码器由七位数码管显示。 3.多功能数字钟的闹钟功能部分,通过按键(KEY1,KEY2,KEY3)设定闹钟时间,当时钟进入闹钟设定的时间(判断时钟的时信号qq6,qq5与分信号qq4,qq3分别与闹钟设定的时信号r6,r5与分信号r4,43是否相等),则以LED灯连续提示一分钟。 4. 多功能数字钟的倒计时功能部分,可通过按键(LOAD7调秒,LOAD8调分,LOAD9调时)设定倒计时开始时刻。倒计时的时钟与数字钟的时钟相同,每迎到一个时钟上升沿,则计数器减一。计数器减至00时,分钟位、秒钟位恢复至59,时钟位恢复至23。倒计时结束时(即00时00分00秒),控制LED灯亮,表示倒计时结束。 本设计通过数据选择器控制译码器,使数码管独立显示,各功能之间互不影响。当LOAD4为高电平,则对秒表信号进行译码,数码管显示秒表数据;当LOAD4为低电平,LOAD5为高电平,则对闹钟信号进行译码,数码管显示闹钟数据;当LOAD4,LOAD5为低电平,LOAD6为高电平,则对倒计时信号进行译码,数码管显示倒计时信号数据;当LOAD4,LOAD5,LOAD6全为低电平,则对正常时钟信号进行译码,数码管显示时钟信号数据。 附图1:系统总体结构框图

数字电路电子时钟课程设计 整个数字钟由时间计数电路、晶体振荡电路、校正电路、整点报时电路组成。 其中以校正电路代替时间计数电路中的时、分、秒之间的进位,当校时电路处于正常输入信号时,时间计数电路正常计时,但当分校正时,其不会产生向时 进位,而分与时的校位是分开的,而校正电路也是一个独立的电路。电路的信 号输入由晶振电路产生,并输入各电路 方案论证:方案一数字电子钟由信号发生器、“时、分、秒”计数器、译码 器及显示器、校时电路、整点报时电路等组成。秒信号产生器是整个系统的时 基信号,它直接决定计时系统的精度,一般用555构成的振荡器加分频器来实现。 优点:数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械 式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。 方案二秒、分计数器为60进制计数器,小时计数器为24进制计数器。 实现这两种模数的计数器采用中规模集成计数器74LS90构成。 优点:简单易懂,比较好调试。 1 设计原理数字电子钟由信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路等组成。秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用555构成的振荡器加分频器来实现。将标 准秒脉冲信号送入“秒计数器”,该计数器采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每累计60分,发出一个“时脉冲”信号,该信号将被 送到“时计数器”。“时计数器”采用24进制计数器,可以实现一天24h的累计。译码显示电路将“时、分、秒”计数器的输出状态经七段显示译码器译码,通 过六位LED显示器显示出来。整点报时电路是根据计时系统的输出状态产生一

数字电子技术课程设计报告 题目:数字电子钟 班级: 2016年 12月26日

目录 1、课程设计内容及要求**********************************************第3页 2、元器件清单及主要器件介绍****************************************第4页 3、原理设计和功能描述***********************************************第7页 4、数字电子钟的实现*************************************************第10页 5、总结与心得体会******************************************************第11页

课程设计内容及要求 1.1 数字钟简介 20世纪末,电子技术获得了飞速的发展。在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高、产品更新换代的节奏也越来越快。数字钟已成为人们日常生活中必不可少的生活日用品。广泛用于个人家庭以及车站、码头、剧场、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。 本次设计就用数字集成电路和一些简单的逻辑门电路来设计一个数字式电子钟,使其完成时间及星期的显示功能。多功能数字钟采用数字电路实现对“时”、“分”、“秒”数字显示的计时装置。具有时间显示、走时准确、显示直观、无机械传动装置等优点,因而得到了广泛的应用。 1.2 设计要求 1. 设计一个有“时”、“分”、“秒”(23小时59分59秒)显示,且有校时功能的电子钟。 2. 整点报时。在59分59秒时输出信号,音频持续1s,在结束时刻为整点。

课程设计任务书 学生姓名:专业班级: 指导教师:工作单位:信息工程学院 题目: 多功能数字钟的设计与实现 初始条件: 本设计既可以使用集成译码器、计数器、定时器、脉冲发生器和必要的门电路等,也可以使用单片机系统构建多功能数字钟。用数码管显示时间计数值。 要求完成的主要任务: (包括课程设计工作量及技术要求,以及说明书撰写等具体要求) 1、课程设计工作量:1周。 2、技术要求: 1)设计一个数字钟。要求用六位数码管显示时间,格式为00:00:00。 2)具有60进制和24进制(或12进制)计数功能,秒、分为60进制计数,时为24进制(或12进制)计数。 3)有译码、七段数码显示功能,能显示时、分、秒计时的结果。 4)设计提供连续触发脉冲的脉冲信号发生器, 5)具有校时单元、闹钟单元和整点报时单元。 6)确定设计方案,按功能模块的划分选择元、器件和中小规模集成电路,设计分电路,画出总体电路原理图,阐述基本原理。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

目录 摘要 (3) Abstract (4) 绪论 (5) 1仿真软件Proteus介绍 (6) 1.1Proteus概述 (6) 1.2Proteus功能特点 (6) 2方案论证 (8) 2.1方案一:采用中小规模集成电路模块实现 (8) 2.2方案二:采用单片机构建数字钟系统 (8) 2.3方案选择 (8) 3总体电路设计 (9) 3.1电路原理分析与设计 (9) 3.2系统原理图 (9) 4各模块电路分析 (10) 4.1时钟脉冲发生器 (10) 4.1.1方案一:RC振荡器 (10) 4.1.2方案二:555定时器 (11) 4.1.3方案三:石英晶体振荡器 (13) 4.1.4结论 (13) 4.2译码显示电路 (14) 4.3计数器电路 (16) 4.3.1 时计数电路 (17) 4.3.2 分计数电路 (18) 4.3.3秒计数电路 (19) 4.4 校时电路部分 (19) 4.4.1 方案一:快速脉冲法 (19) 4.4.1 方案二:按键单脉冲法 (20) 4.5 整点报时电路 (21) 4.6 闹钟电路 (22) 5总体电路设计与仿真 (23) 5.1总体电路图 (24) 5.2仿真结果分析 (24) 6 总结 (24) 参考文献 0

数字电子技术课程设计 数字电子钟 指导老师: 小组成员:

目录 摘要 (3) 第一节系统概述 (4) 第二节单元电路设计与分析 (6) 第三节电路的总体设计与调试 (11) 第四节设计总结 (13) 附录部分芯片功能参数表 (14) 参考文献 (17)

摘要 数字钟是一个将“时”,“分”,“秒”显示于人的视觉器官的计时装置。它的计时周期为24小时,显示满刻度为23时59分59秒。一个基本的数字钟电路主要由秒信号发生器、“时、分、秒、”计数器、译码器及显示器组成。由于采用纯数字硬件设计制作,与传统的机械表相比,它具有走时准,显示直观,无机械传动装置等特点。 本设计中的数字时钟采用数字电路实现对“时”、“分”、“秒”的显示和调整。通过采用各种集成数字芯片搭建电路来实现相应的功能。具体用到了555震荡器,74LS90及与非,异或等门集成芯片等。该电路具有计时的功能。 在对整个模块进行分析和画出总体电路图后,对各模块进行仿真并记录仿真所观察到的结果。 实验证明该设计电路基本上能够符合设计要求! 关键词振荡器、计数器、译码显示器、Multisim

第一节系统概述 数字电子钟是由多块数字集成电路构成的,其中有振荡器,分频器,校时电路,计数器,译码器和显示器六部分组成。振荡器和分频器组成标准秒信号发生器,不同进制的计数器产生计数,译码器和显示器进行显示,通过校时电路实现对时,分的校准。 1.1实验目的 1).掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法; 2).进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力; 3).提高电路布局﹑布线及检查和排除故障的能力; 4).培养书写综合实验报告的能力。 1.2 主要内容 熟悉Multisim10.0仿真软件的应用;设计一个具有显示、校时、整点报时和定时功能的数字时钟,.能独立完成整个系统的设计;用Multisim10.0仿真实现数字时钟的功能。 1.3 系统设计思路与总体方案 数字时钟基本原理的逻辑框图如下所示:

数字逻辑课程设计 自从它被发明的那天起,就成为人们生活中必不可少的一种工具,尤其是在现在这个讲 究效率的年代,时钟更是在人类生产、生活、学习等多个领域得到广泛的应用。然而随着时 间的推移,人们不仅对于时钟精度的要求越来越高,而且对于时钟功能的要求也越来越多,时钟已不仅仅是一种用来显示时间的工具,在很多实际应用中它还需要能够实现更多其它的

功能。诸如闹钟功能、日历显示功能、温度测量功能、湿度测量功能、电压测量功能、频率测量功能、过欠压报警功能等。钟表的数字化给人们的生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、自动起闭路灯、定时开关烘箱、通断动力设备、甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。可以说,设计多功能数字时钟的意义已不只在于数字时钟本身,更大的意义在于多功能数字时钟在许多实时控制系统中的应用。在很多实际应 用中,只要对数字时钟的程序和硬件电路加以一定的修改,便可以得到实时控制的实用系统, 从而应用到实际工作与生产中去。因此,研究数字时钟及扩大其应用,有着非常现实的意义。 数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路?目前,数字钟的功能越来越强,并且有多种专门的大规模集成电路可供选择? 前言 (2) 目录 (2) 题目 (2) 摘要 (2) 关键字 (3) 设计要求 (3) 正文 (3) 1电路结构与原理图 (3) 2数码显示器 (3) 60进制计数和24进制计数 (4) 校时 (7) 振荡器 (8) 3.计算、仿真的过程和结果 (9) 鸣谢 (11) 元器件清单 (11) 参考文献 (11) 总结与体会 (11) 教师评语 (12) 数字时钟的课程设计 摘要: 数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高 的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。 数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。目前, 数字钟的功能越来越强,并且有多种专门的大规模集成电路可供选择。本设计采用74LS290. 74LS47.BCD七段数码管和适当的门电路构成,可实现对时、分、秒等时间信息的采集和较时 功能地实现?

《数字时钟》技术报告 概要 数字钟是一个将“ 时”,“分”,“秒”显示于人的视觉器官的计时装置。它的计时周期为24 小时,显示满刻度为23 时59 分59 秒。一个基本的数字钟电路主要由秒信号发生器、“时、分、秒、”计数器、译码器及显示器组成。由于采用纯数字硬件设计制作,与传统的机械表相比,它具有走时准,显示直观,无机械传动装置等特点。 本设计中的数字时钟采用数字电路实现对“时” 、“分”、“秒” 的显示和调整。通过采用各种集成数字芯片搭建电路来实现相应的功能。具体用到了555 震荡器,74LS90 及与非,异或等门集成芯片等。该电路具有计时和校时的功能。 在对整个模块进行分析和画出总体电路图后,对各模块进行仿真并记录仿真所观察到的结果。 实验证明该设计电路基本上能够符合设计要求! 一、系统结构。 (1)功能。此数字钟能显示“时、分、秒”的功能,它的计时周期是24 小时,最大能显示23 时59 分59 秒,并能对时间进行调整和校对,相对于机械式的手表其更为准确。 2)系统框图

系统方框图 1 (3)系统组成。 1.秒发生器:由555 芯片和RC 组成的多谐振荡器,其555 上3 的输出频率由接入的电阻与电容决定。 2.校时模块:由74LS03 中的4 个与非门和相应的开关和电阻构成。 3.计数器:由74LS90 中的与非门、JK 触发器、或门构成相应芯片串接得到二十四、六十进制的计数器,再由74LS90 与74LS08 相连接而得到秒、分、时的进分别进位。 4.译码器:选用BCD 锁存译码器4511,接受74LS90 来的信号,转换为7 段的二进制数。

5.显示模块:由7 段数码管来起到显示作用,通过接受CD4511 的信号。本次选用的是共阴型的CD4511 。 二、各部分电路原理。 1.秒发生器:555 电路内部(图2-1)由运放和RS 触发器共同组成,其工作原理由8处接VCC ,C1 处当 Uco=2/3Vcc>u11 时运放输出为1,同理C2 也一样。最终如图3 接口就输出矩形波,而形成的秒脉冲。 图 2-2 555 功能表 2.校时模块:校时模块主要由74LS03中的4个与非门构成(图2-3),由其功能图看得出只要有一个输入端由H 到L 或者从L 到H 都会使输出端发生高低变化。因此通过开关的拨动产生高低信号从而对时、分处的计数器起到调数作用。

课程设计任务书 学生姓名: XXX 专业班级: 指导教师:工作单位: 题目: 多功能数字钟电路设计 初始条件:74LS390,74LS48,数码显示器BS202各6片,74LS00 3片,74LS04,74LS08各 1片,电阻若干,电容,开关各2个,蜂鸣器1个,导线若干。 要求完成的主要任务: 用中、小规模集成电路设计一台能显示日、时、分秒的数字电子钟,要求如下: 1.由晶振电路产生1HZ标准秒信号。 2.秒、分为00-59六十进制计数器。 3.时为00-23二十四进制计数器。 4.可手动校正:能分别进行秒、分、时的校正。只要将开关置于手动位置。可分别对秒、分、时进行连续脉冲输入调整。 5.整点报时。整点报时电路要求在每个整点前鸣叫五次低音(500HZ),整点时再鸣叫一次高音(1000HZ)。 指导教师签名:年月日 系主任(或责任教师)签名:年月日 多功能数字钟电路设计 摘要 (1) Abstract (2) 1系统原理框图 (3) 2方案设计与论证 (4)

2.1时间脉冲产生电路 (4) 2.2分频器电路 (6) 2.3时间计数器电路 (7) 2.4译码驱动及显示单元电路 (8) 2.5校时电路 (8) 2.6报时电路 (10) 3单元电路的设计 (12) 3.1时间脉冲产生电路的设计 (12) 3.2计数电路的设计 (12) 3.2.1 60进制计数器的设计 (12) 3.2.2 24进制计数器的设计 (13) 3.3译码及驱动显示电路 (14) 3.4 校时电路的设计 (14) 3.5 报时电路 (16) 3.6电路总图 (17) 4仿真结果及分析 (18) 4.1时钟结果仿真 (18) 4.2 秒钟个位时序图 (18) 4.3报时电路时序图 (19) 4.4测试结果分析 (19) 5心得与体会 (20) 6参考文献 (21) 附录1原件清单 (22) 附录2部分芯片引脚图与功能表 (23) 74HC390引脚图与功能表 (23)

大连理工大学本科实验报告 题目:数电课设——多功能数字钟 课程名称:数字电路课程设计 学院(系):电信学部 专业:电子与通信工程 班级: 学生姓名: *************** 学号:*************** 完成日期: 成绩: 2010 年 12 月 17 日 题目:多功能数字时钟 一.设计要求 1)具有‘时’、‘分’、‘秒’的十进制数字显示(小时从00~23) 2)具有手动校时校分功能 3)具有整点报时功能,从59分50秒起,每隔2秒钟提示一次 4)具有秒表显示、计时功能(精确至百分之一秒),可一键清零 5)具有手动定时,及闹钟功能,LED灯持续提醒一分钟 6)具有倒计时功能,可手动设定倒计时范围,倒计时停止时有灯光提示,可一键清零 二.设计分析及系统方案设计 1. 数字钟的基本功能部分,包括时、分、秒的显示,手动调时,以及整点报时部分。基本模块是由振荡器、分频器、计数器、译码器、显示器等几部分组成。利用DE2硬件中提供的50MHZ晶振,经过分频得到周期为1s的时钟脉冲。将该信号送入计数器进行计算,并把累加结果以“时”“分”“秒”的形式通过译码器由数码管显示出来。 进入手动调时功能时,通过按键改变控制计数器的时钟周期,使用的时钟脉冲进行调时计数(KEY1调秒,LOAD2调分,LOAD3调时),并通过译码器由七位数码管显示。

从59分50秒开始,数字钟进入整点报时功能。每隔两秒提示一次。(本设计中以两个LED灯代替蜂鸣器,进行报时) 2. 多功能数字钟的秒表功能部分,计时范围从00分秒至59分秒。可由输入信号(RST1)异步清零,并由按键(EN1)控制计时开始与停止。 将DE2硬件中的50MHZ晶振经过分频获得周期为秒的时钟脉冲,将信号送入计数器进行计算,并把累计结果通过译码器由七位数码管显示。 3.多功能数字钟的闹钟功能部分,通过按键(KEY1,KEY2,KEY3)设定闹钟时间,当时钟进入闹钟设定的时间(判断时钟的时信号qq6,qq5与分信号qq4,qq3分别与闹钟设定的时信号r6,r5与分信号r4,43是否相等),则以LED灯连续提示一分钟。 4. 多功能数字钟的倒计时功能部分,可通过按键(LOAD7调秒,LOAD8调分,LOAD9调时)设定倒计时开始时刻。倒计时的时钟与数字钟的时钟相同,每迎到一个时钟上升沿,则计数器减一。计数器减至00时,分钟位、秒钟位恢复至59,时钟位恢复至23。倒计时结束时(即00时00分00秒),控制LED灯亮,表示倒计时结束。 本设计通过数据选择器控制译码器,使数码管独立显示,各功能之间互不影响。当LOAD4为高电平,则对秒表信号进行译码,数码管显示秒表数据;当LOAD4为低电平,LOAD5为高电平,则对闹钟信号进行译码,数码管显示闹钟数据;当LOAD4,LOAD5为低电平,LOAD6为高电平,则对倒计时信号进行译码,数码管显示倒计时信号数据;当LOAD4,LOAD5,LOAD6全为低电平,则对正常时钟信号进行译码,数码管显示时钟信号数据。 附图1:系统总体结构框图

华东交通大学理工学院课程设计报告书所属课程名称数字电子技术课程设计题目数字电子钟课程设计分院电信分院 专业班级10电信2班 学号20100210410201 学生姓名陈晓娟 指导教师徐涢基 20 12 年12 月18 日

目录 第1章课程设计内容及要求 (3) 第2章元器件清单及主要器件介绍 (5) 第3章原理设计和功能描述 (10) 第4章数字电子钟的实现 (15) 第5章实验心得 (17) 第6章参考文献 (18)

第1章课程设计内容及要求 1.1 数字钟简介 20世纪末,电子技术获得了飞速的发展。在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高、产品更新换代的节奏也越来越快。数字钟已成为人们日常生活中必不可少的生活日用品。广泛用于个人家庭以及车站、码头、剧场、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。由于数字集成电路技术的发展和采用了先进的石英技术,使数字钟具有走时准确、性能稳定、集成电路有体积小、功耗小、功能多、携带方便等优点。 因此本次设计就用数字集成电路和一些简单的逻辑门电路来设计一个数字式电子钟,使其完成时间及星期的显示功能。多功能数字钟采用数字电路实现对“时”、“分”、“秒”数字显示的计时装置。具有时间显示、走时准确、显示直观、精度、稳定等优点,电路装置十分小巧,安装使用也方便而受广大消费的喜爱。 1.2 设计目的 1. 掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法;

2. 进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力; 3. 提高电路布局,布线及检查和排除故障的能力。 1.3 设计要求 1. 设计一个有“时”、“分”、“秒”(23小时59分59秒)显示,且有校时功能的电子钟。 2. 用中小规模集成电路组成电子钟,并在实验箱上进行组 装、调试。 3. 画出框图和逻辑电路图、写出设计、实验总结报告。 4. 整点报时。在59分59秒时输出信号,音频持续1s,在结束时刻为整点。

2009—2010学年第二学期 《数字电子技术课程设计》报告 专业班级:电气-08-1 姓名:曹操 学号:08051127 设计日期:2010年8月23日~27日 一.设计题目 多功能数字钟电路设计 二.设计任务及要求 多功能数字钟应该具有的功能有:显示时—分—秒、整点报时、小时和分钟可调等基本功能。整个钟表的工作应该是在1Hz信号的作用下进行,这样每来一个时钟信号,秒增加1秒,当秒从59秒跳转到00秒时,分钟增加1分,同时当分钟从59分跳转到00分时,小时增加1小时,小时的范围为0~23时。 在实验中为了显示的方便,由于分钟和秒钟显示的范围都是从0~59,所以可以用一个3位的二进制码显示十位,用一个四位的二进制码(BCD 码)显示个位,对于小时因为他的范围是从0~23,所以可以用一个2位的二进制码显示十位,用一个4位的二进制码(BCD码)显示个位。

实验中由于七段码管是扫描的方式显示,所以虽然时钟需要的是1Hz 时钟信号,但是扫描需要一个比较高频率的信号,因此为了得到准确的1Hz 信号,必须对输入的系统时钟50Mhz进行分频。 对于整点报时功能,本实验设计的是当进行正点的倒计时5秒时,让LED来闪烁进行整点报时的提示。 调整时间的按键用按键模块的S1和S2,S1调节小时,每按下一次,小时增加一个小时;S2调整分钟,每按下一次,分钟增加一分钟。另外用S8按键作为系统时钟复位,复位后全部显示00—00—00。 管脚分配如下表: 端口名使用模块信号对应FPGA管脚说明 S1 按键开关S1 R16 调整小时 S2 按键开关S2 P14 调整分钟 RST 按键开关S8 M15 复位 LED LED模块D1 L14 整点倒计时 LEDAG0 数码管模块A段N4 时间显示 LEDAG1 数码管模块B段G4 LEDAG2 数码管模块C段H4 LEDAG3 数码管模块D段L5 LEDAG4 数码管模块E段L4 LEDAG5 数码管模块F段K4 LEDAG6 数码管模块G段K5 SEL0 数码管选择位1 M4 8个数码管

课程设计任务书 题目: 多功能数字钟的设计与实现 初始条件: 本设计既可以使用集成译码器、计数器、定时器、脉冲发生器和必要的门电路等,也可以使用单片机系统构建多功能数字钟。用数码管显示时间计数值。 要求完成的主要任务: (包括课程设计工作量及技术要求,以及说明书撰写等具体要求) 1、课程设计工作量:1周。 2、技术要求: 1)设计一个数字钟。要求用六位数码管显示时间,格式为00:00:00。 2)具有60进制和24进制(或12进制)计数功能,秒、分为60进制计数,时为24进制(或12进制)计数。 3)有译码、七段数码显示功能,能显示时、分、秒计时的结果。 4)设计提供连续触发脉冲的脉冲信号发生器, 5)具有校时单元、闹钟单元和整点报时单元。 6)确定设计方案,按功能模块的划分选择元、器件和中小规模集成电路,设计分电路,画出总体电路原理图,阐述基本原理。 3、查阅至少5篇参考文献。按《******大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 1、2013年 3 月18 日,布置课设具体实施计划与课程设计报告格式的要求说明。 2、2013 年3 月22日至2013 年5 月10 日,方案选择和电路设计。 3、2013 年5 月25 日至2013 年7 月2 日,电路调试和设计说明书撰写。 4、2013 年7 月5 日,上交课程设计成果及报告,同时进行答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

目录 1 引言 (1) 1.1 数字钟简介 (1) 1.2 EWB简介 (1) 2 方案选择 (3) 3 系统框图 (4) 4 分电路设计 (5) 4.1 脉冲产生电路 (5) 4.1.1设计要求 (5) 4.1.2所需元件 (6) 4.1.3元件介绍 (6) 4.1.4参数计算 (7) 4.1.5电路设计 (8) 4.2计数电路 (9) 4.2.1秒电路 (9) 4.2.2分电路 (11) 4.2.3时电路 (13) 4.3显示电路 (14) 4.3.1所需元件 (14) 4.3.2元件介绍 (14) 4.3.3原理说明 (14) 4.3.4电路设计 (15) 4.4整点报时电路 (15)

数字电子技术电路课程设计题目:数字钟课程设计 学院:XXXXX 专业:XXXXX 班级:XXXX 姓名:XXXX 学号:XXXXX 指导老师:XXXXX

一、设计目的 数字钟是一种用数字电子技术实现时,分,秒计时的装置,具有较高的准确性和直观性等各方面的优势,而得到广泛的应用。此次设计数字电子钟是为了了解数字钟的原理,在设计数字电子钟的过程中,用数字电子技术的理论和制作实践相结合,进一步加深数字电子技术课程知识的理解和应用,同时学会使用Multisim电子设计软件。 二、设计要求 1.显示时,分,秒,用24小时制 2.能够进行校时,可以对数字钟进行调时间 3.能够正点报时(用555产生断续音频信号); 三、设计方案比较 方案一、采用中小规模集成电路实现 采用集成逻辑电路设计具有能实现,时、分、秒计时功能和定点报时功能,计时模块采用时钟信号触发,不需要程序控制。 方案二:EDA技术实现 采用EDA作为主控制器外围电路进行电压,时钟控制、键盘和LED控制。但此方案逻辑电路复杂,外围设备多,灵活性较低,不利于扩展 方案三、单片机编程实现 此方案采用单片机编程来设计和控制。 综上,根据自身的知识和方案比较,采用方案一,因为方案一简便灵活,扩展性好,同时符合此次数子电子知识设计的要求。 四、设计过程和说明 1.数字电子钟计时和显示功能的实现 (1)采用两片十进制计数器74LS160N扩展连接,设计60进制的计数器,显示0到59,在59时采用置数的方法,将两片74LS160N同时置数至0,以循环显示0到59。(图)

(2)24进制亦采用两片十进制计数器74LS160N扩展连接,设计24进制的计数器,显示0到23,在23时采用置数的方法,将两片74LS160N同时置数至0,以循环显示0到23(图)

电子时钟课程设计_数电课程设计数字电子 时钟的实现 课程设计报告设计题目:数字电子时钟的设计与实现班级: 学号: 姓名: 指导教师: 设计时间: 摘要钟表的数字化给人们生产生活带来了极大的方便,大大的扩展了原先钟表的报时。诸如,定时报警、按时自动打铃、时间程序自动控制等,这些,都是以钟表数字化为基础的。功能数字钟是一种用数字电路实现时、分、秒、计时的装置,与机械时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。从原理上讲,数字钟是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。 因此,此次设计与制作数字钟就是为了了解数字钟的原理,从而学会制作数字钟,而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及使用方法。通过此次课程设计可以进一步学习与各种组合逻辑电路与时序电路的原理与使用方法。通过仿真过程也进一步学会了Multisim 7的使用方法与注意事项。

本次所要设计的数字电子表可以满足使用者的一些特殊要求,输 出方式灵活,如可以随意设置时、分、秒的输出,定点报时。由于集 成电路技术的发展,,使数字电子钟具有体积小、耗电省、计时准确、 性能稳定、维护方便等优点。 关键词:数字钟,组合逻辑电路,时序电路,集成电路目 录摘要 (1) 第1章概述 (3) 第2章课程设计任务及要求 (4) 2.1设计任务 (4) 2.2设计要求 (4) 第3章系统设计 (6) 3.1方案论证 (6) 3.2系统设计 (6) 3.2.1 结构框图及说明 (6) 3.2.2 系统原理图及工作原理 (7) 3.3单元电路设计 (8) 3.3.1 单元电路工作原理 (8) 3.3.2 元件参数选择···································14 第 4章软件仿真 (15) 4.1仿真电路图 (15) 4.2仿真过程 (16)

数字电子技术课程设计报告题目:多功能数字钟课程设计 学年:2007 学期:第二学期 专业:自动化班级:0703 学号:姓名:刘磊 指导教师及职称:魏巍 时间:2009年7月9日 太原理工大学现代科技学院

数字电子技术课程设计报告 一、设计目的 数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。 数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。 因此,我们此次设计与制做数字钟就是为了了解数字钟的原理,从而学会制作数字钟.而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法.且由于数字钟包括组合逻辑电路和时叙电路.通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法. 二、设计要求 (1)设计指标 ①时间以12小时为一个周期; ②显示时、分、秒; ③具有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间; ④计时过程具有报时功能,当时间到达整点前10秒进行蜂鸣报时; ⑤为了保证计时的稳定及准确须由晶体振荡器提供表针时间基准信号。 (2)设计要求 ①画出电路原理图(或仿真电路图); ②元器件及参数选择; ③电路仿真与调试; ④PCB文件生成与打印输出。 (3)制作要求自行装配和调试,并能发现问题和解决问题。 (4)编写设计报告写出设计与制作的全过程,附上有关资料和图纸,有心得体会。 三、原理框图 1.数字钟的构成 数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。通常使用石英晶体振荡器电路构成数字钟。

吉林建筑大学 电气与计算机学院 数字电子技术课程设计报告 设计题目:多功能数字钟的电路设计专业班级:自动化141 学生姓名: 学号: 指导教师: 设计时间:2016.06.20-2016.07.01

多功能数字钟的电路设计报告 一、设计任务及要求 本课程设计的基本任务,通过指导学生循序渐进地独立完成数字电路的设计任务,加深学生对理论知识的理解,有效地提高了学生的动手能力,独立分析问题、解决问题能力,协调能力和创造性思维能力。侧重提高学生在数字电路应用方面的实践技能,树立严谨的科学作风,培养学生综合运用理论知识解决实际问题的能力。学生通过电路的设计、安装、调试、整理资料等环节,初步掌握工程设计方法和组织实践的基本技能,逐步熟悉开展科学实践的程序和方法。 设计要求: 1.时钟显示功能,能够以十进制显示“时”、“分”、“秒”。 2.具有校时功能,可分别对“时”、“分”进行单独校时。 3.能用硬件成功实现以上各功能。 4.具有整点自动报时功能,整点前的6s自动发出鸣叫声,步长1s,每1s 鸣叫一次,前五响是低音,最后一响为高音。 二、设计的作用、目的 数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。因此,我们此次设计与制做数字钟就是为了了解数字钟的原理,从而学会制作数字钟.而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法.且由于数字钟包括组合逻辑电路和时叙电路.通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。掌握数字钟的设计、组装与调试方法。熟悉集成电路的使用方法。 三、设计过程 1.方案设计与论证 1.1系统设计思路 能按时钟功能进行小时、分钟、秒计时,能调时调分,能整点报时,使

课程设计任务书 课题名称:数字时钟电路 设计内容与要求: (1)准确计时,以数字形式显示时、分、秒的时间; (2)具有手动校时、校分功能,分别可以对时和分进行校正; (3)计时过程具有整点报时功能,当时间到达整点前60秒开始,蜂鸣器1秒响一次; 技术条件与要求: (1)计时电路分和秒采取60进制,时采取24进制; (2)整点报时电路采用了74LS20. 指导教师签名:教研室主任签名:讲师 发题日期:年月日完成日期:年月日 年月日

摘要 在生活中的各种场合经常要用到电子钟,现代电子技术的飞跃发展各类智能化产品脱颖而出,数字电路具有电路简单、可靠性高、成本低等优点,本设计重点以数字电路为核心设计智能电子钟。 本设计电路由计时电路、控制电路、显示电路等部分组成,在数码管上显示24小时计时的时刻,具有清零、保持、校时、报时功能。 关键字数字钟;计数器;显示器;校准;整点报时

目录 1 数字时钟概述 (4) 2 电路设计流程图 (5) 3 电路工作原理及分析 (6) 3.1核心芯片74LS90介绍 (6) 3.2计数电路设计与仿真 (8) 3.2.1 个位向十位进制的实现 (8) 3.2.2 六十进制的实现 (9) 3.2.3 秒向分进位的实现 (10) 3.2.4 计时电路的实现 (11) 3.3校时及整点报时电路的实现 (12)

1 数字时钟概述 数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性等优点,数字钟从原路上讲是一种典型的数字电路,其中包括了组合逻辑和时序逻辑。 数字钟是采用数字电路实现对时、分、秒数字显示的计时装置,广泛用于个人家庭办公、车站、办公室等公共场合,成为人们日常生活中不可缺少的物品,由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度远远超过老式钟表,钟表的数字化给人们生活带来了极大的方便,而且扩展了报时功能。

大连理工大学本科实验报告题目:多功能数字钟 课程名称:《数字电路课程设计》 学院(系):电子信息与电气工程学部 专业:自动化 班级:电自0801 学生姓名: 学号:200881142 完成日期:2011年7月20日 成绩: 2011 年7 月20 日

题目:多功能数字钟 1 设计要求 (1)一个具有“时”,“分”,“秒”的十进制数字显示(小时从00~23) 计时器。 (2)具有手动校时,校分的功能。 (3)定时与闹钟功能,能在设定的时间发出闹铃声 (4)能整点报时。要求从59分54秒起报时,每隔2秒发出低音,,连续 3次,在整点要求是高音。 2 设计分析及系统方案设计 系统总体结果 系统设计要求说明: (1)该秒表用模24、模60计数器实现24小时计时 (2)在调节闹钟时不影响数字钟的正常走表; (3)在调节闹钟时要通过数码管显示出; 3系统以及模块硬件电路设计 根据上述给出的系统总体结构框图,给出系统硬件电路设计,并作必要的说明和理论计算。由于“数字电路课程设计”课程采用实验箱完成,没有学时涉

及有关FPGA芯片的使用,因此有关FPGA芯片的部分可以用“FPGA最小系统”模块框代替。其余接口部分(按键,LED以及数码管,各种接口等需要设计电路以及参数)。 下载时选择的开发系统模式以及管脚定义 表1 GW48-CK开发系统工作模式:模式0 接口名称 类型 (输入/输 出) 结构图上 的信号名引脚号说明 en 输入PIO7 16 手动校时(1-调时,0- 走表) th 输入PIO6 11 调时按键(en=1,或 en1=1调时) en1 输入PIO5 10 闹钟设定(1-调时,0- 不走) tm 输入PIO4 9 调分按键(en=1或 en1=1,才可调分)alarmstop 输入PIO3 8 闹铃控制端 clk 输入CLOCK1 42 系统走表时钟(f=1Hz)clk1 输入CLOCK0 2 闹钟与整点报时时钟 (f=256Hz) clk2 输入CLOCK5 83 整点报时时钟时钟 (f=1024Hz) qhh 输出PIO47-PIO44 79、78、73、72 输出小时的高位 qlh 输出PIO43-PIO40 71、70、67、66 输出小时的低位 qhm 输出PIO39-PIO36 65、64、62、61 输出分钟的高位 qlm 输出PIO35-PIO32 60、59、58、54 输出分钟的低位 qhs 输出PIO31-PIO28 53、52、51、50 输出秒的高位 qls 输出PIO27-PIO24 49、48、47、39 输出秒的低位 speaker 输出SPEAKER 3 输出蜂鸣器的时钟 4 系统的VHDL设计 系统的各个部分如何用VHDL设计出来的应该有说明,包括论述以及真值表或者状态图等。 要求:系统(或顶层文件)结构描述,各个模块(或子程序)的功能描述; 1)用原理图实现的,需包含以下内容: (1)系统原理图

1.设计题目:简易数字电子钟设计 1.1设计目的:(1)能独立查阅、整理、分析有关资料 (2)能用数字集成电路完成设计任务 (3)掌握脉冲产生、整形与分频电路 (4)掌握组合逻辑器件 1.2基本要求: (1) 24小时制时间显示,6个7段数码管显示 (2)要具有分钟与小时的校时电路 (3)其他附加功能可以自行设计 2.设计过程的基本要求: 2.1 基本部分必须完成,学有余力的同学可以根据自己的能力自行确定发挥部分 并完成。 2.2 符合设计要求的报告一份。 设计报告内容要求: 1. 写出你考虑该问题的基本思路,画出一个实现电路功能的大致框图。 2. 设计出框图中各部分逻辑电路,可用中、小规模集成电路,也可用中 规模集成电路连接而成。对各部分电路的工作原理应作出说明。最 后,画出整个设计电路的原理电路图,并说明电路工作原理。 3. 进行设计的仿真验证。 4. 要求用A4纸打印,不允许复印。装订顺序为:封面、任务书、成绩 评审意见表、中文摘要和关键词、目录、正文、参考文献。

5. 设计报告提交的截止时间为2013年1月17日。

中文摘要 本数字钟设计为具有24小时显示,及分钟、秒的显示、有校正功能,利用74LS290、石英晶振、74LS48、数码管等器件连接完成的。核心是多谐振荡器,可以是用555型的,也可利用石英晶振型的。 此简易数字钟为基础型,可由此拓展额外功能,例如:报时等。 关键字74LS290,英晶振,分频器,计数器,译码器。

目录 题目分析 (1) 1 方案设计 (2) 1.1总体框图 (2) 1.1.1 总体概括 (2) 1.2各部分电路图与详解 (3) 1.2.1 振荡器 (3) 1.2.2 分频器 (3) 1.2.3 译码与显示 (5) 1.2.4 计数器 (6) 1.2.5 校时 (7) 1.2.6 额外电路----整点报时 (7) 附录 (8) 原件清单 (9) 附加电路元件清单 (9) 总结 (10)

机电工程学院 本科生课程设计 题目:数字时钟 课程:数字电子技术 专业:电气工程及其自动化 班级: 学号: 姓名: 指导教师: 完成日期:

任务书

目录 1设计的目的及任务 (1) 1.1 课程设计的目的 (1) 1.2 课程设计的任务与要求 (1) 1.3 课程设计的技术指标 (1) 2 数字时钟的介绍和原理 (2) 2.1 数字时钟的介绍 (2) 2.2 数字时钟的电路组成 (2) 2.3 数字时钟的工作原理 (3) 3 数字时钟总设计方案和各部分电路设计方案 (4) 3.1 数字时钟总设计方案 (4) 3.2 各部分电路设计方案 (5) 3.3 总电路设计图 (17) 4 电路仿真 (17) 5收获与体会 (24) 6 仪器仪表明细清单 (24) 参考文献 (25)

1.设计的目的及任务 1.1 课程设计的目的 (1)巩固所学的相关理论知识; (2)实践所掌握的电子制作技能; (3)会运用Mutisim工具对所作出的理论设计进行模拟仿真测试,进一步完善理论设计;(4)通过查阅手册和文献资料,熟悉常用电子器件的类型和特性,并掌握合理选用元器件的原则; (5)掌握模拟电路的安装\测量与调试的基本技能,熟悉电子仪器的正确使用方法,能力(6)分析实验中出现的正常或不正常现象(或数据)独立解决调试中所发生的问题;(7)学会撰写课程设计报告; 1.2 课程设计的任务与要求 (1)根据技术指标要求及实验室条件设计出电路图,分析工作原理,计算元件参数;(2)列出所有元器件清单; (3)安装调试所设计的电路,达到设计要求; (4)记录实验结果。 1.3 课程设计的技术指标 (1)准确计时,用数码管显示小时、分和秒; (2)小时以24小时计时; (3)带有时间校正功能; (4)“闹钟”功能;