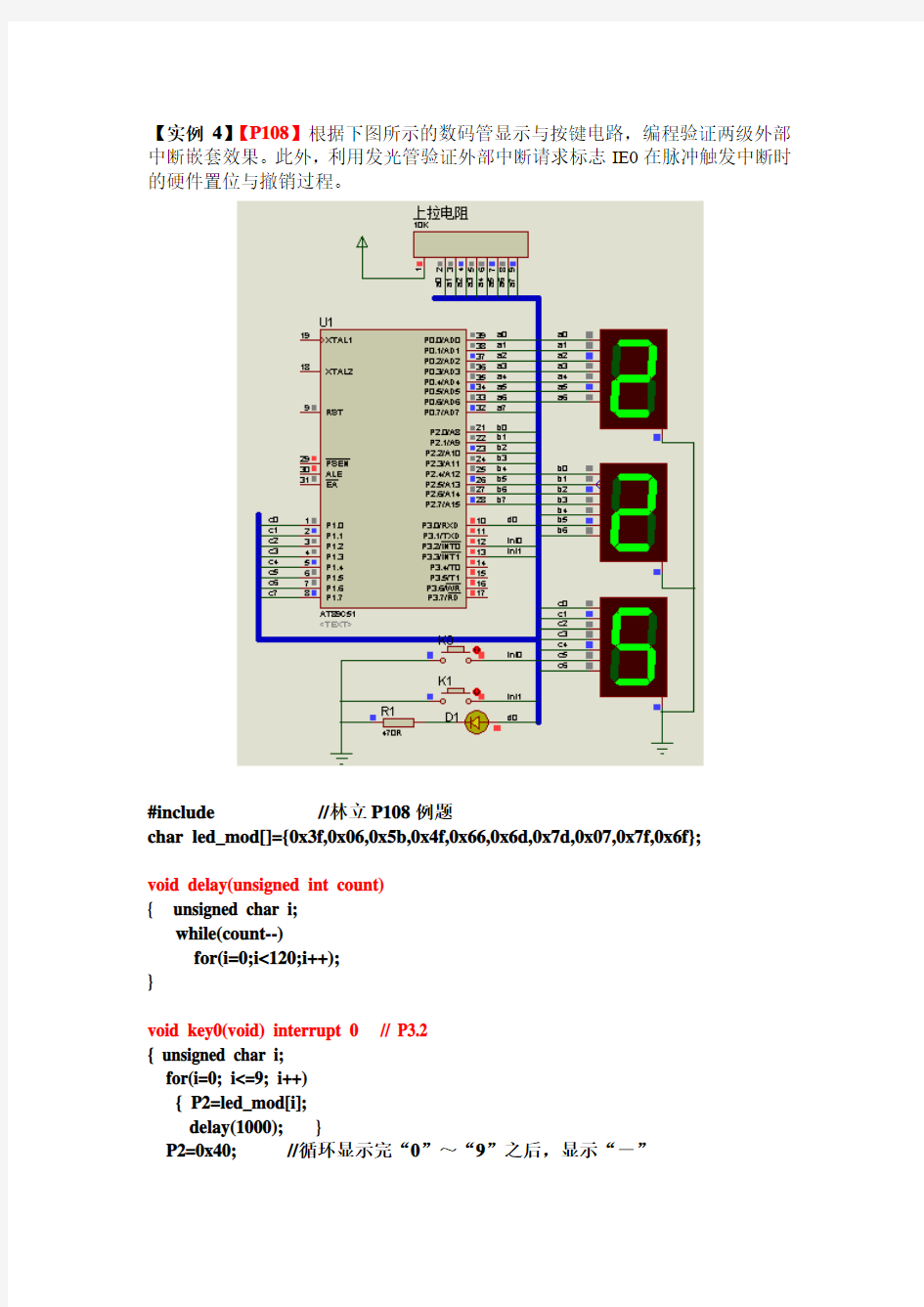

【实例4】【P108】根据下图所示的数码管显示与按键电路,编程验证两级外部中断嵌套效果。此外,利用发光管验证外部中断请求标志IE0在脉冲触发中断时的硬件置位与撤销过程。

#include

char led_mod[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f};

void delay(unsigned int count)

{ unsigned char i;

while(count--)

for(i=0;i<120;i++);

}

void key0(void) interrupt 0 // P3.2

{ unsigned char i;

for(i=0; i<=9; i++)

{ P2=led_mod[i];

delay(1000); }

P2=0x40; //循环显示完“0”~“9”之后,显示“-”

void key1(void) interrupt 2 //P3.3

{ unsigned char i;

for(i=0; i<=9; i++)

{ P1=led_mod[i];

delay(1000);

}

P1=0x40;

}

void main(void)

{ unsigned char i;

TCON=0x05; // 0x05= 0000 0101,最好写成IT0=1,IT1=1

PX0=0;

PX1=1; //INT1 高优先级

P1=0x40; P2=0x40;

IE=0x85; // 0x85=1000 0101, EA=1, EX1=1,EX0=1

while(1)

{ for(i=0;i<=9;i++)

{ P0=led_mod[i];

delay(1000); }

}

}

5.6 扩充外部中断源

实际应用中,两个外部中断请求源往往不够用,需对外部中断源进行扩充,如图5-10所示。系统有5个外部中断请求源IR0~IR4,高电平有效。

INT,优先级高的请求源IR0直接接到80C51的一个外部中断请求输入端0

其余4个请求源IR1~IR4通过各自的OC门(集电极开路门)连到80C51的另

INT,同时还连到P1口的P1.0~P1.3脚,供80C51查询。一个外中断源输入端1

图5-10所示电路,除了IR0优先权级别最高外,其余4个外部中断源的中断优先权的高与低取决于查询顺序。

图5-10 中断和查询相结合的多外部中断请求源系统假设图5-10中的4个外设中有一个提出高电平有效的中断请求信号,则中断请求通过4个集电极开路OC门的输出公共点,即1

INT脚的电平就会变低。究竟是哪个外设提出的请求,要通过程序查询P1.0~P1.3引脚上的逻辑电平来确定。

查询法扩展外部中断源比较简单,但是扩展的外部中断源个数较多时,查询时间稍长。因此,可以采用74LS优先编码器来实现。

【74LS148;8-3线八进制优先编码器】

8线-3线优先编码器:54148/74148

148为8线-3线,148将8条数据线(0-7)进行3线(4-2-1)二进制(八进制)优先编码,即对最高位数据线进行译码。

利用选通端5(EI)和输出选通端15(EO)可进行八进制扩展。引脚图如下:

【例】利用74LS148扩展外部中断【P110】

#include

#include

unsigned char led_code[]={0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8};

void delay(unsigned int count)

{ unsigned char i;

while(count--)

for(i=0;i<120;i++);

}

void EX_INT0() interrupt 0

{ unsigned char bi;

bi= P2 & 0x07; //0x07=0000 0111,保留P2口的低3位switch(bi)

{ case 0x00: //7按下

P0= led_code [7];

break;

case 0x01: //6按下

P0= led_code [6];

break;

case 0x02: //5按下

P0= led_code [5];

break;

case 0x03: //4按下

P0= led_code [4];

break;

case 0x04: //3按下

P0= led_code [3];

break;

case 0x05: // 2按下

P0= led_code [2];

break;

case 0x06: // 1按下

P0= led_code [1];

break;

case 0x07: // 0按下

P0= led_code [0];

break;

}

}

void main()

{ EA=1;

EX0=1;

IT0 = 1; //INT0引脚上,出现负跳变作为中断信号

while(1);

}

小结

1、5个中断源及其对应入口地址:

外中断2个:INT0、INT1

定时中断2个:T0、T1

串行中断1个:RI/TI

2、中断优先原则:分2个优先级;

同级:INT0→T0→INT1→T1→RI/TI。

3、中断响应过程:

4、中断请求的撤消:3类中断请求撤消的异同点。

5、中断源的扩展。

【第十一次课20111010的一部分】

作业:把教材的P87页的图4.24改为中断实现,用负跳变方式,中断0(INT0)显示“L2”,中断1(INT1)显示“H3”。

#include

// 林立P87的例题20120930

unsigned char led_mod[]={0x38,0x5b,0x76,0x4f}; // L2H3 unsigned char i,led_pos;

sbit P17=P1^7;

void delay(unsigned int count)

{ unsigned char i;

while(count--)

for(i=120;i>0;i--);

}

void xint0(void) interrupt 0

{ led_pos=2; }

void xint1(void) interrupt 2

{ led_pos=0; }

main()

{ IT0=1;

IT1=1;

EX0=1;

EX1=1;

EA=1;

P1=0xfd; //0xfd=1111 1101 while(1)

{

for(i=0;i<2;i++)

{ P2=led_mod[i+led_pos];

delay(5);

P1=~P1;

}

}

}

第5章中断系统 1)作业题 1.8051微控制器中,有几个中断源?几个中断优先级?中断优先级是如何控制的?在出 现同级中断申请时,CPU按什么顺序响应(按由高级到低级的顺序写出各个中断源)? 各个中断源的入口地址是多少? 答:8051微控制器中有五个中断源,两个中断优先级。通过IP进行优先级控制。IP为中断优先级寄存器,物理地址为B8H,其中的后五位PS PT1 PX1 PT0 PX0分别控制串行口、定时器/计数器1、外部中断1、定时器/计数器0、外部中断0的优先级。在出现同级中断申请时,CPU按如下顺序响应各个中断源的请求:INT0、T0、INT1、T1、串行口,各个中断源的入口地址分别是0003H、000BH、0013H、001BH、0023H。 2.8051微控制器中,各中断标志是如何产生的,又如何清0的? 答:每个中断源请求中断时会在SFR的某些寄存器中产生响应的标志位,表示该中断源请求了中断。INT0、INT1、T0和T1的中断标志存放在TCON(定时器/计数器控制寄存器)中,占4位;串行口的中断标志存放在SCON(串行口控制寄存器)中,占2位。 TF0:T0溢出标志,溢出时由硬件置1,并且请求中断,CPU响应后,由硬件自动将TF0清0;不用中断方式时,要用软件清0。 TF1:T1溢出标志,溢出时由硬件置1,并且请求中断,CPU响应后,由硬件自动将TF1清0;不用中断方式时,要用软件清0。 IE0:INT0中断标志,发生INT0中断时,硬件置IE0为1,并向CPU请求中断。 IE1:INT1中断标志,发生INT1中断时,硬件置IE1为1,并向CPU请求中断。SCON:串行口控制寄存器。 TI:串行口发送中断标志,发送完一帧数据时由硬件置位,并请求中断。 RI:串行口接受中断标志,接收到一帧数据时,由硬件置位,并且请求中断。 TI、RI标志,必须用软件清0。 3.简述8051微控制器中中断响应的过程。 答:单片机响应中断的条件:中断源有请求(响应的中断标志位置1),CPU允许所有中断(CPU中断允许位EA=1),中断允许寄存器IE中,相应中断源允许位置1;没有同级或者高级中断正在服务,现行指令已经执行完毕,若执行指令为RETI或者读/写IE或者IP指令时则该指令的下一条指令也执行完毕。 中断响应的过程: 1)CPU在每个机器周期的S5P2检测中断源。在下一个机器周期的S6按照优先次序查询各个中断标志。若查询到有中断标志为1时,按照优先级别进行处理,即响应中断;2)置相应的“优先级状态”触发器为1,即指出CPU当前正在处理的中断优先级,以阻断同级或者低级中断请求; 3)自动保护断点,即将现行PC内容(即断点地址)压入堆栈,并且根据中断源把相应的

第五章习题答案 5-1 什么是中断系统?中断系统的功能是什么? 实现中断功能的硬件和软件称为中断系统. 中断系统功能包括进行中断优先排队、实现中断嵌套、自动响应中断和实现中断返回。 5-2 什么是中断嵌套? CPU在响应某一个中断源中断请求而进行中断处理时,若有中断优先级更高的中断源发出中断请求,CPU会暂停正在执行的中断服务程序,转向执行中断优先级更高的中断源的中断服务程序,等处理完后,再返回继续执行被暂停的中断服务程序,这个过程称为中断嵌套。 5-3 什么是中断源?MCS-51有哪些中断源?各有什么特点? ①实现中断功能的硬件和软件称为中断系统,产生中断请求的请求源称为中断源. ②5个中断源中共有两个外部中断、两个定时中断和一个串行中断。 (1)外部中断源 外部中断是由外部原因(如打印机、键盘、控制开关、外部故障)引起的,可以通过两 个固定引脚来输入到单片机内的信号,即外部中断0(INT0)和外部中断1(INT1)。 (2)定时中断类 定时中断是由内部定时(或计数)溢出或外部定时(或计数)溢出引起的,即T0和T1 中断。 (3)串行口中断类 串行口中断是为接收或发送一帧串行数据,硬件自动使RI和TI置1,并申请中断 5-4 MCS-51单片机响应外部中断的典型时间是多少?在哪些情况下,CPU将推迟对外部中断请求的响应? (1)MCS-51单片机的最短响应时间为3个机器周期,最长响应时间8个机器周期。 (2)有下列任何一种情况存在,则中断响应会受到阻断。 ①CPU正在执行一个同级或高一级的中断服务程序; ②当前的机器周期不是正在执行的指令的最后一个周期,即正在执行的指令还未完成前,任何中断请求都得不到响应; ③正在执行的指令是返回指令或者对专业寄存器IE、IP进行读/写的指令,此时。在 执行RETI或者读写IE或IP之后,不会马上响应中断请求,至少在执行一条其他之后才会 响应。若存在上述任何一种情况,中断查询结果就被取消,否则,在紧接着的下一个机器周期,就会响应中断。 5-5 MCS-51有哪几种扩展外部中断源的方法?各有什么特点? 扩展外部中断源的方法有定时扩展法和中断加查询扩展法两种。定时扩展法用于外部 中断源个数不太多并且定时器有空余的场合。中断加查询扩展法用于外部中断源个数较多的 场合,但因查询时间较长,在实时控制中要注意能否满足实时控制要求。 5-6 MCS-51单片机各中断源发出的中断请求信号,标记那些寄存器中? 外部中断0(INT0)和外部中断1(INT1)中断请求信号标记在TCON中IE1和IE0。 T0和T1中断中断请求信号标记在TCON中TF1和TF0 串行口中断类中断请求信号标记在SCON中TI和RI 5-7 编写出外部中断1为跳沿触发的中断初始化程序。 SETB EA SETB EX1 SETB IT1

第五章中断系统及定时/计数器参考答案 1、80C51有几个中断源?各中断标志是如何产生的?又是如何复位的?CPU 响应各中断时,其中断地址入口是多少? 答:80C51有5个中断源,具体的名称、产生方式、复位方式和中断入口地址如下: (1)INT0(P302), 外部中断0请求信号输入引脚。当CPU检测到P3.2引脚出现有效的中断信号时,中断标志IE0(TCON.1)置一,向CPU 申请中断,中断入口地址为0003H。可由IT0(TCON.0)选择其为低 电平有效还是下降沿有效。当IT0=0时,中断标志在CPU响应中断 时不能自动清零,只能撤除INT0引脚的低电平,IE0才清零;当ITO=1 时,由硬件自动清除IE0标志。 (2)INT1(P3.3), 外部中断1请求信号输入引脚。当CPU检测到P3.3引脚上出现有效的中断信号时,中断标志IE1(TCON.3)置一,向CPU 申请中断,入口地址为000BH。可由IT1(TCON.2)选择其为低电平 有效还是下降沿有效,中断标志复位清零与INTO类同。 (3)TF0(TCON.5), 片内定时/计数器T0溢出中断请求标志。当定时/计数器T0发生溢出时,置位TF0,并向CPU申请中断,入口地址为0013H。 CPU响应中断时,TF0自动清零。 (4)TF1(TCON.7), 片内定时/计数器T1溢出中断请求标志。当定时/计数器T1发生溢出时,置位TF1,并向CPU申请中断,入口地址为001 BH。CPU响应中断时,TF1自动清零。 (5)RI(SCON.0)或TI(SCON.1),串行口中断请求标志。当串行口收完一帧串行数据时置位RI或当串行口发送完一帧串行数据时置位TI, 向 CPU申请中断,入口地址为0023H。RI和TI必须由软件清除。 2、某系统有三个外部中断源1、2、3,当某一中断源变低电平时便要求CPU 处理,它们的优先处理次序由高到低为3、2、1,处理程序的入口地址分别为2000H、2100H、2200H,试编写主程序及中断服务程序(转至相应的入口即可)。 答:ORG 0000H LJMP BOOT ORG 0003H LJMP INT3 ORG 000BH LJMP INT2 ORG 0013H LJMP INT1 ORG 001BH RETI BOOT:ACALL INT0_0 ;中断启动程序 ACALL T0_0 ACALL INT1_0 SETB EA SJMP $

第五章中断系统作业 1.外部中断1所对应的中断入口地址为()H。 2.对中断进行查询时,查询的中断标志位共有、__、、_和_、 __六个中断标志位。 3.在MCS-51中,需要外加电路实现中断撤除的是:() (A)定时中断(B)脉冲方式的外部中断 (C)外部串行中断(D)电平方式的外部中断 4.下列说法正确的是:() (A)同一级别的中断请求按时间的先后顺序顺序响应。() (B)同一时间同一级别的多中断请求,将形成阻塞,系统无法响应。() (C)低优先级中断请求不能中断高优先级中断请求,但是高优先级中断请求 能中断低优先级中断请求。() (D)同级中断不能嵌套。() 5.在一般情况下8051单片机允许同级中断嵌套。() 6.各中断源对应的中断服务程序的入口地址是否能任意设定?() 7.89C51单片机五个中断源中优先级是高的是外部中断0,优先级是低的是串行口中断。() 8.各中断源发出的中断申请信号,都会标记在MCS-51系统中的()中。 (A)TMOD(B)TCON/SCON(C)IE(D)IP 9.要使MCS-51能够响应定时器T1中断、串行接口中断,它的中断允许寄存器 IE的内容应是() (A)98H(B)84H(C)42(D)22H 10.编写出外部中断1为负跳沿触发的中断初始化程序。 11.什么是中断?其主要功能是什么? 12.什么是中断源?MCS-51有哪些中断源?各有什么特点? 13.什么是中断嵌套? 14.中断服务子程序与普通子程序有哪些相同和不同之处? 15.中断请求撤除的有哪三种方式? 16.特殊功能寄存器TCON有哪三大作用? 17.把教材的P82页的图4.24改为中断实现,用负跳变方式,中断0(INT0)显 18.示“L2”,中断1(INT1)显示“H3”。(可参考第四章的电子教案中的例子) 19.第5章课后作业第9题。

第五章 中断系统 5. 1 输入/输出数据的传输控制方式 一、输入/输出的一般概念 1.引言 输入/输出是微机系统与外部设备进行信息交换的过程。输入/输出设备称为外部设备,与存储器相比,外部设备有其本身的特点,存储器较为标准,而外部设备则比较复杂,性能的离散性比较大,不同的外部设备,其结构方式不同,有机械式、电动式、电子式等;输入/输出的信号类型也不相同,有数字信号,也有模拟信号;有电信号,也有非电信号;输入/输出信息的速率也相差很大。因此,CPU与外部设备之间的信息交换技术比较复杂。 CPU与外设之间的信息交换,是通过它们之间接口电路中的I/O端口来进行的,由于同一个外部设备与CPU之间所要传送的信息类型不同,方向不同,作用也不一样(例如数据信息、状态信息、控制信息、输入/输出等),所以接口电路中可以设置多个端口来分别处理这些不同的信息。 2.输入/输出端口的寻址方式 微机系统采用总线结构形式,即通过一组总线来连接组成系统的各个功能部件(包括CPU、内存、I/O端口),CPU、内存、I/O端口之间的信息交换都是通过总线来进行的,如何区分不同的内存单元和I/O 端口,是输入/输出寻址方式所要讨论解决的问题。 根据微机系统的不同,输入/输出的寻址方式通常有两种形式:(1).存储器对应的输入、输出寻址方式 这种方式又称为存储器统一编址寻址方式或存储器映象寻址方式。方法:把外设的一个端口与存储器的一个单元作同等对待,每一个I/O 端口都有一个确定的端口地址,CPU与I/O端口之间的信息交换,与存储单元的读写过程一样,内存单元与I/O端口的不同,只在于它们具有不同的的地址。 优点: ①CPU对I/O端口的读/写操作可以使用全部存储器的读/写操作指 令,也可以用对存储器的不同寻址方式来对I/O端口中的信息,直接进行算术、逻辑运算及循环、移位等操作。