第27卷第5期

遥 测 遥 控

Vol .27,№.5

2006年9月Journa l of Tele m etry,Track i n g,and Co mmand Sep te mber 2006

一种基于FPGA 的硬件开环位

同步电路设计与实现

秦文兵1, 罗来源1, 向 闻2

(1 西南电子电信技术研究所 成都 610041

2 解放军装备指挥技术学院 北京 101416)

收稿日期:2006201209 收修改稿日期:2006203229

摘 要:针对短时突发数据接收对位同步电路的要求,设计一种基于FPG A 的硬件开环位同步电路。从时序关系,状态转化等方面分析其同步过程和原理,推导其相位误差、同步建立时间、同步保持时间等主要性能参数,并在现有通用FPG A 芯片上实现完成设计方案。该同步电路完成无线数据接收中位同步从软件模块向硬件模块的转化,提高了位同步对高速数据及短时突发数据接收的适应能力,硬件测试结果验证了其正确性和有效性。

关键词:FPG A; 位同步; 相位误差

中图分类号:T N919.3 文献标识码:A 文章编号:C N11-1780(2006)05-0043-04

引 言

随着数字通信及遥测遥控技术的迅速发展和可编程芯片性能的不断提高,无线接收处理数字化、软件化应用已越来越多,对接收部分的功能(如短时突发信号接收)和速度的要求也越来越高。作为无线接收方的重要组成单元,位同步模块在无线数字传输领域里具有十分重要的作用,它直接影响到数字接收机的稳定性和可靠性。位同步是通过补偿数字基带码元频率及相位误差来达到收、发两端数字码元一致的数字处理技术,从数据信号中提取位同步信息作为无线接收系统中主要位同步方案,当前常用的有全数字化锁相环法和开环补偿同步法。开环补偿同步法具有同步时间短、设计简单、调试方便等优点,能够满足高速数据及短时突发数据传输的位同步要求,是FPG A 片上系统位同步设计中一种较好的方法。

本文针对无线高速数据及短时突发数据接收对位同步电路的要求,提出并设计了一种基于FPG A 的硬件开环位同步电路,给出该电路的FPG A 主要实现方案,从信号处理流程、时序关系、计数状态等方面介绍该方案的原理。通过一组伪随机序列对该同步电路进行了原理和功能上的仿真,分析其相位误差、同步建立时间、同步保持时间等主要性能参数。

1 硬件开环位同步电路的原理及FPG A 实现

[6][7]

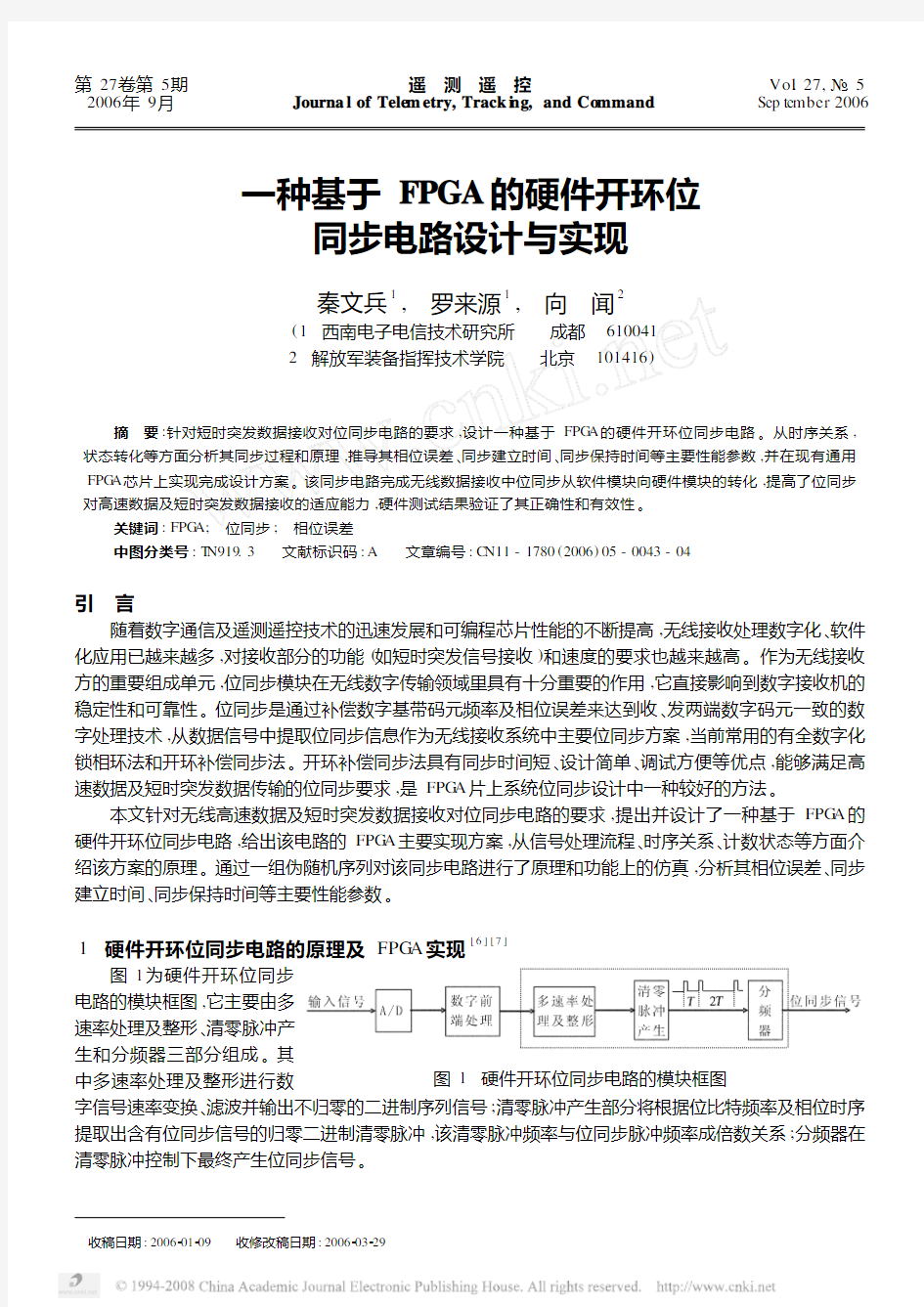

图1 硬件开环位同步电路的模块框图图1为硬件开环位同步电路的模块框图,它主要由多

速率处理及整形、清零脉冲产

生和分频器三部分组成。其

中多速率处理及整形进行数

字信号速率变换、滤波并输出不归零的二进制序列信号;清零脉冲产生部分将根据位比特频率及相位时序提取出含有位同步信号的归零二进制清零脉冲,该清零脉冲频率与位同步脉冲频率成倍数关系;分频器在清零脉冲控制下最终产生位同步信号。

图2为硬件开环位同步电路的时序图。设a,b 为发射端、接收端本地的位时钟信号,c 为硬件开环位同步产生的清零脉冲,d 为硬件开环位同步电路得到的位同步时钟。图2(a ),图2(b )为接收端位时钟频率大于和小于发射端位时钟频率情况下的时序图。

图2 硬件开环位同步电路的时序图由于位同步时钟源误差的影响,接收端位时钟

(本地时钟)、发射端位时钟频率和相位通常是不一致

的。设采用2N 方式分频,当接收端位频率大于发射端

位频率时,如图2(a )所示,清零脉冲滞后于分频器计

数归零时刻,产生的位同步信号低电平占空比略大于

高电平占空比;当接收端位频率小于发射端位频率时,如图2(b )所示,清零脉冲超前于分频器计数归零时刻,产生的位同步信号低电平占空比略小于高电平占空比。

硬件开环位同步电路是通过调整计数器的模值来补偿收、发两端的时钟频率及相位误差达到同步的。如图3所示,设计数器的模值为N ,若收、发两端时钟完全一致(理想状态),清零时刻和计数器归零时刻相同。在图3(a )中,计数器值从0到N 循环;若发射端位频率大于接收端位频率,清零时刻滞后于计数器归零时刻。在图3(b )中,计数器归零后继续计数,到清零脉冲来时重新清零计数;在图3(c )中,若发射端位频率小于接收端位频率

,清零时刻超前于计数器归零时刻,计数器将每次从0到小于N 计数。

图3 硬件开环位图同步电路计数值时序图

硬件开环位同步电路在清零时刻对由收、发端的位时钟频率误差产生的相位滑动进行补偿,而清零时刻取决于传输数据中二进制比特的分布,可合理采用随机序列作为激励源来进行理论仿真。图4为相位误差的仿真图。

从图中可以看出,硬件开环位同步电路同步速度快,能够满足突发数据接收对位同步电路的要求,其同步误差δ在一定程度上受二进制比特序列分布的影响。

图4 硬件开环位同步电路相位误差仿真图

图5是突发数据接收系统的硬件开环位同步电路FPG A 简要框图[2~4]

,它主要包含获取同步时钟及同步时钟有效两部分。该模块适合5种数据速率,输入数据总线信号为X,输出同步时钟为RCK,Rce 为同步有效信号。在有信号且正确接收解调输出时,Rce 指示有效,作为后继处理的使能和锁定指示。?44?秦文兵等,一种基于FPGA 的硬件开环位同步电路设计与实现第27卷第5期

图5 硬件开环位同步电路FPG A 实现框图

其内部信号RX1为施密特整形后的基

带数字序列,设输入驱动时钟为79.

872MHz,经DC M 倍频后输入两模值Cnt1、

Cnt2分别为39和52的分频器,Cnt1输出

256k,512k,1M ,2M 的数据时钟,分别对应

16计数器的高低4位,其后端的双比较器两

门限可设置位3和34。Cnt2输出1.536M

的数据时钟,其后端的双比较器两门限可置

3和47,见图6(a )和(b )。

该同步电路使能信号采用序惯检测方

法产生,可对没有数据接收和无效数据接收

进行输出指示,其指示的灵敏性和可靠性可

图6 硬件开环位同步电路同步、失步逻辑状态图灵活通过模值参数来调节。在锁定

计数器和失锁计数器模值均为5,无

源计数器模值为64的参数下实验测

试效果较好,这些参数可根据实际要

求进行微调。

该位同步模块在Xilinx 公司的

XC3S1000芯片中进行了设计实现,

所耗主要资源是:382个Slice,81个LUT,2个B l ock RAM 和2个全局Gclk,约占该芯片的3%;实现结果中采用了300组18比特512K 符号速率的G MSK 突发信号进行了测试。结果表明,该同步方案能在1b 保护时间内实现快速同步,验证了该方案的正确性和有效性。2 主要性能参数分析

[1][5]

2.1 相位误差θe 硬件开环位同步电路提取位同步信号时,相位误差θe 的产生受发送数据二进制序列分布的影响,因此相位误差需要从概率意义上来分析,由于在发射端通常加了交织扰码,其出现长时间二进制序列不变的概率很低。设位同步时钟周期为T b ,时钟精度为P e ,则相位误差为

θe =2

π(n -1)T b ?P e (1)式中n 为数据序列电平连续不变的码元个数。由式(1)可以看出,相位误差受传输数据二进制序列变化快慢的影响,当n =1,即在二进制序列变化得最快时,所对应的相位锁定误差最小。

2.2同步建立时间和同步保持时间

同步建立时间t s 即失去同步后重新同步所需要的时间,硬件开环位同步电路同步于清零时刻,前面已定性地分析了其同步建立时间快的优点。同步建立时间和同步误差一样受传输数据二进制序列分布的影响,仍然可从概率意义上定量分析该参数,可合理假设两相邻码元中出现01,10,11,00的概率相等,其中码元发生变化的情况占总体的一半,平均来说,每2T b 可产生一清零脉冲来调整相位,故同步建立时间为

t s =2T b

(2)同步建立后,由于收发双方的位时钟驱动源之间在一定精确范围内存在频差△F,接收端信号的相位

将逐渐发生漂移,且漂移量随时间增加不断增大,当相位漂移量达到最大值2K

π(K 为固定常数,且K ≤1)时,位同步电路又转入非同步状态,这段同步时间可近似计算如下。

设收发两端的固有位时钟频率分别为F 1=1/T 1和F 2=1/T 2,则

|T 1-T 2|=1F 1-1F 2=|F 2-F 1|F 1F 2=△F F 1F 2

(3)?

54?2006年9月遥 测 遥 控

若F 1,F 2的几何平均值为F 0,即

F 20=F 1F 2

=1/T 20(4)

代入式(3)可得T 1-T 2=△F /F 2

0](T 1-T 2)/T 0=△F /F 0(5)即每经过T 0时间,收发两端就会产生T 1-T 2时间漂移,相应相位漂移量为2

π(T 1-T 2)/T b t c

T 0=2π/k 2π(T 1-T 2)/T b (6)

由式(6)得同步保持时间t c 为

t c =T b T 0/[k (T 1-T 2)](7)

4 结束语

传统的无线数字接收系统位同步通常在DSP 、计算机程序等软件中设计实现,相比之下,硬件FPG A 位同步具有处理速度快,易于实现并行算法等优点,但同时,FPG A 硬件闭环电路编程具有灵活性比软件差、时序复杂、调试难度大等缺点。从前面的分析可知,硬件开环位同步电路能够较好地发挥FPG A 高速数据处理能力的优势,有效地降低了调试难度,适于FPG A 片上系统的同步设计。该位同步方案的应用实现了无线数字接收中位同步电路从软件模块向硬件模块的转化,大幅度提高了位同步对高速数据接收的适应能力,为无线短时突发数据信号接收的位同步提供了一种适用的硬件实现方案。

参考文献

[1] 郑继禹等.锁相环路原理与应用[M ].北京:人民邮电出版社,1976.

[2] 张顺心.数字电路与系统[M ].南京:东南大学出版社,2001.

[3] 张建军、许林、陈正霞.基于FPG A 的多模式通信信号解调及自适应位同步技术[J ].电讯技术,2005,45(1):120

~123.

[4] 孟宪元、单长虹.基于FPG A 的全数字锁相环路的设计[J 〗.电子技术应用,2001,27(9):58~60.

[5] Farrell J;Murtha J;Statistical B it Synchr onizati on in D igital Communicati ons[J ].Communicati ons,I EEE Transacti ons

on [legacy,p re -1988],1971,19(4):487~491.

[6] Takasaki Y .Op ti m izing Pulse Shap ing for Baseband D igital Trans m issi on with Self -B it Synchr onizati on[J ].Communi 2

cati ons,I EEE Transacti ons on [legacy,p re -1988],1980,28(8):164~1172.

[7] Kokkonen M ,Pietila S .A Ne w B it Synchr onizati on Method for a GPS Receiver[C ].Positi on Locati on and Navigati on

Sy mposiu m,2002I EEE,15~18,2002:85~90.

FPGA Ba sed O pen L oop Hardware B it Synchron i z i n g Cu it

Q in W enbing, Luo Laiyuan, Xiang W en

Abstract:A hard ware electr ocircuit sche me for bit synchr onizati on are designed t o met the de mands of bit synchr onizati on little par oxys mal data receiving in wireless digital syste m.The p rinci p le and p r ocess of synchr onizati on are analyzed fr om ti m e sequence and state convertsi on,and the main p r operty para meter,such as Phase Err or,Setup Ti m e and Hold Ti m e of synchr onizati on are de 2rived .And the p lan is achieved in current FPG A Chi p.The app licati on of the scheme converts s oft w are module int o hard ware mod 2ules s o that high -s peed data or little par oxys mal data trans m issi on can be achieved,the correctness and the validity are certified by the i m p le mentati on result .

Key words:FPG A (Field Pr ogrammable Gate A rray ); B it synchr onizati on; Phase err or

[作者简介]

秦文兵 1978生,在读博士研究生,研究方向为扩频信号处理,短波、超短波通信与定位等。

罗来源 1963生,高工,博士生导师,研究方向为跳频通信系统,信号辨识、阵列信号处理等。

向 闻 1981生,硕士研究生,研究方向为电子对抗,雷达信号处理,网络通信技术等。?64?秦文兵等,一种基于FPGA 的硬件开环位同步电路设计与实现第27卷第5期