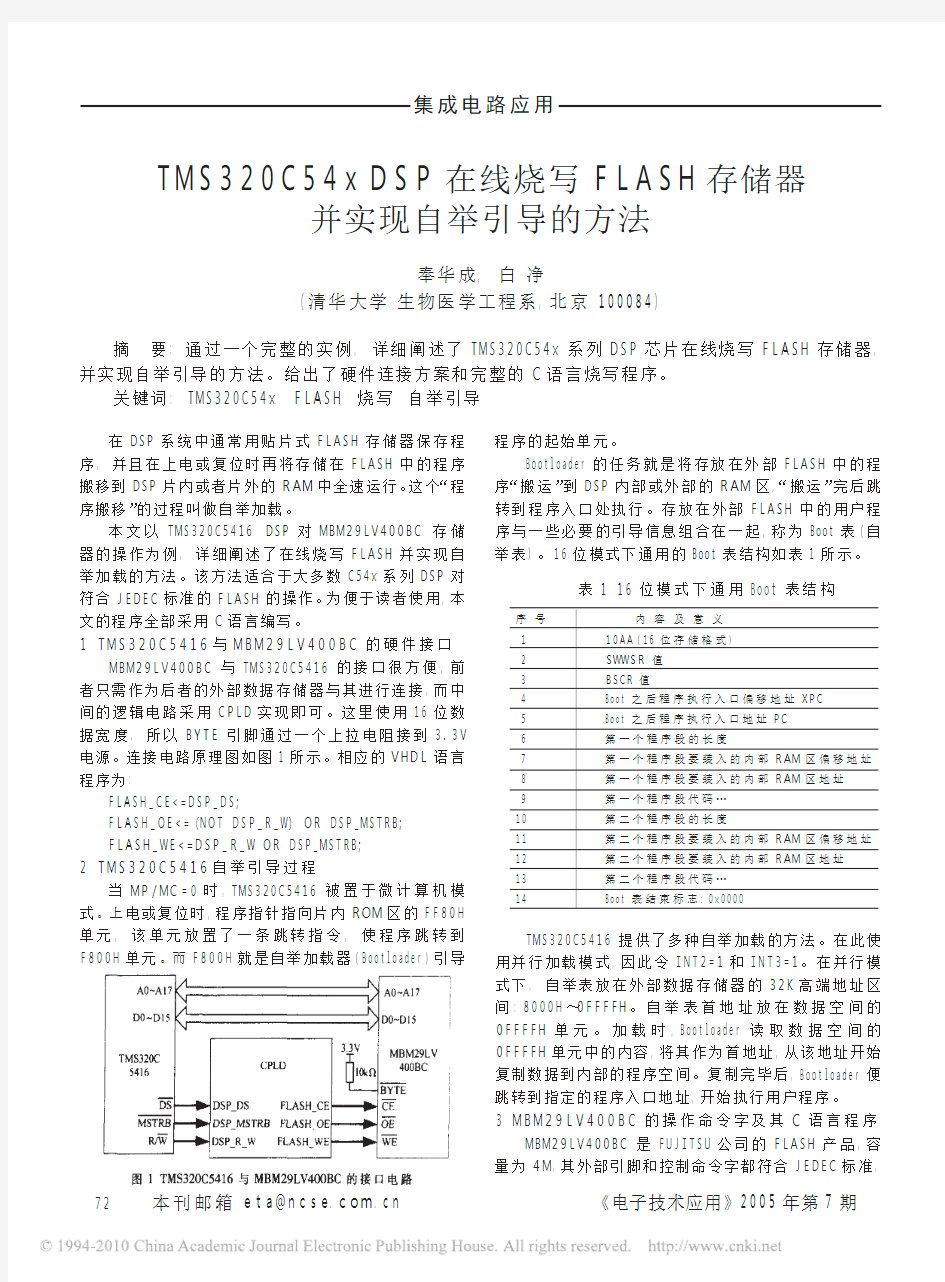

序号

内容及意义

110AA(16位存储格式)2SWWSR值3BSCR值

4Boot之后程序执行入口偏移地址XPC5Boot之后程序执行入口地址PC6第一个程序段的长度

7第一个程序段要装入的内部RAM区偏移地址8第一个程序段要装入的内部RAM区地址9第一个程序段代码…10第二个程序段的长度

11第二个程序段要装入的内部RAM区偏移地址12第二个程序段要装入的内部RAM区地址13第二个程序段代码…

14

Boot表结束标志:0x0000

表116位模式下通用Boot表结构

在DSP系统中通常用贴片式FLASH存储器保存程序,并且在上电或复位时再将存储在FLASH中的程序搬移到DSP片内或者片外的RAM中全速运行。这个“程序搬移”的过程叫做自举加载。

本文以TMS320C5416DSP对MBM29LV400BC存储器的操作为例,详细阐述了在线烧写FLASH并实现自举加载的方法。该方法适合于大多数C54x系列DSP对符合JEDEC标准的FLASH的操作。为便于读者使用,本文的程序全部采用C语言编写。

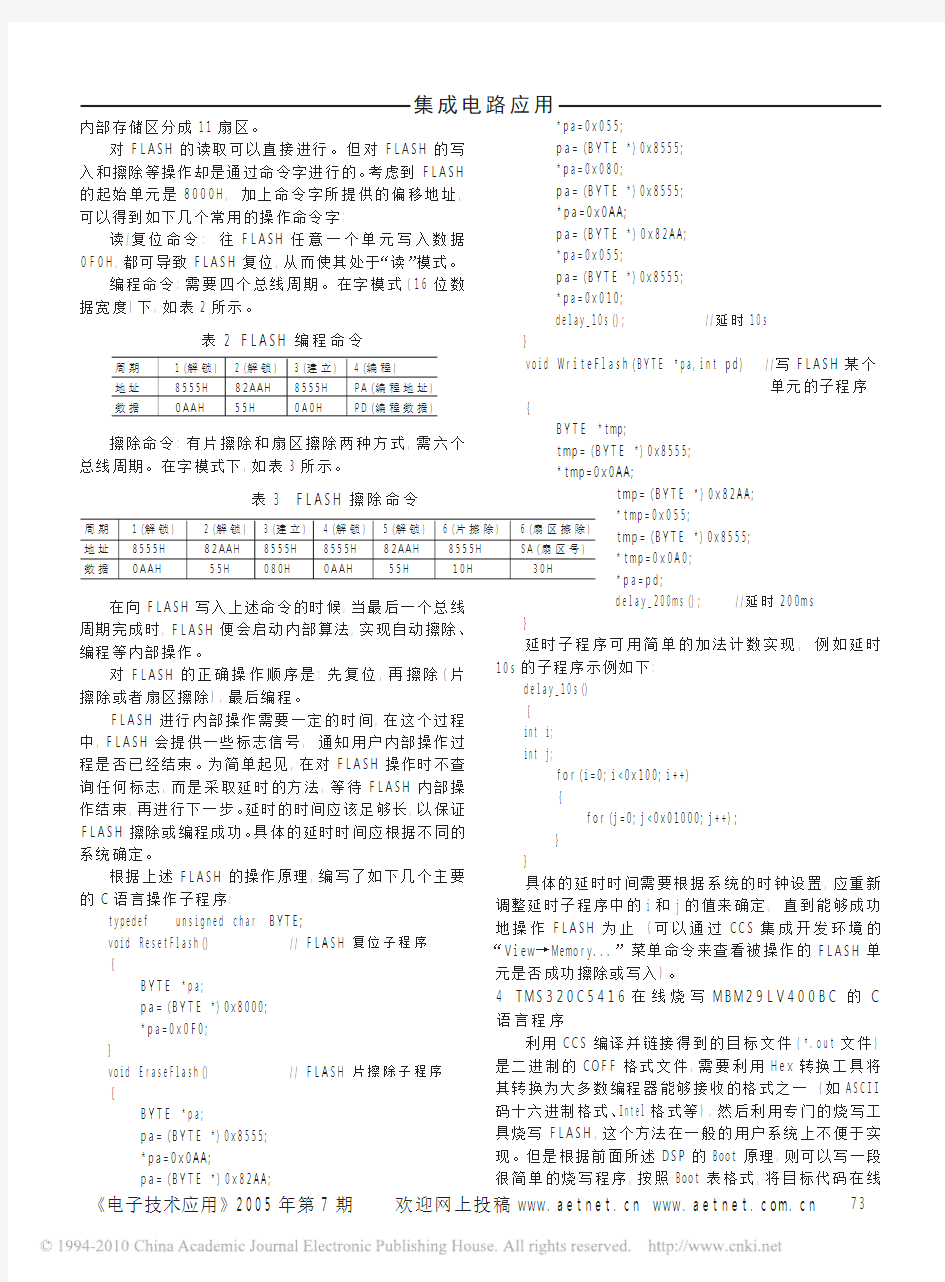

1TMS320C5416与MBM29LV400BC的硬件接口

MBM29LV400BC与TMS320C5416的接口很方便,前

者只需作为后者的外部数据存储器与其进行连接,而中间的逻辑电路采用CPLD实现即可。这里使用16位数据宽度,所以BYTE引脚通过一个上拉电阻接到3.3V电源。连接电路原理图如图1所示。相应的VHDL语言程序为:

FLASH_CE<=DSP_DS;

FLASH_OE<=(NOTDSP_R_W)ORDSP_MSTRB;FLASH_WE<=DSP_R_WORDSP_MSTRB;

2TMS320C5416自举引导过程

当MP/MC=0时,TMS320C5416被置于微计算机模式。上电或复位时,程序指针指向片内ROM区的FF80H单元,该单元放置了一条跳转指令,

使程序跳转到

F800H单元。而F800H就是自举加载器(Bootloader)引导

程序的起始单元。

Bootloader的任务就是将存放在外部FLASH中的程

序“搬运”到DSP内部或外部的RAM区,“搬运”完后跳转到程序入口处执行。存放在外部FLASH中的用户程序与一些必要的引导信息组合在一起,称为Boot表(自举表)。16位模式下通用的Boot表结构如表1所示。

TMS320C5416提供了多种自举加载的方法。在此使

用并行加载模式,因此令INT2=1和INT3=1。在并行模式下,自举表放在外部数据存储器的32K高端地址区间:8000H~0FFFFH。自举表首地址放在数据空间的

0FFFFH单元。加载时,Bootloader读取数据空间的0FFFFH单元中的内容,将其作为首地址,从该地址开始

复制数据到内部的程序空间。复制完毕后,Bootloader便

跳转到指定的程序入口地址,开始执行用户程序。

3MBM29LV400BC的操作命令字及其C语言程序

MBM29LV400BC是FUJITSU公司的FLASH产品,容量为4M,其外部引脚和控制命令字都符合JEDEC标准,

TMS320C54xDSP在线烧写FLASH存储器

并实现自举引导的方法

奉华成,白净

(清华大学生物医学工程系,北京100084)

摘

要:通过一个完整的实例,详细阐述了TMS320C54x系列DSP芯片在线烧写FLASH存储器,

并实现自举引导的方法。给出了硬件连接方案和完整的C语言烧写程序。

关键词:TMS320C54xFLASH烧写自举引导

周期1(解锁)2(解锁)3(建立)4(编程)地址8555H82AAH8555HPA(编程地址)数据

0AAH

55H

0A0H

PD(编程数据)

表2FLASH编程命令

周期1(解锁)2(解锁)3(建立)4(解锁)5(解锁)6(片擦除)6(扇区擦除)地址8555H82AAH8555H8555H82AAH8555HSA(扇区号)数据

0AAH

55H

080H

0AAH

55H

10H

30H

表3FLASH擦除命令

内部存储区分成11扇区。

对FLASH的读取可以直接进行。但对FLASH的写入和擦除等操作却是通过命令字进行的。考虑到FLASH的起始单元是8000H,加上命令字所提供的偏移地址,可以得到如下几个常用的操作命令字:

读/复位命令:往FLASH任意一个单元写入数据0F0H,都可导致FLASH复位,从而使其处于

“读”模式。编程命令:需要四个总线周期。在字模式(16位数据宽度)下,如表2所示。

擦除命令:有片擦除和扇区擦除两种方式,需六个总线周期。在字模式下,如表3所示。

在向FLASH写入上述命令的时候,当最后一个总线周期完成时,FLASH便会启动内部算法,实现自动擦除、编程等内部操作。

对FLASH的正确操作顺序是:先复位,再擦除(片擦除或者扇区擦除),最后编程。

FLASH进行内部操作需要一定的时间,在这个过程中,FLASH会提供一些标志信号,通知用户内部操作过程是否已经结束。为简单起见,在对FLASH操作时不查

询任何标志,而是采取延时的方法,等待FLASH内部操作结束,再进行下一步。延时的时间应该足够长,以保证FLASH擦除或编程成功。具体的延时时间应根据不同的系统确定。

根据上述FLASH的操作原理,编写了如下几个主要的C语言操作子程序:

typedefunsignedcharBYTE;

voidResetFlash()

//FLASH复位子程序

{

BYTE*pa;

pa=(BYTE*)0x8000;*pa=0x0F0;}

voidEraseFlash()//FLASH片擦除子程序

{

BYTE*pa;

pa=(BYTE*)0x8555;*pa=0x0AA;

pa=(BYTE*)0x82AA;

*pa=0x055;

pa=(BYTE*)0x8555;*pa=0x080;

pa=(BYTE*)0x8555;*pa=0x0AA;

pa=(BYTE*)0x82AA;*pa=0x055;

pa=(BYTE*)0x8555;*pa=0x010;delay_10s();//延时10s

}

voidWriteFlash(BYTE*pa,intpd)

//写FLASH某个

单元的子程序

{

BYTE*tmp;

tmp=(BYTE*)0x8555;*tmp=0x0AA;

tmp=(BYTE*)0x82AA;

*tmp=0x055;

tmp=(BYTE*)0x8555;*tmp=0x0A0;*pa=pd;delay_200ms();

//延时200ms

}

延时子程序可用简单的加法计数实现,例如延时

10s的子程序示例如下:

delay_10s(){inti;intj;

for(i=0;i<0x100;i++){

for(j=0;j<0x01000;j++);}}

具体的延时时间需要根据系统的时钟设置,应重新调整延时子程序中的i和j的值来确定,直到能够成功地操作FLASH为止(可以通过CCS集成开发环境的“View→Memory...”菜单命令来查看被操作的FLASH单元是否成功擦除或写入)。

4TMS320C5416在线烧写MBM29LV400BC的C

语言程序

利用CCS编译并链接得到的目标文件(*.out文件)是二进制的COFF格式文件,需要利用Hex转换工具将其转换为大多数编程器能够接收的格式之一(如ASCII码十六进制格式、Intel格式等),然后利用专门的烧写工具烧写FLASH,这个方法在一般的用户系统上不便于实现。但是根据前面所述DSP的Boot原理,则可以写一段很简单的烧写程序,按照Boot表格式,将目标代码在线

烧写进FLASH。

现在用一个实际的例子来说明在线烧写的过程。具体过程如下:

建立两个独立的工程文件:MyProject.pjt和FlashBurn.pjt。前者生成的目标文件就是要烧入到FLASH中的用户程序,后者则用来实现烧入过程。MyProject.pjt有两个程序段:第一段是“.text”段,位于0x1000开始的单元,长度为0x2e。它用中断的方法实现LED灯的闪烁;第二段为“.VECTORS”段,位于0x0080开始的单元,长度为0x0078。它实现中断向量表的重新映射。程序执行入口地址也在0x1000单元。烧写时只需烧写用户程序的已初始化段(代码或数据表)。用户程序各段的起始单元及其长度可以参考该工程编译链接后所生成的.map文件(如本例的MyProject.map),这是编写烧写程序的依据。

烧写工程文件FlashBurn.pjt只有一个程序段,定位在0x7000开始的存储区(注意不要与MyProject.pjt所占的程序空间有重叠),并将其_c_int00直接定位到该区域。

用户程序拟烧写到外部FLASH的0x8000开始的存储区。

两个工程建立并且编译完毕后,在CCS中先打开MyProject.pjt工程文件,用“File→LoadProgram...”菜单命令下载用户程序目标代码MyProject.out;再打开FlashBurn.pjt工程文件,下载FlashBurn.out,运行FlashBurn.out,即可将MyProject.out代码及其Boot引导信息写入到FLASH中。

脱离仿真器,令MP/MC=0,上电复位,即可实现自举加载并自动运行。

本例的烧写工程文件FlashBurn.pjt的C语言主程序如下:

typedefunsignedcharBYTE;

voidmain()

{

BYTE*FlashPtr;//指向FLASH的指针

intFlashData;//写往FLASH的数据

inti;

BYTE*OriMem;//代码在片内RAM的源地址

intiDatalen;//代码段长度

ResetFlash();//复位FLASH

EraseFlash();//整片擦除FLASH

//开始烧写FLASH,下面为Boot表引导信息

FlashPtr=(BYTE*)0x8000;

FlashData=0x10AA;//16位存储器格式

WriteFlash(FlashPtr++,FlashData);

FlashData=0x7FFF;//置SWWSR初始化值

WriteFlash(FlashPtr++,FlashData);

FlashData=0x0F800;//置BSCR初始化值

WriteFlash(FlashPtr++,FlashData);

FlashData=0x0000;//程序执行入口偏移地址XPC

WriteFlash(FlashPtr++,FlashData);

FlashData=0x1000;//程序执行入口地址PC

WriteFlash(FlashPtr++,FlashData);

FlashData=0x002e;//第一个程序段的长度

WriteFlash(FlashPtr++,FlashData);

FlashData=0x0000;//第一个程序段要装入的内部

RAM区偏移地址

WriteFlash(FlashPtr++,FlashData);

FlashData=0x1000;//第一个程序段要装入的内部

RAM区地址

WriteFlash(FlashPtr++,FlashData);

//开始烧写第一段程序

OriMem=(BYTE*)0x1000;//第一段程序首地址

iDatalen=0x002e;//第一段程序长度

for(i=0;i<iDatalen;i++)

{

FlashData=*OriMem++;

WriteFlash(FlashPtr++,FlashData);

}

//第二段程序(中断向量表)Boot引导信息

FlashData=0x0078;//第二个程序段的长度

WriteFlash(FlashPtr++,FlashData);

FlashData=0x0000;//第二个程序段要装入的

内部RAM区偏移地址WriteFlash(FlashPtr++,FlashData);

FlashData=0x0080;//第二个程序段要装入的

内部RAM区地址WriteFlash(FlashPtr++,FlashData);

//开始烧写第二段程序(中断向量表)

OriMem=(BYTE*)0x080;//第二段程序首地址

iDatalen=0x0078;//第二段程序长度

for(i=0;i<iDatalen;i++)

{

FlashData=*OriMem++;

WriteFlash(FlashPtr++,FlashData);

}

//程序烧写结束,写入Boot表结束标志

FlashData=0x0000;//引导表结束标志

WriteFlash(FlashPtr,FlashData);

//在数据空间0xFFFF写入引导表起始地址

FlashPtr=(BYTE*)0x0FFFF;

FlashData=0x8000;

WriteFlash(FlashPtr,FlashData);

for(;;);//FLASH烧写完毕

}

本文所叙述的方法简单方便,无需考虑FLASH的存储格式。如果要烧写其它用户程序,只需修改FlashBurn.pjt中有关用户程序的起始地址、代码段长度等参数即可,因此通用性较好。文中所提供的程序已全部经过调试,能够成功运行。

(下转第77页)

(上接第74页)参考文献

1TMS320C54xDSPReferenceSetVolume4:ApplicationGuide(SPRU173).TexasInstrumentsIncorporated,October,19962ApplicationReport:SPRA602E.TexasInstrumentsIncorporated,April,2004

3MBM29LV400BCFlashMemoryDataSheet.JAPAN:Fujitsu

Limited,1998

4张勇.C/C++语言硬件程序设计-基于TMS320C5000系

列DSP(第一版).西安:西安电子科技大学出版社,2003

5唐冰.TMS320C5410烧写FLASH实现并行自举引导.单片

机与嵌入式系统应用,2003(4)

(收稿日期:2004-09-25

)

分别送到三个不同颜色的发光二极管进行报警显示。

2.4时钟分频电路

时钟分频电路的功能是将系统提供的主时钟进行分频,提供其它模块电路所需的两个时钟(1kHz和8Hz)。其中,周期计数器的时钟(clk1)决定了周期计数器的位数。当心率测量范围为20~200跳/分钟时,对应的心率周期

T为3~0.3秒。若时钟信号clk1的频率f0=1kHz,则在最

低心率(20跳/分钟)时的计数值N=3/10-3=3000,因此计数器的位数为12位。由下面的性能评价指标分析可知,更高的时钟频率可扩大心率测量范围并提高测量分辨率,但同时会增加电路的复杂性;而报警控制电路的时钟

(clk2)决定了显示闪烁的快慢。在FPGA中,时钟分频电路

一般是通过VHDL语言的进程语句由计数器实现的。

3性能评价指标

心率计性能评价指标主要包括测量误差和分辨率。由表1可知,由于计数值N的边界取值对应于相邻两个心率值的中点,故在20~200跳/分钟范围内测量的每一个显示心率值的误差都为0.5跳/分钟。最大相对误差

(用百分比表示)如图5所示。相对误差的最大值发生在

最低心率20跳/分钟处,随着心率值的增加,相对误差

减小。当心率值大于或等于50跳/分钟时,相对误差小于1%,而当心率值大于100跳/分钟时,相对误差小于

0.5%。

另一个性能指标是仪器的分辨率。由瞬时心率

IHR=6×104/N和表1可知,当周期计数值N较小时,N

变化一个单位(增大或减小1)对应瞬时心率变化比较大。因此,高心率处的分辨率较差,而低心率处的分辨率较好。在瞬时心率接近200跳/分钟时,N值很小,分辨率为1跳/分钟;在较低的瞬时心率时,分辨率小于1跳/分钟。

如果将时钟频率提高到8kHz,同时将周期计数器的位数提高到16位,分辨率将会大幅提高。此时,在瞬时心率接近200跳/分钟处,分辨率会小于0.1跳/分钟,而在瞬时心率较低处,分辨率将进一步变好。因此,在20~200跳/分钟的心率范围内,可以0.1跳/分钟的分辨率显示所有心率。不过,将周期计数器从12位提高到16位会增加电路的复杂性。另外,在实际心率测量中,人们习惯1跳/分钟的分辨率,更高的分辨率没有必要。

基于FPGA的数字心率计测量精度高,测量范围宽,在20~200跳/分钟的测量范围内,最大误差为2.5%,而当心率大于50跳/分钟时,误差小于1%,而且它的工作稳定性和可靠性好、功耗低、不需要电路参数校正和灵敏度调节,能够测量瞬时心率和平均心率,并具有心率异常报警功能。因此,与文献中报道的其它心率计相比,具有更好的性能。参考文献

1赵葆华.新型瞬时和平均两用数字心率计的研制.上海生

物医学工程,2000(4)

2I.A.Dotsynskyetal.ADigitalHeart-rateMeterUsinganE.P.R.O.M.Converter.Med.&Biol.Eng.&Comput,July,1980;18:481~

4823N.C.Voulgaris,A.A.Bailas.DigitalBeat-to-beatHeart-rateMeter.Med.&Biol.Eng.&Comput.Mar.1984:181~1834A.K.Gorge,A.E.Marble.DigitalHeart-rateMeterUsingC.M.O.S.Devices.Med.&Biol.Eng.&Comput.,July,1981;(19):517~520

5王毅,樊兆勋.便捷式数字心率计.中国医疗器械,1989(1)6梁延超.电桥传感器式数字心率计.现代医学仪器与应用,1995(3)

7白玉山,林默君.单片机心率计的设计.福建医学院学报,1995(2)

8李广军,孟宪元.可编程ASIC设计及应用.成都:电子科技

大学出版社,2003(1)

(收稿日期:2004-10-26)

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

实验一存储器实验 1.FPGA中LPM_ROM定制与读出实验 一.实验目的 1、掌握FPGA中lpm_ROM的设置,作为只读存储器ROM的工作特性与配置方法。 2、用文本编辑器编辑mif文件配置ROM,学习将程序代码以mif格式文件加载于 lpm_ROM中; 3、在初始化存储器编辑窗口编辑mif文件配置ROM; 4、验证FPGA中mega_lpm_ROM的功能。 二.实验原理 ALTERA的FPGA中有许多可调用的LPM (Library Parameterized Modules)参数化的模块库,可构成如lpm_rom、lpm_ram_io、lpm_fifo、lpm_ram_dq的存储器结构。CPU 中的重要部件,如RAM、ROM可直接调用她们构成,因此在FPGA中利用嵌入式阵列块EAB 可以构成各种结构的存储器,lpm_ROM就是其中的一种。lpm_ROM有5组信号:地址信号address[ ]、数据信号q[ ]、时钟信号inclock、outclock、允许信号memenable,其参数都就是可以设定的。由于ROM就是只读存储器,所以它的数据口就是单向的输出端口,ROM中的数据就是在对FPGA现场配置时,通过配置文件一起写入存储单元的。图3-1-1中的lpm_ROM有3组信号:inclk——输入时钟脉冲;q[23、、0]——lpm_ROM的24位数据输出端;a[5、、0]——lpm_ROM的6位读出地址。 实验中主要应掌握以下三方面的内容: ⑴ lpm_ROM的参数设置; ⑵ lpm_ROM中数据的写入,即LPM_FILE初始化文件的编写; ⑶lpm_ROM的实际应用,在GW48_CP+实验台上的调试方法。 三.实验步骤 (1)用图形编辑,进入mega_lpm元件库,调用lpm_rom元件,设置地址总线宽度address[] 与数据总线宽度q[],分别为6位与24位,并添加输入输出引脚,如图3-1-1设置与连接。 (2)设置图3-1-1为工程。 (3)在设置lpm_rom数据参数选择项lpm_file的对应窗口中(图3-1-2),用键盘输入 lpm_ROM配置文件的路径(rom_a、mif),然后设置在系统ROM/RAM读写允许,以便能

基于March C-算法的单片机存储器测试 作者:于文考高成张栋 来源:《现代电子技术》2010年第06期 摘要:为了保证单片机系统的可靠性,对单片机内嵌存储器的测试显得尤为重要。根据MCS-51系列单片机系统内嵌存储器的结构特点和故障模型,研究了测试算法的选择、数据背景的产生等问题,首次提出将March C-算法用于单片机内嵌存储器的用户级测试程序编写。该测试程序对SAF,TF,AF,CF的故障覆盖率可达到100%,并且能够检测部分NPSF故障,具有较高的故障覆盖率,适合于对用户级MCS-51系列单片机存储器的测试。 关键词:单片机;March C-算法;存储器测试;故障覆盖率 中图分类号:TP333文献标识码:B 文章编号:1004-373X(2010)06-019-03 Test of Single Chip Microcomputer′s Memory Based on March C- Algorithm YU Wenkao,GAO Cheng,ZHANG Dong (Beihang University,Beijing,100191,China) Abstract:In order to ensure thereliability of single chip microcomputer system,test of the single chip microcomputer embedded memory is particularly important.In accordance with characteristics and fault model of MCS-51 embedded memory,selection of the test algorithm and the data background are researched,and the test program which based on March C- algorithm for MCS-51 single chip microcomputer embedded memory for the first time in user-level is presented.The test program can reach all of the SAF,TF,AF,CF failure and some of NPSF failure,has a high fault coverage,suitable for test of MCS-51 single chip microcomputer embedded memory in user-level. Keywords:single chip microcomputer;March C- algorithm;memory test;fault coverage 0 引言 存储器是单片机系统中的重要组成部分,其功能的正确性直接影响到单片机的可靠性。因此,为了保证单片机系统的可靠性,对单片机内嵌存储器的功能测试尤为重要。针对单片机内嵌存储器的结构特点,在详细分析嵌入式存储器故障模型的基础上,合理选择测试算法和数据背景,采用面向位与面向字节相结合的March C-算法,实现了基于March C-算法的单片机内嵌存储器测试。 1 存储器的故障模型

JToolpad代码生成工具使用说明文档 本文档是使大家能正确使用JToolpad工具,从而缩短开发时间,简化开发流程,生成规范且正确的代码。 1.打开JToolpad 如果本机有此工具则在开始菜单->所有程序中打开即可,若本机没有此程序,则可在局域网内找到,http://192.168.60.21/jtoolpad/ 点击链接即可打开工具。主界面如下:

打开已经编译好的pdm文件,即可导入数据结构

3配置属性 选择菜单中的模型选项,打开属性即可弹出如下对话框 1.应用代码:暂时无具体意义 2.Sysframework基本包名:是工具包的存放路径,随项目变化会相应的发生变化 3.应用基准包名:是具体的应用包的名称,比如上面的这个包platfrom下就会是具体的dto, web,service等 4.Java源代码目录:是具体的Java代码存放位置,此相必须指向component文件夹,在 component文件夹下就是相应的应用基准包名目录,如:component\com\ chinainsurance\application\platform\..... 5.Web应用根目录:是具体的web发布页面的存放位置,此项必须指向webapps文件夹, 在此文件夹下是具体的web发布路径。 配置好以上路径后确定即可。 注意:此项路径必须指向实际开发路径不能指向临时文件夹或备份文件夹。应为部分代码的生成是基于某些已经存在的文件而生成的,这点切记! 4生成代码方法 生成代码有两种方式: 第一种就是选择所需要的一个或多个表生成部分文件:方法是打开Tables的下来菜单,选中需要的一个或多个,在选中的这些表上点击右键,选择要生成的部分即可。

本技术公开了一种存储器测试方法,包括以下步骤:激活操作系统,令系统进入存储器测试的保护模式;在存储器中创建一地址转换页表;判断待测存储器的物理地址空间是否超过 4GB;若是,激活地址转换页表,将系统给定的32位线性地址转换为与存储器的实际物理地址相对应,并在系统中央处理器的控制下,依照地址转换页表查询和访问存储器的实际物理地址,且执行存储器检测算法进行存储器测试;若不是,则在系统中央处理器的控制下,直接访问与系统的32位线性地址相对应的存储器的实际物理地址,并执行存储器检测算法进行存储器测试。采用本技术可以访问和测试4GB以上存储器地址空间的问题及缺陷,从而在提 高了存储器测试范围的同时节约了测试成本。

技术要求 1、一种存储器测试方法,应用于使用英特尔中央处理器的计算机服务器 系统或个人微电脑系统中的存储器检测过程,其特征在于,该方法包括以下步骤: 激活操作系统,并令系统进入存储器测试的保护模式; 在存储器中创建一地址转换页表结构,用以在后续步骤中将系统给定的 32位线性地址转换成具有4GB以上物理地址空间的存储器的物理地址; 判断所测试的存储器的物理地址空间是否超过4GB; 如超过4GB,则激活所述地址转换页表结构,将系统给定的32位线性地 址转换为与所述存储器的实际物理地址相对应,并在系统中央处理器的控制下,依据该地址转换页表查询和访问所述存储器的实际物理地址,且执行存储器检测算法对该存储器进行测试,并且在完成对所述存储器的实际物理地址的访问及存储器测试后,关闭该地址转换页表结构;以及 如未超过4GB,则不激活所述地址转换页表结构,而在所述系统中央处理 器的控制下,直接访问与系统给定的32位线性地址相对应的所述存储器的实际物理地址,并执行存储器检测算法对该存储器进行测试。 2、根据权利要求1所述的方法,其特征在于,所述地址转换页表结构是 基于Intel公司提供的物理地址扩展/页扩展技术而构建的。 3、根据权利要求2所述的方法,其特征在于,进一步包括如下步骤: 在存储器的控制缓存器CR3中装载一具有两级页表结构的页映像表; 在存储器的控制缓存器CR4中设定所述线性地址第5位支持所述物理地址 扩展功能,并设定该线性地址第4位的偏移大小;以及

实验一存储器实验 1.FPGA中LPM_ROM定制与读出实验 一.实验目的 1、掌握FPGA中lpm_ROM的设置,作为只读存储器ROM的工作特性和配置方法。 2、用文本编辑器编辑mif文件配置ROM,学习将程序代码以mif格式文件加载于 lpm_ROM中; 3、在初始化存储器编辑窗口编辑mif文件配置ROM; 4、验证FPGA中mega_lpm_ROM的功能。 二.实验原理 ALTERA的FPGA中有许多可调用的LPM (Library Parameterized Modules)参数化的模块库,可构成如lpm_rom、lpm_ram_io、lpm_fifo、lpm_ram_dq的存储器结构。CPU中的重要部件,如RAM、ROM可直接调用他们构成,因此在FPGA中利用嵌入式阵列块EAB可以构成各种结构的存储器,lpm_ROM是其中的一种。 lpm_ROM有5组信号:地址信号address[ ]、数据信号q[ ]、时钟信号inclock、outclock、允许信号memenable,其参数都是可以设定的。由于ROM是只读存储器,所以它的数据口是单向的输出端口,ROM中的数据是在对FPGA现场配置时,通过配置文件一起写入存储单元的。图3-1-1中的lpm_ROM有3组信号:inclk——输入时钟脉冲;q[23..0]——lpm_ROM的24位数据输出端;a[5..0]——lpm_ROM的6位读出地址。 实验中主要应掌握以下三方面的内容: ⑴lpm_ROM的参数设置; ⑵lpm_ROM中数据的写入,即LPM_FILE初始化文件的编写;

⑶lpm_ROM的实际应用,在GW48_CP+实验台上的调试方法。 三.实验步骤 (1)用图形编辑,进入mega_lpm元件库,调用lpm_rom元件,设置地址总线宽度address[]和数据总线宽度q[],分别为6位和24位,并添加输入输出引脚,如图3-1-1设置和连接。 (2)设置图3-1-1为工程。 (3)在设置lpm_rom数据参数选择项lpm_file的对应窗口中(图3-1-2),用键盘输入lpm_ROM配置文件的路径(rom_a.mif),然后设置在系统ROM/RAM读写允许,以便能对FPGA中的ROM在系统读写。 (4) 用初始化存储器编辑窗口编辑lpm_ROM配置文件(文件名.mif)。这里预先给出后 面将要用到的微程序文件:rom_a.mif 。rom_a.mif中的数据是微指令码(图3-1-3)。 (5)全程编译。 (6)下载SOF文件至FPGA,改变lpm_ROM的地址a[5..0],外加读脉冲,通过实验台上的数码管比较读出的数据是否与初始化数据(rom_a.mif中的数据)一致。 注:下载sof示例文件至实验台上的FPGA,选择实验电路模式仍为NO.0,24位数据输出由数码8至数码3显示,6位地址由键2、键1输入,键1负责低4位,地址锁存时钟CLK由键8控制,每一次上升沿,将地址锁入,数码管8/7/6/5/4/3将显示ROM 中输出的数据。发光管8至1显示输入的6位地址值。

龙源期刊网 https://www.doczj.com/doc/1918012482.html, 存储器测试算法及诊断覆盖率研究 作者:陈金鸿谢亚莲 来源:《企业技术开发·下旬刊》2014年第04期 摘要:随着微电子技术的快速进步,半导体集成电路高速发展,新的存储器测试技术也 不断更新。文章描述了存储器的经典测试算法运算过程,并分析了其原理。在研究经典测试算法的基础上,吸收经典算法的思想,比较各种不同算法的优缺点,改进测试算法,以便在实际检测中能够减少测试所需要的时间,提高故障诊断覆盖率,达到比较满意的测试效果。 关键词:存储器;测试算法;诊断覆盖率 中图分类号:TP333.8 文献标识码:A 文章编号:1006-8937(2014)12-0009-02 存储器测试技术是一直不断更新的技术,随着存储器在市场上的需求日益增加,每一种新存储器技术的出现都会引起广泛的关注,往往新技术的出现都对实际测试工作造成巨大的改变。而面对越来越大的存储器市场,生产商对于存储器功能安全越来越重视,寻找高效的测试算法一直是存储器测试过程中需要解决的问题。 1 存储器测试算法 对于存储器的测试,目前有许多种测试算法,有使用时间长久的经典算法,也有近些年运用广泛的新型算法,它们都各有特点。 现主要的算法有MSCAN算法(全“0”全“1”算法)、Checkerboard算法(棋盘法)、Gallop算法(奔跳法)、March算法等。一种实用有效的测试算法,能够花费较少的时间和操作程序,更全面的检测出存储器故障。 1.1 MSCAN算法(全“0”全“1”算法) 对所有单元写“1”,再读取所有单元,进行对比。对所有单元写“0”,再读取所有单元,进行对比。算法表达式:{■(w0);■(r0);■(w1);■(r1)}。算法的执行方式可以如下: ①从检测起始点,沿着地址递增的方向将所有存储单元写“0”;②从检测起始点,沿着地址递增的方向读出所有存储单元的值“0”;③从检测起始点,沿着地址递增的方向将所有存储单元写“1”;④从检测起始点,按照地址递增的方向读出所有储存单元的值“1”。 可编程为: For I=1 to n;Do

馆藏架位号批量更新工具V1.0 使用说明书 大连网信软件有限公司

目录 一、软件介绍 (1) 1、软件简介 (1) 2、运行环境 (1) 二、软件配置 (1) 此程序运行时需要访问数据库,因此需要首先正确配置数据库连接才能正常使用。 (1) 1、数据库连接配置 (1) 2、规则表维护 (2) 3、字典表维护 (2) 三、功能说明 (2) 1、导入数据 (2) 2、数据清空 (3) 3、更新至妙思数据库 (3) 4、导出文件 (4) 5、规则维护 (4) 6、字典维护 (5) 7、日志记录 (6) 四、常见问题 (6) 1、如何手工修改,或录入规范有效的导入文档 (6) 2、如何替换文本文档中的制表符 (6)

一、软件介绍 1、软件简介 随着RFID技术在图书馆的应用,使得图书馆馆藏图书的物理位置的揭示成为可能,本软件通过于图书盘点仪器输出的文本文件进行批量处理,获取某复本的条形码及对应的物理架位信息,通过本软件更新至妙思文献管理集成系统V6.5的馆藏库,这样读者在WWW检索系统就能检索到该复本的实际物理位置的架位号信息。 2、运行环境 本程序基于.Net Framework4.0开发,运行在Windows XP及更高版本的操作系统。作为妙思文献管理集成系统V6.5的一部分,需要连接妙思文献管理集成系统V6.5数据库配合使用。 二、软件配置 此程序运行时需要访问数据库,因此需要首先正确配置数据库连接才能正常使用。 1、数据库连接配置 1)在程序目录下使用记事本打开“BookShelfCode.exe.config”文件显示如下: 解释: ●Data Source=192.168.0.48; //数据库地址 ●Initial Catalog=顺德学院; //数据库名称 ●User ID=sa; //登录用户名 ●Password=1//登录密码

Vol.45No.4 740 计算机与数字工程 Computer /Digital Engineering总第330期 2017年第4期存储器测试图形算法概述$ 罗晶杨士宁石雪梅 (航天科工防御技术研究试验中心北京100854) 摘要存储器的高集成度化、高速化,为存储器测试带来了极大挑战。论文介绍了存储器测试图形的原理和发展,基于传统的存储器测试图形,综合描述了目前国内外几种较为新颖的且可用于实际工业生产的存储器测试图形改进算法。 关键词存储器测试;测试图形&改进的齐步算法 中图分类号TP391 DO# 10.3969/j.issn1672-9722. 2017. 04.031 Summary of Test Pattern Algorithm for Memory LUO Jing YANG Shining SHI Xuemei (Institute201 of the Second Academy of China Aerospace Science/Industry Corp,Beijing100854) Abstract tt brings big challenge to the testing of semiconductor memory with the development of its high integration and speed.The principle and development of test pattern for memory are introduced.Ameliorated test pattern for memory used in industry manufacture based on traditional test pattern for memory is described synthetically at present. Key Words memory test,test pattern,improved march pattern algorithm Class Number TP391 1引言 随着集成电路制造工艺的不断进步,半导体芯 片的发展趋于高密度、高速度、高复杂度,给测试带 来了极大的挑战[1]。存储器是集成电路产品中的 一个主要门类,主要用来存放数据、指令、程序等信 息。存储器的测试一方面可用于判断产品质量是 否合格,另一方面通过测试获得一些数据用于改进 工艺[2]。 目前存储器的基本测试方法已经比较成熟,主 要有存储器直接存取测试、存储器的宏测试、存储 器内建自测试三种,各有利弊。存储器直接存取测 试是利用自动测试设备来进行测试,自动测试设备 的性能和测试成本使得直接存取测试方式对大容 量的存储器并不合适。存储器的宏测试将存储器 作为一个宏模块,利用电路内部的扫描路径生成宏 模块的测试向量,再通过自动测试设备在电路外部施加测试矢量,对于较大的存储器,宏测试向量的 数据量较大,测试需要较长时间。存储器内建自测 试是在存储器外围产生一整套控制电路,实现芯片 内置存储器测试模式的自动产生及测试结果的自 动判别,这种方法增加芯片的面积,但是具有自动化程度 、量 、、等优势(]。 对于存储器来说,最主要的测试是读写逻辑功 能测试,以检测存储单元的故障,包括由于坏的金 属连接、坏的元件、芯片逻辑错误等原因引起的功 能故障。这些故障通常被简化为几个较为成熟的 故障模型,通过不同的测试图形算法来检测故障。 本文以存储器的测试图形为切入点,先简单介 绍存储器简化的故障模型,然后介绍常用的存储器 测试图形算法以及一些新近提出的改进存储器测 试图形算法,对其进行比较,并对将来存储器测试 图形的发展进行预期。 收稿日期:2016年10月8日,修回日期:2016年11月25日 作者简介:罗晶,女,硕士,助理工程师,研究方向:元器件测试。杨士宁,男,硕士,工程师,研究方向:元器件测试。石雪梅,女,硕士,工程师,研究方向:元器件测试。

FLASH烧写程序方法: 1、将要烧写的程序例如TIMER调通可以在线(用仿真器)下载。注意其source文件 中一定要包含boot.asm程序(见附件) 其cmd文件设置如下:主要修改其L2的长度为8000 *---------timer1.cmd--------- MEMORY { L1 : o = 0h l = 0x400 L2 : o = 00000400h l = 00008000h /* not all SRAM */ } SECTIONS { .boot_load > L1 .cinit > L2 .text > L2 .stack > L2 .bss > L2 .const > L2 .data > L2 .far > L2 .switch > L2 .sysmem > L2 .tables > L2 .cio > L2 } 2、查看TIMER程序的map文件,根据map文件中各段的地址和长度修改FLASH_PRG 程序(见附件)中flash_timer.h文件中的各段地址和长度如下: /* 程序入口点 */ #define ENTRY_POINT 0x000015a0 /* boot段的长度和RAM中地址设定 */ #define BOOT_SECTION_SIZE 0x00000400 #define BOOT_SECTION_ADDRESS 0x00000000 /* cinit段的长度和RAM中地址设定 */ #define CINIT_SECTION_SIZE 0x00001000 #define CINIT_SECTION_ADDRESS 0x00001820 /* text段的长度和RAM中地址设定 */ #define TEXT_SECTION_SIZE 0x00001420 #define TEXT_SECTION_ADDRESS 0x00000400 /* end of table */

网络存储测试方案 一.目前主流网络存储设备厂商及其主要产品的特点及主要性能指标主流厂商: EMC,IBM,HDS,Netapp等。 EMC 目前EMC产品存储方面主要涵盖:NAS、SAN、云计算等方面。主要产品有: EMC Atmos 集全球规模的存储能力与云体系结构的优势于一身,提供能够满足企业和服务提供商需求的解决方案。 EMC isilon 针对大数据的强大横向扩展NAS 解决方案,不管规模如何,其安装、管理和扩展都很简单。 EMC Symmetrix 10K/20K/40K 这系列三个产品从经济性到高性能均覆盖到,其中 10K:最经济划算的多控制器阵列,专门针对高性能和高效率而设计,适合在虚拟环境中整合应用程序。 20K:专门针对高要求虚拟数据中心环境的性能、整合和自动化需求而打造。 40K:专为混合云环境打造,提供了业界最高级别的整合、性能和可扩展性。 EMC VNX 高性能统一存储,具有无与伦比的简洁性和高效性,针对虚拟应用程序而优化。 IBM IBM TotalStorage DS8870 提供高达 3 倍的性能提升,以实现更快的事务处理速度和实时分析 凭借与IBM 企业级服务器集成的完全硬件冗余的先进业务持续性解决方案,提供卓越的系统可用性 凭借 5 代IBM? System Storage? Easy Tier? 功能和其他先进的自我调整功能,优化性能和成本目标 扩展至高达 1 TB 的系统缓存和高达 2 PB 的容量 通过出色的可扩展性、自我优化、驱动器分层和对广泛工作负载的支持实现整合 IBM XIV 存储系统 针对极致的易用性和运营敏捷性设计的久经考验的创新性高端磁盘存储系统热点、始终如一的高性能,以及通过网格架构实现的大规模并行处理 适用于优化的云与虚拟环境的虚拟化存储资源 通过完全冗余、自我修复和无与伦比的重建速度实现的极高可靠性与可用性

Pksqs工具(1.3.5.2) 使用说明 (2) 安装或升级 (2) 卸载 (3) 1、字段分割 (3) 2、栅格提取 (4) 3、栅格裁切 (5) 4、小班编号 (6) 5、导出Excel (7) 6、挂接Excel (8) 7、属性拷贝 (8) 8、底图切割 (9) 9、细碎小班 (10) 10、新建字段 (10) 11、提取界线 (11) 关于 (12)

使用说明 Pksqs工具是一个提高效率的arcgis插件,支持arcgis10及以上arcmap产品,不支持9.3,10.1版本性能较为稳定,速度较快(安装包有10.1版本和10版本两个安装文件,10.1及以上建议使用10.1版本,10建议使用10版本);使用前请先查看使用说明和备份数据,mdb或gdb数据最好先导出为shp格式;电脑最好安装Microsoft .NET Framework 4版本。 安装或升级 双击安装,安装后打开gis,在自定义中打开自定义模式,勾选pksqs工具。 勾选

卸载 选中点击上图删除此加载项就可以了。 1、字段分割 适用于矢量图层按照字段分割成图斑。 注意:开始后请稍等一段时间,分割时间取决于图层图斑数量。请先将图层导入arcgis后打开此插件,选择图层。

2、栅格提取 适用于栅格按照提取范围的大小批量提取栅格数据,例如批量地形图裁边。 注意:栅格文件应该是配准后文件,提取范围栅格文件应该具有相同的坐标系,提取范围和栅格文件应该命名相同,忽略大小写,忽略文件名。提取范围可为任意形状图斑图层文件,裁切范围可为栅格文件,开始后会出现进度,以进度完成提示为准;栅格提取过程需要调用Spatial Analyst 部分内容,请确保自定义菜单,扩展模块中勾选。 可选择配准后的地形图文件夹。 提取范围可使用字段分割工具,先按照字段分割,作为栅格提取范围。 匹配个数

主流DS P存储器测试方法 本文选自电子发烧友网5月《智能工业特刊》特别聚焦栏目,转载请注明出处 存储器相关的问题是DSP 应用中非常普遍的问题。本文介绍KeyStone I 系列DSP 上一些存储器测试的方法。 KeyStone DSP 存储器系统简介 KeyStone DSP 存储器架构如图1 所示。 对不同的DSP,存储器的大小可能不同,DSP 核和EDMA 传输控制器的个数也可能不同。表1比较了KeyStone I 系列中常用的3颗

DSP。 表1 KeyStone I 存储器系统比较 本文介绍几种存储器测试算法,并讨论这几种算法的用途。 数据测试 下面是数据测试的伪代码: for(memory range under test) fill the memory with a value; for(memory range under test) read back the memory and compare the readback value to the written value 通常,这个测试会被执行几次,每次填充的值不一样。常用的填充值包括 0x55555555, 0xAAAAAAAA, 0x33333333, 0xCCCCCCCC, 0x0F0F0F0F , 0xF0F0F0F0, 0x00FF00FF , 0xFF00FF00FF00, 0xFFFFFFFF , 0。 这个测试可以用来检测数据比特粘连(bit -stuck)问题,例如,如果,

written value = 0, readback value = 0x8, 表示bit 3 粘连到1. 如果 written value = 0xFFFFFFFF , readback value = 0xFFFFFFFE, 表示bit 0 粘连到0. 如果能正确的写入并读出0x55555555(或0xAAAAAAAA),说明相邻的两个比特没有粘连;如果能正 确写入并读出0x33333333(或0xCCCCCCCC),说明相邻的4 个比特没有粘连;如果能正确写入并读出 0x0F0F0F0F(或0xF0F0F0F0),说明相邻的8 个比特没有粘连… 这个算法既可以用来测试数据总线连接,也可以用于测试存储器单元。当用于测试存储器单元时则每一 个存储单元都需要写读所有的值,这将是比较耗时的测试;而用于测试数据总线连接时,只需要把所有的值都 写读一遍就可以了(地址不限)。 地址测试 地址测试的伪代码如下: for(memory range under test) fill each memory unit with its address value; for(memory range under test) read back the memory and compare the readback value to the written value

使用Nios II Flash Programmer下载后无法从EPCS启动的问题集中在以下版本:9.0SP2 、9.1、9.1SP2 、11.0 究其根本,就是这几个版本的Series Flash Leader有Bug。其中11.0,无法在下载jic时,擦除EPCS。 解决方法sof+elf>flash>hex>jic 经Edison指点,得知alteraforum上有前辈给出解决方法。看似简单,疗效却比较好。 在所在QII工程文件夹中,新建一个文件夹。此处以sof+elf_jic为例; 将QII工程和NII工程编译生成的sof和elf都拷贝到此文件夹内; 按如下格式,新建一个sh文件,此处命名为make_hex.sh;(sh文件,bash的批处理文件;类似于DOC的bat文件) Code: sof="DE0_Nano.sof" elf="DE0_Nano.elf" echo "sof>flash ..."; sof2flash --epcs --input=$sof --output=hw.flash --quiet echo "elf>flash ..."; elf2flash --epcs --after=hw.flash --input=$elf --output=sw.flash echo "cat flash ..."; cp hw.flash hw_sw.flash; cat sw.flash >> hw_sw.flash echo "flash>hex ..."; nios2-elf-objcopy --input-target srec --output-target ihex hw_sw.flash hw_sw.hex echo "del flash ..."; rm -f *.flash // 修改第1~2行处所指的文件名,保存。打开开始>程序>Altera>Nios II EDS xx.x>Nios II xx.x Command Shell,此处以Nios II 10.1 Command Shell做示范(图1)。

Flash程序烧写步骤 1、protect off all erase all (如果要同时烧录fpga0、fpga1、vmlinux内核才使用此命令,擦除所有all。如果只需要更换其中的部分,可单独擦除,如下。) 2、printenv(查看网络连接情况) 3、setenv serverip 192.168.11.60(设置电脑地址) 4、setenv ipaddr 192.168.11.201(设置UC IP地址) 5、saveenv(保存设置) 6、setenv ethact octeth1 (erase 18080000 180fffff - 如果单独烧写fpga0则使用该命令擦除flash中原fpga0的内容,如果执行了命令“erase all”,则不用执行该命令) 7、tftp 20000000 fp0_v200c_0802.app (使用tftp将fpga0从电脑传到UC内存的20000000地址) tftp 20000000 fp0_v200d_20101108.app(软交换) 8、cp.b 20000000 0x18080000 0x39998 (【1】将刚传到UC内存地址20000000的fpga0拷贝到UC的flash的18080000地址中;【2】注意文件大小正确,此例的大小是0x39998) (erase 19f40000 19ffffff - 如果单独烧写fpga1则使用该命令擦除flash中原fpga1的内容,如果执行了命令“erase all”,则不用执行该命令) 9、tftp 20000000 fp1_v2005_0802.app (使用tftp将fpga1从电脑传到UC内存的20000000地址) tftp 20000000 fp1_v2007_20101207.app(软交换) 10、cp.b 20000000 0x19f40000 0x39998 (【1】将刚传到UC内存地址20000000的fpga1拷贝到UC的flash的18080000地址中;【2】注意文件大小正确,此例的大小是0x39998) (erase 0x18100000 0x186fffff - 如果单独烧写Linux则使用该命令擦除flash中原Linux的内容,如果执行了命令“erase all”,则不用执行该命令) tftp 20000000 vmlinux.64.2011_01_05.gz tftp 20000000 vmlinux.64.2011_01_18.gz(1-18最新内核) 11、tftp 20000000 vmlinux.64.2011_01_20.gz cp.b 0x20000000 0x18100000 0x598a41 (【1】将刚传到UC内存地址20000000的vmlinux.64.gz拷贝到UC的flash的18080000地址中;【2】注意文件大小正确,此例的大小是0x4fcff0) cp.b 0x20000000 0x18100000 0x598a7e(新版本的大小)在其修改了,还是在终端出现错误 12、cp.b 0x20000000 0x18100000 0x5cd321 13、askenv boot(设置boot参数) Please enter 'boot':gunzip 0x18100000 0x598a41 0x20000000 0xb00000(1-5号的版本) Please enter 'boot':gunzip 0x18100000 0x598a7e 0x20000000 0xb00000(1-18号的版本) 14、Please enter 'boot':gunzip 0x18100000 0x5cd321 0x20000000 0xb00000 (1-20号的版本) 15、askenv bootcmd(设置boot参数) 16、Please enter 'bootcmd':run boot;Init8201;bootoctlinux 17、saveenv(保存设置) 18、run bootcmd 19、在shell终端执行命令: 20、~ # ifconfig eth1 up<激活UC网口eth1> 21、~ # ifconfig eth1 192.168.11.1 <为UC的eth1网口配置IP地址>

搜索配置工具使用说明 1.网络设备搜索 网络设备搜索用于发现与软件运行PC同一个子网内的在线设备,工具软件还可以对搜索出的设备的基本信息进行修改。工具软件开始运行时如图1-1所示 图1-1 1.1修改端口 用户选择一个在线设备后,其各项信息会显示在图1-1中在线列表的下方,用户可以对端口进行修改。 1.2批量修改IP 当用户在在线列表中勾选多个设备后,输入起始IP、子网掩码、DNS、网关,点击批量修改IP,可以对多个设备自动修改IP地址。 1.3导出设备信息 该功能是将在线列表中的所有设备信息以CSV格式文件导出。 1.4恢复密码 (1).用户首先获得设备ID和运行时长 (2).拨打400电话获得加密字符串 (3).一小时内将加密字符串输入到密码追回框中,进行密码恢复 1.5重启设备 对当前选中的设备进行重启,不支持批量。 1.6写入文件 如果勾选了写入文件,该软件所产生的日志信息将会以文本形式记录到C盘下 2.参数配置 该配置页包含前端设备参数、通道参数、常用设置、保存配置文件、网络测试、格式化磁盘、清理插件功能。 在每项参数设置中都有“保存至模板”复选框,如果勾选“保存至模板”,当点击“保存模板”按钮时,可以将“常用参数配置”的数据保存到配置文件中,不勾选“保存至模板”

则

不对其进行保存。 界面如图2-1所示 图2-1 2.1前端参数配置 (1).打开参数配置页,默认进入前端参数配置 (2).右击设备树,点击“登录”按钮登陆设备,登录后设备树会有相应颜色变化(成功:绿色,失败:红色,超时:蓝色) (3)在面板右侧选择设备类型IPC或者球机 (4).用户可以在“常用参数配置”中对设备进行控制 (5).点击“保存参数”,会将数据配置到设备 (6).勾选“显示码率帧率”,视频会叠加当前的码率和帧率 2.2 通道参数配置,界面如图2-2所示 (1).在字符叠加配置中,用户可以选择叠加通道名称和叠加通道时间,点击“保存参数”时,会进行相应的叠加。 (2).在音视频参数配置中,可以对设备的音视频参数进行设置,视频默认连接的是主码流,音视频参数模块的主副码流单纯的只是配置参数,与IE相对应,具体设置项见图2-2。(3).录像参数配置中,用户可以设置设备的录像时间模板,具体设置项见图2-2。

281x无需仿真器,串口烧写Flash方法 再发一次!希望版主不要再删!! 考虑到众多买不起仿真器的劳苦大众!下面提供利用PC RS232下载flash到281x的方法: 第一步:安装CCS2.2或更高版本 以确保你的源代码能编译为下载源码:xxx.out文件 第二步:安装串口编程算法项目文件:sdf28xx_v3_0_serial (Ti网站上有下载) 详情请阅读包含的:SDFlash_Serial_RefGuide_v3_0.pdf文件 第三步:在算法项目文件中设置好相应的时钟频率,并生成.out文件 (1)在CC中导入F2812SerialFlash.pjt文件 文件目录: C:\CCStudio_v3.1\specdig\sdflash\mydrivers\DSP281x_v3_0\DSP281x_serial\build\F28xxSerialFlas h (2)设置好你的目标板相应的时钟频率 在Flash280x_API_Config.h中相应的PLL时钟,我使用的是20M晶掁则选择: #define CPU_RATE 10.000L // for a 100MHz CPU clock speed (SYSCLKOUT) (3)保存并编译项目文件,生成F2812SerialFlash.out文件存放在: C:\CCStudio_v3.1\specdig\sdflash\mydrivers\DSP281x_v3_0\DSP281x_serial\bin 注:确定你的程序空间定义在flash段,(在CMD文件修改) 第四步:安装SdFlashV1.60或更高版本 第五步:编辑sdopts.cfg文件,此文件存放在你所安装的windows的System32目录下 (1)用记事本的方式打开sdopts.cfg (2)在"# End of sdopts.cfg”前加入如下文本: [EmulatorId=C1] EmuPortAddr=0xC1 EmuPortMode=RS232 EmuProductName=SERIAL_FLASH [EmulatorId=C2] EmuPortAddr=0xC2 EmuPortMode=RS232 EmuProductName=SERIAL_FLASH [EmulatorId=C3] EmuPortAddr=0xC3 EmuPortMode=RS232 EmuProductName=SERIAL_FLASH [EmulatorId=C4] EmuPortAddr=0xC4 EmuPortMode=RS232 EmuProductName=SERIAL_FLASH

SecureCRT工具使用说明 1.背景及相关概念 SecureCRT是一款支持SSH(SSH1和SSH2)的终端仿真程序,同时支持Telnet 和rlogin协议。SecureCRT是一款用于连接运行包括Windows、UNIX和VMS的远程系统的理想工具。通过使用内含的VCP命令行程序可以进行加密文件的传输。有流行CRTTelnet客户机的所有特点,包括:自动注册、对不同主机保持不同的特性、打印功能、颜色设置、可变屏幕尺寸、用户定义的键位图和优良的VT100,VT102,VT220和ANSI竞争。能从命令行中运行或从浏览器中运行.其它特点包括文本手稿、易于使用的工具条、用户的键位图编辑器、可定制的ANSI颜色等.SecureCRT的SSH协议支持DES,3DES和RC4密码和密码与RSA鉴别。 SSH的英文全称是Secure Shell。传统的网络服务程序,如:ftp和telnet 在本质上都是不安全的,因为它们在网络上用明文传送口令和数据别有用心的人非常容易就可以截获这些口令和数据。而通过使用SSH客户端与服务器端通讯时,用户名及口令均进行了加密,有效防止了对口令的窃听。同时通过SSH的数据传输是经过压缩的,所以可以提高数据的传输速度,既然如此我们为什么不使用它呢。SSH是由客户端和服务端的软件组成的,有两个不兼容的版本分别是:1.x 和 2.x。至于具体如何安装服务器端,普通用户就不需要关心了。 2.基本设置 为了SecureCRT用起来更方便,需要做一些设置,需要修改的有如下几处: A.退出主机自动关闭窗口 Options => Global ptions => General => Default Session => Edit Default Settings...

简述存储器测试图形算法 1 介绍 随着集成电路制造工艺的不断进步,半导体芯片的发展趋于高密度、高速度、高复杂度,给测试带来了极大的挑战。存储器是集成电路产品中的一个主要门类,主要用来存放数据、指令、程序等信息。存储器的测试一方面可用于判断产品质量是否合格,另一方面通过测试获得一些数据用于改进工艺。 目前存储器的基本测试方法已经比较成熟,主要有存储器直接存取测试、存储器的宏测试、存储器内建自测试三种,各有利弊。存储器直接存取测试是利用自动测试设备来进行测试,自动测试设备的性能和测试成本使得直接存取测试方式对大容量的存储器并不合适。存储器的宏测试将存储器作为一个宏模块,利用电路内部的扫描路径生成宏模块的测试向量,再通过自动测试设备在电路外部施加测试矢量,对于较大的存储器,宏测试向量的数据量较大,测试需要较长时间。存储器内建自测试是在存储器外围产生一整套控制电路,实现芯片内置存储器测试模式的自动产生及测试结果的自动判别,这种方法增加芯片的面积,但是具有自动化程度高、测试质量高、测试成本低、测试时间短等优势。 对于存储器来说,最主要的测试是读写逻辑功能测试,以检测存储单元的故障,包括由于坏的金属连接、坏的元件、芯片逻辑错误等原因引起的功能故障。这些故障通常被简化为几个较为成熟的故障模型,通过不同的测试图形算法来检测故障。本文以存储器的测试图形为切入点,先简单介绍存储器简化的故障模型,然后介绍常用的存储器测试图形算法以及一些新近提出的改进存储器测试图形算法,对其进行比较,并对将来存储器测试图形的发展进行预期。 2 常用的存储器测试图形算法 对于存储器的功能测试,算法有很多种,分别针对不同的存储器故障模型,包括固定故障、转换故障、耦合故障、图形敏感故障、寻址故障、数据保留故障等。一个高效率的测试算法,需要用尽可能少的测试图形和尽可能短的测试时间检测到尽可能多的故障。从理论上说,存在覆盖所有故障的测试算法,但是实际上由于时间复杂度的原因无法实现。假设用N 表示一个存储器的地址数,那么测试图形的复杂度可以用N来表示。 对于较大容量的存储器来说,N3/2图形和N2图形的测试时间在实际测试中是无法承受的。在实际测试中最常用的算法主要有全0/全1图形,奇偶校验板图形和齐步1/0图形。这三种图形均为N图形。 1、全0/全1图形 将全部存储单元按顺序写0、读0、写1、读1,测试图形序列长度为4 N,可用于检测存储器的固定故障。 2、奇偶校验板图形