HDL实验报告 马茜

- 格式:doc

- 大小:474.00 KB

- 文档页数:36

生物化学设计性实验报告阿托伐他汀钙片对小鼠调脂作用的观察1.实验目的观察临床常用调脂药物阿托伐他汀钙片对小鼠血清中脂类物质调节作用。

2.实验原理本品为HMG-CoA还原酶选择性抑制剂,通过抑制HMG-CoA还原酶和胆固醇在肝脏的生物合成而降低血浆胆固醇和脂蛋白水平,并能通过增加肝细胞表面低密度脂蛋白(LDL)受体数目而增加LDL的摄取和分解代谢,因此对高密度脂蛋白(HDL)也有一定的调节作用。

对小鼠使用阿托伐他汀钙片,一段时间后测定血清中的总胆固醇含量和高密度脂蛋白的含量,并设置对照组,来观察此药物对脂类物质的调节作用2+ 空腹血浆脂蛋白主要为低密度脂蛋白(LDL)和高密度脂蛋白(HDL),PAT-Mg 具有选择性沉淀载脂蛋白为apoB的脂蛋白LDL,则上清液为HDL,HDL以HDL-C表示含量。

胆固醇酯+HO --------胆固醇酯酶---->胆固醇+RCOOH 2胆固醇+O --------胆固醇氧化酶---->?4-胆甾烯酮+HO 222HO+4—AA+ESPAS----过氧化氢酶------>醌亚胺染料+ HO 222血清胆固醇经如下反应,可以生成红色醌亚胺:胆固醇酯+HO --------胆固醇酯酶---->游离胆固醇+脂肪酸 2游离胆固醇+O--------胆固醇氧化酶---->胆甾烯酮+HO 222HO+4—氨基安替比林+4—氯酚-----过氧化物酶------>苯醌亚胺(红色) 223.实验步骤3.1取两只小鼠于鼠笼中,做好标记,对药物组小鼠灌胃适量阿托伐他汀钙片溶液(用药量参照人体用量,按照小鼠重量进行比例换算,并溶解于适量生理盐水中,生理盐水不宜过多),灌胃后等待一个半小时,让小鼠将药物充分吸收并起作用。

3.2对两只小鼠分别进行摘除眼球放血处理,并将血液放置于抗凝瓶中,后转至离心管中以3000r/min离心5min。

3.3取上清液即为血清,测量血清高密度脂蛋白和总胆固醇含量。

目录1. 检测原理2. 标本采集与处理2.1 受检者的准备2.2 静脉采血2.3 抗凝剂2.4 标本处理3. 试剂3.1 试剂3.2 校准血清3.3 试剂与校准血清的稳定性4. 仪器5. 操作6. 计算7. 操作性能7.1 精密度7.2 准确度7.3 灵敏度7.4 可报告范围7.5 特异性7.6 干扰8. 参考值9. 临床意义附录A: 参数1. 检测原理1. 试剂1使血清中低密度脂蛋白和极低密度脂蛋白经化学反应被消除。

胆固醇酯酶胆固醇酯+ H2O -------------------- 胆固醇+ 脂肪酸胆固醇氧化酶胆固醇+ O2 ------------------------- 胆淄烯酮+ H2O2过氧化氢酶H2O2 ------------------ O2+H2O2. 试剂2中的变性剂释放出高密度脂蛋白后,对HDL进行测量。

胆固醇酯酶胆固醇酯+ H2O -------------------- 胆固醇+ 脂肪酸胆固醇氧化酶胆固醇+ O2 ------------------------- 胆淄烯酮+ H2O2过氧化物酶H2O2 + 4-氨基安替比林+ HDAOS -------------------- 醌染料+ 4H2O在600nm醌染料的吸光度的与胆固醇的含量相关。

2.标本采集与处理2.1 受检者的准备:病人空腹12h,不饮酒24h后采集血样。

体检对象抽血前应有两周的的正常状况记录。

妊娠后期各项血脂都会增高,应在产后或中哺乳后3个月检验才能反应其基本血脂水平。

注意有无应用影响血脂的药物,如降血脂药、避孕药等。

此外,对于体检者,采血的季节都应做相关记录,因为血脂水平有季节性变动,为了前后比较应在每年同一季节检验,应嘱体检对象在抽血前24小时内不做剧烈运动。

2.2 静脉采血:除非是卧床的病人,一般在采血时取坐位。

体位影响水分在血管内外的分布,会影响测试项目的浓度。

在采血前至少应静坐5分钟,一般从肘静脉取血,使用止血带的时间不超过1分钟,穿刺成功后立即松开止血带。

第24卷,第3期光 谱 实 验 室V ol.24,N o.3 2007年5月Ch inese J ou rnal of S p ectroscop y L aboratory M ay,2007硫酸钡吸光比浊法测定大蒜中大蒜素含量马茜①(太原理工大学化学化工学院 太原市 030024)摘 要 用浓硝酸将大蒜中有机硫化物定量氧化成硫酸根,在聚乙烯醇介质中与钡离子反应生成稳定的硫酸钡悬浊液,吸光比浊法测定其硫酸根含量,从而换算出大蒜素含量。

建立了吸光比浊法测定大蒜中大蒜素含量的新方法,该法不需大蒜素标准样品,简单、快速、实用,结果与定硫法(重量法)基本一致。

关键词 比浊法,大蒜,大蒜素,聚乙烯醇。

中图分类号:O657.32 文献标识码:B 文章编号:100428138(2007)03203452031 前言大蒜是百合科葱属植物的地下鳞茎,在我国和世界各地作为民间用药已有数千年历史。

大蒜有抗菌、消炎、杀虫、降脂、抗动脉粥样硬化、抗肿瘤和提高机体免疫力的作用。

大蒜的医疗保健作用与大蒜中的主要含硫化合物大蒜素密切相关。

因此大蒜素含量已成为评价大蒜及其制品质量的重要指标。

但大蒜素稳定性差,测定较为困难。

目前测定大蒜中大蒜素含量多采用定硫法[1](重量法)和高效液相色谱法[2],前者操作繁琐费时,后者则必须有大蒜素标准样品,硫酸钡吸光比浊法测定大蒜中大蒜素未见报道。

该法不需大蒜素标样,操作简单、快捷、实用。

结果与重量法基本一致。

2 实验部分2.1 测定原理新鲜大蒜中含硫化合物都以蒜氨酸(大蒜素的前体物质)形式存在,当鳞茎组织受损时,分解成大蒜素[3]。

用浓硝酸将大蒜中蒜氨酸的亚砜基和大蒜素的硫代亚砜基定量氧化成硫酸根,在聚乙烯醇介质中与氯化钡反应生成稳定的硫酸钡悬浊液,吸光比浊法测定其硫酸根含量,从而换算出大蒜素含量。

2.2 仪器与试剂TU21901双光束紫外可见分光光度计(北京普析通用仪器有限公司).;SO2-4标准溶液:0.1 g L,以硫酸钾配制;10%氯化钡溶液;2%聚乙烯醇溶液;20%六次甲基四胺2HC l缓冲溶液;浓硝酸;试剂均为分析纯;实验用水为蒸馏水。

实验名称:超敏之星原理实验实验目的:1. 深入理解I型超敏反应的机理。

2. 掌握I型超敏反应实验的操作方法。

3. 通过实验观察和结果分析,加深对超敏反应现象的认识。

实验原理:I型超敏反应,又称为即时型超敏反应,是一种由IgE介导的过敏反应。

在I型超敏反应中,变应原首次进入机体后,会刺激B细胞分化为浆细胞,产生特异性IgE抗体。

这些IgE抗体的Fc段与肥大细胞或嗜碱性粒细胞表面的Fc受体(FcR)结合,使这些细胞致敏。

当相同的变应原再次进入机体时,会与致敏细胞表面的IgE结合,引发一系列生物活性介质的释放,如组胺、细胞因子、前列腺素和白三烯等,从而导致平滑肌痉挛、小血管通透性增加、黏膜腺体分泌增加和神经末梢敏感等症状。

实验材料:- 家兔两只- 鸡蛋清- 鸭蛋清- 酒精- 一次性注射器实验步骤:1. 实验前两周,取健康家兔两只,分别皮下注射0.5ml鸡蛋清,作为初次致敏。

2. 实验当天,将一只家兔作为阳性组,另一只作为阴性组。

3. 对阳性组家兔,耳缘静脉注射1/10鸡蛋清溶液1~2ml;对阴性组家兔,耳缘静脉注射1/10鸭蛋清溶液1~2ml。

4. 观察并记录两组家兔的生理反应。

实验结果:1. 阳性组家兔在注射鸡蛋清后,迅速出现呼吸急促、呼吸道阻塞、张嘴呼吸等症状,最终因窒息死亡。

2. 阴性组家兔在注射鸭蛋清后,未出现明显异常反应。

分析与讨论:本实验通过观察家兔在注射鸡蛋清和鸭蛋清后的生理反应,验证了I型超敏反应的原理。

在初次注射鸡蛋清时,家兔体内的B细胞被激活,产生特异性IgE抗体,使肥大细胞和嗜碱性粒细胞致敏。

当再次注射相同变应原(鸡蛋清)时,致敏细胞表面的IgE与变应原结合,引发生物活性介质的释放,导致家兔出现呼吸急促、呼吸道阻塞等症状,最终窒息死亡。

而注射鸭蛋清(非致敏原)的家兔,未出现明显异常反应,说明I型超敏反应具有特异性。

本实验结果提示我们在日常生活中,应尽量避免接触已知的过敏原,以减少I型超敏反应的发生。

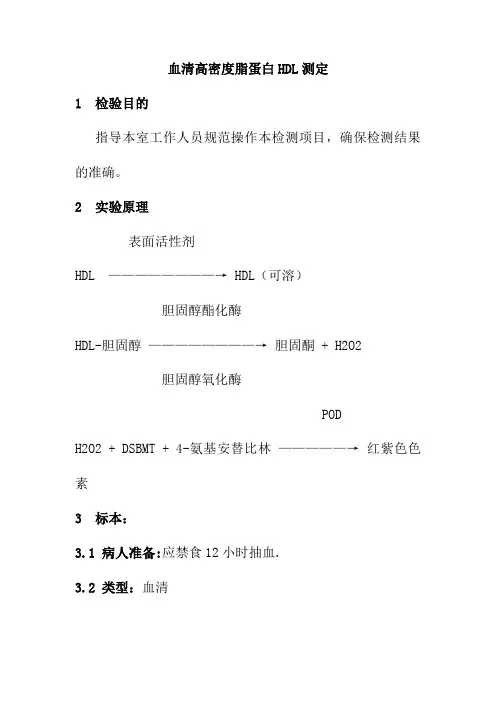

血清高密度脂蛋白HDL测定1 检验目的指导本室工作人员规范操作本检测项目,确保检测结果的准确。

2 实验原理表面活性剂HDL ————————→ HDL(可溶)胆固醇酯化酶HDL-胆固醇————————→胆固酮 + H2O2胆固醇氧化酶PODH2O2 + DSBMT + 4-氨基安替比林—————→红紫色色素3 标本:3.1 病人准备:应禁食12小时抽血.3.2 类型:血清3.3 标本存放留取标本后请尽快分离血清。

在冰箱保存的条件下(2~8℃)稳定3天,-20℃保存至少可以稳定3个月。

3.4 标本运输室温条件下运输3.5 标本拒收标准细菌污染的不能做测定。

4 实验材料4.1 试剂:宁波美康生物科技股份有限公司血清高密度脂蛋白胆固醇(HDL)测定试剂盒(浙械注准20142400141)4.1.1 试剂组成试剂1(R1):哌嗪-1,4-双(2-乙磺酸) 缓冲液pH 7.0 50mmol/L胆固醇脂酶(CE) 800U/L胆固醇氧化酶(CO) 400U/L过氧化氢酶 20KU/LTriton X-100 2ml/L 试剂2(R2):哌嗪-1,4-双(2-乙磺酸) 缓冲液pH 7.0 50mmol/L过氧化物酶(POD) 1000U/L4-氨基安替比林(4-APP) 1.0mmol/LN,N-双(4-磺丁基)-3-甲基苯胺(DSBMT)0.5mmol/L4.1.2 试剂准备:试剂为即用式。

4.1.3 试剂稳定性与贮存:试剂保存于2~8℃,若无污染,可稳定至失效期。

试剂不可冰冻。

试剂可避光保存可稳定12个月;试剂开口稳定1个月。

4.1.4 变质指示:当试剂有看得见的微生物生长,有浊度,或者未开盖的液体有沉淀时,表明试剂已变质,不能继续使用。

4.1.5 注意事项:试剂中含叠氮钠(0.95g/L)为防腐剂。

不可入口!避免接触皮肤及粘膜。

应采取必要的预防措施使用试剂4.2 校准品:建议使用宁波美康生物科技有限公司提供的脂类标准品进行全点校准操作。

高密度脂蛋白胆固醇直接一步法作业指导书1、前言试验名称:高密度脂蛋白胆固醇测定,英文名称:HDL-C,方法:直接一步法。

本文件适用于安阳鼎城糖尿病医院检验科生化实验室,目的是指导工作人员正确的在科华KHB-450全自动生化分析仪上测定血清、血浆样本中的高密度脂蛋白胆固醇的浓度,以保证测定结果的准确可靠。

本试验用体外定量测定人血清或血浆样本中高密度脂蛋白胆固醇的浓度。

HDL-C水平与冠心病发病率负相关,因此认为高密度脂蛋白降低是动脉粥样硬化的危险因素,高密度脂蛋白-胆固醇下降在冠状动脉疾病、高脂血症、抽烟、肥胖、糖尿病、肝疾患等疾病时有反映。

2、测定原理本实验使用与除HDL以外的脂蛋白结合、对反应起选择性遮蔽作用的高分子化合物及对HDL亲和作用高的表面活性剂,根据对HDL可溶性的特异作用,测定高密度脂蛋白的浓度。

高密度脂蛋白胆固醇酯CE 胆固醇+脂肪酸胆固醇+O2CO胆甾-4-烯-3-酮+H2O2H2O2+HBA+4-氨基安替比林POD醌亚胺色素+H2O在上述反应中,经色醌亚胺色的生成量与样本中胆固醇的浓度成正比,通过在500nm波长处测定吸光度的变化值,即可测得样本中胆固醇的浓度。

注:CE胆固醇酯酶CO胆固醇氧化酶POD过氧化物酶HBA对-羟基苯甲酸3、试剂试剂生产商:长海科华公司。

剂型:液体双试剂。

包装量:R1:4*45ml R2:2*20ml注册号:沪食药监械(准)字2011第2400011号。

生产许可证号:沪药管械生产许20030916号。

基本成份:试剂1胆固醇氧化酶>300u/l胆固醇酯酶>300u/l过氧化物酶>750u/l4-氨基安替比林0.2mmol/l缓冲液30mol/l表面活性剂高分子化合物试剂2对-羟基苯甲酸30mmol/l缓冲液50mol/l表面活性剂储存条件和有效期:试剂避光储存于2―8℃可稳定至试剂盒标注的有效期。

4、标准品:使用试剂盒附带标准品5、质控品:生产商:英国Randox公司。

高密度脂蛋白测定实验报告高密度脂蛋白测定实验报告引言:高密度脂蛋白(High-Density Lipoprotein, HDL)是一种血浆中的脂蛋白,对人体健康十分重要。

本次实验旨在通过测定血液中HDL的浓度,了解其与心血管疾病的关系,并探讨一些影响HDL水平的因素。

实验方法:1. 实验材料准备:- 血液样本:从志愿者中采集新鲜全血样本,以避免血液成分的变化。

- 试剂盒:使用经过质量控制的HDL测定试剂盒,以确保测定结果的准确性。

- 实验仪器:使用自动生化分析仪进行测定。

2. 实验步骤:- 样本处理:将采集的全血样本离心,分离血浆,并将血浆保存在低温条件下,以防止HDL的降解。

- 试剂配置:按照试剂盒说明书的要求,准备好所需的试剂和标准品。

- 操作仪器:将标本和试剂按照仪器的操作要求装载,启动自动生化分析仪进行测定。

- 结果记录:记录测定结果,并进行数据分析。

实验结果:通过测定多个样本的HDL浓度,我们得到了如下结果:样本A:1.20 mmol/L样本B:1.05 mmol/L样本C:1.35 mmol/L样本D:0.95 mmol/L样本E:1.25 mmol/L数据分析:根据实验结果,我们可以得出以下结论:1. 样本C的HDL浓度最高,样本D的HDL浓度最低。

这表明不同个体之间HDL水平存在差异,可能受到遗传和生活方式等因素的影响。

2. 样本A、B和E的HDL浓度相对较高,可能与他们的饮食结构和运动习惯有关。

高纤维、低脂肪的饮食和适量的运动有助于提高HDL水平。

3. 样本D的HDL浓度较低,这可能是由于其生活习惯不良,如高脂肪、高糖的饮食和缺乏运动等。

讨论与启示:通过本次实验,我们深入了解了HDL的测定方法以及其与心血管疾病的关系。

HDL被认为是“好胆固醇”,其水平越高,心血管疾病的风险越低。

因此,保持适当的HDL水平对于预防心血管疾病非常重要。

此外,本次实验还启示我们以下几点:1. 饮食结构:合理的饮食结构对HDL水平有重要影响。

脂蛋白代谢实验报告简介脂蛋白代谢是机体内脂质的运输和代谢过程,对维持机体的脂质平衡具有重要作用。

本实验旨在研究脂蛋白代谢的相关指标,为疾病的诊断和治疗提供参考。

实验方法实验对象本实验选取了20名健康成年男性作为实验对象。

实验步骤1. 采集血样:实验前,空腹采集实验对象的静脉血样。

2. 分离脂蛋白:将采集到的静脉血样离心分离,得到血浆。

3. 电泳分析:将血浆样品进行一维非凝胶电泳分析,利用电泳仪测量主要的脂蛋白质量和浓度。

4. 检测指标:根据电泳结果,测量脂蛋白的蛋白质含量、胆固醇含量、三酰甘油含量等指标。

5. 统计分析:对实验数据进行统计学分析,并与对照组进行比较。

实验结果脂蛋白质量通过电泳分析,得到实验对象脂蛋白的质量分布情况。

结果显示,血浆中主要存在四种脂蛋白,即乳糜微粒(chylomicrons),低密度脂蛋白(LDL),高密度脂蛋白(HDL),和极低密度脂蛋白(VLDL)。

其中,HDL的含量最高。

脂蛋白含量根据分析得到的数据,我们测量了实验对象脂蛋白的蛋白质含量、胆固醇含量和三酰甘油含量。

结果显示,在实验对象中,LDL胆固醇和VLDL三酰甘油的含量显著高于对照组,而HDL蛋白质的含量显著低于对照组。

其他指标此外,实验还测得实验对象的血脂和血糖水平。

结果表明,实验对象的总胆固醇和甘油三酯水平较高,而高密度脂蛋白胆固醇的水平较低。

而血糖水平与对照组相比,并无显著差异。

数据分析通过对实验结果的统计学分析,得到以下结论:1. 健康成年男性的脂蛋白代谢主要表现为LDL和VLDL含量的升高。

2. 高胆固醇和高三酰甘油血症与实验对象的血脂异常有关。

3. HDL的蛋白质含量在实验对象中显著低于对照组,可能存在脂代谢紊乱。

结论本实验从脂蛋白质量、蛋白质含量、胆固醇含量等多个指标出发,研究了脂蛋白代谢的特征。

结果显示,实验对象在脂蛋白代谢过程中,出现了血脂异常的情况,其中以LDL和VLDL的升高为主要表现。

一、实验目的1. 了解血浆蛋白的性质及其在不同盐浓度下的溶解度变化。

2. 掌握盐析技术在血浆蛋白分离纯化中的应用。

3. 通过实验观察和分析,了解盐析过程中蛋白质沉淀和溶解的规律。

二、实验原理血浆蛋白是由多种蛋白质组成的复杂混合物,其溶解度受盐浓度的影响。

在一定范围内,随着盐浓度的增加,蛋白质的溶解度降低,当达到一定浓度时,蛋白质会发生沉淀。

盐析是利用这一原理,通过调节盐浓度使蛋白质沉淀,从而实现蛋白质的分离纯化。

三、实验材料与仪器1. 实验材料:- 血浆样品- 氯化钠(NaCl)- 0.1 mol/L Tris-HCl缓冲液(pH 7.4)- 透析袋- 磁力搅拌器- 酶标仪- 离心机- 试剂瓶- 移液器2. 实验仪器:- 电子天平- pH计- 烧杯- 玻璃棒- 镜头四、实验方法1. 配制不同浓度的NaCl溶液:分别配制0.01 mol/L、0.05 mol/L、0.1 mol/L、0.2 mol/L、0.5 mol/L、1.0 mol/L的NaCl溶液。

2. 样品处理:取适量血浆样品,用移液器加入0.1 mol/L Tris-HCl缓冲液(pH 7.4)稀释至10倍,混匀。

3. 盐析实验:分别将稀释后的血浆样品加入不同浓度的NaCl溶液中,室温下搅拌30分钟。

4. 蛋白质沉淀:将混合液以3000 r/min离心10分钟,取上清液备用。

5. 蛋白质复溶:将沉淀物用0.1 mol/L Tris-HCl缓冲液(pH 7.4)溶解,混匀。

6. 蛋白质定量:利用酶标仪测定蛋白质浓度。

五、实验结果与分析1. 实验结果(1)不同盐浓度下蛋白质的沉淀情况:随着NaCl浓度的增加,蛋白质沉淀逐渐增多,0.1 mol/L NaCl溶液中蛋白质沉淀最多。

(2)蛋白质复溶情况:将沉淀物用0.1 mol/L Tris-HCl缓冲液(pH 7.4)溶解后,蛋白质浓度基本恢复到原浓度。

2. 结果分析(1)盐析过程中蛋白质沉淀的原因:随着盐浓度的增加,蛋白质分子间的静电斥力减弱,导致蛋白质分子间的聚集,从而形成沉淀。

《大动脉粥样硬化型急性缺血性脑卒中生物学诊断标志物的实验研究》篇一一、引言急性缺血性脑卒中(S)是一种严重的神经系统疾病,其中大动脉粥样硬化型S是最为常见的类型。

早期诊断和及时治疗对于改善患者预后具有重要意义。

然而,现有的诊断方法多以临床症状和影像学检查为基础,缺乏高效、特异性的生物学诊断标志物。

因此,研究大动脉粥样硬化型急性缺血性脑卒中的生物学诊断标志物具有重要的科学价值和临床意义。

二、方法本研究采用多种生物学技术手段,结合临床资料,对大动脉粥样硬化型急性缺血性脑卒中的生物学诊断标志物进行实验研究。

具体研究方法如下:1. 收集大动脉粥样硬化型急性缺血性脑卒中患者及健康对照组的血液样本。

2. 采用高通量测序技术,对血液样本中的基因表达谱进行检测,分析差异表达基因。

3. 利用蛋白质组学技术,对血液样本中的蛋白质组进行检测,筛选出差异表达的蛋白质。

4. 结合临床资料,分析差异表达基因和蛋白质与大动脉粥样硬化型急性缺血性脑卒中的关联性。

5. 通过统计学方法,对实验结果进行验证和分析。

三、结果1. 基因表达谱分析:通过高通量测序技术,我们发现大动脉粥样硬化型急性缺血性脑卒中患者与健康对照组在基因表达谱上存在显著差异。

其中,某些基因的异常表达与卒中发病密切相关。

2. 蛋白质组学研究:利用蛋白质组学技术,我们筛选出大动脉粥样硬化型急性缺血性脑卒中患者血液中差异表达的蛋白质。

这些蛋白质可能在大动脉粥样硬化及脑缺血过程中发挥重要作用。

3. 关联性分析:结合临床资料,我们发现差异表达基因和蛋白质与大动脉粥样硬化型急性缺血性脑卒中的发病机制、病情严重程度及预后密切相关。

4. 统计学验证:通过统计学方法,我们对实验结果进行验证和分析,证实了差异表达基因和蛋白质作为大动脉粥样硬化型急性缺血性脑卒中生物学诊断标志物的可行性。

四、讨论本研究通过实验研究,发现了大动脉粥样硬化型急性缺血性脑卒中患者与健康对照组在基因和蛋白质水平上的差异。

《氢分子对氧化应激所致衰老及高密度脂蛋白结构功能损伤的保护作用研究》篇一一、引言随着人口老龄化趋势的加剧,衰老及与之相关的健康问题已经成为全球关注的焦点。

氧化应激是导致衰老的重要机制之一,而高密度脂蛋白(HDL)的结构和功能损伤也被认为是衰老过程中的关键因素。

近年来,氢分子在医学领域的应用逐渐受到关注,其抗氧化和抗炎作用被认为是潜在的治疗手段。

本研究旨在探讨氢分子对氧化应激所致衰老及高密度脂蛋白结构功能损伤的保护作用。

二、材料与方法2.1 实验材料本实验选用健康老年人和中年人为研究对象,通过采集血液样本进行后续实验。

同时,使用各种化学试剂和设备进行实验操作和数据分析。

2.2 实验方法本实验分为对照组和实验组,对实验人员进行分组,实验组人员每天需摄取氢气相关补充剂。

通过对实验组和对照组的对比,研究氢分子对氧化应激、衰老及高密度脂蛋白的影响。

采用细胞生物学、分子生物学等方法,对样本进行检测和分析。

三、结果3.1 氢分子对氧化应激的抑制作用实验结果显示,实验组在摄取氢分子后,体内氧化应激水平明显降低。

这表明氢分子具有显著的抗氧化作用,能够抑制氧化应激反应,从而减缓衰老进程。

3.2 氢分子对高密度脂蛋白的保护作用本实验发现,实验组在摄取氢分子后,高密度脂蛋白的结构和功能得到了明显改善。

氢分子能够减少高密度脂蛋白的结构损伤,恢复其功能,有助于维护人体代谢平衡。

3.3 氢分子对衰老的影响通过对比实验组和对照组的生理指标,发现实验组在摄取氢分子后,各项衰老指标均有明显改善。

这表明氢分子能够延缓衰老进程,提高生活质量。

四、讨论本研究表明,氢分子具有显著的抗氧化和抗炎作用,能够抑制氧化应激反应,减缓衰老进程。

同时,氢分子还能改善高密度脂蛋白的结构和功能,有助于维护人体代谢平衡。

这些结果为氢分子在抗衰老和防治相关疾病中的应用提供了有力依据。

值得注意的是,本研究的样本量相对较小,可能存在一定局限性。

此外,氢分子的具体作用机制尚需进一步研究。

《年龄与性别对高密度脂蛋白功能影响的研究》篇一摘要:本研究探讨了年龄与性别对高密度脂蛋白(HDL)功能的影响。

通过对大量人群样本的调查分析,发现年龄和性别对HDL的功能存在显著影响。

本文详细阐述了研究方法、数据分析和结果,为进一步理解HDL在人体健康中的作用提供了科学依据。

一、引言高密度脂蛋白(HDL)是一种重要的脂质代谢物质,具有保护心血管健康的作用。

近年来,越来越多的研究表明,年龄和性别对HDL的功能具有重要影响。

因此,本研究旨在探讨年龄与性别对HDL功能的影响,为预防和治疗心血管疾病提供科学依据。

二、研究方法1. 研究对象本研究共收集了1000名年龄、性别、种族等特征不同的健康人群样本,通过问卷调查和实验室检测收集数据。

2. 实验方法(1)实验室检测:检测受试者HDL水平、胆固醇等生化指标;(2)统计分析:采用描述性统计、t检验、方差分析等方法对数据进行处理和分析。

三、数据分析与结果1. 年龄对HDL功能的影响本研究发现,随着年龄的增长,HDL水平呈下降趋势。

通过比较不同年龄段受试者的HDL功能,发现年轻组HDL的代谢能力和抗氧化能力均优于老年组。

进一步分析发现,年龄对HDL的乳化胆固醇作用、清除血管内炎症等功能有显著影响。

2. 性别对HDL功能的影响本研究发现,男性HDL水平普遍高于女性,但女性HDL的抗动脉粥样硬化作用更为显著。

通过对性别差异的进一步分析,发现女性HDL在抗氧化、抗炎等方面具有独特优势。

此外,女性在生理周期不同阶段,如孕期和更年期等,HDL功能也会有所变化。

3. 交互作用分析除了年龄和性别的影响外,我们还分析了两者之间的交互作用对HDL功能的影响。

结果表明,在相同年龄段内,女性HDL 的抗动脉粥样硬化作用相对较强;而在不同性别间,年轻组的HDL功能整体优于老年组。

这表明年龄和性别因素在HDL功能上存在明显的交互作用。

四、讨论本研究结果表明,年龄和性别对HDL功能具有重要影响。

实验名称:HDL语言姓名:学号:装订线实验报告课程名称:HDL语言指导老师:余锋成绩:______________实验名称:实验二数据的乘法,累加实验类型:同组学生姓名:___________一、实验目的和要求(必填)二、实验内容和原理(必填)三、主要仪器设备(必填)四、操作方法和实验步骤五、实验数据记录和处理六、实验结果与分析(必填)七、讨论、心得实验二、数据的输出,乘法运算,累加运算一.实验目的完成输入数据的乘累加功能;要求乘法部分使用移位方式实现,可参照教材的page98;即完成如下表达式:p_o[n] = p_o[n-1] + a_i[n]*b_i[n];要求完成macc的实现代码;二.实验仪器计算机PC:ModelSim SE 6.5软件三.实验内容完成输入数据的乘累加功能;要求乘法部分使用移位方式实现,可参照教材的page98;即完成如下表达式:p_o[n] = p_o[n-1] + a_i[n]*b_i[n];要求完成macc的实现代码;//macc.vmodule macc(input clk_i,input rst_i,input [7:0] a_i,input [7:0] b_i,input valid_i,output reg [31:0] p_o);//add implementation code hereendmodule提供输入:clk_i 时钟信号,100MHz;rst_i 复位信号,高电平复位;a_i 被乘数,无符号类型;b_i 乘数,无符号类型;valid_i 指示a_i和b_i的有效性;要求输出:p_o 当复位时输出0,否则根据valid_i来完成a_i * b_i的累加;//tb_macc.v专业:电子信息技术及仪器姓名:学号:日期:2014.3.6地点:生仪楼202装订线module tb_macc;//add simulate code hereendmodule文件程序:1.module macc(input clk_i,input rst_i,input [7:0] a_i,input [7:0] b_i,input valid_i,output reg [31:0] p_o,output reg [31:0] pi);reg [7:0] a;reg [7:0] b;always @(posedge clk_i)beginif(rst_i)begin p_o=32'b0;pi=32'b0;end endalways @(posedge valid_i )begina=a_i;b=b_i;pi=32'b0;repeat(8)beginpi=pi<<1;if(a[7])pi=pi+b;a=a<<1;endp_o=pi+p_o;endendmodule2.module tb_macc;reg clk;reg rst;reg [7:0] a;reg [7:0] b;reg valid;wire [31:0] p;wire [31:0] p_i;reg x;macc inst_macc(.clk_i(clk),装订线 .rst_i(rst),.a_i(a),.b_i(b),.valid_i(valid),.p_o(p),.pi(p_i));initial begin$monitor($time,,, "a = %d, b = %d, valid = %b, p = %d,rst=%b,pi=%d", a, b, valid, p,rst,p_i);clk = 1'b0;rst = 1'b1;a = 8'h0;b = 8'h0;valid = 1'b0;#30;rst = 1'b0;//add simulate code here;send_data(8'h1, 8'h2);send_data(8'h11, 8'h32);send_data(8'h21, 8'h42);send_data(8'h31, 8'h52);send_data(8'h41, 8'h62);#30;rst = 1'b1;#30;rst = 1'b0;send_data(8'hf, 8'hab);send_data(8'h11, 8'h0);send_data(8'h21, 8'h33);send_data(8'h78, 8'h45);endalways#5 clk = ~clk;task send_data(input [7:0] a_i,input [7:0] b_i);begin#30;@(posedge clk);a = a_i;b = b_i;valid = 1'b1;装订线 @(posedge clk);valid = 1'b0;a=x;b=x;endendtask四、仿真结果:五.实验小结天哪,这简直就是c乘啊!虽然有一点点不一样,比如建立工程的模块的形式,以及一些关装订线键字不同。

实验名称:血清蛋白质分离实验实验日期:XXXX年XX月XX日实验地点:实验室实验目的:1. 掌握电泳技术分离血清蛋白质的基本原理和操作方法;2. 了解不同血清蛋白质的等电点、分子量和形状;3. 分析血清蛋白质分离实验结果,并探讨实验误差。

实验原理:血清蛋白质分离实验主要采用醋酸纤维素薄膜电泳法。

该法以醋酸纤维素薄膜为支持物,利用蛋白质在电场中的迁移速度差异进行分离。

由于血清中各种蛋白质的等电点、分子量和形状不同,它们在电场中的迁移速度也不同,从而实现分离。

实验器材与药品:1. 实验器材:醋酸纤维素薄膜、电极、电源、染色液、显色液、显色剂、移液器、离心机、显微镜等;2. 实验药品:血清样品、缓冲液、染色液、显色液、显色剂等。

实验步骤:1. 准备实验器材和药品,检查是否齐全;2. 将血清样品进行适当稀释,以适应实验要求;3. 将醋酸纤维素薄膜剪成适当大小,并在薄膜上点样;4. 将点样的薄膜放入缓冲液中,使蛋白质溶解;5. 将薄膜固定在电极上,连接电源;6. 开启电源,进行电泳分离;7. 电泳完成后,取出薄膜,用染色液染色;8. 将染色后的薄膜放入显色液中,显色;9. 将显色后的薄膜放入显色剂中,显色;10. 使用显微镜观察并记录实验结果。

实验结果与分析:1. 实验结果显示,血清蛋白质在醋酸纤维素薄膜电泳中分离出5条区带,分别为清蛋白、α-球蛋白、β-球蛋白、γ-球蛋白和脂蛋白;2. 清蛋白在电泳中迁移速度最快,α-球蛋白次之,β-球蛋白、γ-球蛋白和脂蛋白迁移速度依次减慢;3. 通过比较实验结果与文献报道,发现实验结果与文献报道相符,说明实验方法可行。

实验误差分析:1. 实验过程中,血清样品的稀释倍数和点样量对实验结果有一定影响。

若稀释倍数过大或点样量过少,可能导致区带不明显或无法分离;2. 电泳过程中,缓冲液的pH值和电流强度对蛋白质迁移速度有较大影响。

若pH值过高或过低,电流强度过大或过小,可能导致区带分离不完全或分离速度不均;3. 实验过程中,薄膜的制备和染色操作也可能导致实验误差。

高密度脂蛋白(HDL)拮抗内毒素的实验研究王宁;魏利召【期刊名称】《中国药理通讯》【年(卷),期】2005(022)003【摘要】目的:通过对高密度脂蛋白(HDL)体内外生物学活性实验研究,探讨HDL对内毒素的中和作用。

方法:应用勤和生物传感器技术检测HDL与LPS的结合活性,采用ELISA方法检测HDL对LPS攻击小鼠的保护作用等试验来阐明HDL对LPS的中和效果。

结果:应用亲和生物传感器亲和力检测,结果发现HDL 与lipidA之间具有很高的.木和能力;HDL可以显著抑制LPS刺激小鼠RAW264.7细胞释放TNF—α,并成量效关系;在小鼠体内使用剂量为120mg /kg的HDL可以明显保护致死剂量LPS攻击小鼠,保护率达到70%。

结论:HDL在体内外与LPS结合,从而抑制了LPS的生物学活性,被认为是一种内毒素清除剂,对防治脓毒症具有临床指导意义,【总页数】2页(P51-52)【作者】王宁;魏利召【作者单位】重庆第三军医大学附属西南医院中心实验室,重庆400038【正文语种】中文【中图分类】R446.112【相关文献】1.地骨皮提取物CL-5拮抗内毒素的实验研究 [J], 伏建峰;曹红卫;龙宇鹏;王宁;刘鑫;杨东;鲁永玲;郑江2.野黄芩苷拮抗内毒素抑制人牙周膜细胞增殖作用的实验研究 [J], 杨宁;张莹;葛志华;王春艳3.升高高密度脂蛋白胆固醇(HDL-C)面临的挑战——升HDL-C药物的不同机制和HDL-C升高的疗效评价 [J], 曲鹏;王虹艳4.升高高密度脂蛋白胆固醇(HDL-C)面临的挑战——升HDL-C药物的不同机制和HDL-C升高的疗效评价 [J], 曲鹏; 王虹艳5.抗内毒素IgY体外拮抗内毒素效应的实验研究 [J], 李强;张雅萍因版权原因,仅展示原文概要,查看原文内容请购买。

HDL的异质性及其功能的检测

倪雅懿;王金良

【期刊名称】《实验与检验医学》

【年(卷),期】2008(26)4

【摘要】HDL具有促使细胞外排胆固醇且将胆固醇逆转运至肝中代谢的功能.因而其抗动脉硬化作用已成为人们的共识。

近期的研究对此认识提出疑问。

其原因在于HDL具有异质性且HDL在体内经修饰而发生功能的改变。

由此.检测HDL的多种亚组分及其多项功能已成为研究HDL与心血管病危险性关系的热点。

现就此方面的进展作一综述。

【总页数】3页(P425-427)

【作者】倪雅懿;王金良

【作者单位】300122,天津市民族医院;300122,天津市公安医院

【正文语种】中文

【中图分类】R446.11;Q513

【相关文献】

1.血清HDL2和HDL3的检测对肝病的诊断价值

2.UA、HDL-C、ApoA1/HDL在不同帕金森亚型患者中的差异及其与认知功能的相关性分析

3.异质性荧光染色的巨噬细胞功能研究──Ⅱ.异质性荧光染色的巨噬细胞过氧化物酶活性

4.冠心病人血清TC、HDL—C、HDL—C/TC100例检测

5.HDL功能检测与冠状动脉斑块的相关性

因版权原因,仅展示原文概要,查看原文内容请购买。

Verilog HDL 实验报告专业自动化学号授课班号学生姓名指导教师实验一Modelsim 仿真软件的使用一、实验目的(1)熟悉Modelsim 软件;(2)掌握Modelsim 软件的编译、仿真方法;(3) 熟练运用Modelsim软件进行HDL 程序设计开发二、实验内容用Verilog HDL 程序实现一个异或门,Modelsim 仿真,观察效果程序:module one(key1,key2,led1);input key1,key2;output led1;assign led1 = ~ (key1+key2);endmodulemodule t_one;reg data_in1,data_in2;wire data_out;initialbegindata_in1 = 0;#50 data_in1 = 1;#50 data_in1 = 0;#50 data_in1 = 0;$stop;endinitialbegindata_in2 = 0;#30 data_in2 = 1;#40 data_in2 = 0;#70 data_in2 = 0;$stop;endone test(data_in1,data_in2,data_out);endmodule实验要求:异或门是数字逻辑中实现逻辑异或的逻辑门。

若两个输入的电平相异,则输出为高电平1;若两个输入的电平相同,则输出为低电平0。

实验步骤:(1)分析原理;(2)根据原理编写程序并进行仿真;(3)观察波形,分析仿真结果是否正确。

三、实验结果:波形:四、心得:(1)熟悉了modelsim软件;(2)掌握了modelsim的编译和仿真的方法;(3)会应用modelsim编译HDL的小程序。

实验二:简单组合电路设计一、实验目的:(1)掌握基于Modelsim 的数字电路设计方法;(2)熟练掌握HDL 程序的不同实现方法。

二、实验要求:用与门和或门来实现。

即:Y=A&B+C。

实验步骤:(1)分析原理;(2)根据原理编写程序并进行仿真;(3)观察波形,分析仿真结果是否正确。

实验内容:设计一个三人表决器(高电平表示通过),实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用Verilog HDL 程序实现上述实验内容,并使用modelsim仿真(要求:至少使用两种方法实现上述实验内容和testbench)。

方法一:程序:module two(a,b,c,y);input a,b,c;output y;assigny=a+b&c;endmodulemodule t_two;reg a,b,c;wire y;initialbegina=0;#20 a=1;#40 a=0;#200 $stop;endinitialbeginb=1;#30 b=0;#70 b=1;#100 $stop;endinitialbeginc=0;#20 c=1;#50 c=0;#170 $stop;endtwo u1(a,b,c,y); endmodule三、实验结果:波形:方法二:module two_2(a,b,c,y); input a,b,c;output y;reg y;always@(a or b or c) beginif(a==1'b1)y=1'b1;elsey=a+b;endendmodulemodule t_two_2;reg a,b,c;wire y;initialbegina=1'b0;forever #20 a=~a; endinitialbeginb=1'b0;forever #35 b=~b; endinitialbeginc=1'b1;forever #25 c=~c; endtwo_2 u1(a,b,c,y); endmodule波形:四、心得:(1)同样的电路可以通过不同的方法来进行仿真实现;(2)灵活运用数电知识,写出简单的逻辑表达式,可以使编程简单;(3)Alwaya模块和assign语句的异同;(4)Initial模块的灵活运用;(5)对HDL有了更进一步的了解。

实验三二进制全加器设计一、实验目的:(1)熟悉Verilog HDL 元件例化语句的作用;(2)熟悉全加器的工作原理;(3)用Verilog HDL 语言设计四位二进制全加器,并仿真,下载验证其功能。

二、实验要求:(1)一位全加器原理:A iB i分别是两个二进制位,C i-1是前级进位,C i是进位,S i是加法结果。

S i=A i^B i^C i-1C i=A i&B i+A i&C i-1+B i&C i-1(2)四位二进制全加器原理:在一位全加器基础上设计多位全加器,利用进位进行级联。

实验步骤:(1)分析原理;(2)根据原理编写程序并进行仿真;(3)观察波形,分析仿真结果是否正确。

实验内容:一:用Verilog HDL语言描述一位全加器:程序:module three(ad1,ad2,c,ss,sc);input ad1,ad2,c;output ss,sc;assignss=ad1^ad2^c;assignsc=ad1&ad2+ad1&c+ad2&c;endmodulemodule t_three;reg ad1,ad2,c;wire ss,sc;initialbeginad1=1'b0;forever #10 ad1=ad1+1'b1;endinitialbeginad2=1'b0;forever #80 ad2=ad2+1'b1;endinitialbeginc=1'b0;forever #640 c=c+1'b1;endthree text(ad1,ad2,c,ss,sc);endmodule波形:二:用Verilog HDL 元件例化语句实现四位全加器程序:module three(a1,a2,c,s,sc);input a1,a2,c;output s,sc;assigns=a1^a2^c;assignsc=a1&a2+a1&c+a2&c;endmodulemodule three2(ad1,ad2,c,ss,sc); input [3:0] ad1,ad2;input c;output [3:0] ss;output sc;wire c1,c2,c3;three u1(ad1[0],ad2[0],c,ss[0],c1); three u2(ad1[1],ad2[1],c1,ss[1],c2); three u3(ad1[2],ad2[2],c2,ss[2],c3); three u4(ad1[3],ad2[3],c3,ss[3],sc);endmodulemodule t_three2;reg [3:0] ad1,ad2;reg c;wire [3:0] ss;wire sc;initialbeginad1=4'b0;forever #10 ad1=ad1+1'b1;endinitialbeginad2=4'b0;forever #80 ad2=ad2+1'b1;endinitialbeginc=4'b0;forever #640 c=c+1'b1;endthree2 text(ad1,ad2,c,ss,sc); endmodule三、实验结果:波形:四、心得:在仿真时,输出结果会有毛刺,采用以下方法可以消除毛刺(1)发现并消去互补相乘项;(2)增加乘积项以避免互补项相加;(3)输出端并联电容器。

实验四二进制计数器设计一、实验目的:(1)熟悉Verilog HDL时序电路的设计方法;(2)了解清零和使能的概念,以及同步清零和异步清零的区别;(3)用Verilog HDL 语言设计二进制计数器,并仿真;二、实验要求:计数器是最常见的寄存器逻辑电路,从微处理器的地址发生器到频率计都需要用到计数器。

一般计数器可以分为两类:加法计数器和减法计数器。

加法计数器每来一个脉冲计数值加1;减法计数器每来一个脉冲计数器值减1;有时将两者做在一起称可逆计数器。

计数器也分为自由计数器和可预置计数器。

有的计数器只有简单复位控制端,称自由计数器;有的计数器可以预置计数初值,称可预置计数器。

下面将用Verilog HDL语言设计一个带异步同步清零的二进制加法计数器。

计数器采用,有一个时钟输入端CLK,每个时钟上升沿,计数器工作。

一个同步清零端CLR,CLR=1 时,清零。

一个使能端ENA,ENA=1 时计数,ENA=0 时保持二进制输出为Q3、Q2、Q1、Q0,一位进位输出信号OUTQ。

当计数输出端Q3Q2Q1Q0=1111 时,OUTY=1。

实验步骤:(1)分析原理;(2)根据原理编写程序并进行仿真;(3)观察波形,分析仿真结果是否正确。

实验内容:一、编程实现二进制计数器并仿真:程序:module four (count, clk, reset);output [3:0] count;input clk, reset;reg [3:0] count;always @ (posedge clk or posedge reset)if (~reset)count = 4'h00;elsecount <= count + 4'h01; endmodulemodule t_four;reg clk;reg reset;wire count;parameter FAST_PERIOD = 10; initialbeginclk = 0;forever# (FAST_PERIOD/2) clk = ~clk; endparameter PERIOD = 20;initialbeginreset= 0;# PERIOD reset =1;# (10*PERIOD) reset= 0;endfour u1(count,clk,reset); endmodule三、实验结果波形:二、编程实现十进制计数器,含同异步清零端和进位输出端程序:module four(clk,rst,outy,count);input clk,rst;output count;output [3:0] outy;reg count;reg [3:0] outy;always@(posedge clk)beginif(rst)beginouty<=4'b0;count<=1'b0;endelseif(outy==4'b1001)beginouty<=4'b0;count<=1'b1;endelsebeginouty<=outy+4'b1;count<=1'b0;endendendmodulemodule t_four;reg clk;reg rst;wire count;parameter FAST_PERIOD = 10;initialbeginclk = 0;forever# (FAST_PERIOD/2) clk = ~clk;endparameter PERIOD = 20;initialbeginrst= 0;# PERIOD rst =1;# (10*PERIOD) rst= 0;endfour u1(clk,rst,count);endmodule实验结果:波形:四、心得:(1)明白了异步清零与同步清零功能的不同;(2)学会用HDL设计时序电路;(3)学会编写不同进制的计数器,加深了对HDL语言的理解和应用。