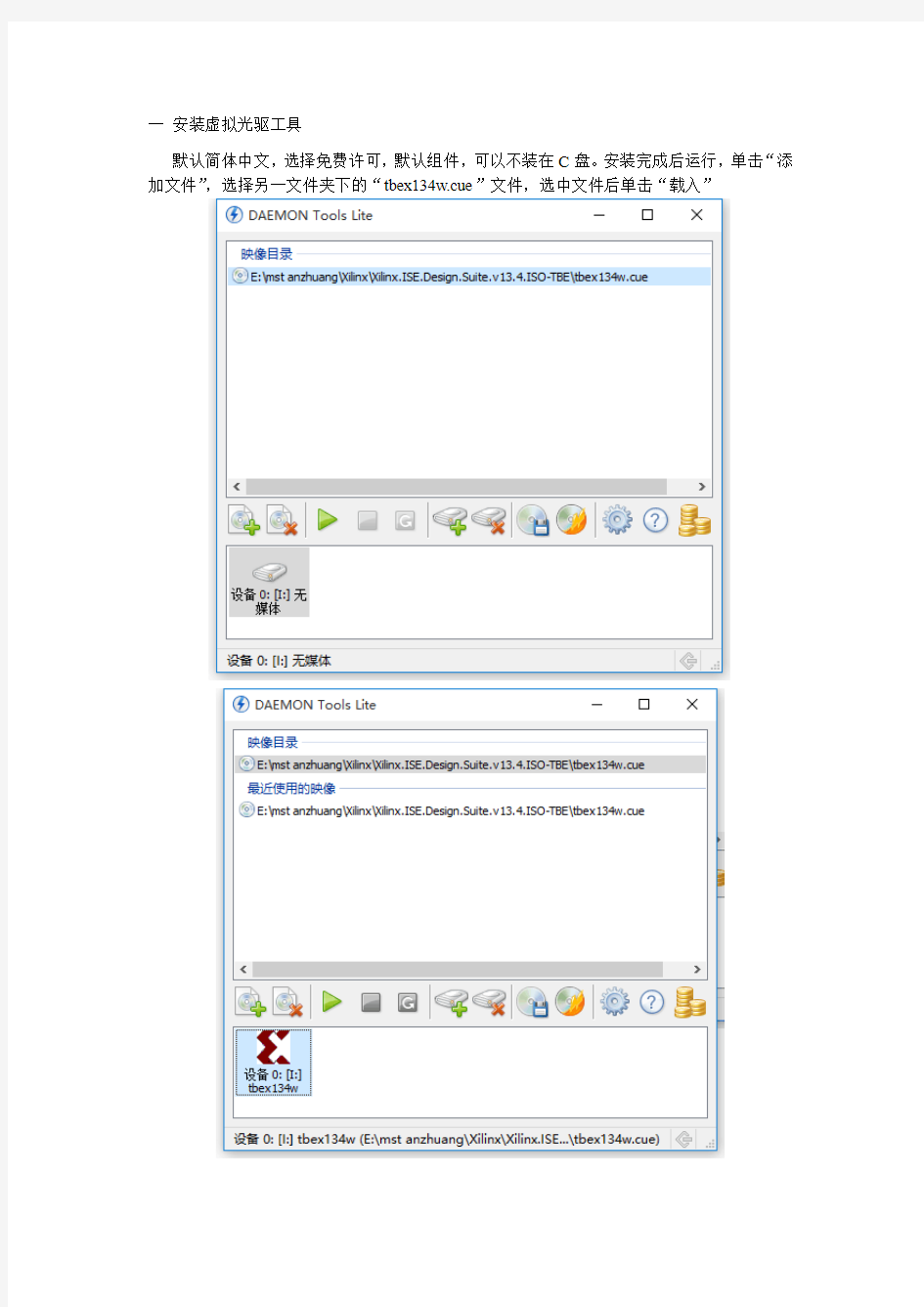

一安装虚拟光驱工具

默认简体中文,选择免费许可,默认组件,可以不装在C盘。安装完成后运行,单击“添加文件”,选择另一文件夹下的“tbex134w.cue”文件,选中文件后单击“载入”

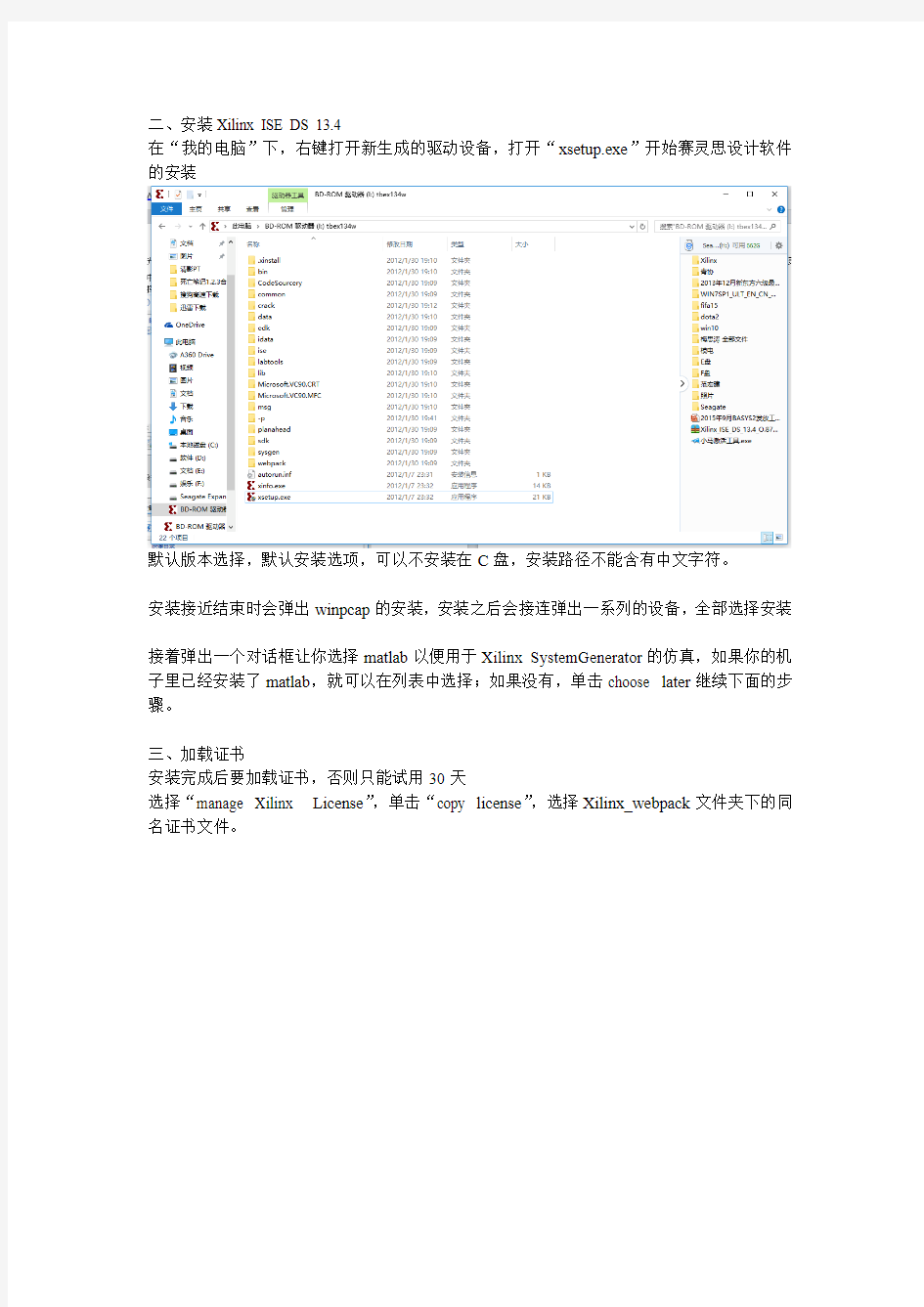

二、安装Xilinx ISE DS 13.4

在“我的电脑”下,右键打开新生成的驱动设备,打开“xsetup.exe”开始赛灵思设计软件的安装

默认版本选择,默认安装选项,可以不安装在C盘,安装路径不能含有中文字符。

安装接近结束时会弹出winpcap的安装,安装之后会接连弹出一系列的设备,全部选择安装

接着弹出一个对话框让你选择matlab以便用于Xilinx SystemGenerator的仿真,如果你的机子里已经安装了matlab,就可以在列表中选择;如果没有,单击choose later继续下面的步骤。

三、加载证书

安装完成后要加载证书,否则只能试用30天

选择“manage Xilinx License”,单击“copy license”,选择Xilinx_webpack文件夹下的同名证书文件。

运行桌面上的快捷方式,如果出现上图的情况,需要更改目标路径

E:\Xilinx\ISE_DS\settings64.bat E:\Xilinx\ISE_DS\ISE\bin\nt64\ise.exe 将前面的64改为32,删除后面的64

E:\Xilinx\ISE_DS\settings32.bat E:\Xilinx\ISE_DS\ISE\bin\nt\ise.exe 本教程完成的有些仓促,如有错误还请见谅。欢迎批评指正。

Xilinx FPGA入门连载1:ISE14.6安装 特权同学,版权所有 配套例程和更多资料下载链接: https://www.doczj.com/doc/1c13795558.html,/s/1jGjAhEm 1 安装文件拷贝与解压缩 到SP6共享网盘(链接https://www.doczj.com/doc/1c13795558.html,/s/1jGjAhEm)下的software文件夹下载ISE14.6的安装包。 随意选中前面的某个压缩包,右键单击选择“解压到当前文件夹”。 随后大约需要5-10分钟,解压才能完成。解压完成后,出现如下文件夹。

2 虚拟光驱或解压缩安装 点击进入文件夹“Xilinx.ISE.Design.Suite.14.6”,如图所示。 若用户PC安装了虚拟光驱,则使用虚拟光驱打开“XILINX_ISE_DS_14.6”进行安装。 假设用户PC没有安装虚拟光驱,则按照我们下面的步骤操作。右键单击“XILINX_ISE_DS_14.6”,选择“解压到XILINX_ISE_DS_14.6”,如图所示。 又是5-10分钟的漫长等待,谁让咱们土得连个虚拟光驱都没有捏! 3 ISE14.6安装 安装前面的步骤解压缩后,如图所示。

在着手开始安装前,建议大家把什么乱起八糟的杀毒软件都关一关,免得后面一大堆郁闷问题。 双击上图的最后一个可执行文件“xsetup”,随后便弹出了最基本的ISE安装界面,如图所示。点击右下角的“Next”进入下一步。 如图所示分别勾选“I accept …”和“I also accept…”两个选项,再点击右下角的“Next”进入下一步。

如图所示,勾选最下方的“I accept…”选项,然后点击右下角的“Next”进入下一步。 入下一步。

XilinxFPGA引脚功能详细介绍 注:技术交流用,希望对大家有所帮助。 IO_LXXY_# 用户IO引脚 XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号 2.IO_LXXY_ZZZ_# 多功能引脚 ZZZ代表在用户IO的基本上添加一个或多个以下功能。 Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。配置完成后,这些引脚又作为普通用户引脚。 D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。 D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。 An:O,A[25:0]为BPI模式的地址位。配置完成后,变为用户I/O口。 AW AKE:O,电源保存挂起模式的状态输出引脚。SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。除非SUSPEND模式被使能,AWAKE被用作用户I/O。 MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。 FCS_B:O,BPI flash 的片选信号。 FOE_B:O,BPI flash的输出使能信号 FWE_B:O,BPI flash 的写使用信号 LDC:O,BPI模式配置期间为低电平 HDC:O,BPI模式配置期间为高电平 CSO_B:O,在并口模式下,工具链片选信号。在SPI模式下,为SPI flsah片选信号。 IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。 DOUT_BUSY:O,在SelectMAP模式下,BUSY表示设备状态;在位串口模式下,DOUT 提供配置数据流。 RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平有效的写使能信号;配置完成后,如果需要,RDWR_B可以在BANK2中做为Vref。 HSW APEN:I,在配置之后和配置过程中,低电平使用上拉。 INIT_B:双向,开漏,低电平表示配置内存已经被清理;保持低电平,配置被延迟;在配置过程中,低电平表示配置数据错误已经发生;配置完成后,可以用来指示POST_CRC 状态。 SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性。 CMPMOSI,CMPMISO,CMPCLK:N/A,保留。 M0,M1:I,配置模式选择。M0=并口(0)或者串口(1),M1=主机(0)或者从机(1)。 CCLK:I/O,配置时钟,主模式下输出,从模式下输入。 USERCCLK:I,主模式下,可行用户配置时钟。 GCLK:I,这些引脚连接到全局时钟缓存器,在不需要时钟的时候,这些引脚可以作为常规用户引脚。 VREF_#:N/A,这些是输入临界电压引脚。当外部的临界电压不必要时,他可以作为

DC综合全过程及使用的命令 DC的初始化文件.synopsys.dc.setup,该文件是隐藏文件,需要用ls –a显示 读取文件 DC支持多种硬件描述格式,.db .v .vhd等 对于dcsh工作模式来说,读取不同的文件格式需要不同的参数 Read -format Verilog[db\vhdl ect] file //dcsh工作模式 对于tcl工作模式来说,读取不同文件格式使用不同的命令。

Read_db file.db //tcl工作模式读取db格式 Read_verilog file.v //tcl工作模式读取verilog格式 Read_vhdl file.v //tcl工作模式读取vhdl格式 读取源程序的另外一种方式是配合使用analyzer命令和elaborate命令; Analyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下 Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体 缺省情况下,elaborate读取的是work目录中的文件 当读取完所要综合的模块后,需要使用link命令将读到DC存储区中的模块或实体连接起来 注意:如果在使用link命令后,出现unresolved design reference的警告信息,需要重新读取该模块,或者在.synopsys_dc.setup 文件中添加link_library,告诉DC到库中去找这些模块,同时还要注意search_path中的路径是否指向该模块或单元电路所在的目录 Link命令执行后,DC就将模块按照RTL级或者门级的描述将电路连接起来,之后的各种限制条件就可以对该电路的顶层模块施加 DC限制条件施加的对象 针对以下电路成分:输入输出端口、模块、子模块的实例化、单元电路、连线及电路的引脚。在使用DC命令的时候,不要使用模糊的对象,例如,如下面的电路: Set_load 3 Clk 由于在电路中含有名称为CLK的pin、port和net,因此,DC无法知道该处的load是施加在哪个对象上,注意到一般连线会驱动负载,该命令就改为: Set_load 3 [get_nets Clk] TCL mode Set_load 3 find(net,”Clk”)dc_shell mode 路径的划分与合法路径 DC综合的时候是基于路径的优化,对于DC来说,合法的路径必须满足以下条件 路径的起点为输入端口或者是触发器的数据端 路径终点为输出端口或者是触发器的时钟端 DC设定的限制条件的值都是无单位的,这些单位都是由工艺库中给定的 可以用report_lib lib_name来查看所有在工艺库中设定的各个参数的单位 定义电路的工作环境和综合环境

《网店美工视觉设计实战教程(全彩微课版)》 教学大纲 一、课程信息 课程名称:网店美工:店铺装修+图片美化+页面设计+运营推广(全彩微课版) 课程类别:素质选修课/专业基础课 课程性质:选修/必修 计划学时:21 计划学分:2 先修课程:无 选用教材:《网店美工视觉设计实战教程(全彩微课版)》,何晓琴编著,2018年;人民邮电出版社出版教材; 适用专业:本书可作为有志于或者正在从事淘宝美工相关职业的人员学习和参考,也可作为高等院校电子商务相关课程的教材。 课程负责人: 二、课程简介 随着网店的迅速普及和全民化,衍生了“淘宝美工”这个针对网店页面视觉设计的新兴行业。本书从淘宝美工的角度出发,为淘宝卖家提供全面、实用、快速的店铺视觉设计与装修指导。主要包括网店美工基础、图片调色、图片修饰、店铺首页核心模块设计、详情页视觉设计、页面装修、视觉营销推广图制作等,最后针对无线端进行首页、详情页视觉的设计与装修。本书内容层层深入,并通过丰富的实例为读者全方面介绍淘宝美工在日常工作中所需的知识和技能,有效地引导读者进行淘宝店铺装修的学习。 本课程主要对淘宝美工的设计基础和方法进行详细介绍,通过学习该课程,使学生了解网店美工的基本要求,以及掌握网店的设计与制作。 三、课程教学要求

体描述。“关联程度”栏中字母表示二者关联程度。关联程度按高关联、中关联、低关联三档分别表示为“H”“M”或“L”。“课程教学要求”及“关联程度”中的空白栏表示该课程与所对应的专业毕业要求条目不相关。 四、课程教学内容

五、考核要求及成绩评定 注:此表中内容为该课程的全部考核方式及其相关信息。 六、学生学习建议 (一)学习方法建议 1. 理论配合实战训练进行学习,提高学生的实战动手能力; 2. 在条件允许的情况下,可以申请一个网店,进行深入学习; 3. 提高学生的是设计感和审美能力; (二)学生课外阅读参考资料 《网店美工:店铺装修+图片美化+页面设计+运营推广(全彩微课版)》,何晓琴编著,2018年,人民邮电出版社合作出版教材

《Xilinx ISE 14.2 安装指南》 1. 写在前面的话 到了这个年纪,一个人的路,总是孤独的。型号还有FPGA这一爱好,凭着自己的兴趣,不屈不饶的努力学习,不求有多大的成就,但求能给数字界贡献微薄的一份子。曾经无数的跌倒,曾经无数次的失落,曾经无数次的崩溃,尽管失去总比得到的多,这些都不重要,因为,我一直在努力,像松鼠那么努力! 光阴似箭,玩了大约3年的Altera FPGA,把它当做最亲密的伙伴的同时,我竟然开始玩弄Xilinx FPGA了。。。甚是激动。。。也许知己知彼,百战百殆,但对我而言,每一个都将是我学习的对象,也许是我的兴趣,也许是我的使命,这两者必定在我未来扮演重要的角色。尽然开始读研了,一个人的奋斗,没有找到久违的团队感,一度,我感到很孤独!虽然水平不过如此,见识还是那么的肤浅,能力还是不足,但好歹我终于找到了激情的欲望,也许拿到ZedBoard这一刻起,我又能找回方向,填补孤独的心灵了。 允许,还是老样子,我将会一步一步记录我Xilinx FPGA的学习过程,包括我的设计,思想,灵感;我会将此与Altera FPGA对照着来触摸,深化,我希望能让更多的人了解Xilinx,而不是仅仅局限于Altera FPGA。此刻开始,从新回归到菜鸟水平,“巧妇难为无米之炊”,万事开头难,在收集了一大包相关Xilinx的资料后,咱就开始安家吧—Xilinx ISE 14.2安装指南。

2. Xilinx ISE 14.2软件下载 由于偷懒,省的更换系统后又得下载对应版本的软件,在官网直接下载全功能版本,8.2G,支持Windows & Linux,网址及连接如下所示:

5.1.6 SelectIO模块 Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。 图5-24 I/O 片结构图 本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。 (1) SelectIO 的电气特性。 (2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。 (3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。 一、SelectIO IO 的电气特性 所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。支持单端I/O 标准(LVCMOS、 HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。 注意:差分输入和VREF 相关输入由VCCAUX 供电。 IOB、引脚及部逻辑的连接如图5-25 所示。 图5-25 IOB、引脚及部逻辑连接图 IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O 标准。与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。 二、SelectIO的逻辑资源 SelectIO的逻辑资源主要是指ILOGIC和OLOGIC资源,它们完成了FPGA引脚到部逻辑的连接功能,包括组合输入/输出、三态输出控制、寄存器输入/输出、寄存器三态输出控制、DDR输入/输出、DDR输出三态控制、IODELAYE1高分辨率可调整延迟单元及其控制模块。 下面简要介绍ILOGIC和OLOGIC功能。

喾林原创 Synopsys DC10.03安装配置 1、需准备安装包: 1)、Synopsys DC(design compiler)安装包 2)、SCL 安装包(注:此包为synopsys license 管理)。 3)、Synopsys 图像安装工具:installer2.0及以上均可。 (注:图形安装操作简单,不易出错,故采用图形安装界面) 4)、Synopsys license 制作工具( EFA LicGen 0.4b 和Synopsys SSS Feature Keygen )。 2、开始安装DC : 1)、启动图形安装界面 于linux 系统下解压installer2.0包(在windows 下解压文件易损坏)。解压后运行setup.sh 得如图(一)所示界面。 图 (一)

喾林原创点击“start ”有如图(二)所示界面开始安装。在“Source ”栏选中DC 安装文件所在上层目录。“Done ”后“Next ”(此次“Next ”时间较长,耐心等待)。 图 (二) 之后可一直“NEXT ”到如图(三)所示。 图 (三)

在该界面勾选linux选项即可,继续下一步到如图(四)所示。选择安装路径后继续下一步直到结束。 喾林原创 图(四) 至此DC安装结束。 3、开始安装SCL: 此安装与DC安装步骤一直,几乎没有差别,唯一不同的就是安装路径不同。 4、license的制作: License的制作是在windows下制作的。

1)、打开EFA LicGen 0.4b文件夹运行LicGen.exe程序出现如图(五)所示界面。 喾林原创 图(五) 点击“OPEN”选择Synopsys.lpd文件,“打开”。回到图(五)所示界面。勾选上Custon、Use Daemon及最后一个Custon。

1、ISE的安装 现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。 1)系统配置要求 ISE 5.2i推荐的系统配置与设计时选用的芯片有关。因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。在ISE 5.2i支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。 2)ISE 5.2i的安装 以中文版Windows XP操作系统为例加以说明。 (1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。 图4.25 ISE5.2i安装界面 (2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框 (3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框 通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。 安装完成后,环境变量应作如下描述: 若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入: 变量名:Xilinx 变量值:C:Xilinx(即安装路径) 具体设置如图4.28所示。

Spartan-3E Starter Kit Board User Guide

Chapter 1: Introduction and Overview Chapter 2: Switches, Buttons, and Knob Chapter 3: Clock Sources Chapter 4: FPGA Configuration Options Chapter 5: Character LCD Screen Chapter 6: VGA Display Port Chapter 7: RS-232 Serial Ports Chapter 8: PS/2 Mouse/Keyboard Port Chapter 9: Digital to Analog Converter (DAC) Chapter 10: Analog Capture Circuit Chapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial Flash Chapter 13: DDR SDRAM Chapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion Connectors Chapter 16: XC2C64A CoolRunner-II CPLD Chapter 17: DS2432 1-Wire SHA-1 EEPROM

Chapter 1:Introduction and Overview Spartan-3E 入门实验板使设计人员能够即时利用Spartan-3E 系列的完整平台性能。 设备支持设备支持::Spartan-3E 、CoolRunner-II 关键特性关键特性::Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner?-II (XC2C64A-5VQ44C)与Platform Flash (XCF04S-VO20C) 时钟时钟::50 MHz 晶体时钟振荡器 存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM 连接器与接口: 以太网10/100 Phy, JTAG USB 下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED 输出, 四个瞬时接触按钮, 100管脚hirose 扩展连接端口与三个6管脚扩展连接器 显示器: VGA 显示端口,16 字符- 2 线式 LCD 电源电源::Linear Technologies 电源供电,TPS75003三路电源管理IC 市场: 消费类, 电信/数据通信, 服务器, 存储器 应用: 可支持32位的RISC 处理器,可以采用Xilinx 的MicroBlaze 以及PicoBlaze 嵌入式开发系统;支持DDR 接口的应用;支持基于Ethernet 网络的应用;支持大容量I/O 扩展的应用。 Choose the Starter Kit Board for Your Needs Spartan-3E FPGA Features and Embedded Processing Functions Spartan3-E FPGA 入门实验板具有Spartan3-E FPGA 系列突出独特的特点和为嵌入式处理发展与应用提供了很大的方便。该板的特点如下: Spartan3-E 特有的特征:并行NOR Flash 配置;通过并行NOR Flash PROM 实现FPGA 的多种配置方式 嵌入式系统:MicroBlaze? 32-bit 嵌入RISC 处理器;PicoBlaze? 8-bit 嵌入控制器;DDR 存储器接口 Learning Xilinx FPGA, CPLD, and ISE Development Software Basics Spartan3-E FPGA 入门实验板比其他的入门实验板先进、复杂。它是学习FPGA 或CPLD 设计和怎样运用ISE 软件的基础。 Advanced Spartan-3 Generation Development Boards 入门实验板示范了MicroBlaze? 32-bit 嵌入式处理器和EDK 的基本运用。其更先进的地方

以.cshrc 及用户根目录下的.synopsys_vss.setup .synopsys_dc.setup 已经配置为前提)1.创建工作目录; 2.编写vhdl源程序; 3.编写.synopsys_vss.setup 和.synopsys_dc.setup文件; 4.编译vhdl源程序; 5.运行vhdldbx 仿真器; 6.运行synopsys的综合器; 7.完成综合后的门级仿真; 以一个一位加法器为例,进行具体说明(用户界面为CDE): 1)创建adder 目录: 可以在资源管理器中完成,也可以在unix环境下完成:mkdir adder; 2)在adder目录下创建work目录; 3)编写.synopsys_vss.setup文件并存入adder目录;.synopsys_vss.setup的内容如下:WORK >DEFAULT DEFAULT:work TIMEBASE = NS 4)编写一位加法器的源程序(adder1.vhd)并存入adder目录下: library ieee; use ieee.std_logic_1164.all; entity adder1 is port(din1 : in std_logic; din2 : in std_logic; cin : in std_logic; dout: out std_logic; cout: out std_logic); end adder1; architecture rtl of adder1 is begin dout <= din1 xor din2 xor cin; cout <= (din1 and din2) or (cin and (din1 xor din2)); end rtl; 5)编写一位加法器的测试基准(即test_bench)并存入adder目录下:(tb_adder1.vhd)library ieee; use ieee.std_logic_1164.all; entity tb_adder1 is end tb_adder1; architecture rtl of tb_adder1 is component adder1 is port(din1 : in std_logic; din2 : in std_logic; cin : in std_logic;

从网上下载测试版软件华中科技大学ftp:211.69.207.25下载 ModelSim.SE.v6.0 仿真工具 Xilinx.ISE.v6.3i.Incl.Keymaker- foundation安装软件 Xilinx.ISE.v6.3i.VIRTEX.VIRTEXE.Addon- foundation库文件1 Xilinx.ISE.v6.3i.VIRTEX.VIRTEXE.Addon.Addon- foundation库文件2 SYNPLICITY_SYNPLIFY_PRO_V7.7 foundation器件综合软件 一、ModelSim.SE.v6.0的安装 双击图标进行安装,然后双击keygenerate产生文件license.dat文件。将其拷贝到modelsim安装的文件夹下。单击我的电脑,在右键中修改环境变量。 加入环境变量LM_LICENSE_FILE,变量值为C:/Modeltech_6.0/license.dat 则modelsim安装成功.还需在modelsim安装的文件夹下拷贝已经编译好的一些库文件,为其后面的处理作好准备,三个库文件为XilinxCoreLib_ver、unisims_ver、simprims_ver。 进入ModelSIM安装文件夹,找到一个名为ModelSIM.ini的文件,将其属性由只度改为存档,在[Library]段的最后加上simprims_ver = $MODEL_TECH/../simprims_ver XilinxCoreLib_ver= $MODEL_TECH/../XilinxCoreLib_ver unisims_ver= $MODEL_TECH/../unisims_ver 目的是让ModelSIM运行时可以自动加载编译好的库文件。 二、Xilinx.ISE.v6.3i.Incl.Keymaker的安装 双击其安装软件进行安装,光盘里有两张光盘,和一个ID产生器,安装两个光盘时,要使用同一个ID。 将Xilinx.ISE.v6.3i.VIRTEX.VIRTEXE.AddXilinx .ISE .v6.3i.VIRTEX.VIRTEXE.Addon.Add 分别解压缩,将解压缩得到的文件夹拷贝到Xilinx安装的目录下(第二个文件只需拷贝最後一个文件) ISE6.2的安装,大体一致,记得有选择set/update时全选,不然有些功能无法适用,至于升级,打开edit后,在perference中去掉就可以了。 如果你装了防火墙,如天网、瑞星,第一次启动时,要一直允许ise访问网络,不然会抱错的。 经试验,最好安装在winXP系统下。 三、SYNPLICITY_SYNPLIFY_PRO_V7.7的安装 将其完全解压后进行安装,其中的license要选择使用本机的license,然后用解压后的 license.txt覆盖SYNPLICITY目录下的license,用解压后的覆盖 Synplicity\Synplify_77\bin\mbin目录下的同名文件。 发现环境变量改变为SYNPLICITY_LICENSE_FILE,变量值为C:\Synplicity\license.txt。软件整体安装成功!

Xilinx FPGA配置的一些细节 2010年07月03日星期六 14:26 0 参考资料 (1) Xilinx: Development System Reference Guide. dev.pdf, v10.1 在Xilinx的doc目录下有。 (2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005 在Xilinx网站上有,链接 (3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007 在Xilinx网站上有,链接 注:此外xapp139和xapp151也是和配置相关的。 (4)Xilinx: Virtex-4 Configuration Guide. UG071 (v1.5) January 12, 2007 (5) Tell me about the .BIT . 链接: 1 Xilinx配置过程 主要讲一下Startup Sequence。 Startup Sequence由8个状态组成. 除了7是固定的之外,其它几个的顺序是用户可设置的,而且Wait for DCM和DCI是可选的。 其中默认顺序如下: 这些在ISE生成bit文件时通过属性页设定。 这几个状态的具体含义如下: Release_DONE : DONE信号变高 GWE : 使能CLB和IOB,FPGA的RAMs和FFs可以改变状态 GTS : 激活用户IO,之前都是高阻。

设置启动dc_shell-t工具的 .synopsys.setup文件 Author:周建伟 Company:西安邮电大学SOC组 Date:2013.10.30 摘要:若你在读不进你的库,即在你的运行报告中总是有:warning:Can?t read link_library file …your_library.db?,这边文档会对你有一定的帮助

逻辑综合环境 启动文件 启动文件用来指定综合工具所需要的一些初始化信息。DC使用名为“.synopsys_dc.setup”的启动文件(位置:inst_dir/admin/setup/.synopsys_dc.setup)。启动时,DC会以下述顺序搜索并装载相应目录下的启动文件: DC安装目录($DC_PATH/admin/setup) 用户主目录 工具启动目录 注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置 本文档重在讲述怎么设置工具启动目录 1、把inst_dir/admin/setup/.synopsys_dc.setup文件拷贝到你DC脚本目录下(也就是和你 脚本在同个目录下) 2、在.synopsys_dc.setup文件的第92行,即set link_force_case “check_reference”命令下 修改内容如下: A、set lib_path /library/smic18/feview~2/version2.2(注:lib_path为你smic18库安装 目录,不同于DC安装目录) B、set link_library [list * $lib_path/STD/Synopsys/smic18_ss.db \ $lib_path/IO/Synopsys/smic18IO_line_ss.db \ $lib_path/IO/Synopsys/smic18IO_stagger_ss.db ] C、set search_path [list . ${synopsys_root}/libraries/syn ${synopsys_root}/dw/syn_ver \ ${synopsys_root}/dw/sim_ver \ $lib_path/STD/Synopsys $lib_path/IO/Synopsys ] D、set target_library [list $lib_path/STD/Synopsys/smic18_ss.db \ $lib_path/IO/Synopsys/smic18IO_line_ss.db \ $lib_path/IO/Synopsys/smic18IO_stagger_ss.db ] E、set synthetic_library “” set command_log_file “./command.log” set designer “zjw” set company “soc of xupt”

Spartan-3平台与ISE软件的入门 一、快速浏览Spartan-3E Starter Kit的用户指南,便于以后进行内容查找。 中文用户指南:Spartan-3E Starter Kit Board User Guide.mht 英文用户指南:Spartan-3E Starter Kit Board User Guide.pdf 二、ISE软件安装。 根据资料自学完成安装(在个人电脑上),ISE推荐版本:14.7。注意需要破解(即提供license)。 三、ISE软件的初次使用。 在Spartan-3E开发板上,使用ISE软件,完成一个最基本工程的建立、编程、仿真、下载实现。 3.1 1)运行ISE Design Suite软件,界面如下

File New Project a)设置顶层文件类型Top-level source type为Schematic(原理图)

b)选择工程的保存位置Location和工作目录Working Directory 为fpgaxunlian c)为工程取名,如:xunlian1 点击Next 进行下述设置

根据观察我们使用的Spartan 3E开发板上的FPGA芯片上的字,可知目标FPGA芯片的属性如下 芯片系列(Family):Spartan3E 芯片型号(Device):XC3S500E 芯片封装(Package):FG320 速度等级(Speed):-4(注:XILINX的FPGA,值越大,速度等级越高) 综合工具(Systhesis Tool)选择ISE自带的XST 仿真工具(Simulator)选择ISE自带的Isim 编程语言(Preferred Language)选择Verilog 然后,点击Next

0 前言 一套完整的FPGA设计流程包括电路设计输入、功能仿真、设计综合、综合后仿真、设计实现、添加约束、布线后仿真和下载、调试等主要步骤。 图1 FPGA设计流程 目前赛灵思公司FPGA设计软件的最新版本是ISE 13,由于笔者暂未用到该版本,本文中以ISE 12.4为例。 ISE 9以后的版本的安装文件都是集成到了一个包当中,安装起来很方便。软件包里面包含四个大的工具,ISE Design Tools、嵌入式设计工具EDK、PlanAhead、Xtreme DSP设计工具System Generator。ISE设计工具中包含ISE Project Navigator、ChipScope Pro 和以下工具: 图2 ISE软件包中部分工具 做一般的FPGA逻辑设计时只需要用到ISE设计工具,下面通过一个最简单的“点亮LED 灯”实例,具体讲解ISE设计工具的使用,并介绍基于ISE的FPGA设计基本流程。 1 创建工程 (1)在桌面快捷方式或开始→所有程序→Xilinx ISE Design Suite 12.4→ISE Design Tools中打开ISE Project Navigator。 (2)单击File→New Project...出现下图所示对话框。

图3 新建工程对话框 在该界面输入工程名、选择工程存放路径、选择顶层模块类型,其中顶层模块类型有硬件描述语言(HDL)、原理图(Schematic)、SynplifyPro默认生成的网表文件(EDIF)、Xilinx IP Core和XST生成的网表文件(NGC/NGO)这四种选项,这里我们使用Verilog模块作为顶层输入,所以选HDL。 (3)单击Next >进入下一步,弹出下图所示对话框。

光盘放进DVD光驱,等待其自动运行(如果没有自动运行,直接执行光盘目录下的Setup.exe文件程序即可),会弹出图4-1所示的欢迎界面,点击“Next”进入下一页。 图4-1 ISE安装过程的欢迎界面 2.接着进入注册码获取、输入对话框,如图4-2所示。注册码可以通过网站、邮件和传真方式申请注册码。如果已有注册码,输入后单击“Next”按键后继续。

图4-2 ISE9.1安装程序的注册码输入界面 购买了正版软件后,最常用的方法就是通过网站注册获取安装所需的注册码。首先在Xilinx的官方主页 https://www.doczj.com/doc/1c13795558.html,上建立自己的帐号,然后点击图4-1中的“Website”按键,登陆帐号,输入CD盒上的产品序列号(序号的格式为:3个字符+9个数字),会自动生成16位的注册码,直接记录下来即可,同时Xilinx网站会将注册码的详细信息发送到帐号所对应的邮箱中。 3.下一个对话框是Xilinx软件的授权声明对话框,选中“I accept the terms of this software license”,单击“Next”后进入安装路径选择界面,如图4-3所示。单击“Browse”按键后选择自定义安装路径,单击“Next”按键继续 图4-3 ISE软件安装路径选择对话框 4.接下来的几个对话框分别是选择安装组件选择,如图4-4所示,用户需要选择自己使用的芯片所对应的模块,这样才能在开发中使用这些模块。在计算机硬盘资源不紧张的情况下,通常选择“Select All”。

图4-4 ISE安装组件选择界面 评论[支持者: 0 人,反对者: 0 人,中立者: 0 人] 查看评论信息 2008-11-26 20:53:00 第3楼 小大 个性首页| QQ 5.随后进入设置环境变量页面,保持默认即可。如果环境变量设置错误,则安装后不能正常启动ISE。选择默认选项,安装完成后的环境变量,其值为安装路径。最后进入安装确认对话框,单击Install按钮,即可按照用户的设置自动安装ISE,如图4-5所示

Step1 学习下载配置Xilinx 之FPGA 配合Mars-EDA 的Spartan2 核心板,用图文方式向大家详细讲述如何下载配置Xilinx 的FPGA。 FPGA 下载模式说明 S1 为 FPGA 下载模式选择跳线,M0,M1,M2 默认状态为通过 4.7K 电阻上拉到 3.3V,当用跳线帽短接 S1 的PIN3 和PIN6 将置 M0 为0,同理,短接 PIN2 和PIN5,PIN3 和PIN4 将置 M1,M2 为0。M0,M1,M2 的电平和 FPGA 下载之间的关系参见下图:(Boundary-scan mode)是调试最常用的 JTAG 模式。当采用板载 PROM 时,采用的跳线模式是 Master Serial Mode –短路 PIN1 和PIN6,PIN2 和PIN5 J2 为Slave Serial Mode 的接口。下载模式跳线 S1 短接PIN1 和PIN6,PIN2 和PIN5 即可。 J3 为 JTAG Mode 的接口。下载模式跳线短接 PIN1 和 PIN6 即可。

S2 跳线说明 1.通过 JTAG 方式烧录 FPGA:短接 PIN1 和PIN3。 2.通过 JTAG 方式烧录 PROM:短接 PIN3 和PIN5,PIN2 和PIN4. 3.通过菊花链下载 FPGA 和烧录 PROM:短接 PIN3 和PIN5,PIN4 和PIN6. 下面我们利用 Spartan2 核心板介绍一下通过 JTAG 菊花链方式下载 FPGA 和烧录 PROM. 硬件跳线选择: 1.跳线 S1: 此时要求 M0 M1 M2 = 100, 设置 FPGA 的下载方式为 Boundary-scan mode, 此时将 M1 和M2 的跳线安上。 跳线 S2 : 通过菊花链下载 FPGA 和烧录 PROM:短接 PIN3 和 PIN5,PIN4 和 PIN6. 2.将 Xilinx 下载线和核心板上 JTAG mode 接口 J3 相连,连接到计算机并口。核心板上电。

注:技术交流用,希望对大家有所帮助。 IO_LXXY_# 用户IO引脚 XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号 2.IO_LXXY_ZZZ_# 多功能引脚 ZZZ代表在用户IO的基本上添加一个或多个以下功能。 Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。配置完成后,这些引脚又作为普通用户引脚。 D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。 D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。 An:O,A[25:0]为BPI模式的地址位。配置完成后,变为用户I/O口。 AWAKE:O,电源保存挂起模式的状态输出引脚。SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。除非SUSPEND模式被使能,AWAKE被用作用户I/O。 MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。 FCS_B:O,BPI flash 的片选信号。 FOE_B:O,BPI flash的输出使能信号 FWE_B:O,BPI flash 的写使用信号 LDC:O,BPI模式配置期间为低电平 HDC:O,BPI模式配置期间为高电平 CSO_B:O,在并口模式下,工具链片选信号。在SPI模式下,为SPI flsah片选信号。 IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。