安徽大学2008—2009学年第二学期

《数字电子技术》考试试卷(A 卷)

(闭卷 时间120分钟)

一、填空题(每空2分,共20分) 1、CMOS 逻辑门电路是目前应用最广泛的逻辑门电路。其优点是集成度高,_________________,扇出数大,噪声容限亦大,开关速度较高。

2、TTL 反相器的输入级由BJT 构成,输出级采用推拉式结构,其目的是为了________________和增强带负载的能力。

3、在数字电路中,不论哪一种逻辑门电路,其中的关键器件是MOS 管或BJT ,它们均可以作为___________器件。

4、逻辑门电路的主要技术参数有输入和输出高、低电平的最大值或最小值,传输延迟时间,功耗,________________,扇入数和扇出数。

5、锁存器和触发器都是具有存储功能的逻辑电路,是构成时序电路的基本单元,每个锁存器或触发器都能存储_______位二值信息。

6、触发器是对时钟脉冲____________敏感的电路。

7、当一个逻辑门的两个输入端的信号同时向相反方向变化,而变化的时间有差异的现象称为竞争,由竞争而可能产生输出干扰的现象称为___________。

8、在逻辑体制中有正、负逻辑的规定,正负逻辑可以等效变换,对于正逻辑的“与非”功能,变换成负逻辑相当于“______________”功能。 9、时序逻辑电路分为同步时序和_____________两大类。

10、同步时序电路的设计,首先根据逻辑功能的需求,导出原始状态图或原始状态表,有必要时需进行_______________,继而对状态进行编码,然后根据状态表导出激励方程组和输出方程组,最后画出逻辑图完成设计任务。

院/系 年级 专业 姓名 学号

答 题 勿 超 装 订 线 ------------------------------装------------------------------------

---------订----------------------------------------线----------------------------------------

2、用卡诺图法化简逻辑式F(A,B,C,D)=∑m (0,2,4,5,6,7,12)+∑d (8,10)。 解:

四、分析题(第一题5分,第二题10分,第三题15分,共30分)

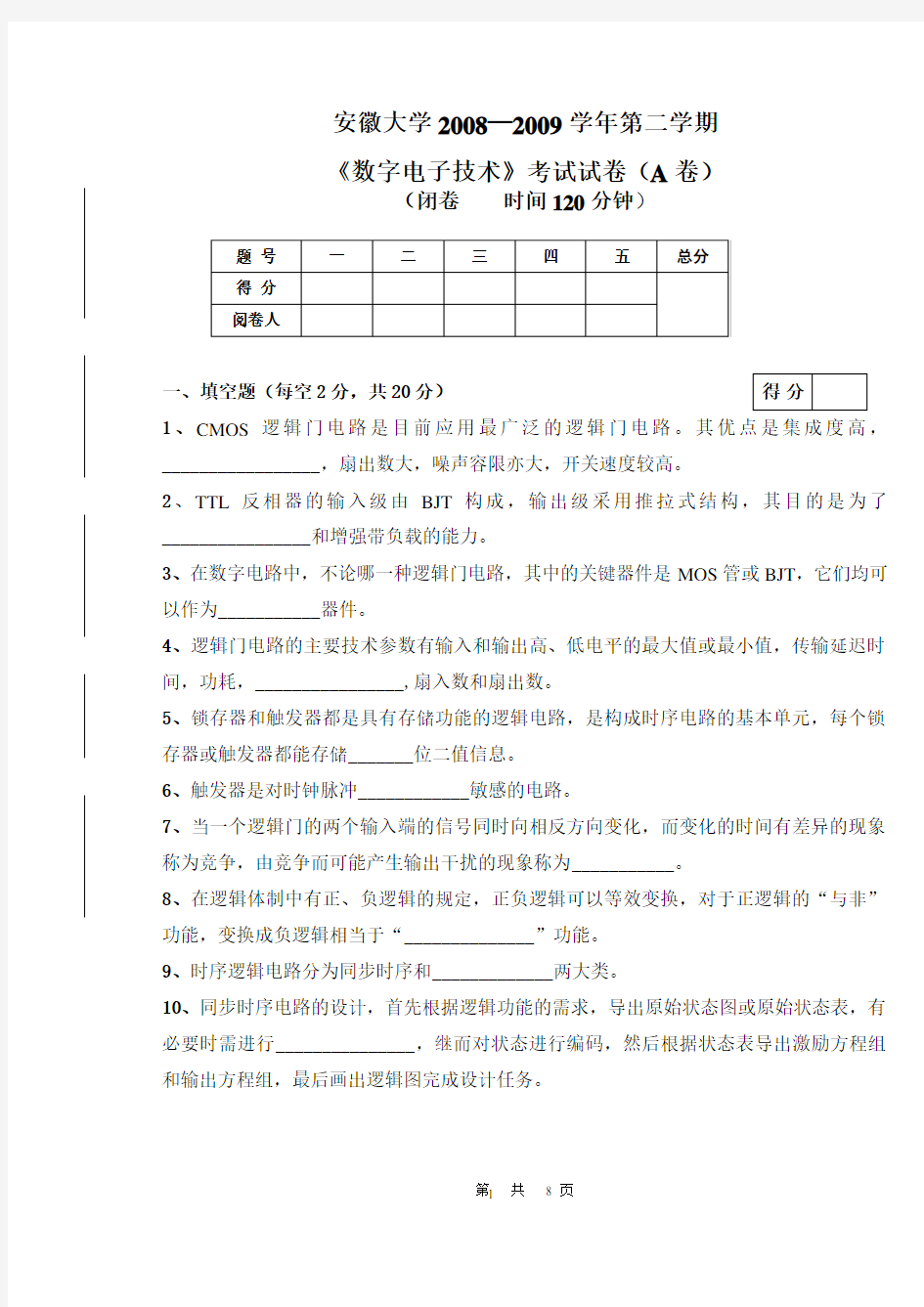

1、TTL 三态门如图3所示。在图示输入波形的情况下,画出其输出端L 的波形。

图3

A

B

C

解: L

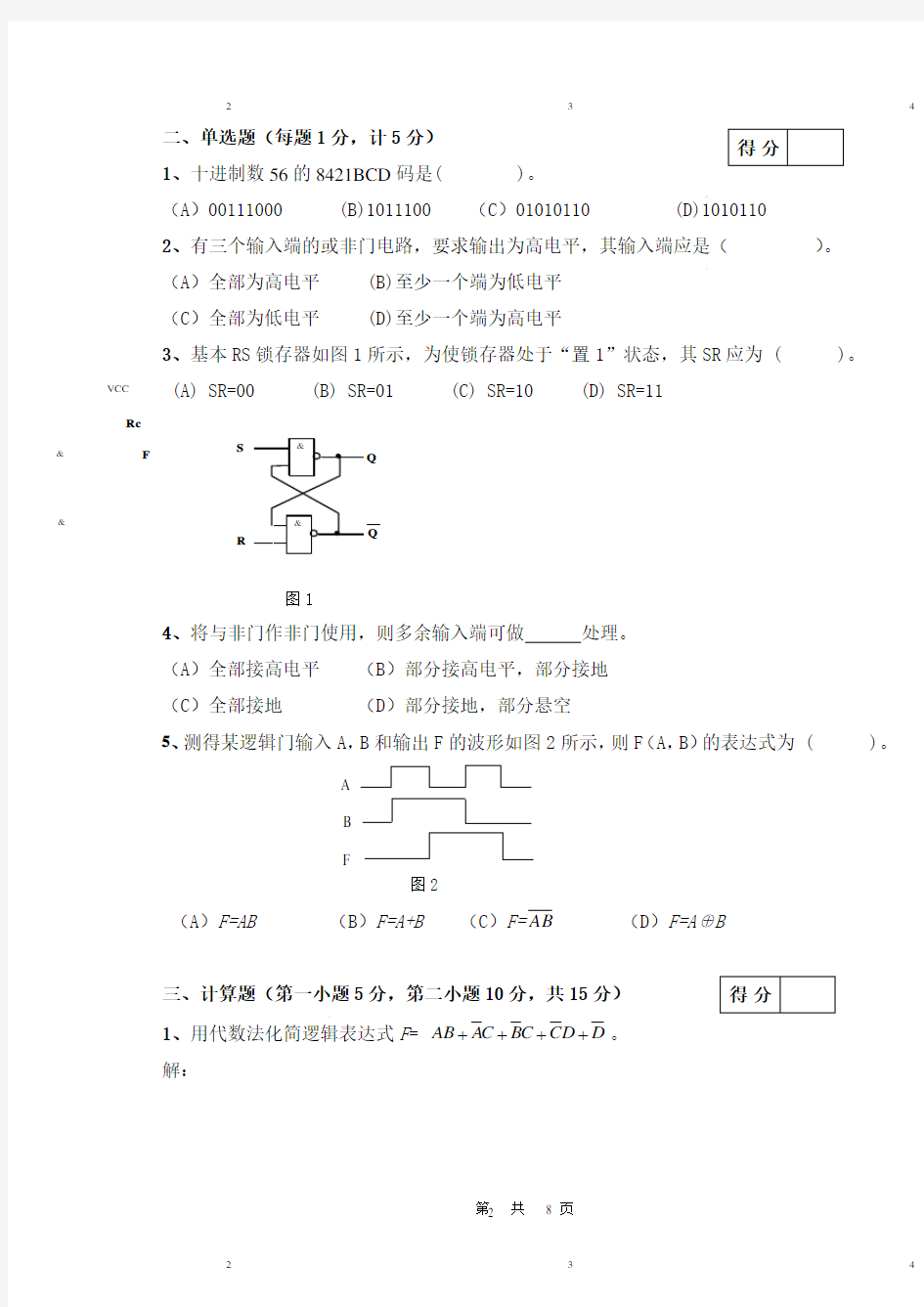

2、用74138构成一个多功能组合逻辑电路,如图4所示。电路中,X 为功能选择输入信号,a 和b 为输入逻辑变量,L 为输出信号。

(1)试写出电路输出函数L 的逻辑表达式。

(2)如果功能选择输入信号X 取“0”,则此电路的功能是什么? 其中:i i m E E E Y 123= ΛA B C m A B C m ==10,

A A

B B C

C

院/系 年级 专业 姓名 学号

答 题 勿 超 装 订 线 ------------------------------装---------------------------------------------订----------------------------------------线----------------------------------------

图4

解:

3、电路如图5所示。(1)写出各触发器驱动方程;(2)写出触发器特性方程;(3)导出电路的状态表;(4)画出电路状态图;(5)画出时序图(设电路初始状态为000);(6)说明电路是否可以自启动。

图5

解:

五、设计题(每小题10分,共30分)

1、某雷达站有3部雷达A 、B 、C ,其中雷达A 和B 工作时消耗的功率相等,雷达C 消耗

的功率是雷达A 的两倍。这些雷达由两台发电机X 和Y 供电,发电机X 的最大输出功率

等于雷达A 的功率消耗,发电机Y 的最大输出功率是X 的3倍。要求设计一个逻辑电路,

能够根据各雷达的启动和关闭信号,以最节约电能的方式启、停发电机;并用与非门实现

该逻辑电路。

院/系 年级 专业 姓名 学号

答 题 勿 超 装 订 线 ------------------------------装---------------------------------------------订----------------------------------------线----------------------------------------

解:

2、试用两片74 LVC 161,采用反馈清零法设计四十四进制计数器。

表1:74LVC161逻辑功能表

×

××××××进

预*

数

计

×

×

×

×

↑

H

H

H

H

*持保×××××L ×H H *持保×××××L H H *D 0

D 1D 2D 3

D 0D 1D 2D 3↑×L H L L L L L ×××L TC Q 0Q 1Q 2Q 3D 0D 1D 2D 3CP CET

CEP

位计数预置数据输入时钟使能

置清零

输出输

入

解:

3、555定时器电路如图6所示,试用其产生一振荡频率50f Hz =,占空比为60%的周期

脉冲信号,现有10C F μ=的电容,画出电路图并确定电路中电阻值。

图6

解: .

答 题 勿 超 装 订 线 ------------------------------装--------------------------------------------订----------------------------------------线----------------------------------------