差分放大器AD813x常见问题解答

问题:如何计算差分放大器电路的增益,如何分析差分放大器电路?

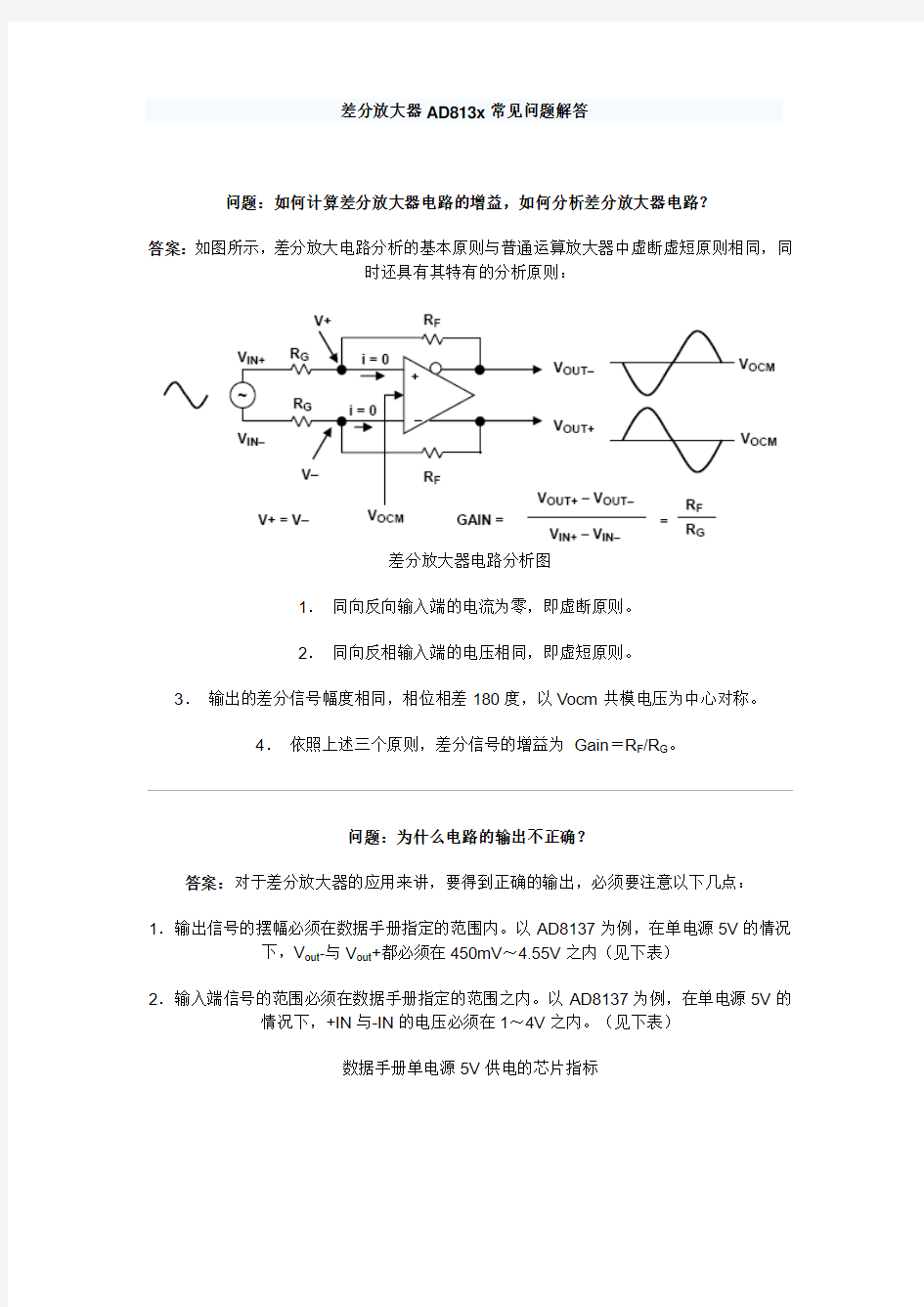

答案:如图所示,差分放大电路分析的基本原则与普通运算放大器中虚断虚短原则相同,同

时还具有其特有的分析原则:

差分放大器电路分析图

1.同向反向输入端的电流为零,即虚断原则。

2.同向反相输入端的电压相同,即虚短原则。

3.输出的差分信号幅度相同,相位相差180度,以Vocm共模电压为中心对称。

4.依照上述三个原则,差分信号的增益为Gain=R F/R G。

问题:为什么电路的输出不正确?

答案:对于差分放大器的应用来讲,要得到正确的输出,必须要注意以下几点:

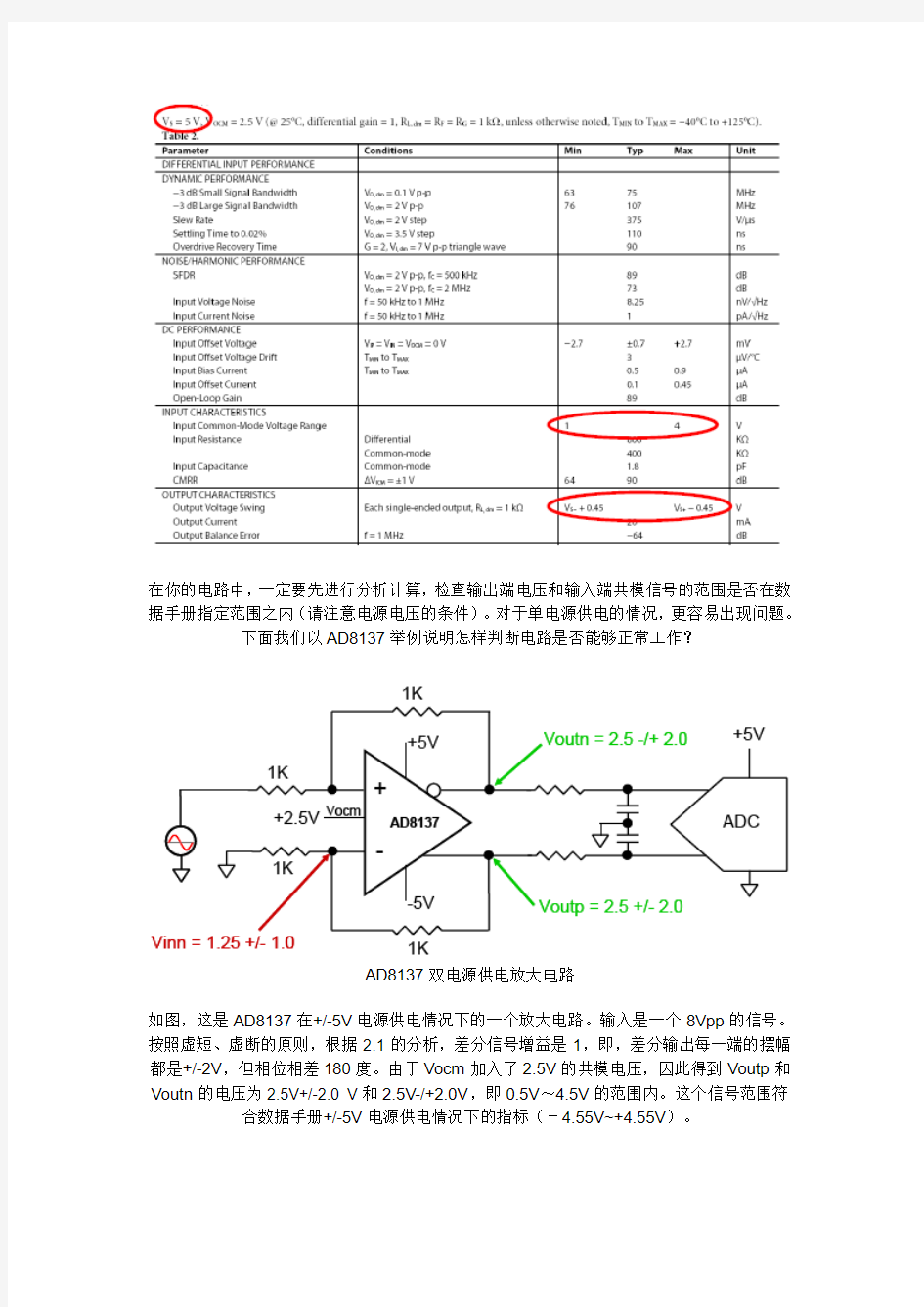

1.输出信号的摆幅必须在数据手册指定的范围内。以AD8137为例,在单电源5V的情况下,V out-与V out+都必须在450mV~4.55V之内(见下表)

2.输入端信号的范围必须在数据手册指定的范围之内。以AD8137为例,在单电源5V的情况下,+IN与-IN的电压必须在1~4V之内。(见下表)

数据手册单电源5V供电的芯片指标

在你的电路中,一定要先进行分析计算,检查输出端电压和输入端共模信号的范围是否在数据手册指定范围之内(请注意电源电压的条件)。对于单电源供电的情况,更容易出现问题。

下面我们以AD8137举例说明怎样判断电路是否能够正常工作?

AD8137双电源供电放大电路

如图,这是AD8137在+/-5V电源供电情况下的一个放大电路。输入是一个8Vpp的信号。按照虚短、虚断的原则,根据2.1的分析,差分信号增益是1,即,差分输出每一端的摆幅都是+/-2V,但相位相差180度。由于Vocm加入了2.5V的共模电压,因此得到Voutp和Voutn的电压为2.5V+/-2.0 V和2.5V-/+2.0V,即0.5V~4.5V的范围内。这个信号范围符合数据手册+/-5V电源供电情况下的指标(-4.55V~+4.55V)。

然后我们计算输入端的共模电压,按照虚短、虚断的原则,Vinn的电压是Voutp在两个1K ohm电阻上面的中点分压,即得到如图红色所示的共模电压为Vinn=1.25V+/-1.0V,即0.25V~2.25V,这也符合+/-5V供电下数据手册对输入共模电压的要求(-4V~+4V)。所

以此电路满足要求,会正确工作。下图是各点的波形。

AD8137双电源供电电路各点波形

但是,如果上面的电路改为单电源5V供电,电路就会有问题。如下图所示,

AD8137单电源供电电路

所有的分析都同双电源供电相同,我们会发现输出电压的范围0.5V~4.5V符合数据手册在单电源+5V供电情况下的指标450mV~4.55V,但是输入端共模电压的范围0.25V~2.25V

却超出了数据手册的要求(1~4V)。所以,在这种情况下,得到的输出如下图,信号已经

发生失真。

AD8137单电源供电情况下错误的输出

在这种情况下,可以试着调节Vocm端的值(请注意,Vocm端加入的电压范围也有要求,请参见数据手册),或者改变电路增益,或者减小输入信号的幅值,使输入端和输出端的范

围都满足要求。

前面的情况是输入信号中不含直流共模成分,当输入信号含有直流偏置时,也要注意输入端

和输出端的电压范围。下面是一个例子。

AAD8137 输入信号偏置在1V DC的电路

如上图所示,此图的区别在于输入信号有一个1V的直流偏置。这样我们以同样的方法分析电路,这个1V的输入会在两个输出端各加入0.5V的直流正负偏置。得到如图所示的输入端的电压和输出端的电压值,我们看到此时V outp端的电压1V~5V已经超出了规定的-

4.55V~+4.55V范围。所以得到的结果如下图所示

AD8137输入加入1V DC偏置的错误结果

解决的方法是可以使用交流耦合,如下图

使用交流耦合的AD8137放大电路

这样,输入端和输出端的范围都正确了。结果如下图所示

采用交流耦合后正确的结果

所以在使用AD813x时,一定要先计算各点的电压,然后与数据手册上相同供电电源电压条件下的指标相比较,确定电路是否工作正常。另外一个电路检查的方法是使用ADI网站上提供的SPICE模型进行仿真,这样更加直观。同时ADI网站上还提供了在线的AD813X 差分放大器辅助计算工具,可以帮你检查电路的正确性。

这个工具的链接是

https://www.doczj.com/doc/1512006767.html,/zh/amplifiers-and-comparators/differential-amplifiers/AD8138/pro

ducts/product.html。

问题:单端输入时的端接问题?

答案:在高速应用中,有必要对差分放大器进行端接。如下图所示,信号源阻抗为50Ω,

峰峰值为2V,我们希望输出为1V。

根据单端输入时输入阻抗计算公式,差分电路的输入阻抗实际是267Ω。因此,我们要用267Ω负载匹配50Ω的信号源,计算可知,需要对地接61.9Ω的电阻,如下图所示。

上图中,将虚线框中的电路做戴维南等效,如图中绿色电路。可以看出,源电压是1.1V而不是1V,同时,28Ω电阻与200Ω电阻串联,这增加了RG,即降低了增益。

上图中,为使两个反馈环匹配,在反向端增加28Ω的电阻,以保持反馈比相同。同时,为了得到1V的电压输出,将两个反馈电阻改为205Ω。

高速差分ADC驱动放大器AD8137及其应用

慧聪网 2006年1月18日11时30分信息来源:国外电子元器件

AD8137是ADI公司推出的轨对轨输出低成本全差分高速放大器,它具有低噪声、低失真和宽动态范围,可用于驱动12位ADC,非常适用于要求低成本和低功耗的系统。AD8137采用ADI公司新一代的XFCB双极型制造工艺,内部的共模反馈结构使之可以通过施加于一个引脚上的电压来控制其输出的共模电压。AD8137内部的反馈环可实现平衡输出,同时还可以抑制偶次谐波失真。利用AD8137很容易实现全差分和单端-差分结构,在典型连接下,四只电阻器组成的外部反馈网络可决定放大器的闭环增益,这一点使其具有极大的灵活性。

点击此处查看全部新闻图片

1 AD8137的主要特点

AD8137具有以下主要特点:

·全差分;

·外部增益可调;

·输出共模电压可调;

·输入偏移电压和电流很低;

·具有110MHz的大信号带宽和450V/μs的转换速率;

·轨对轨输出;

·电源电压低且具有掉电特性;

·5V供电时的静态电流只有2.6mA,待机模式时为450μA;

·全差分和单端-差分两种工作方式;

·电源电压范围为3V~12V。

图1是AD8137的8脚SOIC封装图。

2 器件工作原理

点击此处查看全部新闻图片

AD8137含内部共模参考电压的共模电路以及偏置关断电路,其原理框图如图2所示。AD8137的输入跨导部分是一个H桥,它的输出电流镜像到高阻结点CP和CN。输出部分是传统的H桥驱动电路,带着普通的发射装置驱动结点+OUT和-OUT。

AD8137采用两个反馈环来分别控制差模和共模反馈。它的差模增益由外部电阻决定,这与传统放大器一样。而输出共模电压则由一个受外部Vocm输入控制的内部反馈环决定。这样的结构使其可以很容易地任意设定输出的共模电压,而不影响放大器的差模增益。

在共模反馈环中,共模反馈放大器ACM用来对输出共模电压进行采样,然后通过负反馈迫使输出的共模电压等于VOCM引脚输入的电压。也就是说,在反馈环的作用下,输出共模电压向Vocm处的输入电压变化。通常情况下,内部偏置发生器设定Vocm的值约为电源电压的一半,因此,在Vocm输入浮置时,输出共模电压约为电源电压的一半。由于内部偏置发生器的源阻抗比较大,因此,如有输出阻抗相对较小的外部电源电压,那么,它将代替Vocm输入到AD8137上。

点击此处查看全部新闻图片

3 AD8137的应用

图3是AD8137的一个典型连接电路,该电路采用外部RF/RG匹配网络。其差分输入端VAP和VAN作为求和点,加到VOCM端的外部参考电压可决定输出共模电压。同时,两个输出端以平衡方式输出的VOP和VON与其输入信号相对应。

应当说明的是,在一些单端-差分转换的应用中,如果采用单电源电压供电,设计时必须注意放大器输入端上共模电压VACM的动态范围。

此外,当AD8137输入电路呈现的输入阻抗与终端电阻器串联时,必须考虑它的负载效应,即单端输入时的阻抗匹配问题。

目录 1. 设计指标 (1) 2. 运算放大器主体结构的选择 (1) 3. 共模反馈电路(CMFB)的选择 (1) 4. 运算放大器设计策略 (2) 5. 手工设计过程 (2) 5.1 运算放大器参数的确定 (2) 5.1.1 补偿电容Cc和调零电阻的确定 (2) 5.1.2 确定输入级尾电流I0的大小和M0的宽长比 (3) 5.1.3 确定M1和M2的宽长比 (3) 5.1.4确定M5、M6的宽长比 (3) 5.1.5 确定M7、M8、M9和M10宽长比 (3) 5.1.6 确定M3和M4宽长比 (3) 5.1.7 确定M11、M12、M13和M14的宽长比 (4) 5.1.8 确定偏置电压 (4) 5.2 CMFB参数的确定 (4) 6. HSPICE仿真 (5) 6.1 直流参数仿真 (5) 6.1.1共模输入电压范围(ICMR) (5) 6.1.2 输出电压范围测试 (6) 6.2 交流参数仿真 (6) 6.2.1 开环增益、增益带宽积、相位裕度、增益裕度的仿真 (6) 6.2.2 共模抑制比(CMRR)的仿真 (7) 6.2.3电源抑制比(PSRR)的仿真 (8) 6.2.4输出阻抗仿真 (9) 6.3瞬态参数仿真 (10) 6.3.1 转换速率(SR) (10) 6.3.2 输入正弦信号的仿真 (11) 7. 设计总结 (11) 附录(整体电路的网表文件) (12)

采用折叠式结构的两级全差分运算放大器的设计 1. 设计指标 5000/ 2.5 2.551010/21~22v DD SS L out dias A V V V V V V GB MHz C pF SR V s V V ICMR V P mW μ>==?== >=±=?≤的范围 2. 运算放大器主体结构的选择 图1 折叠式共源共栅两级运算放大器 运算放大器有很多种结构,按照不同的标准有不同的分类。从电路结构来看, 有套筒 式共源共栅、折叠式共源共栅、增益提高式和一般的两级运算放大器等。本设计采用的是如图1所示的折叠式共源共栅两级运算放大器,采用折叠式结构可以获得很高的共模输入电压范围,与套筒式的结构相比,可以获得更大的输出电压摆幅。 由于折叠式共源共栅放大器输出电压增益没有套筒式结构电压增益那么高,因此为了得到更高的增益,本设计采用了两级运放结构,第一级由M0-M10构成折叠式共源共栅结构,第二级由M11-M14构成共源级结构,既可以提高电压的增益,又可以获得比第一级更高的输出电压摆幅。 为了保证运放在闭环状态下能稳定的工作,本设计通过米勒补偿电容Cc 和调零电阻Rz 对运放进行补偿,提高相位裕量! 另外,本文设计的是全差分运算放大器,与单端输出的运算放大器相比较,可以获得更高的共模抑制比,避免镜像极点及输出电压摆幅。 3. 共模反馈电路(CMFB )的选择 由于采用的是高增益的全差分结构,输出共模电平对器件的特性和失配相当敏感,而且不能通过差动反馈来达到稳定,因此,必须增加共模反馈电路(CMFB )来检测两个输出端

第九章集成运算放大器及其应用(易映萍) 9.1 差分放大电路 9.2互补功率放大电路 9.3 集成运算放大电路 9.4 理想集成运放的线性运用电路 9.5 理想集成运放的非线性运用电路 习题 第九章集成运算放大器及其应用 9.1 差分放大电路 9.1.1 直接耦合多级放大电路的零点漂移现象 工业控制中的很多物理量均为模拟量,如温度、流量、压力、液面和长度等,它们通过不同的传感器转化成的电量也均为变化缓慢的非周期性连续信号,这些信号具有以下两个特点: 1.信号比较微弱,只有通过多级放大才能驱动负载; 2.信号变化缓慢,一般采用直接耦合多级放大电路将其放大。 u=0)时,人们在试验中发现,在直接耦合的多级放大电路中,即使将输入端短路(即 i u≠0),这种现象称为零点漂移(简称为零漂),如图输出端还会产生缓慢变化的电压(即 o 9.1所示。 (a)测试电路(b)输出电压u o的漂移 图9.1 零点漂移现象 9.1.2 零漂产生的主要原因 在放大电路中,任何参数的变化,如电源电压的波动、元件的老化以及半导体元器件参数随温度变化而产生的变化,都将产生输出电压的漂移,在阻容耦合放大电路中,耦合电容对这种缓慢变化的漂移电压相当于开路,所以漂移电压将不会传递到下一级电路进一步放

大。但是,在直接耦合的多级放大电路中,前一级产生的漂移电压会和有用的信号(即要求放大的输入信号)一起被送到下一级进一步放大,当漂移电压的大小可以和有用信号相当时,在负载上就无法分辨是有效信号电压还是漂移电压,严重时漂移电压甚至把有效信号电压淹没了,使放大电路无法正常工作。 采用高质量的稳压电源和使用经过老化实验的元件就可以大大减小由此而产生的漂移,所以由温度变化所引起的半导体器件参数的变化是产生零点漂移现象的主要原因,因而也称零点漂移为温度漂移,简称温漂,从某种意义上讲零点漂移就是静态工作点Q点随温度的漂移。 9.1.3抑制温漂的方法 对于直接耦合多级放大电路,如果不采取措施来抑制温度漂移,其它方面的性能再优良,也不能成为实用电路。抑制温漂的方法主要由以下几种: (1)采用稳定静态工作的分压式偏置放大电路中Re的负反馈作用; (2)采用温度补偿的方法,利用热敏元件来抵消放大管的变化; (3)采用特性完全相同的三极管构成“差分放大电路”; 9.1.4 差分放大电路 差分放大电路是构成多级直接耦合放大电路的基本单元电路。直接耦合的多级放大电路的组成框图如图9.2所示。 图9.2 多级放大的组成框图 A倍后传送到负载上,对电路造从上图可知输入级一旦产生了温漂,会经中间级放大 u2 A≈1,对电路造成的成严重的影响,而中间级产生的温漂,由于直接到达功放级而功放的 u 影响跟输入级相比少得多,所以,我们主要应设法抑制输入级产生的温漂,故在直接耦合的多级放大电路中只有输入级常采用差分放大电路的形式来抑制温漂。 9.1.4.1 差分放大电路的组成及结构特点 一.电路组成 差分放大电路如图9.3所示。

1. 差分放大器的结构、特点及作用 特点: 差分信号作为输出可以增大最大输出压摆。 差分工作模式,能很好抑制环境噪声(如电源噪声),即所谓的共模抑制。虽然这是以电路面积为代价的,但对于在单端模式时采用其它的方法来抑制环境噪声的干扰的电路面积而言还是较小的。 差分电路还具有偏置电路简单和线性度高等优点。 结构: 应用: 2. 基本差分对中的尾电流源的作用 为差分对提供一个电流源I S ,以使差分对具有固定的尾电流,从而产生独立于输入共模信号V ic 的电流I D1+I D2。 在共模输入时差分对管的工作电流I D1=I D2= I S /2,并且保持恒定; 同理,其共模输出电平也保持恒定,且其值为V DD -RI S /2(R 为负载等效电阻)。 解决了由于差分对管在共模输入时的工作电流变化引起非线性及输出信号失真等。 V i1 V i2 V i1V i2

3. 各类差分放大器的增益(共模增益、差模增益)、输入输出共模电平范围、 线性增益区的范围(对所给电路图分析计算) 双端输入双端输出时的差模电压增益 双端输入单端输出差模电压增益 在理想情况下,由于电路的完全对称性,则当输入共模信号时,由于引起差分对管的每边的输出电压的变化量相等,双端输出的电压为0,故电压增益为0。 理想情况下,单端输出共模小信号增益也为0。 4. 各类差分放大器的失调分析(失调的表示方式、原因,减小失调的方法) P83 减小由于输入差分对管不对称所引起的输入失调电压a 、减小输入差分对管MOS 管的阈值电压差,一种有效的方法就是采用离子注入工艺,使输入差分对管的阈值电压一致性较好。b 、减小失调误差的另一种方法是减小由于差分对管的几何尺寸的不对称引入的误差,这可以增大差分对管的尺寸,从而减小ΔW/W 与ΔL/L 的值(但这会造成输入差分对管具有大的寄生电容)来实现,并且通过提高光刻精度以减小ΔW/W 与ΔL/L 的误差值。 5. 差分放大器共模抑制能力的表示方式 R g V V V m i o o -=-)2)(121R g m 2 1 -

一.差分信号的特点: 图1 差分信号 1.差分信号是一对幅度相同,相位相反的信号。差分信号会以一个共模信号 V ocm 为中心,如图1所示。差分信号包含差模信号和公模信号两个部分, 差模与公模的定义分别为:Vdiff=(V out+-V out- )/2,Vocm=(V out+ +V out- )/2。 2.差分信号的摆幅是单端信号的两倍。如图1,绿色表示的是单端信号的摆 幅,而蓝色表示的是差分信号的摆幅。所以在同样电源电压供电条件下,使用差分信号增大了系统的动态范围。 3.差分信号可以抑制共模噪声,提高系统的信噪比。In a differential system, keeping the transport wires as close as possible to one another makes the noise coupled into the conductors appear as a common-mode voltage. Noise that is common to the power supplies will also appear as a common-mode voltage. Since the differential amplifier rejects common-mode voltages, the system is more immune to external noise. 4.差分信号可以抑制偶次谐波,提高系统的总谐波失真性能。 Differential systems provide increased immunity to external noise, reduced even-order harmonics, and twice the dynamic range when compared to signal-ended system. 二.分析差分放大器电路 图2.差分放大器电路分析图

全差分运算放大器设计 岳生生(200403020126) 一、设计指标 以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下: ?直流增益:>80dB ?单位增益带宽:>50MHz ?负载电容:=5pF ?相位裕量:>60度 ?增益裕量:>12dB ?差分压摆率:>200V/us ?共模电压:2.5V (VDD=5V) ?差分输入摆幅:>±4V 二、运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT N V 之和小于0.5V ,输出端的所有PMOS 管的,DSAT P V 之和也必须小于0.5V 。对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该 要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 三、性能指标分析 1、 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 11 1357 113 51 3 57 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=-+ 第二级增益 9 2 2 9112 9 9 11 ()m o o o m m o o g g G A R r r g g =-=-=- + 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r = = ≥++ 2、 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR :

差分接法:差分放大电路(图3.8a.4)的输入信号是从集成运放的反相和同相输入端引入,如果反馈电阻RF等于输入端电阻R1 ,输出电压为同相输入电压减反相输入电压,这种电路也称作减法电路。 图3.8a.4 差分放大电路 差分放大器 如图所示,通过采用两个输入,该差分放大器产生的输出等于U1和U2之差乘以增益系数

运算放大器的单电源供电方法 梦兰 大部分运算放大器要求双电源(正负电源)供电,只有少部分运算放大器可以在单电源供电状态下工作,如LM358(双运放)、LM324(四运放)、CA3140(单运放)等。需要说明的是,单电源供电的运算放大器不仅可以在单电源条件下工作,也可在双电源供电状态下工作。例如,LM324可以在、+5~+12V单电源供电状态下工作,也可以在+5~±12V双电源供电状态下工作。 在一些交流信号放大电路中,也可以采用电源偏置电路,将静态直流输出电压降为电源电压的一半,采用单电源工作,但输入和输出信号都需要加交流耦合电容,利用单电源供电的反相放大器如图1(a)所示,其运放输出波形如图1(b)所示。 该电路的增益Avf=-RF/R1。R2=R3时,静态直流电压Vo(DC)=1/2Vcc。耦合电容Cl和C2的值由所需的低频响应和电路的输入阻抗(对于C1)或负载(对于C2)来确定。Cl及C2可由下式来确定:C1=1000/2πfoRl(μF);C2=1000/2πfoRL(μF),式中,fo是所要求最低输入频率。若R1、RL单位用kΩ,fO用Hz,则求得的C1、C2单位为μF。一般来说,R2=R3≈2RF。 图2是一种单电源加法运算放大器。该电路输出电压Vo=一RF(V1/Rl十V2/R2十V3/R3),若R1=R2=R3=RF,则Vo=一(V1十V2十V3)。需要说明的是,采用单电源供电是要付出一定代价的。它是个甲类放大器,在无信号输入时,损耗较大。

差分放大器的工作原理 差分放大器也叫差动放大器是一种将两个输入端电压的差以一固定增益放大的电子放大器,有时简称为“差放”。差分放大器通常被用作功率放大器(简称“功放”)和发射极耦合逻辑电路 (ECL, Emitter Coupled Logic) 的输入级。 如果Q1 Q2的特性很相似,则V a,V b将同样变化。例如,V a变化+1V,V b也变化+1V,因为输出电压VOUT=V a-V b=0V,即V a的 变化与V b的变化相互抵消。这就是差动放大器可以作直流信号放大的原因。若差放的两个输入为,则它的输出V out为: 其中Ad是差模增益 (differential-mode gain),Ac是共模增益 (common-mode gain)。 因此为了提高信/噪比,应提高差动放大倍数,降低共模放大倍数。二者之比称做共模仰制比(CMRR, common-mode rejection ratio)。共模放大倍数AC可用下式求出: A c=2R l/2R e 通常以差模增益和共模增益的比值共模抑制比 (CMRR, common-mode rejection ratio) 衡量差分放大器消除共模信号的能力: 由上式可知,当共模增益Ac→0时,CMRR→∞。Re越大,Ac就越低,因此共模抑制比也就越大。因此对于完全对称的差分放大器来说,其Ac = 0,故输出电压可以表示为: 所谓共模放大倍数,就是V a,V b输入相同信号时的放大倍数。如果共模放大倍数为0,则输入噪声对输出没有影响。 要减小共模放大倍数,加大R E就行通常使用内阻大的恒流电路来带替R E

差分放大器是普通的单端输入放大器的一种推广,只要将差放的一个输入端接地,即可得到单端输入的放大器。很多系统在差分放大器的一个输入端输入反馈信号,另一个输入端输入反馈信号,从而实现负反馈。常用于电机或者伺服电机控制,稳压电源,测量仪器以及信号放大。在离散电子学中,实现差分放大器的一个常用手段是差动放大,见于多数运算放大器集成电路中的差分电路。 单端输出的差动放大电路 (不平衡输出) 称为单端Single ended或不平衡输出Unbalance Output。 单端较差动输出之幅度小一倍,使用单端输出时,共模讯号不能被抑制,因Vi1与Vi2同时增加,VC1与VC2则减少,而且VC1=VC2,但Vo =VC2,并非于零(产生零点漂移)。 但是加大RE阻值可以增大负回输而抑制输出,并且抑制共模讯号,因Vi1=Vi2时, Ii1及Ii2也同时增加,IE亦上升而令VE升高,这对Q1和Q2产生负回输, 令Q1和Q2之增益减少,即Vo减少。 当差动讯号输入时,Vi1 = -Vi2,IC1增加而IC2减少,总电流IE = IC1 + IC2便不变, 因此VE也不变,加大RE电阻值之电路会将差动讯号放大,不会对Q1及Q2产生负回输 及抑制。 。 b)减低功率消耗(相对纯电阻来说)。 c)提高差动放大之输出电压。 d)提高共模抑制比CMRR。 即差动输入,则IC1升而IC2下降(并且,ΔIC1 = ΔIC2) 因电流镜像原理,IC4 = IC1 故此,Io = IC4 IC2 = IC1 IC2 (ΔIo = 2ΔIC1或2ΔIC2) 这说明了输出电流是IC1和IC2的相差,即将输出变为具有双端差动输出性能的单端输出 (故对共模讯号之抑制有改善因双端差动输出才能产生消除共模讯号作用)。

专业课程设计任务书 第一周课题(四选一) 1.1M调幅接收机设计 要求:中心频率f0=1MHz,低频信号频率f m=10kHz。 2.锁相频率合成器设计 要求:锁相环使用C4046芯片,频率范围为10k~100k,步进10k。 3.LC低通滤波器设计 要求:设计一五阶Butterworth低通滤波器,截止频率为1.6MHz,输入、输出阻抗为50Ω 4.差分编码器(码发生器和编码器)设计 要求:码发生器输出一n=4的m序列伪码,码元传输速率10kB 第二周课题(三选一) 5.FSK调制解调系统设计 要求:码元传输速率1kB,载波频率分别为300kHz和600kHz 6.高频小信号放大器设计 要求:中心频率f0=1MHz,通频带30kHz<2Δf0.7<50kHz,电压增益不低于15dB 7.高频LC振荡电路设计制作 要求:(1)设计一个LC正弦波振荡电路 (2)电路采用单电源12V (3)可采用考毕兹,克拉波或西勒振荡器电路稳定输出频率 (4)振荡频率在1-2MHz连续可调 (5)在频率范围内输出峰峰值大于4V且无明显失真

课题一 课程设计报告内容索引 内容页码 1、课程设计题目 (5) 2、主要技术指标(电路功能及其精度等) (5) 3、方案论证及选择 (5) 4、系统组成框图 (8) 5、单元电路设计及说明 (9) 6、总体电路图 (10) 7、元器件列表 (10) 8、总结 (10) 9、参考文献 (11)

一、课程设计题目 差分编码器设计 要求:码发生器输出N=4的序列伪码,码元传输速率10KB 二、主要技术指标 1、码发生器输出n=4的序列伪码 2、码元传输速率为10KB 三、方案论证及选择 方案一 1基本原理: DQPSK(Differential QuadriPhase-Shift Keying,差分四相正交相移健控)是在QPSK(四相正交绝对调相)的基础上作的改进,它克服了QPSK信号载波的相位模糊问题,用相邻码元之间载波相位的相对变化来表示两位二进制数字信息。常用的DQPSK系统的方框图如图1所示,信息源来的信码先通过串/并变换电路分成两路并行二进制信号,再送入差分编码器实现两路二进制(即四进制)的差分编码。由于格雷码有其自身的优点,即判决接收到一个信号码元时,如发生错误,最容易判为它相邻的信号码元,即最多错一比特,所以送入QPSK四相绝对调制器要用格雷码。由于差分编码器是对自然二进制作差分编码,所以要在差分编码器和QPSK调制器之间做一个二-格变换电路,把双比特自然二进制码变换为双比特格雷码,再输入QPSK调制器。

加法器及差分放大器项目实验报告 一、项目内容和要求 (一)、加法器 1、任务目的: (1)掌握运算放大器线性电路的设计方法; (2)理解运算放大器的工作原理; (3)掌握应用仿真软件对运算放大器进行仿真分析的方法。 2、任务内容: 2.1 设计一个反相加法器电路,技术指标如下: (1)电路指标 运算关系:)25(21i i O U U U +-=。 输入阻抗Ω≥Ω≥K R K R i i 5,521。 (2)设计条件 电源电压Ec=±5V ; 负载阻抗Ω=K R L 1.5 (3)测试项目 A :输入信号V U V U i i 5.0,5.021±=±=,测试4种组合下的输出电压; B :输入信号V KHz U V U i i 1.0,1,5.021为正弦波±=信号,测试两种输入组合情况下的输出电 压波形。 C :输入信号V U i 01=,改变2i U 的幅度,测量该加法器的动态范围。 D :输入信号V U i 01=,V U i 1,2为正弦波,改变正弦波的频率,从1kHz 逐渐增加,步长为 2kHz ,测量该加法器的幅频特性。 2.2 设计一个同相加法器电路,技术指标如下: (1)电路指标 运算关系:21i i O U U U +=。 (2)设计条件 电源电压Ec=±5V ; 负载阻抗Ω=K R L 1.5 (3)测试项目 A :输入信号V U V U i i 1,121±=±=,测试4种组合下的输出电压; B :输入信号V KHz U V U i i 1,1,121为正弦波±=信号,测试两种输入组合情况下的输出电压 波形。 (二)、差分放大器 1、任务目的: (1)掌握运算放大器线性电路的设计方法; (2)理解运算放大器的工作原理; (3)掌握应用仿真软件对运算放大器进行仿真分析的方法。 2、任务内容 2.1 设计一个基本运放差分放大器电路,技术指标如下: (1)电路指标 运算关系:)(521i i O U U U --=。 输入阻抗Ω≥Ω≥K R K R i i 5,521。 (2)设计条件

全差分套筒式运算放大器设计 1、设计内容 本设计基于经典的全差分套筒式结构设计了一个高增益运算放大器,采用镜像电流源作为偏置。为了获得更大的输出摆幅及差模增益,电路采用了共模反馈及二级放大电路。 本设计所用到的器件均采用SMIC 0.18μm的工艺库。 2、设计要求及工艺参数 本设计要实现的各项指标和相关的工艺参数如表1和表2所示:

3、放大器设计 3.1 全差分套筒式放大器拓扑结构与实际电路 图1 全差分套筒式放大器拓扑结构 图2 最终电路图

3.2 设计过程 在图1中,Mb1和M9组成的恒流源为差放提供恒流源偏置,且M1,M2完全一样,即两管子所有参数均相同。Mb2、M7和M8构成了镜像电流源,M5、M6和M7、M8构成了共源共栅电流源,M1、M2、M3、M4构成了共源共栅结构,可以显著提高输出阻抗,提高放大倍数(把M3的输出阻抗提高至原来的(gm3 + gmb3)ro2倍。但同时降低了输出电压摆幅。为了提高摆幅,控制增益,在套筒式差分放大器输出端增加二级放大。 本设计中功率上限为10mW,可以给一级放大电路分配3mA的电流。设计要求摆幅为3V,所以图1中M1、M3、M5、M9的过驱动电压之和不大于1.8-3/2=0.3V。我们可以平均分配每个管子的过驱动电压。根据漏电计算流公式(1)(考虑沟道长度调制效应),可以计算出每个管子的宽长比。 I D=1 2μn C ox W L (V GS?V TH)2(1+λV DS)(1) 其中,C ox等于ε/t ox,μn和t ox可以从工艺库中查找。 4、仿真结果 经过调试优化之后的仿真结果如以下各图所示: 图3 增益及相位裕度 从图中可以看出,本设计的低频增益达到了74.25dB,达到了预期要求。3dB 带宽为35kHz左右,比较小,可见设计还有改进的余地。 当CL为2pF时,相位裕度: PM=180°+∠βH(ω)=180°?125.5°=54.5° 电源电压为1.8V时,输出摆幅如下图所示,达到了3V。

全差分运算放大器设计 岳生生(0126) 一、设计指标 以上华CMOS 工艺设计一个全差分运算放大器,设计指标如下: 直流增益:>80dB 单位增益带宽:>50MHz 负载电容:=5pF 相位裕量:>60度 增益裕量:>12dB 差分压摆率:>200V/us 共模电压:(VDD=5V) 差分输入摆幅:>±4V 运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的 ,DSAT N V 之和小于,输出端的所有PMOS 管的 ,DSAT P V 之和也必须小于。对于单 级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 性能指标分析 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 1 1 1 3 5 7 1 1 3 5 1 3 5 7 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=- +P 第二级增益9 2 2 9 11 2 9 9 11 ()m o o o m m o o g g G A R r r g g =-=-=-+P 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r == ≥++ 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR : 1)、输入级: max 1max |2| Cc out DS C C d SR dt I v I C C = = = 单位增益带宽1m u C g C ω= ,可以得到 1m C u g C ω =

几个常用经典差动放大器应用电路详解 成德广营浏览数:1507发布日期:2016-10-10 10:48 经典的四电阻差动放大器(Differential amplifier,差分放大器)似乎很简单,但其在电路中的性能不佳。本文从实际生产设计出发,讨论了分立式电阻、滤波、交流共模抑制和高噪声增益的不足之处。关键词:CMRR差动放大器差分放大器 简介 经典的四电阻差动放大器(Differential amplifier,差分放大器)似乎很简单,但其在电路中的性能不佳。本文从实际生产设计出发,讨论了分立式电阻、滤波、交流共模抑制和高噪声增益的不足之处。 大学里的电子学课程说明了理想运算放大器的应用,包括反相和同相放大器,然后将它们进行组合,构建差动放大器。图 1 所示的经典四电阻差动放大器非常有用,教科书和讲座 40 多年来一直在介绍该器件。 图 1. 经典差动放大器 该放大器的传递函数为: 若R1 = R3 且R2 = R4,则公式 1 简化为:

这种简化可以在教科书中看到,但现实中无法这样做,因为电阻永远不可能完全相等。此外,基本电路在其他方面的改变可产生意想不到的行为。下列示例虽经过简化以显示出问题的本质,但来源于实际的应用问题。 CMRR 差动放大器的一项重要功能是抑制两路输入的共模信号。如图1 所示,假设V2 为 5 V,V1 为 3 V,则4V为共模输入。V2 比共模电压高 1 V,而V1 低 1 V。二者之差为 2 V,因此R2/R1的“理想”增益施加于2 V。如果电阻非理想,则共模电压的一部分将被差动放大器放大,并作为V1 和V2 之间的有效电压差出现在VOUT ,无法与真实信号相区别。差动放大器抑制这一部分电压的能力称为共模抑制(CMR)。该参数可以表示为比率的形式(CMRR),也可以转换为分贝(dB)。 在1991 年的一篇文章中,Ramón Pallás-Areny和John Webster指出,假定运算放大器为理想运算放大器,则共模抑制可以表示为: 其中,Ad为差动放大器的增益, t 为电阻容差。因此,在单位增益和 1%电阻情况下,CMRR 等于 50 V/V(或约为 34 dB);在 0.1%电阻情况下,CMRR等于 500 V/V(或约为 54 dB)-- 甚至假定运算放大器为理想器件,具有无限的共模抑制能力。若运算放大器的共模抑制能力足够高,则总CMRR受限于电阻匹配。某些低成本运算放大器具有 60 dB至 70 dB的最小CMRR,使计算更为复杂。 低容差电阻 第一个次优设计如图 2 所示。该设计为采用OP291 的低端电流检测应用。R1 至R4 为分立式 0.5%电阻。由Pallás-Areny文章中的公式可知,最佳CMR为 64 dB.幸运的是,共模电压离接地很近,因此CMR并非该应用中主要误差源。具有 1%容差的电流检测电阻会产生 1%误差,但该初始容差可以校准或调整。然而,由于工作范围超过 80°C,因此必须考虑电阻的温度系数。

第4节 差分放大器设计 [学习要求] 掌握差分放大器的主要特性参数及其测试方法;学会设计具有恒流源的差分放大器及电路的调试技术。 [重点与难点] 重点:差分放大器的传输特性及差模特性。 难点:恒流源的镜像电流;输入输出信号的连接方式对性能的影响。 [理论内容] 一、具有恒流源的差分放大器 具有恒流源的差分放大器,应用十分广泛。特别是在模拟集成电路中,常作为输入级或中间放大级,电路如图1所示。其中,T 1、T 2称为差分对管,常采用双三极管如5G921或BG319等,它与电阻R Bl 、R B2、R Cl 、R C2及电位器RP 共同组成差分放大器的基本电路。T 3、T 4与电阻R E3、R E4、R 共同组成恒流源电路,为差分对管的射极提供恒定电流。均压电阻R 0I 1、R 2给差分放大器提供对称差模输入信号。晶体管T 1与T 2、T 3与T 4的特性应相同,电路参数应完全对称,改变RP 可调整电路的对称性。由于电路的这种对称性结构特点及恒流源的作用,无论是温度的变化,还是电源的波动(称之为共模信号),对T 1、T 2两管的影响都是一样的。因此,差分放大器能有效地抑制零点漂移。 图1具有恒流源的差分放大器 1、输入输出信号的连接方式

如图1所示,差分放大器的输入信号与输出信号可以有4种不同的连接方 .id V . od V 式: ·双端输入—双端输出连接方式为①—A'—A ,②—B'—B ;③—C ,④—D 。 ·双端输入—单端输出连接方式为①—A'—A ,②—B'—B ;③、④分别接一电阻 RL 到地。 ·单端输入—双端输出连接方式为①—A ,②—B —地:③—C ,④—D 。 ·单端输入—单端输出连接方式为①—A ,②—B —地:③、④分别接一电阻R L 到地。 连接方式不同,电路的特性参数有所不同。 2、静态工作点的计算 静态时,差分放大器的输入端不加信号。对于恒流源电路的电流值 .id V 0 4444422I I I I I I I Q C Q C Q C Q C Q B R ≈≈+=+=β (1) 故称为0I R I 的镜像电流,其表达式为 407.0E EE R R R V V I I +??== (2) 上式表明,恒定电流主要由电源电压0I EE V ?及电阻R 、4E R 决定 对于差分对管T1、T2组成的对称电路,则有 2021I I I Q C Q C == (3) 21 01121C CC C Q C CC Q C Q C R I V R I V V V ?=?== (4) {}(){}mA I mV mA I mV r mA mA E be ?++?=?++?=226130026)1(3000ββ (5) 可见差分放大器的静态工作点,主要由恒流 源电流的大小决定 0I 二、主要特性参数及其测试方法 1、传输特性 传输特性是指差分放大器在差模信号输

图3.8a.4 差分放大电路 差分放大器 如图所示,通过采用两个输入,该差分放大器产生的输出等于U1和U2之差乘以增益系数 运算放大器的单电源供电方法 大部分运算放大器要求双电源(正负电源)供电,只有少部分运算放大器可以在单电源供电状态下工作,如LM358(双运放)、LM324(四运放)、CA3140(单运放)等。需要说明的是,单电源供电的运算放大器不仅可以在单电源条件下工作,也可在双电源供电状态下工作。例如,LM324可以在、+5~+12V单电源供电状态下工作,也可以在+5~±12V双电源供电状态下工作。 在一些交流信号放大电路中,也可以采用电源偏置电路,将静态直流输出电压降为电源电压的一半,采用单电源工作,但输入和输出信号都需要加交流耦合电容,利用单电源供电的反相放大器如图1(a)所示,其运放输出波形如图1(b)所示。 该电路的增益Avf=-RF/R1。R2=R3时,静态直流电压Vo(DC)=1/2Vcc。耦合电容Cl和C2的值由所需的低频响应和电路的输入阻抗(对于C1)或负载(对于C2)来确定。Cl及C2可由下式来确定:C1=1000/2πfoRl(μF);C2=1000/2πfoRL(μF),式中,fo是所要求最低输入频率。若R1、RL单位用kΩ,fO用Hz,则求得的C1、C2单位为μF。一般来说,R2=R3≈2RF。 图2是一种单电源加法运算放大器。该电路输出电压Vo=一RF(V1/Rl十V2/R2十V3/R3),若R1=R2=R3=RF,则Vo=一(V1十V2十V3)。需要说明的是,采用单电源供电是要付出一定代价的。它是个甲类放大器,在无信号输入时,损耗较大。 思考题(1)图3是一种增益为10、输入阻抗为10kΩ、低频响应近似为30Hz、驱动负载为1kΩ的单电源反相放大器电路。该电路的不失真输入电压的峰—峰值是多少呢?(提示:一般运算放大器的典型输入、输

第三章差动放大电路与集成运算放大器 3.1 选择填空 1.使用差动放大电路的目的是为了提高()。 A输入电阻B电压放大倍数C抑制零点漂移能力D电流放大倍数 2.差动放大器抑制零点漂移的效果取决于()。 A两个晶体管的静态工作点B两个晶体管的对称程度 C各个晶体管的零点漂移D两个晶体管的放大倍数 3.差模输入信号是两个输入信号的(),共模输入信号是两个输入信号的()。 A 和 B 差 C 比值 D 平均值 4.电路的差模放大倍数越大表示(),共模抑制比越大表示()。 A有用信号的放大倍数越大B共模信号的放大倍数越大 C抑制共模信号和温漂的能力越强 5.差动放大电路的作用是()。 A放大差模B放大共模C抑制共模D抑制共模,又放大差模 6.差动放大电路由双端输入变为单端输入,差模电压增益是()。 A增加一倍B为双端输入的1/2 C不变D不定 7.差动放大电路中当U I1=300mV,U I2=-200mV,分解为共模输入信号U IC=()mV,差模输入信号U ID=()mV。 A500 B100 C250 D50 8.在相同条件下,阻容耦合放大电路的零点漂移()。 A比直接耦合电路大B比直接耦合电路小C与直接耦合电路相同 9.差动放大电路由双端输出改为单端输出,共模抑制比K CMRR减小的原因是()。 A A UD不变,A UC增大 B A UD减小,A UC不变 C A UD减小,A UC增大 D A UD增大,A UC减小 3.2简答题 1.直接耦合放大电路能放大交流信号吗?直接耦合放大电路和阻容耦合放大电路各有什么优缺点? 2.什么叫零点漂移?产生零点漂移的主要原因是什么?如何抑制零点漂移?在阻容耦合放大电路中是否存在零点漂移? 3.有甲已二个直接耦合放大电路,甲电路的Au=100,乙电路的Au=50。当外界温度变化了20℃时,甲电路的输出电压漂移了10V,乙电路的输出电压漂移了6V,向哪个电路的温度漂移参数小?其数值是多少? 4.解释下列术语的含义:差模信号,共模信号,差模电压放大倍数,共模电压放大倍数,共模抑制比。 5.差动式放大电路为什么能抑制零点漂移?单端输出和双端输出时,它们抑制零点漂移的原理是否一样?为什么? 6.共模抑制比是如何定义的?为什么说共模抑制比越大电路抗共模干扰能力就越强?7.长尾电路中的公共射极电阻Re,它对差模信号和共模信号各有什么影响?用恒流源取代Re有什么好处? 8.集成运算放大器的内部电路一般由哪几个主要部分组成?各部分的作用是什么? 3.3双端输出的差动式放大电路如图3.1所示,已知Rc1= Rc2=3KΩ,Re=5.1KΩ,每个三极管的U BE=0.7V,β=50,r be=2kΩ,Rs1=Rs2=02.KΩ

全差分运算放大器设计 岳生生(6) 一、设计指标 以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下: ?直流增益:>80dB ?单位增益带宽:>50MHz ?负载电容:=5pF ?相位裕量:>60度 ?增益裕量:>12dB ?差分压摆率:>200V/us ?共模电压:2.5V (VDD=5V) ?差分输入摆幅:>±4V 二、运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT N V 之和小于0.5V ,输出端的所有PMOS 管的 ,DSAT P V 之和也必须小于0.5V 。对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该 要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 三、性能指标分析 1、 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 11135711 3 5 1 3 5 7 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=- +P 第二级增益 9 2 291129 9 11 ()m o o o m m o o g g G A R r r g g =-=-=- +P 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r == ≥++ 2、 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR :

设计课题 设计一个具有恒流偏置的单端输入-单端输出差分放大器。 学校:延安大学

一: 已知条件 正负电源电压V V V V EE cc 12,12-=-+=+;负载Ω=k R L 20;输入差 模信号mV V id 20=。 二:性能指标要求 差模输入电阻Ω>k R id 10;差模电压增益15≥vd A ;共模抑制 比dB K CMR 50>。 三:方案设计及论证 方案一:

方案二

方案论证: 在放大电路中,任何元件参数的变化,都将产生输出电压的漂移,由温度变化所引起的半导体参数的变化是产生零点漂移的主要原因。采用特性相同的管子使它们产生的温漂相互抵消,故构成差分放大电路。差分放大电路的基本性能是放大差模信号,抑制共模信号好,采用恒流源代替稳流电阻,从而尽可能的提高共模抑制比。 论证方案一:用电阻R6来抑制温漂 ?优点:R6 越大抑制温漂的能力越强; ?缺点:<1>在集成电路中难以制作大电阻; <2> R6的增大也会导致Vee的增大(实际中Vee不

可能随意变化) 论证方案二 优点:(1)引入恒流源来代替R6,理想的恒流源内阻趋于无穷,直流压降不会太高,符合实际情况; (2)电路中恒流源部分增加了两个电位器,其中47R的用来调整电路对称性,10K的用来控制Ic的大小,从而调节静态工作点。 通过分析最终选择方案二。 四:实验工作原理及元器件参数确定 ?静态分析:当输入信号为0时, ?I EQ≈(Vee-U BEQ)/2Re ?I BQ= I EQ /(1+β) ?U CEQ=U CQ-U EQ≈Vcc-I CQ Rc+U BEQ 动态分析 ?已知:R1=R4,R2=R3

半导体基本知识和 半导体器件(二极管、三极管、场效应管、集成运放) 一、选择题: 1、PN结外加正向电压时,其空间电荷区()。 A.不变 B.变宽 C.变窄 D.无法确定 2、PN结外反正向电压时,其空间电荷区()。 A.不变 B.变宽 C.变窄 D.无法确定 3、当环境温度升高时,二极管的反向饱和电流I s将增大,是因为此时PN结内部的() A. 多数载流子浓度增大 B.少数载流子浓度增大 C.多数载流子浓度减小 D.少数载流子浓度减小 4、PN结反向向偏置时,其内电场被()。 A.削弱 B.增强 C.不变 D.不确定 5、在绝对零度(0K)和没有外界激发时,本征半导体中( ) 载流子。 A.有 B.没有 C.少数 D.多数 6、集成运放的输入级采用差分放大电路是因为可以()。 A.减小温漂B. 增大放大倍数 C. 提高输入电阻 D. 减小输出电阻 7、以下所列器件中,()器件不是工作在反偏状态的。 A、光电二极管 B、发光二极管 C、变容二极管 D、稳压管 8、当晶体管工作在放大区时,()。 A. 发射结和集电结均反偏 B.发射结正偏,集电结反偏 C.发射结和集电结均正偏 D.发射结反偏,集电结正偏 9、稳压二极管稳压时,其工作在( ), A.正向导通区B.反向截止区C.反向击穿区 D.不确定 10、抑制温漂(零漂)最常用的方法是采用()电路。 A.差放 B.正弦 C.数字 D.功率放大 11、在某放大电路中,测得三极管三个电极的静态电位分别为0 V,-10 V,-9.3 V,则这只三极管是()。 A.NPN 型硅管B.NPN 型锗管Array C.PNP 型硅管 D.PNP 型锗管 12、某场效应管的转移特性如右图所示,该管为()。 A.P沟道增强型MOS管 B.P沟道结型场效应管 C.N沟道增强型MOS管 D.N沟道耗尽型MOS管 13、通用型集成运放的输入级采用差动放大电路,这是因为它的()。 A.输入电阻高 B.输出电阻低 C.共模抑制比大 D.电压放大倍数大 14、如右图所示复合管,已知V1的β1 = 30,V2的β2 = 50,则复合后的β约为()。