MT-008

TUTORIAL Converting Oscillator Phase Noise to Time Jitter

by Walt Kester

INTRODUCTION

A low aperture jitter specification of an ADC is critical to achieving high levels of signal-to-noise ratios (SNR). (See References 1, 2, and 3). ADCs are available with aperture jitter specifications as low as 60-fs rms (AD9445 14-bits @ 125 MSPS and AD9446 16-bits @ 100 MSPS). Extremely low jitter sampling clocks must therefore be utilized so that the ADC performance is not degraded, because the total jitter is the root-sum-square of the internal converter aperture jitter and the external sampling clock jitter. However, oscillators used for sampling clock generation are more often specified in terms of phase noise rather than time jitter. The purpose of this discussion is to develop a simple method for converting oscillator phase noise into time jitter.

PHASE NOISE DEFINED

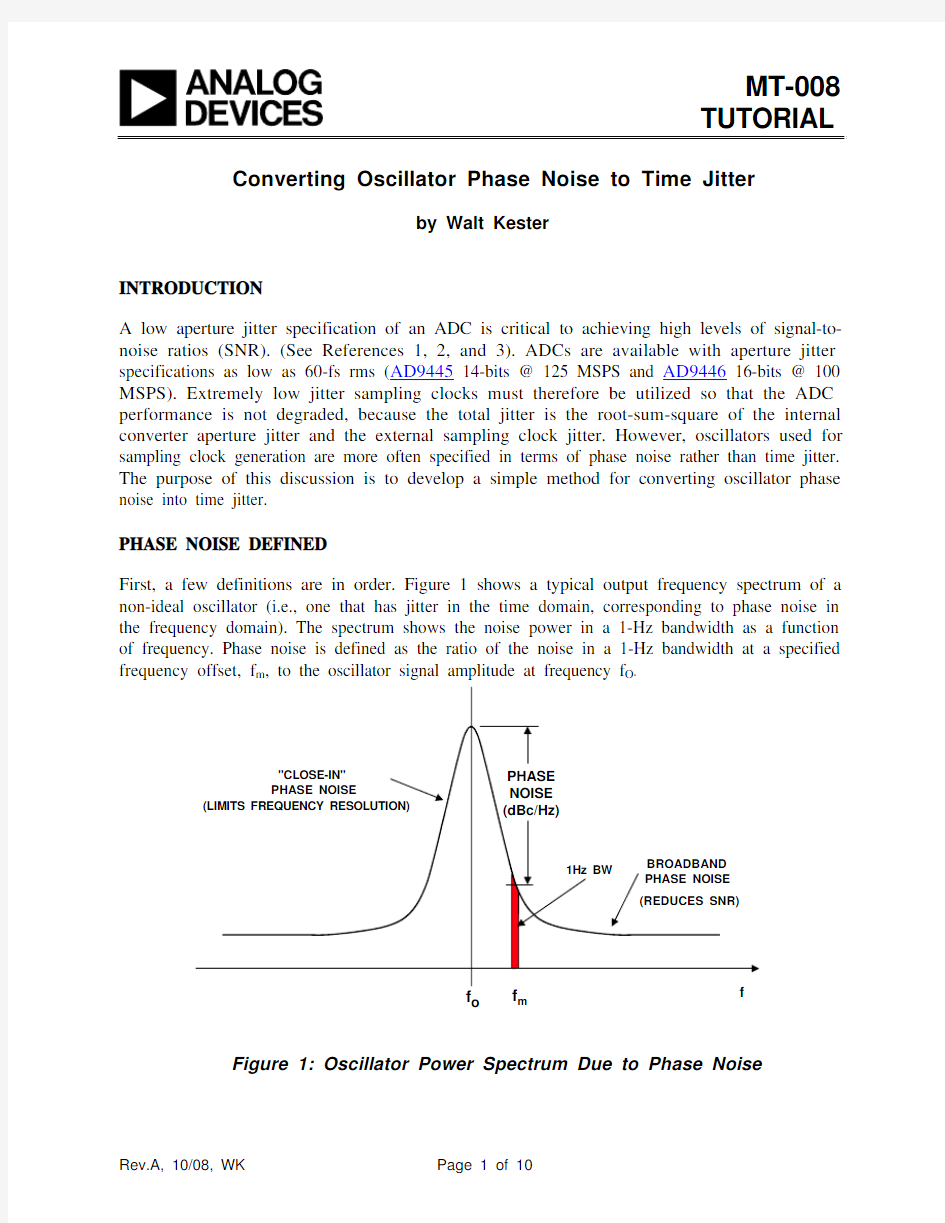

First, a few definitions are in order. Figure 1 shows a typical output frequency spectrum of a non-ideal oscillator (i.e., one that has jitter in the time domain, corresponding to phase noise in the frequency domain). The spectrum shows the noise power in a 1-Hz bandwidth as a function of frequency. Phase noise is defined as the ratio of the noise in a 1-Hz bandwidth at a specified frequency offset, f m, to the oscillator signal amplitude at frequency f O.

o m

Figure 1: Oscillator Power Spectrum Due to Phase Noise

The sampling process is basically a multiplication of the sampling clock and the analog input signal. This is multiplication in the time domain, which is equivalent to convolution in the frequency domain. Therefore, the spectrum of the sampling clock oscillator is convolved with the input and shows up on the FFT output of a pure sinewave input signal (see Figure 2).

f o

f s

f o

IDEAL SINEWAVE

INPUT SAMPLING CLOCK WITH PHASE NOISE

FFT OUTPUT FOR IDEAL ADC WITH N →∞(MEASURED FROM DC TO f s /2)SNR = 20log 101

2πf o t j f f

Figure 2: Effect of Sampling Clock Phase Noise Ideal Digitized Sinewave

The "close-in" phase noise will "smear" the fundamental signal into a number of frequency bins, thereby reducing the overall spectral resolution. The "broadband" phase noise will cause a degradation in the overall SNR as predicted by Eq. 1 (Reference 1 and 2):

???

?

????π=j 10t f 21log 20SNR .

Eq. 1

It is customary to characterize an oscillator in terms of its single-sideband phase noise as shown in Figure 3, where the phase noise in dBc/Hz is plotted as a function of frequency offset, f m , with the frequency axis on a log scale. Note the actual curve is approximated by a number of regions, each having a slope of 1/f x , where x = 0 corresponds to the "white" phase noise region (slope = 0 dB/decade), and x = 1 corresponds to the "flicker" phase noise region (slope = –20 dB/decade). There are also regions where x = 2, 3, 4, and these regions occur progressively closer to the carrier frequency.

PHASE NOISE (dBc/Hz)

FREQUENCY OFFSET, f m , (LOG SCALE)

Figure 3: Oscillator Phase Noise in dBc/Hz vs. Frequency Offset

Note that the phase noise curve is somewhat analogous to the input voltage noise spectral density of an amplifier. Like amplifier voltage noise, low 1/f corner frequencies are highly desirable in an oscillator.

We have seen that oscillators are typically specified in terms of phase noise, but in order to relate phase noise to ADC performance, the phase noise must be converted into jitter. In order to make the graph relevant to modern ADC applications, the oscillator frequency (sampling frequency) is chosen to be 100 MHz for discussion purposes, and a typical graph is shown in Figure 4. Notice that the phase noise curve is approximated by a number of individual line segments, and the end points of each segment are defined by data points.

FREQUENCY OFFSET (Hz)PHASE

NOISE

(dBc/Hz)f m

Figure 4: Calculating Jitter from Phase Noise

CONVERTING PHASE NOISE TO JITTER

The first step in calculating the equivalent rms jitter is to obtain the integrated phase noise power over the frequency range of interest, i.e., the area of the curve, A. The curve is broken into a number of individual areas (A1, A2, A3, A4), each defined by two data points. Generally speaking, the upper frequency range for the integration should be twice the sampling frequency, assuming there is no filtering between the oscillator and the ADC input. This approximates the bandwidth of the ADC sampling clock input.

Selecting the lower frequency for the integration also requires some judgment. In theory, it should be as low as possible to get the true rms jitter. In practice, however, the oscillator specifications generally will not be given for offset frequencies less than 10 Hz, or so—however, this will certainly give accurate enough results in the calculations. A lower frequency of integration of 100 Hz is reasonable in most cases, if that specification is available. Otherwise, use either the 1-kHz or 10-kHz data point.

One should also consider that the "close-in" phase noise affects the spectral resolution of the system, while the broadband noise affects the overall system SNR. Probably the wisest approach is to integrate each area separately as explained below and examine the magnitude of the jitter contribution of each area. The low frequency contributions may be negligible compared to the broadband contribution if a crystal oscillator is used. Other types of oscillators may have significant jitter contributions in the low frequency area, and a decision must be made regarding their importance to the overall system frequency resolution.

The integration of each individual area yields individual power ratios. The individual power ratios are then summed and converted back into dBc. Once the integrated phase noise power is known, the rms phase jitter in radians is given by the equation (see References 3-7 for further details, derivations, etc.),

10/A 102)radians (Jitter Phase RMS ?=,

Eq. 2

and dividing by 2πf O converts the jitter in radians to jitter in seconds:

O

10

/A f 2102)onds (sec Jitter Phase RMS π?=

.

Eq. 3

It should be noted that computer programs and spreadsheets are available online to perform the integration by segments and calculate the rms jitter, thereby greatly simplifying the process (References 8, 9).

Figure 5 shows a sample calculation which assumes only broadband phase noise. The broadband phase noise chosen of –150 dBc/Hz represents a reasonably good signal generator specification, so the jitter number obtained represents a practical situation. The phase noise of –150 dBc/Hz (expressed as a ratio) is multiplied by the bandwidth of integration (200 MHz) to obtain the integrated phase noise of –67 dBc. Note that this multiplication is equivalent to adding the

quantity 10 log 10[200 MHz – 0.01 MHz] to the phase noise in dBc/Hz. In practice, the lower frequency limit of 0.01 MHz can be dropped from the calculation, as it does not affect the final result significantly. A total rms jitter of approximately 1 ps is obtained using Eq. 3.

10k

100k

1M

10M

100M

1G

FREQUENCY OFFSET (Hz)

PHASE NOISE (dBc/Hz)

f m

–150

RMS PHASE JITTER (radians) ≈2?10 = 6.32×10–4radians

A/10

RMS JITTER (seconds) =

RMS PHASE JITTER (radians)

2 πf O

A = –150dBc + 10 log 10

200×106–0.01×106

= –150dBc + 83dB = –67dBc

= 1ps

Figure 5: Sample Jitter Calculation Assuming Broadband Phase Noise

Crystal oscillators generally offer the lowest possible phase noise and jitter, and some examples are shown for comparison in Figure 6. All the oscillators shown have a typical 1/f corner frequency of 20 kHz, and the phase noise therefore represents the white phase noise level. The two Wenzel oscillators are fixed-frequency and represent excellent performance (Reference 9). It is difficult to achieve this level of performance with variable frequency signal generators, as shown by the –150 dBc specification for a relatively high quality generator.

Wenzel ULN Series*–174dBc/Hz @ 10kHz+

Wenzel Sprinter Series,–165dBc/Hz @ 10kHz+ High Quality Signal Generator –150dBc/Hz @ 10kHz+ z Thermal noise floor of resistive source in a matched system @ +25°C = –174dBm/Hz z 0dBm = 1mW = 632mV p-p into 50Ωz * An oscillator with an output of +13dBm (2.82V p-p) into 50Ωwith a phase noise of –174dBc/Hz has a noise floor of

+13dBm –174dBc = –161dBm, 13dB above the thermal noise floor (Wenzel ULN and Sprinter Series Specifications and Pricing Used with Permission of Wenzel Associates)

Figure 6: 100-MHz Oscillator Broadband Phase Noise Floor Comparisons (Wenzel ULN

and Sprinter Series Specifications and Pricing used with Permission of Wenzel

Associates)

At this point, it should be noted that there is a theoretical limit to the noise floor of an oscillator determined by the thermal noise of a matched source: –174 dBm/Hz at +25°C. Therefore, an oscillator with a +13-dBm output into 50 Ω (2.82-V p-p) with a phase noise of –174 dBc/Hz has a noise floor of –174 dBc + 13 dBm = –161 dBm. This is the case for the Wenzel ULN series as shown in Figure 6.

Figure 7 shows the jitter calculations from the two Wenzel crystal oscillators. In each case, the data points were taken directly for the manufacturer's data sheet. Because of the low 1/f corner frequency, the majority of the jitter is due to the "white" phase noise area. The calculated values of 64 fs (ULN-Series) and 180 fs represent extremely low jitter. For informational purposes, the individual jitter contributions of each area have been labeled separately. The total jitter is the root-sum-square of the individual jitter contributors.

1001k 10k 100k 1M 10M

PHASE

NOISE (dBc/Hz)

100

1k

10k

100k

1M

10M

PHASE

NOISE (dBc/Hz)

100M

100M

Figure 7: Jitter Calculations for Low Noise 100-MHz Crystal Oscillators

(Phase Noise Data used with Permission of Wenzel Associates)

In system designs requiring low jitter sampling clocks, the costs of low noise dedicated crystal oscillators is generally prohibitive. An alternative solution is to use a phase-locked-loop (PLL) in conjunction with a voltage-controlled oscillator to "clean up" a noisy system clock as shown in Figure 8. There are many good references on PLL design (see References 10-13, for example), and we will not pursue that topic further, other than to state that using a narrow bandwidth loop filter in conjunction with a voltage-controlled crystal oscillator (VCXO) typically gives the lowest phase noise. As shown in Figure 8, the PLL tends to reduce the "close-in" phase noise while at the same time, reducing the overall phase noise floor. Further reduction in the white noise floor can be obtained by following the PLL output with an appropriate bandpass filter.

f s

Figure 8: Using a Phase-Locked Loop (PLL) and Bandpass

Filter to Condition a Noisy Clock Source

The effect of enclosing a free-running VCO within a PLL is shown in Figure 9. Notice that the "close-in" phase noise is reduced significantly by the action of the PLL.

Figure 9: Phase Noise for a Free-Running VCO and a PLL-Connected VCO

Analog Devices offers a wide portfolio of frequency synthesis products, including DDS systems, N, and fractional-N PLLs. For example, the ADF4360 family are fully integrated PLLs complete with an internal VCO. With a 10-kHz bandwidth loop filter, the phase noise of the ADF4360-1 2.25-GHz PLL is shown in Figure 10, and the line-segment approximation and jitter calculations shown in Figure 11. Note that the rms jitter is only 1.57 ps, even with a non-crystal VCO.

PHASE NOISE (dBc/Hz)

Figure 10: Phase Noise for ADF4360-1 2.25-GHz PLL

with Loop Filter BW = 10 kHz

100

1k

10k

100k

1M 10M 100M 1G 4.5G

PHASE NOISE (dBc/Hz)

FREQUENCY OFFSET (Hz)

Figure 11: Line Segment Approximation to ADF4360-1, 2.25-GHz

PLL Phase Noise Showing Jitter

Historically, PLL design relied heavily on textbooks and application notes to assist in the design of the loop filter, etc. Now, with Analog Devices free downloadable ADIsimPLL? software, PLL design is much easier. To start, choose a circuit by entering the desired output frequency range, and select a PLL, VCO, and a crystal reference. Once the loop filter configuration has been selected, the circuit can be analyzed and optimized for phase noise, phase margin, gain, spur levels, lock time, etc., in both the frequency and time domain. The program also performs the rms jitter calculation based on the PLL phase noise, thereby allowing the evaluation of the final PLL output as a sampling clock.

SUMMARY

Sampling clock jitter can be disastrous to the SNR performance of high performance ADCs. terms of their phase noise. This article has shown how to convert phase noise into jitter so that the SNR degradation can be easily calculated.

Although not as good as relatively expensive stand alone crystal oscillators, modern PLLs using crystal VCOs (along with suitable filtering) can achieve jitter performance suitable for all but the most demanding requirements.

The entire problem of clock distribution has become much more critical because of low jitter requirements. Analog Devices is now offering a line of clock distribution ICs to serve these needs (https://www.doczj.com/doc/198584940.html,/clocks).

REFERENCES

1.Brad Brannon, "Aperture Uncertainty and ADC System Performance," Application Note AN-501, Analog

Devices, download at https://www.doczj.com/doc/198584940.html,.

2.Bar-Giora Goldberg, "The Effects of Clock Jitter on Data Conversion Devices," RF Design, August 2002,

pp. 26-32, https://www.doczj.com/doc/198584940.html,.

3.Ulrich L. Rohde, Digital PLL Frequency Synthesizers, Theory and Design, Prentice-Hall, 1983, ISBN 0-

13-214239-2, all of Chapter 2 and pp. 411-418 for computer analysis.

4.Joseph V. Adler, "Clock-Source Jitter: A Clear Understanding Aids Oscillator Selection," EDN, February

18, 1999, pp. 79-86, https://www.doczj.com/doc/198584940.html,.

5.Neil Roberts, "Phase Noise and Jitter – A Primer for Digital Designers," EEdesign, July 14, 2003,

https://www.doczj.com/doc/198584940.html,.

6.Boris Drakhlis, "Calculate Oscillator Jitter by using Phase-Noise Analysis Part 1," Microwaves and RF,

January 2001, p. 82, https://www.doczj.com/doc/198584940.html,.

7.Boris Drakhlis, "Calculate Oscillator Jitter by using Phase-Noise Analysis Part 2," Microwaves and RF,

February 2001, p. 109, https://www.doczj.com/doc/198584940.html,.

8.Raltron Electronics Corporation, 10651 Northwest 19th Street, Miami, Florida 33172, Tel: (305) 593-

6033, https://www.doczj.com/doc/198584940.html,. (see "Convert SSB Phase Noise to Jitter" under "Engineering Design Tools").

9.Wenzel Associates, Inc., 2215 Kramer Lane, Austin, Texas 78758, Tel: (512) 835-2038,

https://www.doczj.com/doc/198584940.html, (see "Allan Variance from Phase Noise" under "Spreadsheets").

10.Mike Curtin and Paul O'Brien, "Phase-Locked Loops for High-Frequency Receivers and Transmitters, Part

1, Analog Dialogue 33-3, 1999, https://www.doczj.com/doc/198584940.html,.

11.Mike Curtin and Paul O'Brien, "Phase-Locked Loops for High-Frequency Receivers and Transmitters, Part

2, Analog Dialogue 33-5, 1999, https://www.doczj.com/doc/198584940.html,.

12.R. E. Best, Phase-Locked Loops: Theory, Design and Applications, Fourth Edition, McGraw-Hill, 1999,

ISBN 0071349030.

13. F. M. Gardner, Phaselock Techniques, Second Edition, John Wiley, 1979, ISBN 0471042943.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers’ products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

基于熵的图像二值化算法设计二维最大熵分割公司内部档案编码:[OPPTR-OPPT28-OPPTL98-OPPNN08]

1设计目的与要求 设计目的 (1)熟悉和掌握MATLAB程序设计方法。 (2)学习和掌握MATLAB图像处理工具箱。 (2)了解图像分割和图像二值化的原理。 (3)掌握图像二值化技术阈值的选取。 (4)将原彩色图像变为二值化后的图像,通过二维最大熵图像分割法对图像进行分割达到预期目的。 设计要求 (1)了解图像变换的意义和手段。 (2)熟悉最大熵和二值化的基本性质。 (3)通过本实验掌握利用MATLAB编程实现数字图像处理。 (4)理解图像分割的原理,了解其应用,掌握最大熵和二值化分割的方法。

2 设计方案 图像二值化 图像二值化是数字图像处理技术中的一项基本技术,二值化图像的显示与打印十分方便,存储与传输也非常容易,在目标识别、图像分析、文本增强、字符识别等领域得到广泛应用。图像二值化是将灰度图像转化为只有黑白两类像素的图像,大多采用阈值化算法处理。在不同的应用中,阈值的选取决定着图像特。 征信息的保留。因此,图像二值化技术的关键在于如何选取阈值。 最大熵原理 最大熵原理:最大熵原理是在1957 年由 提出的,其主要思想是,在只掌握关于未知分布的部分知识时,应该选取符合这些知识但熵值最大的概率分布。因为在这种情况下,符合已知知识的概率分布可能不止一个。我们知道,熵定义的实际上是一个随机变量的不确定性,熵最大的时候,说明随机变量最不确定,换句话说,也就是随机变量最随机,对其行为做准确预测最困难。 图像分割中最大熵的引入:在图像分割中若假定以灰度级T 分割图像,则图像中低于灰度级T 的像素点构成目标物体,高于灰度级T 的像素点构成背景那么各个灰度级在图像分割后的两区域中的概率如下: O :t i N N ???(0<=i<=t) () B : t i N N N - (t+1<=i<=255) () ? 其中Ni 为图像中灰度级为i 的像素点个数,Nt 为灰 度级从0~t 的像素点总和,N 为图像总像素点,t 为假定灰度阈值T 。 ) l og()(0 t i t i N N N N H ∑ -= ??? ? (0<=i<=t) ? ? ()

按键电路:常用的非编码键盘,每个键都是一个常开开关电路。 按键消抖: 通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,电压信号小型如下图。由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,如下图。抖动时间的长短由按键的机械特性决定,一般为5ms~10ms。这是一个很重要的时间参数,在很多场合都要用到。 按键稳定闭合时间的长短则是由操作人员的按键动作决定的,一般为零点几秒至数秒。键抖动会引起一次按键被误读多次。为确保CPU对键的一次闭合仅作一次处理,必须去除键抖

动。在键闭合稳定时读取键的状态,并且必须判别到键释放稳定后再作处理。按键的抖动,可用硬件或软件两种方法。 <1> 硬件消抖:在键数较少时可用硬件方法消除键抖动。下图所示的RS触发器为常用的硬件去抖。 图中两个“与非”门构成一个RS触发器。当按键未按下时,输出为1;当键按下时,输出为0。此时即使用按键的机械性能,使按键因弹性抖动而产生瞬时断开(抖动跳开B),中要按键不返回原始状态A,双稳态电路的状态不改变,输出保持为0,不会产生抖动的波形。也就是说,即使B 点的电压波形是抖动的,但经双稳态电路之后,其输出为正规的矩形波。这一点通过分析RS触发器的工作过程很容易得到验证。 <2> 软件消抖:如果按键较多,常用软件方法去抖,即检测出键闭合后执行一个延时程序,产生5ms~10ms的延时,让前沿抖动消失后再一次检测键的状态,如果仍保持闭合状态电平,则确认为真正有键按下。当检测到按键释放后,也要给5ms~10ms的延时,待后沿抖动消失后才能转入该键的处理程序。按键消抖

Agilent——眼图、抖动、相噪2009-02-25 22:31 随着数据速率超过Gb/s水平,工程师必须能够识别和解决抖动问题。抖动是在高速数据传输线中导致误码的定时噪声。如果系统的数据速率提高,在几秒内测得的抖动幅度会大体不变,但在位周期的几分之一时间内测量时,它会随着数据速率成比例提高,进而导致误码。新兴技术要求误码率(BER),亦即误码数量与传输的总码数之比,低于一万亿分之一(10-12)。随着数据通信、总线和底板的数据速率提高,市场上已经出现许多不同的抖动检定技术,这些技术采用各种不同的实验室设备,包括实时数字示波器、取样时间间隔分析仪(TIA)、等时取样示波器、模拟相位检波器和误码率测试仪(BERT)。为解决高数据速率上难以解决的抖动问题,工程师必需理解同步和异步网络中使用的各种抖动分析技术 本文重点介绍3 Gb/s以上新兴技术的数据速率。低于3 Gb/s的实时示波器可以捕获连续的数据流,可以同时在时域和频域中分析数据流;在更高的数据速率上,抖动分析要更具挑战性。本文将从数字工程师的角度,介绍应对SONET/SDH挑战的各种经验。 抖动分析基本上包括比较抖动时钟信号和参考时钟信号。参考时钟是一种单独的黄金标准时钟,或从数据中重建的时钟。在高数据速率时,分析每个时钟的唯一技术是位检测和误码率测试;其它技术则采用某种取样技术。 如图1所示,眼图是逻辑脉冲的重叠。它为测量信号质量提供了一种有用的工具,即使在极高的数据速率时,也可以在等时取样示波器上简便生成。边沿由‘1’到‘0’转换和‘0’到‘1’转换组成,样点位于眼图的中心。如果电压(或功率)高于样点,则码被标为逻辑‘1’;如果低于样点,则标为‘0’。系统时钟决定着各个位的样点水平位置。 图1: 具有各项定义的眼图 E1是逻辑‘1’的平均电压或功率电平,E0是逻辑‘0’的平均电压或功率电平。参考点t = 0在

实验五按键消抖 一. 实验目的 1. 掌握QuartusII的硬件描述语言设计方法 2. 了解同步计数器的原理及应用 3. 设计一个带使能输入、进位输出及同步清零的增1四位N (N<16)进制同步计数器 二. 准备知识 在按键使用的过程中,常常遇到按键抖动的问题,开关在闭合(断开)的瞬间,不能一接触就一直保持导通(断开),因为开关的机械特性,重要经历接触-断开-再接触-再断开,最终稳定在接触位置,这就是开关的抖动,即虽然只是按下按键一次然后放掉,结果在按键信号稳定前后,竟出现了一些不该存在的噪声,这样就会引起电路的误动作。在很多应用按键的场合,要求具有消抖措施。按键抖动与开关的机械特性有关,其抖动期一般为5-10ms。 键按下 键稳定 前沿抖动后沿抖动 图5.1 按键电平抖动示意图 按键的消除抖动分为硬件消除抖动和软件消除抖动。硬件消除抖动一般采用滤波的方法,通常在按键两端并联一个1~10u左右的电容,有时这样也不能完全消除按键的抖动。软件消除抖动的方法有多种,常用的是延时扫描和定时器扫描。延时扫描其原理为:检测到按键操作后延时一端时间(如10ms)后,再检测是否为仍然为同样的按键操作状态,如果相同,就认为是进行了按键操作,然后对该操作进行相应的处理。定时器扫描的原理是:每隔一端时间(几毫秒)扫描一次键盘,如果连续两次(或3次)的所获得的按键状态相同,就输出按键状态,然后再对这种按键状态进行处理,这里的扫描时间间隔和连续判断按键状态的次数是有关系的,一般总时间要大于按键的抖动期。如果总时间太长,则感觉按键迟钝,太短可能不能完全消除抖动,要根据实际的情况合适的选择。 在实际电路设计中,经常采用的是软硬件相结合对按键进行消除抖动的处理方法。 本实验采用的方法:实验箱按键的硬件电路是共阳极电路,按下按键时输出到FPGA管脚的电平为低电平,松开按键时为高电平。我们采用5ms的定时器扫描FPGA管脚电平,如果连续3次为低电平时,存储连续按键状态的次数CNT的值加1,直到该计数值等于10(或再大一些),就不再累加(防止长按该值溢出而重新计数),此时认为按键已稳定,输出按键操作标志;在该过程中,一旦FPGA管脚电平为低电平就对CNT复位清零并同时对按键操作标志位复位,即一个异步复位。 本实验采用的方法:实验箱按键的硬件电路是共阳极电路,按下按键时输出到FPGA管脚的电平为低电平,松开按键时为高电平。我们采用5ms的定时器扫描采样FPGA管脚电平,如果连续3次为低电平时,可以认为此时按键已稳定,输出一个低电平按键信号;继续采样的过程中如果不能满足连续3次采样为低,则认为键稳定状态结束,这时输出变为高电平(连线3次采用信号相“或”),

高速FPGA系统的信号完整性测试和分析 张楷 泰克科技(中国)有限公司 摘要:随着FPGA器件的速度和容量日益提高,各种高速的并行和串行接口都广泛应用在FPGA上,其中典型的高速串行总线速率超过1Gb/s,这为设计和应用人员提供了极大的灵活性,同时对于FPGA IO的测试和验证也带来了新的挑战。本文针对FPGA中各种高速串行总线的信号,提供全面的信号完整性测试和分析方法。 关键词:FPGA,高速串行信号, 信号完整性, 抖动,眼图测试,采样示波器 1. 引言 随着FPGA的设计速度和容量的明显增长,当前流行的FPGA芯片都提供高速总线,例如DDR内存总线,PCI-X总线、SPI总线;针对超高速的数据传输,FPGA通过集成SerDes提供高速串行IO,支持各种诸如PCI-E、GBE、XAUI等高速串行总线协议,为各种不同标准的高速传输提供极大的灵活性。典型的高速FPGA器件提供的每一条物理链路的速度从200Mbps到高达10Gbps,高速IO的测试和验证更成为传统专注于FPGA内部逻辑设计的设计人员面临的巨大挑战。这些挑战使设计人员非常容易会把绝大部分设计周期时间放在调试和检验设计上。 为了加速对于FPGA中高速并行和串行总线的调试和验证,它需要使用新的高速信号完整性测试工具和分析方法。本文根据当前FPGA的高速总线测试和分析,提供了最新的方法和工具。 图1是一个典型FPGA的提供的各种高速接口。对于这些速度从200M到高达10G的高速总线,信号完整性的测试和分析是保证设计成功的基础和关键。 图1 典型FPGA的提供的各种高速接口

2. 高速串行总线眼图测试 对于采用内嵌SERDES电路的FPGA芯片,其高速串行信号进行测试和验证,最基本的工具是通过示波器进行对其眼图测试。因为眼图能够非常直观的反映一条被测信号路径上的整体信号质量问题,包括信号的抖动量大小(眼宽)以及幅度的大小(眼高)等重要信息。图2是一个高速数据信号的眼图形成的过程。 图2 眼图的形成过程 从眼图的形成过程可以看出,一个NRZ编码的高速数据无论传输何种码流,都可以看作一个重复信号,经过一定时间和样本数的累计,它反映整个传输链路上的总体信号质量。 3. 选择合适的眼图测试工具 3.1 示波器带宽的要求 示波器是进行高速串行信号眼图测试的首选工具。无论是用高速实时示波器还是采样示波器(Sampling Scope)得到眼图,带宽是对示波器的基本要求。以一个NRZ编码的高速串行总线为例,它理想的波形是一个方波信号,方波信号是由它的基波(正弦波)和奇次谐波(3次,5次,7次…)组成。根据信号的传输速率和上升时间,选择尽量高带宽和最快上升时间的示波器,这样测试结果保留更多的谐波分量,构建高精度的眼图测试结果。 示波器带宽反映了对被测信号幅度上的衰减,而示波器上升时间决定了对被测信号上升时间测试的误差。经典的示波器带宽和上升时间的关系为:带宽×上升时间=0.35-0.45,0.35-0.45为常系数。每一个高性能示波器除了提供带宽的指标外,还会给出上升时间,表征其对阶跃信号的测试能力和精度。示波器测试结果的经验公式为: 高速串行数据(NRZ编码)提供一般为数据率,其最高的基频为比特率的一半。即假设给定一个NRZ编码的串行信号,码型为时钟码型(即传输的数据为1-0-1-0-1),从频域的角度观测该信号,它成为一个基波为数据率一半的方波信号,这个时钟码型是数据变化最快的情况。以泰克TDS6154C 大于15GHz带宽的实时示波器为例,它可以测试保留6.25Gb/s (2×XAUI)信号的五次谐波,以及10Gb/s (XFI)信号的三次谐波。下表列出了不同的高速串行总线在不同测

指纹图像二值化算法的分析和比较 1引言 指纹作为人体的重要特征,因其具有唯一性和终生不变性,已经成为生物识别领域的重要手段。它不仅应用于公安司法系统的犯罪识别,而且还广泛应用于如一些保密系统的身份验证,成为生物识别领域的新热点。在指纹自动识别系统中,图像采集设备所得到的图像是一幅含有较多噪声的灰度图,必须经过预处理,除去大量的噪声信号,得到一幅纹线清晰的点线图,才能进行指纹特征的提取和匹配。指纹图像的预处理是正确地进行特征提取、比对等操作的基础,而二值化是图像预处理中非常重要的一步,也是指纹细化并提取特征前的重要步骤。 不同的二值化经常会对后续的步骤产生极大的影响,常用的二值化方法由于仅仅利用了图像的灰度信息,没有考虑指纹图像自身的方向结构特点,对指纹图像的二值化效果不理想. 本文首先对常用的二值化算法进行了讨论,并主要通过实验比较了两种特别针对指纹图像的二值化算法。 通常认为一个好的针对指纹图像的二值化算法应满足以下几点要求[f。1]: ●保持纹线的原始走向; ●相关领域内指纹的纹线走向基本一致; ●避免造成指纹纹线的中断和粘连; ●避免生成虚假指纹纹线; ●纹线间的间距变化平稳; 2图像的二值化算法 在很多情况下,图象是由具有不同灰度的两类区域组成的。如在指纹图象中,指纹脊线和谷线就由不同的灰度构成,通常脊线要比谷线暗。所谓灰度图象的二值化就是通过设定阀值,把它变为仅用两个灰度值分别表示图象的前景和背景颜色的二值图象。图象的二值化可以根据下面的阀值来处理: 假设一幅灰度图的像素值为f(i,j)∈(r1,r2 ,…,rm),设有一阀值为T=ri ,1≤i≤m,则: 二值化的方法很多,关键在于阀值T的选取。而T的取值方法又取决于二值化的技术。T的选择有基于由点的像灰度值单独决定的、有由像素的局部特征决定的、也有基于全局像素决定的。阀值可以分为两类:全局阀值和局部阀值。 1)全局阈值 全局阈值是在整个图像中将灰度阈值的值设置为常数。如果背景的灰度值在整个图像中可以合理的看作恒定,而且所有的物体于背景都具有几乎相同的的对比度,那么只要选择了正确的阈值,使用一个全局阈值可以得到非常好的的效果。代表算法有最大类间方差法(OSTU方法)。 OSTU方法计算简单,稳定有效,是实际应用中经常采用的方法。但是它对噪声和目标大小十分敏感,仅对类间方差是单峰的图像有较好效果。当目标与背景的大小比例悬殊时,类间方差准则函数可能为双峰或多峰,此时OSTU方法就会失效。 2)自适应阈值 自适应阈值化算法也称动态局部阈值化算法。所谓动态是指根据每个像素及其邻域像素的灰度值情况动态地计算分割所需的阈值,如:Bernsen算法,它对图像上的每个点以之为中心取一个局部窗口,则该点的阈值为窗口中最大灰度和最小灰度的平均,依次对每个点根据其阈值进行二值化。 4.基于方向图的动态阈值指纹图像二值化方法

Agilent——眼图、抖动、相噪 随着数据速率超过Gb/s水平,工程师必须能够识别和解决抖动问题。抖动是在高速数据传输线中导致误码的定时噪声。如果系统的数据速率提高,在几秒内测得的抖动幅度会大体不变,但在位周期的几分之一时间内测量时,它会随着数据速率成比例提高,进而导致误码。新兴技术要求误码率(BER),亦即误码数量与传输的总码数之比,低于一万亿分之一(10-12)。随着数据通信、总线和底板的数据速率提高,市场上已经出现许多不同的抖动检定技术,这些技术采用各种不同的实验室设备,包括实时数字示波器、取样时间间隔分析仪(TIA)、等时取样示波器、模拟相位检波器和误码率测试仪(BERT)。为解决高数据速率上难以解决的抖动问题,工程师必需理解同步和异步网络中使用的各种抖动分析技术 本文重点介绍3 Gb/s以上新兴技术的数据速率。低于3 Gb/s的实时示波器可以捕获连续的数据流,可以同时在时域和频域中分析数据流;在更高的数据速率上,抖动分析要更具挑战性。本文将从数字工程师的角度,介绍应对SONET/SDH挑战的各种经验。 抖动分析基本上包括比较抖动时钟信号和参考时钟信号。参考时钟是一种单独的黄金标准时钟,或从数据中重建的时钟。在高数据速率时,分析每个时钟的唯一技术是位检测和误码率测试;其它技术则采用某种取样技术。 如图1所示,眼图是逻辑脉冲的重叠。它为测量信号质量提供了一种有用的工具,即使在极高的数据速率时,也可以在等时取样示波器上简便生成。边沿由‘1’到‘0’转换和‘0’到‘1’转换组成,样点位于眼图的中心。如果电压(或功率)高于样点,则码被标为逻辑‘1’;如果低于样点,则标为‘0’。系统时钟决定着各个位的样点水平位置。 图1: 具有各项定义的眼图 E1是逻辑‘1’的平均电压或功率电平,E0是逻辑‘0’的平均电压或功率电平。参考点t = 0在左边的交点进行选择,右边的交点及其后是位周期TB。

1设计目的与要求 1.1 设计目的 (1)熟悉和掌握MATLAB程序设计方法。 (2)学习和掌握MATLAB图像处理工具箱。 (2)了解图像分割和图像二值化的原理。 (3)掌握图像二值化技术阈值的选取。 (4)将原彩色图像变为二值化后的图像,通过二维最大熵图像分割法对图像进行分割达到预期目的。 1.2 设计要求 (1)了解图像变换的意义和手段。 (2)熟悉最大熵和二值化的基本性质。 (3)通过本实验掌握利用MATLAB编程实现数字图像处理。 (4)理解图像分割的原理,了解其应用,掌握最大熵和二值化分割的方法。

2 设计方案 2.1 图像二值化 图像二值化是数字图像处理技术中的一项基本技术,二值化图像的显示与打印十分方便,存储与传输也非常容易,在目标识别、图像分析、文本增强、字符识别等领域得到广泛应用。图像二值化是将灰度图像转化为只有黑白两类像素的图像,大多采用阈值化算法处理。在不同的应用中,阈值的选取决定着图像特。 征信息的保留。因此,图像二值化技术的关键在于如何选取阈值。 2.2 最大熵原理 最大熵原理:最大熵原理是在1957 年由E.T.Jaynes 提出的,其主要思想是,在只掌握关于未知分布的部分知识时,应该选取符合这些知识但熵值最大的概率分布。因为在这种情况下,符合已知知识的概率分布可能不止一个。我们知道,熵定义的实际上是一个随机变量的不确定性,熵最大的时候,说明随机变量最不确定,换句话说,也就是随机变量最随机,对其行为做准确预测最困难。 图像分割中最大熵的引入:在图像分割中若假定以灰度级T 分割图像,则图像中低于灰度级T 的像素点构成目标物体,高于灰度级T 的像素点构成背景那么各个灰度级在图像分割后的两区域中的概率如下: O :t i N N (0<=i<=t) (3.2.1) B : t i N N N - (t+1<=i<=255) (3.2.2) 其中Ni 为图像中灰度级为i 的像素点个数,Nt 为灰度级从0~t 的像素点总和,N 为 图像总像素点,t 为假定灰度阈值T 。 ) l og()( t i t i N N N N H ∑-= (0<=i<=t) (3.2.3) ) log()( t i t i B N N N N N N H ---=∑ (t+1<=i<=255) (3.2.4)

一种软件去除键抖动的方法 一种软件去除键抖动的方法 摘要:单片机控制系统中大多使用控制键来实现控制功能。消除按键瞬间的抖动是设计者必须要考虑的问题。本文介绍一种很实用的软件去抖动方法,它借助于单片机内的定时中断资源,只要运算一下逻辑表达就完成了去抖动。这个方法效率高,不耗机时且易实现。文中使用的逻辑表达式由简单卡诺图和真值表推出,使该方法的机理容易理解。文中还提供用C51单片机编程语言编写的实用例程。关键词:单片机键处理控制系统去抖动键盘概述在单片机控制系统中,通过按键实现控制功能是很常见的。对按键处理的重要环节是去抖动,包括去除按下和抬起瞬间的抖动。去抖动的方法有很多种,如使用R-S触发器的硬件方法、运用不同算法的各种软件方法等。硬件方法会增加成本和体积,对于按键较多的矩阵式键盘,会用硬件方法;软件方法用的比较普遍,但有一种加固定延时的去抖动法效率最低,它以无谓地耗费机时来实现去抖动。此处介绍的是一种软件方法。简单说来是一种运算法,配合定时中断读取按键,通过运算逻辑表达式:Keradyn=KtempKinput+Kreadyn-1(Ktemp⊙Kinput)(1) Ktemp=Kinput(2) 可以获得消除抖动的按键消息。这种方法效率高,不需耗时的循环等待,而且算法简单、使用方便。一、基本原理由于按键的按下与抬起都会有10~20ms的抖动毛刺存在,因此,为了获取稳定的按键信息,须要避开这段抖动期。设置3个变量Kready、Ktemp和Kinput,并设置定时中断周期为20ms。在定时中断服务程序中读取按键,并把读取的数据存于变量Kinput中。变量Kready中是所需要的稳定的按键信息;Ktemp是中间变量,它的值是上一次的Kinput。根据当前按键的状态,考虑到Kready中是20ms抖动后的有效键信息,则Kready、Ktemp和Kinput之间,在不同时刻的状态关系如表1所列。表 1 时刻KreadyKtempKinput1000200130104001511161117110810191101000011000 时刻1为没有键按下的初始状态;时刻2的Kinput为1,但时刻3的Kinput又变为0,说明时刻2的Kinput为1并不是有键按下,可能只是干扰,所以Kreqdy为0;时刻4同时刻2的情况类似,但是时刻4和时刻5时Kinput都为1,说明有按键按下,在时刻5时Kready为1;虽然时刻7时Kinput为0,但时刻5、6、

1眼图概述 1.1 串行数据的传输 由于通讯技术发展的需要,特别是以太网技术的爆炸式应用和发展,使得电子系统从传统的并行总线转为串行总线。串行信号种类繁多,如PCI Express、SPI、USB等,其传输信号类型时刻在增加。为何串行总线目前应用越来越广泛呢?相比并行数据传输,串行数据传输的整体特点如下: 1 信号线的数量减少,成本降低 2 消除了并行数据之间传输的延迟问题 3 时钟是嵌入到数据中的,数据和时钟之间的传输延迟也同样消除了 4 传输线的PCB设计也更容易些 5 信号完整性测试也更容易 实际中,描述串行数据的常用单位是波特率和UI,串行数据传输示例如下: 图串行数据传输示例 例如,比特率为3.125Gb/s的信号表示为每秒传送的数据比特位是3.125G比特,对应的一个单位间隔即为1UI。1UI表示一个比特位的宽度,它是波特率的倒数,即1UI=1/(3.125Gb/s)=320ps。现在比较常见的串行信号码形是NRZ码,因此在一般的情况下对于串行数据信号,我们的工作均是针对NRZ码进行的。 1.2 眼图的形成原理 眼图,是由于示波器的余辉作用,将扫描所得的每一个码元波形重叠在一起,从而形成眼图。眼图中包含了丰富的信息,从眼图上可以观察出码间串扰和噪声的影响,体现了数字信号整体的特征,从而可以估计系统优劣程度,因而眼图分析是高速互连系统信号完整性分析的核心。另外也可以用此图形对接收滤波器的特性加以调整,以减小码间串扰,

改善系统的传输性能。 目前,一般均可以用示波器观测到信号的眼图,其具体的操作方法为:将示波器跨接在接收滤波器的输出端,然后调整示波器扫描周期,使示波器水平扫描周期与接收码元的周期同步,这时示波器屏幕上看到的图形就称为眼图。示波器一般测量的信号是一些位或某一段时间的波形,更多的反映的是细节信息,而眼图则反映的是链路上传输的所有数字信号的整体特征,两者对比如下图所示: 图示波器中的信号与眼图 如果示波器的整个显示屏幕宽度为100ns,则表示在示波器的有效频宽、取样率及记忆体配合下,得到了100ns下的波形资料。但是,对于一个系统而言,分析这么短的时间内的信号并不具有代表性,例如信号在每一百万位元会出现一次突波(Spike),但在这100ns 时间内,突波出现的机率很小,因此会错过某些重要的信息。如果要衡量整个系统的性能,这么短的时间内测量得到的数据显然是不够的。设想,如果可以以重复叠加的方式,将新的信号不断的加入显示屏幕中,但却仍然记录着前次的波形,只要累积时间够久,就可以形成眼图,从而可以了解到整个系统的性能,如串扰、噪声以及其他的一些参数,为整个系统性能的改善提供依据。 分析实际眼图,再结合理论,一个完整的眼图应该包含从“000”到“111”的所有状态组,且每一个状态组发生的次数要尽量一致,否则有些信息将无法呈现在屏幕上,八种状态形成的眼图如下所示:

车牌识别中二值化方法的研究与实现 摘要:在基于数字图像处理的车牌识别技术的研究过程中,因为车牌定位和字符分割一般都是基于车牌区域的二值化结果进行的,因此对图像的二值化是非常关键的一步。二值化最主要的是阈值的确定,文章对比了几种常规的车牌图像全局阈值二值化处理算法,发现这些方法不够理想,然后提出几种新的方法——基于图像直方图波形分析的车牌图像二值化处理算法;考虑到光照变化以及定位出的车牌周边环境和自身干扰等因素,提出了一种新的车牌二值化的方法,这种方法结合了高斯拉普拉斯算子法和迭代法;而不均匀光照下的图像二值化是数字图像处理中的另一个难题.为此,本文提出一种解决办法,首先使用同态滤波去掉车牌图像的不均匀光照的影响,然后使用改进的Bernsen算法对车牌图像进行二值化。实验表明,这三种方法在进行车牌图像二值化处理时效果比较理想。 关键词:车牌识别;二值化;高斯拉普拉斯算子;图像直方图;不均匀光线 Realize and Research on binarization method of license plate recognition Abstrac t:During the research for the license plate recognition based on the Distal Image Processing Technology,because the location and segmentation of license plate are usually based on the binarized image,the image binaryzation is a key step.The most important part of the image binaryzation is the determination of threshold.In this paper,severalmethods have been compared,and also the basic principles and computer simulation results of inter-class varimaxand maximum entropy method have been analyzed.But we have found that these methods are not optional when used to process vehicle license plate images.Therefore,a new method has been put forward,which is the arithtactic of license plate image binarization based on image histogram.Considering the changes of illumination,the surrounding environment of the license plate and the license plate itself,a new method of taking threshold value of binarization is introduced.This method combines the Gauss-Laplace method and the iteration method.It is a difficult task to binarize image under nonuniform illumination.A new method is presented as follows:at first,it enhances the plate image quality by homomorphic filtering to eliminate the bad effect of the nonuniform illumination;then,binarizes the plate image by a improved Bernsen algorithm.It has been proved that the three methods are well when used to process vehicle license plate images. Key words:Vehicle license plate recognition, binary, gaosilapulasi operator, image histogram, uneven light

【012】按键消抖 点击数:919 发布日期:2006-6-23 19:29:00 【收藏】【评论】【打印】【编程爱好者论坛】【关闭】 参考: 《单片机原理及接口技术》(李朝青) 按键电路:常用的非编码键盘,每个键都是一个常开开关电路。 按键消抖: 通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,电压信号小型如下图。由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,如下图。抖动时间的长短由按键的机械特性决定,一般为5ms~10ms。这是一个很重要的时间参数,在很多场合都要用到。 按键稳定闭合时间的长短则是由操作人员的按键动作决定的,一般为零点几秒至数秒。键抖动会引起一次按键被误读多次。为确保CPU对键的一次闭合仅作一次

处理,必须去除键抖动。在键闭合稳定时读取键的状态,并且必须判别到键释放稳定后再作处理。按键的抖动,可用硬件或软件两种方法。 <1> 硬件消抖:在键数较少时可用硬件方法消除键抖动。下图所示的RS触发器为常用的硬件去抖。 图中两个“与非”门构成一个RS触发器。当按键未按下时,输出为1;当键按下时,输出为0。此时即使用按键的机械性能,使按键因弹性抖动而产生瞬时断开(抖动跳开B),中要按键不返回原始状态A,双稳态电路的状态不改变,输出保持为0,不会产生抖动的波形。也就是说,即使B点的电压波形是抖动的,但经双稳态电路之后,其输出为正规的矩形波。这一点通过分析RS触发器的工作过程很容易得到验证。 <2> 软件消抖:如果按键较多,常用软件方法去抖,即检测出键闭合后执行一个延时程序,产生5ms~10ms的延时,让前沿抖动消失后再一次检测键的状态,如果仍保持闭合状态电平,则确认为真正有键按下。当检测到按键释放后,也要给5ms~10ms的延时,待后沿抖动消失后才能转入该键的处理程序。

图像二值化算法研究与实现 摘要:图像二值化是图像预处理中的一项重要技术,在模式识别、光学字符识别、医学成像等方面都有重要应用。论文介绍了图像及数字图像处理技术的一些概念和相关知识;对VC++ 软件的发展和软件在图像处理中的应用做了简要介绍;还介绍了图像二值化算法以及利用VC++软件工具进行算法的实现。论文重点实现了图像分割技术中常用灰度图像二值化算法,如Otsu算法、Bernsen算法,并对这些算法运行的实验结果进行分析与比较。 关键词:图像处理;二值化;VC++; 1.引言 1.1 图像与数字图像 图像就是用各种观测系统观测客观世界获得的且可以直接或间接作用与人眼而产生视觉的实体。视觉是人类从大自然中获取信息的最主要的手段。拒统计,在人类获取的信息中,视觉信息约占60%,听觉信息约占20%,其他方式加起来才约占20%。由此可见,视觉信息对人类非常重要。同时,图像又是人类获取视觉信息的主要途径,是人类能体验的最重要、最丰富、信息量最大的信息源。通常,客观事物在空间上都是三维的(3D)的,但是从客观景物获得的图像却是属于二维(2D)平面的。 数字图像:数字图像是将连续的模拟图像经过离散化处理后得到的计算机能够辨识的点阵图像。在严格意义上讲,数字图像是经过等距离矩形网格采样,对幅度进行等间隔量化的二维函数。因此,数字图像实际上就是被量化的二维采样数组。 1.2 数字图像处理技术内容与发展现状 数字图像处理就是采用一定的算法对数字图像进行处理,以获得人眼视觉或者某种接受系统所需要的图像处理过程。图像处理的基础是数字,主要任务是进行各种算法设计和算法实现。 图像处理技术的发展大致经历了初创期、发展期、普及期和实用化期4个阶段。初创期开始与20世纪60年代,当时的图像采用像素型光栅进行少秒显示,大多采用中、大型机对其处理。在这一时期,由于图像存储成本高、处理设备昂贵,其应用面很窄。进入20世纪70年代的发展期,开始大量采用中、小型机进行处理,图像处理也逐渐改用光栅扫描方式,特别是CT和卫星遥感图像的出现,对图像处理技术的发展起到了很好的推动作用。到了20世纪80年代,图像处理技术进入普及期,此时的微机已经能够担当起图形图像处理的任务。超大规模集成电路(Very Large Scale Integration, VLSI)的出现更使处理速度大大提高,设备造价也进一步降低,极大地促进了图形图像系统的普及和应用。20世纪90年代是图像处理技术的实用化时期,图像处理的信息量巨大,对处理速度的要求极高。 1.3 图像二值化原理及意义 图像二值化是指用灰度变换来研究灰度图像的一种常用方法,即设定某一阈值将灰度

按键消抖 无论Nexys4开发板还是zedboard开发板,开发板上的按钮和拨动开关都是机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,为了不产生这种现象而作的措施就是按键消抖。 在时序逻辑电路中,我们通常需要手动产生一个上升沿或者一个下降沿,如将拨动开关拨上去(由0到1),这样就产生了一个上升沿;吧拨动开关从上面拨下来(由1到0),这样就产生了一个下降沿。如果开关有机械抖动的话,那么将开关从下拨到上或从上拨到下面,就会产生若干个上升沿或下降沿,如图1,这样电路就会产生意想不到的情况。因此,如果将拨动开关当作时钟使用,必须对其进行消抖。 抖动时间的长短由按键的机械特性决定,一般为20ms左右。 图1 按键抖动图 消抖是为了避免在按键按下或是抬起时电平剧烈抖动带来的影响。按键的消抖,可用硬件或软件两种方法。 硬件消抖

在键数较少时可用硬件方法消除键抖动。图2所示的RS触发器为常用的硬件去抖电路。 图2 利用RS触发器消除按键抖动 图中两个“与非”门构成一个RS触发器。当按键未按下时,输出为0;当键按下时,输出为1。此时即使用按键的机械性能,使按键因弹性抖动而产生瞬时断开(抖动跳开B),只要按键不返回原始状态A,双稳态电路的状态不改变,输出保持为0,不会产生抖动的波形。也就是说,即使B点的电压波形是抖动的,但经双稳态电路之后,其输出为正规的矩形波。 软件消抖 如果按键较多,常用软件方法去抖,即检测出键闭合后执行一个延时程序,20ms左右的延时,让前沿抖动消失后再一次检测键的状态,如果仍保持闭合状态电平,则确认为真正有键按下。当检测到按键释放后,也要给20ms左右的延时,待后沿抖动消失后才能转入该键的处理程序。

科技信息 SCIENCE &TECHNOLOGY INFORMATION 2011年第23期0引言 指纹识别技术是当前生物识别技术中应用最为广泛的一种。自动指纹识别的关键技术包含指纹预处理,指纹特征提取,指纹特征匹配几方面。实际得到广泛应用的指纹特征匹配多是基于指纹细节点特征。指纹细节点特征的提取通常在细化二值指纹图像上进行。图像二值化就是根据一定的规则,将一幅图像变为只用两阶灰度表示的黑白图像。二值化指纹图像中通常黑像素表示指纹的脊线,而白像素表示指纹的谷线和背景区。 1指纹图像二值化算法分析 指纹图像二值化方法主要有两种:灰度阈值分割法和邻域分析法。目前,自动指纹识别系统中应用的灰度阈值分割二值化算法根据阈值选取方式的不同可以分为全局固定阈值法和局部自适应动态阈值法。 1.1全局固定阈值法 全局固定阈值法一般根据整幅指纹图像前景区的灰度直方图分布选择一个合适的判断阈值,对整幅指纹图像进行二值化处理。该算法在指纹图像对比度较好的情况下,统计直方图的两个峰值比较明显,能够选择合适的阈值对指纹图像进行二值化处理。但该判定阈值的选择完全依赖于统计直方图,抵抗噪声干扰的能力较弱。另外,采集到的指纹图像中心区域和边缘区域的灰度分布一般难以达到一致,故全局固定阈值二值化算法并不能很好地适应实际处理的要求。1.2局部自适应动态阈值法 局部自适应动态阈值法是将整幅指纹图像分块,结合各块图像的自身特点,为每块图像分别选取不同的阈值,对各块指纹图像区域进行二值化处理。分块大小的设定和局部判决阈值的选取对指纹图像二值化效果起着关键作用。最佳的分块大小应该选取指纹图像纹线的整数倍距离,实际应用中很难精确地确定出指纹纹线距离,而且同一指纹图像的各区域纹线距离并不总是一致的。局部自适应动态阈值选取的一般依据是:对每块图像选取的阈值应尽量使该块图像内大于该阈值的像素点数和小于该阈值的像素点数大致相等。 该类算法实现的一般步骤为:首先对整幅指纹图像进行分块;然后根据某一规则确定局部灰度阈值T ;最后将方块中每个像素的灰度值与T 值比较。如果低于灰度阈值T 则视为脊线点,置为0;反之则视为谷线点,置为255。通常阈值T 取块内灰度均值较为简单,但抗噪能力较差。下面对现有的局部阈值选取方法进行分析。 文献[2]将指纹的方向信息引入到二值化处理过程中,综合考虑指纹的方向信息和自适应选择局部阈值,提出了一种结合方向信息的自适应局部阈值二值化算法。局部阈值确定采用迭代法,首先将指纹图像分成W ×W 的块,计算每块的平均灰度值;然后分别计算该区域内大于等于阈值T 的像素点个数N H 和小于阈值T 的像素点个数N L ;当|Nh-Nl|≤α(α=W ×W ×10%)时,则T 为阈值,否则循环调整T 值,直到得到满足上述不等式条件的阈值T 。根据沿指纹脊线方向上的像素灰度阶近似一致的特点,制定二值化规则。具体参见文献[2]。 文献[3]在文献[2]的基础上有所改进,计算局部阈值时综合考虑周边邻域像素的影响,采用块重叠的方式求取阈值T ,并对块内像素进行分类二值化。对二值化图像根据指纹纹理特点和方向信息进行去除粘线,消除孔洞的处理,在一定程度上提高了算法的鲁棒性和抗噪能力,但同时也增加了算法复杂度,降低了处理效率。 文献[4]指出对于一幅指纹图像,由于在脊线和谷线的分界处灰度的变化最大,不确定性最高,以脊线和谷线分界处灰度阶作为分割阈值得到的信息熵最大。文献[5]利用此结论将信息熵引入到指纹图像二值化算法中,先对指纹图像进行分块处理,提取指纹图像有效区域,然 后求取使局部信息熵最大的灰度值作为判决阈值进行二值化处理。该算法对噪声具有鲁棒性,能够有效实现对指纹图像的二值化,提高了细节特征提取结果的准确率,但灰度阈值的计算复杂度较大。1.3邻域分析法 邻域分析法充分利用指纹图像纹线的连续性和脊线谷线相间隔的特点。若指纹图像的某一点在脊线上,则与该点相邻的切线方向上的像素点也应位于脊线上,而该点纹线方向的垂直方向上的点应位于谷线上。因此,对于脊线上的点来说,沿纹线方向的灰度均值较小,沿纹线方向的垂直方向上灰度均值较大。 文献[6]基于指纹图像的这一特点给出一种基于方向信息的指纹图像自适应二值化算法。具体算法为:对于前景区域每一像素点g(x,y),以其为中心分别计算纹线方向上的m 个邻域点的加权灰度均值Gh(x,y)和纹线垂直方向上m 个点的加权灰度均值Gv(x,y);若Gh(x,y) 在使用单片机搭建有人机交互的系统时需要用到键盘,因为单片机工作时间都是纳秒与毫秒级别,但是我们人体的反应时间最少要0.2秒,之间差距很大,现实过程中也会不小心碰到按键,正常的按下按键应该是持续数十秒的稳定。一、按键电路常用的非编码键盘,每个在使用单片机搭建有人机交互的系统时需要用到键盘,因为单片机工作时间都是纳秒与毫秒级别,但是我们人体的反应时间最少要0.2秒,之间差距很大,现实过程中也会不小心碰到按键,正常的按下按键应该是持续数十秒的稳定。 一、按键电路 常用的非编码键盘,每个键都是一个常开开关电路。 计数器输入脉冲最好不要直接接普通的按键开关,因为记数器的记数速度非常快,按键、触点等接触时会有多次接通和断开的现象。我们感觉不到,可是记数器却都记录了下来。例如,虽然只按了1下,记数器可能记了3下。因此,使用按键的记数电路都会增加单稳态电路避免记数错误。 二、按键消抖 通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,电压信号小型如下图。由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,如下图。抖动时间的长短由按键的机械特性决定,一般为5ms~10ms。这是一个很重要的时间参数,在很多场合都要用到。 按键稳定闭合时间的长短则是由操作人员的按键动作决定的,一般为零点几秒至数秒。键抖动会引起一次按键被误读多次。为确保CPU对键的一次闭合仅作一次处理,必须去除键抖动。在键闭合稳定时读取键的状态,并且必须判别到键释放稳定后再作处理。按键的抖动,可用硬件或软件两种方法。 三、硬件消抖 在键数较少时可用硬件方法消除键抖动。下图所示的RS触发器为常用的硬件去抖。消抖电路如下 图中两个“与非”门构成一个RS触发器。当按键未按下时,输出为1;当键按下时,输出为0。此时即使用按键的机械性能,使按键因弹性抖动而产生瞬时断开(抖动跳开B),中要按键不返回原始状态A,双稳态电路的状态不改变,输出按键消抖