实验一EDA软件实验

实验性质:验证性实验级别:必做

开课单位:信息与通信工程学院通信工程系学时:4学时

一、实验目的:

1、了解Xilinx ISE 6.2软件的功能。

2、掌握Xilinx ISE 6.2的VHDL输入方法。

3、掌握Xilinx ISE 6.2的原理图文件输入和元件库的调用方法。

4、掌握Xilinx ISE 6.2软件元件的生成方法和调用方法。

5、掌握Xilinx ISE 6.2编译、功能仿真和时序仿真。

6、掌握Xilinx ISE 6.2原理图设计、管脚分配、综合与实现、数据流下载方法。

7、了解所编电路器件资源的消耗情况。

二、实验器材:

计算机、Quartus II软件或xilinx ISE

三、实验内容:

1、本实验以三线八线译码器(LS74138)为例,在Xilinx ISE 6.2软件平台上完成设计电路的VHDL

文本输入、语法检查、编译、仿真、管脚分配和编程下载等操作。下载芯片选择Xilinx公司的CoolRunner II系列XC2C256-7PQ208作为目标仿真芯片。

2、用1中所设计的的三线八线译码器(LS74138)生成一个LS74138元件,在Xilinx ISE 6.2软

件原理图设计平台上完成LS74138元件的调用,用原理图的方法设计三线八线译码器(LS74138),实现编译,仿真,管脚分配和编程下载等操作。

四、实验步骤:

4.1 Xilinx ISE 6.2环境

1、三线八线译码器(74LS138)VHDL电路设计

(1)、三线八线译码器(74LS138)的VHDL源程序的输入

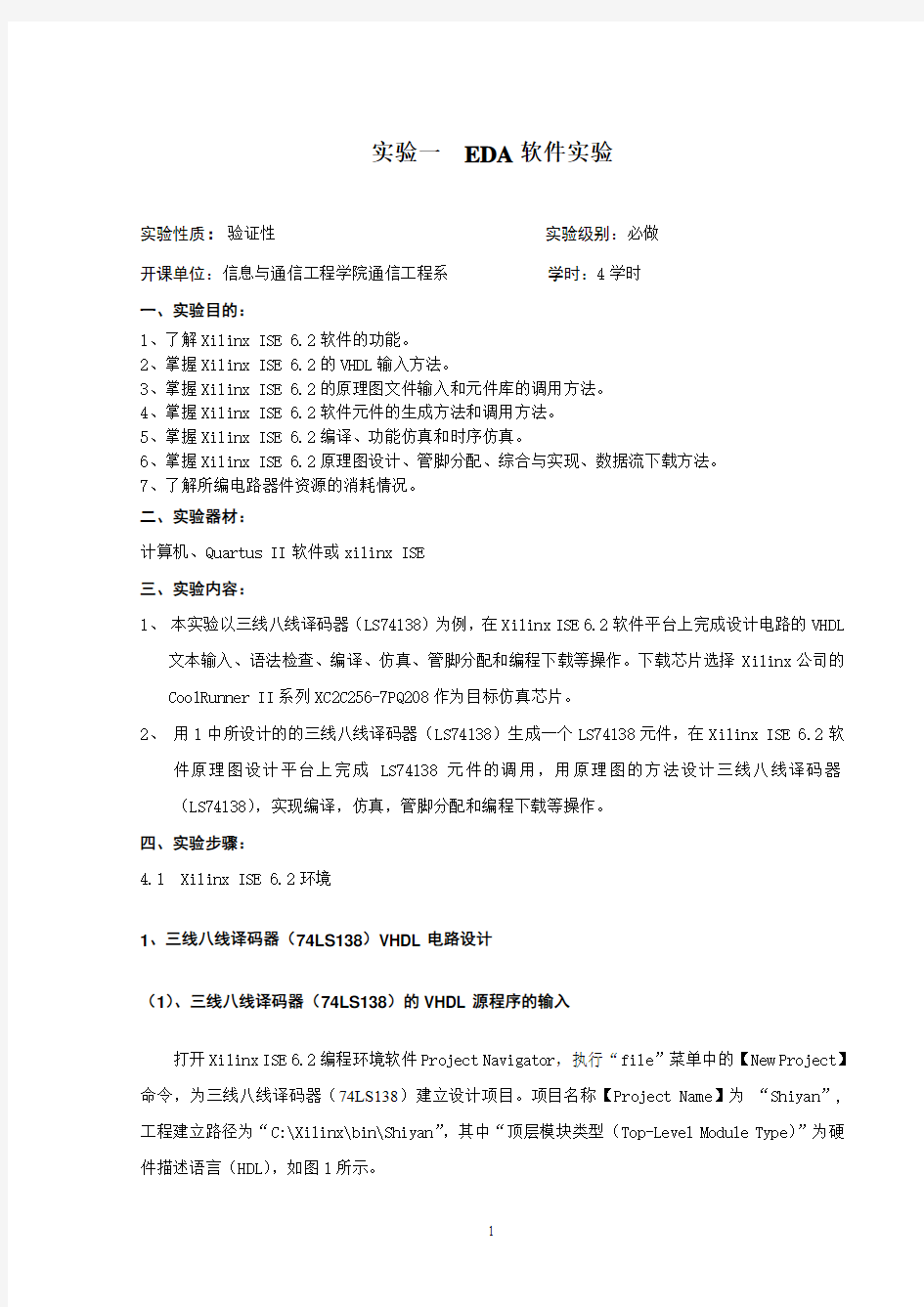

打开Xilinx ISE 6.2编程环境软件Project Navigator,执行“file”菜单中的【New Project】命令,为三线八线译码器(74LS138)建立设计项目。项目名称【Project Name】为“Shiyan”,工程建立路径为“C:\Xilinx\bin\Shiyan”,其中“顶层模块类型(Top-Level Module Type)”为硬件描述语言(HDL),如图1所示。

图1

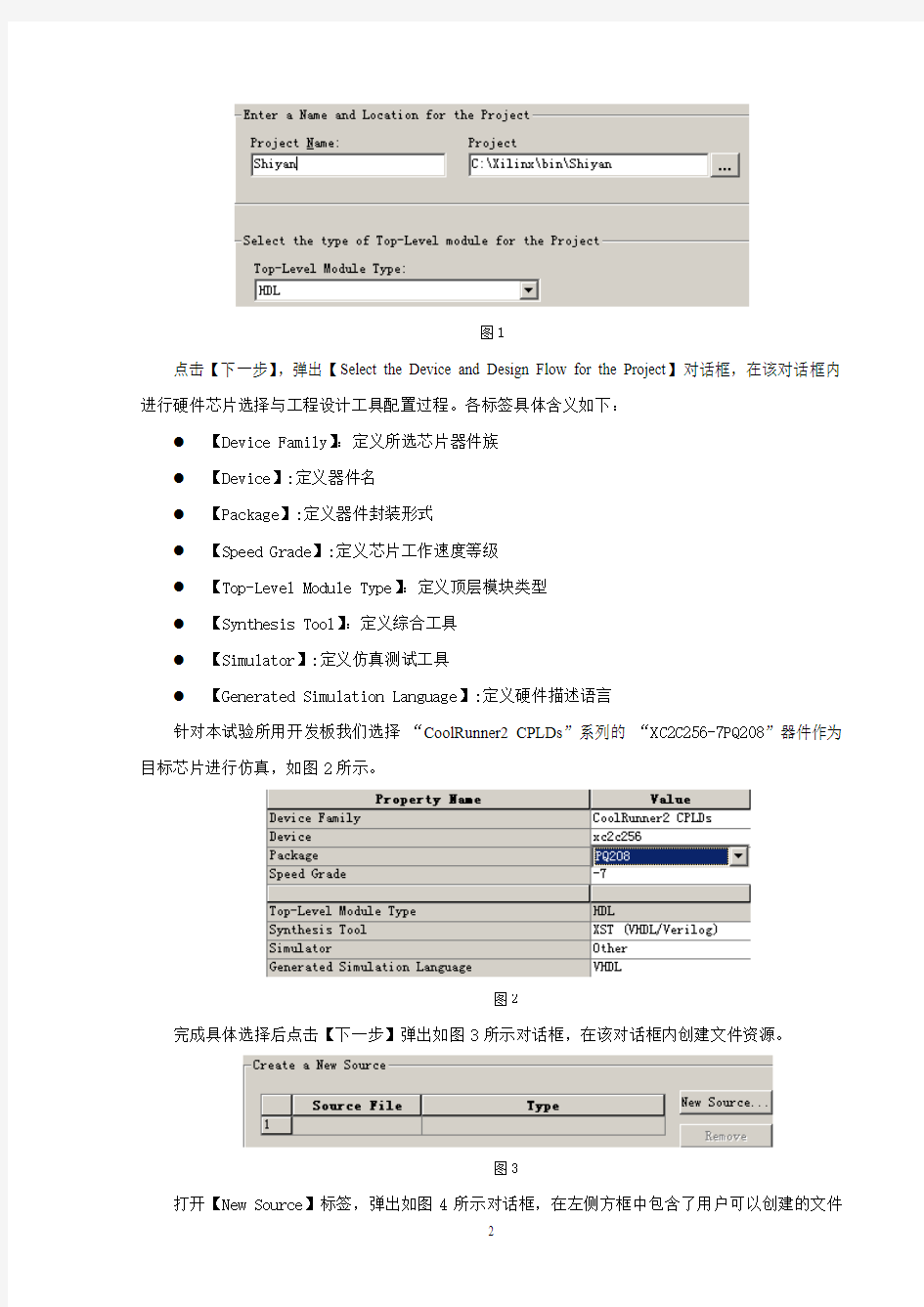

点击【下一步】,弹出【Select the Device and Design Flow for the Project】对话框,在该对话框内进行硬件芯片选择与工程设计工具配置过程。各标签具体含义如下:

●【Device Family】:定义所选芯片器件族

●【Device】:定义器件名

●【Package】:定义器件封装形式

●【Speed Grade】:定义芯片工作速度等级

●【Top-Level Module Type】:定义顶层模块类型

●【Synthesis Tool】:定义综合工具

●【Simulator】:定义仿真测试工具

●【Generated Simulation Language】:定义硬件描述语言

针对本试验所用开发板我们选择“CoolRunner2 CPLDs”系列的“XC2C256-7PQ208”器件作为目标芯片进行仿真,如图2所示。

图2

完成具体选择后点击【下一步】弹出如图3所示对话框,在该对话框内创建文件资源。

图3

类型,包括以下内容:

●【Schematic】:原理图类型文件

●【State Diagram】:状态图类型文件

●【Test Bench Waveform】:波形类型测试文件

●【User Document】:用户类型文件

●【Verilog Module】:Verilog类型文件

●【Verilog Test Fixture】:Verilog语言描述类型测试文件

●【VHDL Library】:VHDL库文件

●【VHDL Module】:VHDL类型模块文件

●【VHDL Package】:VHDL类型文件封装库

●【VHDL Test Bench】:VHDL语言描述类型测试文件

图4

在【File】标签下对话框内写入用户自定义的文件名称,标签【Locatior】下显示了新定义文件的创建路径,选中标签【Add to proje】前的对号标记,将新创建的文74ls138添加到工程“Shiyan”中。点击【下一步】,弹出如图5所示对话框,在此对话框中输入三线八线译码器(74LS138)的的端口信息。

点击【下一步】弹出【New Source Information】对话框,在该对话框内显示了新建文件的属性及信息,如图6所示。

图6

点击【完成】返回资源创建对话框,其中显示了新建文件“LS74138.vhdl”,如图7。

图7

点击【下一步】弹出工程信息对话框【New Project Information】,该对话框给出了所设计的工程信息,如图8所示。

图8

点击【完成】标签结束新建工程过程。进入Xilinx ISE文本编辑方式,在文本框中编辑输入8位加法器的VHDL源程序,如下图所示:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- provided for instantiating Xilinx primitive components.

--library UNISIM;

--use UNISIM.VComponents.all;

entity ls74138 is

Port ( g1 : in std_logic;

g2 : in std_logic;

inp : in std_logic_vector(2 downto 0);

y : out std_logic_vector(7 downto 0));

end ls74138;

architecture Behavioral of ls74138 is

begin

process(g1,g2,inp)

begin

if((g1 and g2)='1') then

case inp is

when "000"=>y<="00000001";

when "001"=>y<="00000010";

when "010"=>y<="00000100";

when "011"=>y<="00001000";

when "100"=>y<="00010000";

when "101"=>y<="00100000";

when "110"=>y<="01000000";

when "111"=>y<="10000000";

when others=>y<="00000000";

end case;

else

y<="00000000";

end if;

end process;

end Behavioral;

在VHDL源程序中,G1和G2为两个使能控制信号,INP为命令码输入信号,Y为8位译码输出信号。

(2)、设计文件存盘与语法检查

图13 图14

完成程序代码输入后单击高亮“ls74138-behavioral(LS74138.vhdl)”标签(图13),此时工具窗口将显示“Process for Source(ls74138-behavioral)”。用鼠标右键点击Process窗口中【Check Syntax】标签,点击运行选项,进行程序语法检查,当显示一绿色对号标志时即表示程序中不存在语法问题,如图14所示。

(3)、仿真文件设计

为了验证所设计电路功能,需要输入测试文件对电路程序功能进行测试。在【Process】菜单中选择【New Source】选项,即可弹出如图5所示对话框,选择【VHDL Test Bench】添加测试向量文件,并将文件添加到LS74138模块中,如图15所示

图15 图16

运行行为仿真选项卡,Xilinx ISE自动调用ModelSim SE 6.1c仿真平台作为仿真工具。运行ModelSim SE 6.1c菜单【Simulate】->【Run】->【Restart】,将仿真时间点置零。在【transcript】窗口中输入仿真时间。在波形【Wave】窗口内使用按钮实现仿真图的“放大”“缩小”“全局”功能。图17即为电路仿真结果,由图中时序及逻辑关系可知该三线八线译码器

图17

测试向量参考程序如下:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY ls74138_tb_74138_vhd_tb IS

END ls74138_tb_74138_vhd_tb;

ARCHITECTURE behavior OF ls74138_tb_74138_vhd_tb IS

COMPONENT ls74138

PORT(

G1 : IN std_logic;

G2 : IN std_logic;

INP : IN std_logic_vector( 2 downto 0);

Y : OUT std_logic_vector(7 downto 0)

);

END COMPONENT;

SIGNAL G1 : std_logic;

SIGNAL G2 : std_logic;

SIGNAL INP : std_logic_vector( 2 downto 0);

SIGNAL Y : std_logic_vector(7 downto 0);

BEGIN

uut: ls74138 PORT MAP(

G1 => G1,

G2 => G2,

INP => INP,

Y => Y

);

-- *** Test Bench - User Defined Section ***

u1:PROCESS

BEGIN

G1<='0';

G1<='1';

wait for 90 us;

G1<='0';

wait;

END PROCESS u1;

u2:PROCESS

BEGIN

G2<='0';

wait for 10 us;

G2<='1';

wait for 90 us;

G2<='0';

wait;

END PROCESS u2;

u3:PROCESS

BEGIN

INP<="000";

wait for 20 us;

INP<="001";

wait for 10 us;

INP<="010";

wait for 10 us;

INP<="011";

wait for 10 us;

INP<="100";

wait for 10 us;

INP<="101";

wait for 10 us;

INP<="110";

wait for 10 us;

INP<="111";

wait;

end PROCESS u3;

-- *** End Test Bench - User Defined Section ***

END behavior ;

(4)芯片管脚定义

如前所述添加用户定义限制文件,运行【Assign Package Pins】选项卡,Xilinx ISE将弹出管脚分配窗口,在如图19,输入各个端口管脚位置并保存,完成芯片管脚定义。

图18 图19

(5)编译与综合

图20 图21

运行【Process for Source】中的【Implement Design】(图20),ISE将自动完成编译并调用内嵌的综合工具XST完成综合过程,运行结果如图21所示。

编译通过后即自动生成了电路烧录下载文件(*.jed)以及资源消耗报告,通过该报告即可了解所设计电路的资源消耗情况。

图22

由图22可知,在三线八线译码器(74LS138)的设计中使用了8个宏单元,9个乘积项,8个寄存器单元,13个用户引脚及5个功能输入块。

(5)、编程下载

本试验用并行电缆将开发实验平台与计算机接在一起。确认下载电缆连接无误后执行Xilinx ISE的【iMPACT】命令,将三线八线译码器(74LS138)设计文件下载到目标芯片XC2C256-7PQ208中,硬件验证所设计电路功能。

2、元件的生成、调用和仿真

1、新建原理图文件,命名为“Sch_LS74138”并添加到工程“Shiyan”中,如图23。点击【下一步】完成原理图文件的创建。在弹出的原理图编辑框内选择【Symbols】标签,在其目录列表内显示了所有可用电路器件,其中包括了我们所设计的LS74138(图24)。

图23 图24

双击“ls74138”将其放置到原理图编辑区内。点击为器件添加外围端口,如图25所示。

图25

将原理图文件保存后返回【Xilinx Project Navigator】平台,此时已经将程序所设计的器件

“LS74138”配置给了原理图文件“sch_ls74138”,其余电路仿真、管脚配置、编译、综合以及电路下载等过程与文本设计方式一致,在此不在重复说明。

五、预习与思考:

思考:比较VHDL语言和原理图的设计方法,这两种设计各有哪些优缺点。

实验二 组合逻辑电路的VHDL 语言实现

实验性质:验证性 实验级别:必做 开课单位:信息与通信工程学院通信工程系 学时:2学时 一、实验目的:

1、掌握VHDL 语言设计基本单元及其构成

2、掌握用VHDL 语言设计基本的组合逻辑电路的方法。

3、掌握VHDL 语言的主要描述语句。 二、实验器材:

计算机、Quartus II 软件或Xilinx ISE 三、实验内容:

1、本实验以1位全加器为例,在Xilinx ISE 软件平台上完成设计电路的VHDL 文本输入,编辑,编

译,仿真,管脚分配和编程下载等操作。下载芯片选择Xilinx 公司的CoolRunner II 系列XC2C256-7PQ208作为目标仿真芯片。

2、用实验内容1所设计的全加器的VHDL 文件生成一个adder 的元件,在Xilinx ISE 软件原理图设

计平台上完成adder 元件的调用,用原理图的方法设计一个8位二进制加法器,实现编译,仿真,管脚分配和编程下载等操作。 3、或优先编码器、多路选择器等其它电路。 四、实验步骤:

(一)、用VHDL 语言实现八位加法器的设计并实现功能仿真。

全加器是带进位位信号的加法器,起逻辑表达式为:carryin dataB dataA Sum ++= 。它的真值表如表1所示,其中dataA 和dataB 为加数与被加数,carryin 是输入的进位位信号,而Sum 是和数,carryout 是输出进位位信号。参考真值表,实现八位全加器的功能。

表1

一)1位加法器的VHDL源程序参考如下:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following lines to use the declarations that are

-- provided for instantiating Xilinx primitive components.

--library UNISIM;

--use UNISIM.VComponents.all;

entity adder is

Port ( a : in std_logic;

b : in std_logic;

cin : in std_logic;

sum : out std_logic;

cout : out std_logic);

end adder;

architecture Behavioral of adder is

begin

sum <= (a xor b) xor cin;

cout <= (a and b) or (cin and a) or (cin and b);

end Behavioral;

测试向量参考程序如下:

-- VHDL Test Bench Created from source file adder.vhd -- 21:00:50 03/18/2008

-- Notes:

-- This testbench has been automatically generated using types std_logic and

-- std_logic_vector for the ports of the unit under test. Xilinx recommends

-- that these types always be used for the top-level I/O of a design in order

-- to guarantee that the testbench will bind correctly to the post-implementation

-- simulation model.

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY adder_adder_vhd_tb IS

END adder_adder_vhd_tb;

ARCHITECTURE behavior OF adder_adder_vhd_tb IS COMPONENT adder

PORT(

a : IN std_logic;

b : IN std_logic;

cin : IN std_logic;

sum : OUT std_logic;

cout : OUT std_logic

);

END COMPONENT;

SIGNAL a : std_logic;

SIGNAL b : std_logic;

SIGNAL cin : std_logic;

SIGNAL sum : std_logic;

SIGNAL cout : std_logic;

BEGIN

uut: adder PORT MAP(

a => a,

b => b,

cin => cin,

sum => sum,

cout => cout

);

BEGIN

a<='0';

wait for 10 us;

a<='1';

wait for 20 us;

a<='0';

wait for 10 us;

a<='1';

wait for 10 us;

a<='0';

wait for 20 us;

a<='1';

wait for 10 us;

a<='0';

wait for 10 us; a<='1';

wait;

END PROCESS u1; u2:process

begin

b<='1';

wait for 10 us;

b<='0';

wait for 10 us;

b<='1';

wait for 10 us;

b<='0';

wait for 10 us;

b<='1';

wait for 20 us;

wait for 10 us;

b<='1';

wait for 10 us;

b<='0';

wait for 20 us;

b<='1';

wait;

END PROCESS u2;

u3: process

begin

cin<='0';

wait for 40 us;

cin<='1';

wait for 20 us;

cin<='0';

wait;

end process u3;

END behavior;

仿真图如下1所示:

图 1

管脚分配和编程下载如实验一,这里不再累述。

二)用实验内容1所设计的全加器的VHDL文件生成一个adder的元件,在Xilinx ISE软件原理图设计平台上完成adder元件的调用,用原理图的方法设计一个8位二进制加法器:

在步骤一)在processer for Source:”adder”窗口点击Create Schematic Symbol如下图2所示,生成adder 的元件,在Sources in Project 窗口新建Schematic 文件命名adder8 ,如下图3所示,在Xilinx ECS 平台上点Symbols如图4所示,添加8个adder到原理图编辑区域,连接各元件并添加引脚,如图5

图2 图3

图4

仿真结果如下图:

(二)、用VHDL语言实现优先编码器的设计并实现功能仿真

优先计编码器常用于中断的优先级控制,以8输入,3位二进制输出的优先级编码器为例,当其中一个输入有效时,就可以输出一个对应得3位二进制编码。另外,当同时有几个输入有效时,将输出优先级最高的那个输入所对应得二进制编码。其真值表如下所示:

表2 优先编码器真值表

用VHDL语言实现优先编码器的设计并实现功能仿真验证其功

能。参考程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY priorityencoder IS

PORT (input:IN STD_LOGIC_VECTOR (7 DOWNTO 0);

y:OUT STD_LOGIC_VECTOR (2 DOWNTO 0));

END priorityencoder;

ARCHITECTURE rt1 OF priorityencoder IS

BEGIN

PROCESS (input)

BEGIN

IF(input(0)='0') THEN

y<="111";

ELSIF(input(1)='0') THEN

y<="110";

ELSIF(input(2)='0') THEN

y<="101";

ELSIF(input(3)='0') THEN

y<="100";

ELSIF(input(4)='0') THEN

y<="011";

ELSIF(input(5)='0') THEN

y<="010";

ELSIF(input(6)='0') THEN

y<="001";

ELSE

y<="000";

END IF;

END PROCESS;

END rt1;

测试向量参考程序如下:

-- VHDL Test Bench Created from source file priorityencoder.vhd -- 16:03:14 03/24/2008 --

-- Notes:

-- This testbench has been automatically generated using types std_logic and

-- std_logic_vector for the ports of the unit under test. Xilinx recommends

-- that these types always be used for the top-level I/O of a design in order -- to guarantee that the testbench will bind correctly to the post-implementation -- simulation model.

--

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY priorityencoder_priorityencoder_vhd_tb IS

END priorityencoder_priorityencoder_vhd_tb;

ARCHITECTURE behavior OF priorityencoder_priorityencoder_vhd_tb IS

COMPONENT priorityencoder

PORT(

input : IN std_logic_vector(7 downto 0);

y : OUT std_logic_vector(2 downto 0)

);

END COMPONENT;

SIGNAL input : std_logic_vector(7 downto 0);

SIGNAL y : std_logic_vector(2 downto 0);

BEGIN

uut: priorityencoder PORT MAP(

input => input,

y => y

);

-- *** Test Bench - User Defined Section ***

tb : PROCESS

BEGIN

input<="11011010";

wait for 10 us;

input<="11101101";

wait for 10 us;

input<="10110011";

wait for 10 us;

input<="11010111";

wait for 10 us;

input<="01101111";

wait for 10 us;

input<="11011111";

wait for 10 us;

input<="10111111";

wait for 10 us;

input<="11111111";

wait for 10 us;

input<="01111111";

wait for 10 us;

input<="11011011";

wait for 10 us;

《集成电路应用》课程实验实验一 4053门电路综合实验 学院:物理与信息工程学院 专业: 电子信息工程 年级: 2015级 姓名:张桢 学号: 指导老师:许志猛

实验一 4053门电路综合实验 一、实验目的: 1.掌握当前广泛使用的74/HC/HCT系列CMOS集成电路、包括门电路、反相 器、施密特触发器与非门等电路在振荡、整形、逻辑等方向的应用。 2.掌握4053的逻辑功能,并学会如何用4053设计门电路。 3.掌握多谐振荡器的设计原理,设计和实现一个多谐振荡器,学会选取和 计算元件参数。 二、元件和仪器: 1.CD4053三2通道数字控制模拟开关 2.万用表 3.示波器 4.电阻、电容 三、实验原理: 1.CD4053三2通道数字控制模拟开关 CD4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。CD4053的管脚图和功能表如下所示 4053引脚图

4053的8种逻辑功能 CD4053真值表 根据CD4053的逻辑功能,可以由CD4053由4053电路构成如下图所示8种逻辑门(反相器与非门或非门、反相器、三态门、RS 触发器、——RS 触发器、异或门等)。 输入状态 接通通道

]) 2)(()(ln[ T DD T DD T DD T V V V V V V V RC T -+--=2.多谐振荡器的设计 非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。电路的基本工作原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT 时,门的输出状态即发生变化。因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。 可以利用反相器设计出如下图所示的多谐振荡器 这样的多谐振荡器输出的信号周期计算公式为: 当R S ≈2R 时,若:VT=0.5VDD ,对于HC 和HCU 型器件,有 T ≈2.2RC 对于HCT 型器件,有 T ≈2.4RC 四、实验内容: 1. 验证CD4053的逻辑功能,用4053设计门电路,并验证其逻辑功能: (1)根据实验原理设计如下的反相器电路图: CD4053构成反相器电路

集成电路课程设计 目录 1 .引言 (1) 1.1 课题目的与意义 (1) 1.2 设计题目与要求 (1) 1.3 Tanner软件的介绍 (2) 2反相器设计 (2) 2.1 S-edit设计反相器 (2) 2.2反相器的瞬时分析 (3) 2.3反相器直流分析 (4) 3 L-edit画PMOS和NMOS布局图 (5) 3.1 L-edit的使用 (5) 3.2 使用L-Edit画PMOS布局图 (5) 3.3 使用L-Edit画NMOS布局图 (6) 3.4 使用L-Edit画基板节点元件 (7) 3.5 L-edit画反相器布局并作瞬时和直流分析 (7) 3.6使用LVS对比反相器 (8) 3.7关于功耗和延迟方面的计算 (9) 4.仿真注意事项 (11) 5 总结 (12) 参考文献 (13)

1 .引言 集成电路产业是信息产业的核心,在全球集成电路产业重心转移的背景下,中国集成电路产业取得了前所唯有的发展,为信息产业向纵深发展奠定了一定的基础。在全球集成电路竞争中,中国国产集成电路仍然处于较弱的地位,一方面供给无法满足中国电子整机产品的需求,另一方面则是自主创新能力不足。同时,也应看到中国集成电路产业发展的希望与契机,作为全球集成电路产业增长最快的地区和全球最具发展潜力的市场,伴随市场需求的扩张、产业规模的升级、技术水准的提高,该看到中国集成电路产业发展的希望。作为全球第三大集成电路市场中国占了20%的份额,而且产业发展速度和市场潜力在全球首屈一指。如今,由于我国集成电路产业还处于发展初期,富有经验的中高层工程,技术人才、设计人才及企业管理运营人才缺口很大。我国集成电路产业对专业设计、制造、营销、管理人才的需求量是25万一30万人,但目前国内这方面的人才数量远远不够。人才短缺,将成为制约我国集成电路产业快速发展的另一个瓶颈。然而,这也是作为一位学生,也是我们的机会,是我们为国家的集成电路信息安全做贡献的机会。让我们国家的集成电路不受外国掣肘。 1.1 课题目的与意义 本课程设计是《集成电路分析与设计基础》的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运用已掌握的知识,利用集成电路设计软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。掌握微电子技术人员所需要的基本理论和技能,日后从事集成电路设计工作打下基础。 通过此课程设计使学生对集成电路设计有了初步的认识认识并熟练使用集成电路相关软件,熟练集成电路设计的技能及规则等方面有重要意义。 1.2 设计题目与要求 1设计时使用的工艺及设计规则:MOSIS:mhp-s5; 2根据所用的工艺,选取合理的模型库; 3选用以lambda(λ)为单位的设计规则; 4全手工、层次化设计版图; 5达到指导书提出的设计指标要求。

《集成电路应用》课程实验实验二锁相环综合实验 学院:物理与信息工程学院 专业: 电子信息工程 年级: 2015级 姓名:张桢 学号: 指导老师:许志猛

实验二锁相环综合实验 一、实验目的: 1.掌握锁相环的基本原理。 2.掌握锁相环外部元件的选择方法。 3.应用CD4046锁相环进行基本应用设计。 二、元件和仪器: 1.CD4046 2.函数信号发生器 3.示波器 4.电阻、电容若干 5.面包板 三、实验原理: 1.锁相环的基本原理。 锁相环最基本的结构如图所示。它由三个基本的部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。 锁相环工作原理图 鉴相器是个相位比较装置。它把输入信号Si(t)和压控振荡器的输出信号So(t)的相位进行比较,产生对应于两个信号相位差的误差电压Se(t)。 环路滤波器的作用是滤除误差电压Se(t)中的高频成分和噪声,以保证环路所要求的性能,增加系统的稳定性。

压控振荡器受控制电压Sd(t)的控制,使压控振荡器的频率向输入信号的频率靠拢,直至消除频差而锁定。 锁相环是个相位误差控制系统。它比较输入信号和压控振荡器输出信号之间的相位差,从而产生误差控制电压来调整压控振荡器的频率,以达到与输入信号同频。在环路开始工作时,如果输入信号频率与压控振荡器频率不同,则由于两信号之间存在固有的频率差,它们之间的相位差势必一直在变化,结果鉴相器输出的误差电压就在一定范围内变化。在这种误差电压的控制下,压控振荡器的频率也在变化。若压控振荡器的频率能够变化到与输入信号频率相等,在满足稳定性条件下就在这个频率上稳定下来。达到稳定后,输入信号和压控振荡器输出信号之间的频差为零,相差不再随时间变化,误差电压为一固定值,这时环路就进入“锁定”状态。这就是锁相环工作的大致过程。 2.CD4046芯片的工作原理。 CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V -18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。 CD4046锁相的意义是相位同步的自动控制,功能是完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成,如下所示。 4046组成框图

福州大学集成电路应用实验一

————————————————————————————————作者:————————————————————————————————日期:

《集成电路应用》课程实验实验一 4053门电路综合实验 学院:物理与信息工程学院 专业: 电子信息工程 年级: 2015级 姓名:张桢 学号: 指导老师:许志猛

实验一 4053门电路综合实验 一、实验目的: 1.掌握当前广泛使用的74/HC/HCT系列CMOS集成电路、包括门电路、反相 器、施密特触发器与非门等电路在振荡、整形、逻辑等方向的应用。 2.掌握4053的逻辑功能,并学会如何用4053设计门电路。 3.掌握多谐振荡器的设计原理,设计和实现一个多谐振荡器,学会选取和 计算元件参数。 二、元件和仪器: 1.CD4053三2通道数字控制模拟开关 2.万用表 3.示波器 4.电阻、电容 三、实验原理: 1.CD4053三2通道数字控制模拟开关 CD4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。CD4053的管脚图和功能表如下所示 4053引脚

4053的8种逻辑功能 CD4053真值表 根据CD4053的逻辑功能,可以由CD4053由4053电路构成如下图所示8种逻辑门(反相器与非门或非门、反相器、三态门、RS 触发器、——RS 触发器、异或门等)。 输入状态 接通通道

]) 2)(()(ln[ T DD T DD T DD T V V V V V V V RC T -+--=2.多谐振荡器的设计 非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。电路的基本工作原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT 时,门的输出状态即发生变化。因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。 可以利用反相器设计出如下图所示的多谐振荡器 这样的多谐振荡器输出的信号周期计算公式为: 当R S ≈2R 时,若:VT=0.5VDD ,对于HC 和HCU 型器件,有 T ≈2.2RC 对于HCT 型器件,有 T ≈2.4RC 四、实验内容: 1. 验证CD4053的逻辑功能,用4053设计门电路,并验证其逻辑功能: (1)根据实验原理设计如下的反相器电路图: CD4053构成反相器电路

电子科技大学 实验报告 二、实验项目名称:CMOS模拟集成电路设计与仿真 三、实验地点:211大楼606房间 四、实验学时:4 五、实验目的: (1)综合运用课程所学知识自主完成相应的模拟集成电路版图设计,掌握基本的IC版图布局布线技巧。 (2)学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计与验证 六、实验原理: IC设计一般规则: ①根据用途要求,确定系统总体方案 ②根据电路的指标和工作条件,确定电路结构与类型,然后通过模拟计算, 决定电路中各器件的参数(包括电参数、几何参数等),EDA软件进行模拟仿真。 ③根据电路特点选择适当的工艺,再按电路中各器件的参数要求,确定满足 这些参数的工艺参数、工艺流程和工艺条件。 ④按电路设计和确定的工艺流程,把电路中有源器件、阻容元件及互连以一 定的规则布置在硅片上,绘制出相互套合的版图,以供制作各次光刻掩模版用。 ⑤生成PG带制作掩模版 ⑥工艺流片 ⑦测试,划片封装

实验模拟基于Cadence 平台的电路设计与仿真 七、实验内容: 1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。 2、设计一个运算放大器电路,要求其增益大于60dB, 相位裕度大于45o, 功耗小于10mW。 3、根据设计指标要求,选取、确定适合的电路结构,并进行计算分析。 4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans 分析、建立时间小信号特性和压摆率大信号分析,能熟练掌握各种分析的参数设置方法。 5、电路性能的优化与器件参数调试,要求达到预定的技术指标。 6、整理仿真数据与曲线图表,撰写并提交实验报告。 八、实验仪器与器材 (1)工作站或微机终端一台 (2)EDA仿真软件 1套 九、实验结果: 1、根据实验指导书熟悉UNIX操作系统常用命令的使用,掌握Cadence EDA仿真环境的调用。 2、根据设计指标要求,设计出如下图所示的电路结构。并进行计算分析,确定其中各器件的参数。 4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析,能熟练掌握各种分 ①增益与频率之间的关系、相位裕度与频率之间关系图如下所示: ②输入、输出关系曲线 十、实验结果计算与分析: 从幅频特性曲线图像中可以读出,电路的增益A V=59dB略小于设计所要求的60dB;找出增益接近于0时候的截止频率为102.4MHz,对应到下方相频特性曲线图像中为-130o,则相位裕度为180o-130o=50o,

实验一集成电路系统EDA软件使用简介 (基础性实验) 一实验目的 1、了解利用Quartus II 8.0 软件开发数字电路的基本流程以及掌握Quartus II软件 的详细操作。 2、了解使用VHDL原理图设计进行集成电路系统设计的实现方法。 3、掌握Quartus II 8.0 软件开发数字电路的基本设计思路,软件环境参数配置,时 序仿真,管脚分配,并且利用JTAG接口进行下载的常规设计流程。 二实验前的准备 1、将红色的MODUL_SEL拨码开关组合的1、 2、8拨上, 3、 4、 5、 6、7拨下,使数码 管显示当前模式为:C1. 2、检查JTAG TO USB转换接口和USB连接线的连接,并且将JTAG线连接到核心板上的 JTAG接口(核心板的第二个十针的插口)处。 三实验要求 学习使用Quartus II 8.0软件,掌握VHDL文本描述和原理图描述的RTL级描述方法。 四实验内容 (一)了解门电路元件库 1、新建原理图设计文件,并在原理图设计文件的基础上插入各种基本门电路元件,包 括与门、或门、非门、异或门等。 2、利用原理图图形编辑窗,将基本门电路元件进行连接,形成布线。 3、为连接好的门电路组合电路添加输入和输出端口。 (二)了解逻辑电路的仿真 1、保存原理图设计文件,新建时序仿真文件。 2、将各端口的信号标出,并对其实施功能仿真或时序仿真。并将仿真波形写入实验报 告。 (三)了解原理图文件的综合和下载 1、对原理图文件进行综合和引脚连结。 2、将对应FPGA端口连接至原理图电路端口中,并将原理图文件综合后的网表文件下载 到FPGA中,进行功能验证。 3、将硬件功能情况描述记录于实验报告中。

实验报告 课程名称:集成电路原理 实验名称: CMOS模拟集成电路设计与仿真 小组成员: 实验地点:科技实验大楼606 实验时间: 2017年6月12日 2017年6月12日 微电子与固体电子学院

一、实验名称:CMOS模拟集成电路设计与仿真 二、实验学时:4 三、实验原理 1、转换速率(SR):也称压摆率,单位是V/μs。运放接成闭环条件下,将一个阶跃信号输入到运放的输入端,从运放的输出端测得运放的输出上升速率。 2、开环增益:当放大器中没有加入负反馈电路时的放大增益称为开环增益。 3、增益带宽积:放大器带宽和带宽增益的乘积,即运放增益下降为1时所对应的频率。 4、相位裕度:使得增益降为1时对应的频率点的相位与-180相位的差值。 5、输入共模范围:在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。 6、输出电压摆幅:一般指输出电压最大值和最小值的差。 图 1两级共源CMOS运放电路图 实验所用原理图如图1所示。图中有多个电流镜结构,M1、M2构成源耦合对,做差分输入;M3、M4构成电流镜做M1、M2的有源负载;M5、M8构成电流镜提供恒流源;M8、M9为偏置电路提供偏置。M6、M7为二级放大电路,Cc为引入的米勒补偿电容。 其中主要技术指标与电路的电气参数及几何尺寸的关系:

转换速率:SR=I5 I I 第一级增益:I I1=?I I2 I II2+I II4=?2I I1 I5(I2+I3) 第二级增益:I I2=?I I6 I II6+I II7=?2I I6 I6(I6+I7) 单位增益带宽:GB=I I2 I I 输出级极点:I2=?I I6 I I 零点:I1=I I6 I I 正CMR:I II,III=I II?√5 I3 ?|I II3|(III)+I II1,III 负CMR:I II,III=√I5 I1+I II5,饱和 +I II1,III+I II 饱和电压:I II,饱和=√2I II I 功耗:I IIII=(I8+I5+I7)(I II+I II) 四、实验目的 本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。其目的在于: 根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。 学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。 五、实验内容 1、根据设计指标要求,针对CMOS两级共源运放结构,分析计算各器件尺寸。 2、电路的仿真与分析,重点进行直流工作点、交流AC和瞬态Trans分析,能熟练掌握各种分析的参数设置方法与仿真结果的查看方法。 3、电路性能的优化与器件参数调试,要求达到预定的技术指标。

《集成电路测试》实验指导书 南通大学集成电路重点实验室 2009年6月

实验一 测试图形生成及验证 一、实验目的 熟悉对被测电路给定故障生成测试图形的过程,掌握异或法和D 算法的具体运用。 二、实验原理 参考教材P74 4.2.1 异或法, P82 4.4 D 算法 三、实验内容 a b c d (1) 用异或法对5/0故障生成测试图形; (2) 用D 算法对6/0故障生成测试图形; (3) 对以上所产生的测试图形进行验证;(在Quartus II 中进行验证) 四、实验报告 写出测试图形生成的具体过程,给出整个实验的原理图和运行结果,分析实验结果的正确性。 f

实验二伪随机序列生成 一、实验目的 了解随机测试和伪随机测试的基本概念;掌握LFSR的基本结构和M序列的基本特性。 二、实验原理 基于故障的确定性测试方法是指用专门的算法对给定的故障生成测试图形,优点是生成的测试图形长度短,但生成过程比较复杂,测试施加比较困难。由微处理器的测试软件算法或者专用的测试电路可容易生成随机的或伪随机的测试图形,并具有较高的故障覆盖率,因此在集成电路测试中得以广泛应用。 如果一个序列,一方面它是可以预先确定的,并且是可以重复地生产和复制的;一方面它又具有某种随机序列的随机特性(即统计特性),我们便称这种序列为伪随机序列。因此可以说,伪随机序列是具有某种随机特性的确定的序列。它们是由移位寄存器产生确定序列,然而他们却具有某种随机序列的随机特性。因为同样具有随机特性,无法从一个已经产生的序列的特性中判断是真随机序列还是伪随机序列,只能根据序列的产生办法来判断。伪随机序列系列具有良好的随机性和接近于白噪声的相关函数,并且有预先的可确定性和可重复性。 伪随机序列的电路为一个反馈移位寄存器,它可分为线性反馈移位寄存器(简称LFSR 计数器)和非线性反馈移位寄存器,由线性反馈移位寄存器(LFSR)产生的周期最长的二进制数字序列称为最大长度线性反馈移位寄存器序列,通常简称为M序列。 关于LFSR构造及M序列的相关特性,请参阅教材p205-212的相关内容。 三、实验内容 下图为4位完全LFSR结构图,试分析其自动生成的序列。(在Quartus II中运行、分析) 四、实验报告 对伪随机序列,LFSR,M序列等相关概念进行综述。对上图进行分析。

实验一 实验箱及小规模集成电路的使用 一 实验目的 1 掌握实验箱的功能及使用方法 2 学会测试芯片的逻辑功能 二 实验仪器及芯片 1 实验箱 2 芯片:74LS00 二输入端四与非门 1片 74LS86 二输入端四异或门 1片 74LS04 六非门 1片 三 实验内容 1 测试芯片74LS00和74LS86的逻辑功能并完成下列表格。 (1) 74LS00的14脚接+5V 电源,7脚接地;1、2、4、5、9、10、12、13脚接逻辑开关,3、6、8、11接发光二极管。(可以将1、4、9、12接到一个逻辑开关上,2、5、10、13接到一个逻辑开关上。)改变输入的状态,观察发光二极管。74LS86的接法74LS00基本一样。 表 74LS00的功能测试 表 74LS86的功能测试 (2)分析74LS00和74LS86的四个门是否都是完好的。 2 用74LS00和74LS04组成异或门,要求画出逻辑图,列出异或关系的真值表。 (3)利用74LS00和74LS04设计一个异或门。画出设计电路图。

实验二译码器和数据选择器 一实验目的 1继续熟悉实验箱的功能及使用方法 2掌握译码器和数据选择器的逻辑功能 二实验仪器及芯片 1 实验箱 2 芯片:74LS138 3线-8线译码器 1片 74LS151 八选一数据选择器 1片 74LS20 四输入与非门 1片 三实验内容 1 译码器功能测试(74LS138) 芯片管脚图如图所示,按照表连接电路,并完成表格。其中16脚接+5V,8脚接地,1~6脚都接逻辑开关,7、9、10、11、12、13、14、15接发光二极管。 表 2 数据选择器的测试(74LS151) 按照表连接电路,并完成表格。其中16脚接+5V,8脚接地;9、10、11,为地址输入端,接逻辑开关;4、3、2、1、12、13、14、15为8个数据输入端,接逻辑开关;G为选通输入端,Y为输出端,接发光二极管。

实验2 导线特性 1 实验目的 了解导线的RC特性和建模方法。 2 实验内容 设某层金属阻值为0.086欧姆/方。金属层导线长度为1300um,宽度为0.13um;其集总电容为0.1pf。设信号源为1.2V,内阻1K欧姆。利用Elmore延时公式计算、并使用下列模型仿真此导线的延时(50%至50%)以及上升和下降时间(10%至90%)。 (1)一个电阻、一个电容的集总模型; (2) 3型RC模型; (3)T3型RC模型。 下面是当时编写的,自己都记不清了,问号是保存为记事本txt有问题。 (a) INVa .options list node post .model m1 pmos level=2 .model m2 nmos level=2 m1 out in vdd vdd?m1 L=0.250u?W=1.125u m2 out in 0? 0? m1 L=0.250u?W=0.375u cl out 0 1pf vdd vdd 0 dc 2.5 vin in 0 dc 2.5 .op .dc vin 0 2.5 0.5 .print dc v(in) v(out) .probe dc v(in) v(out) .END (b) INVb .options list node post

.model m1 pmos level=2 .model m2 nmos level=2 m1 out in vdd vdd?m1 L=0.250u?W=2.750u m2 out in 0? 0? m1 L=0.250u?W=0.375u cl out 0 1pf vdd vdd 0 dc 2.5 vin in 0 dc 2.5 .op .dc vin 0 2.5 0.5 .print dc v(in) v(out) .probe dc v(in) v(out) .END (c) INVc .options list node post .model m1 pmos level=2 .model m2 nmos level=2 m1 out in vdd vdd?m1 L=0.250u?W=1.125u m2 out in 0? 0? m1 L=0.250u?W=0.375u cl out 0 1pf vdd vdd 0 dc 2.5 vin in 0 dc vd .data vd_table 1 1.5 2.5 .enddata .op .tran 100p 100n .print tran v(in) v(out) .probe tran v(in) v(out) .END (d) INVc .options list node post .model m1 pmos level=2 .model m2 nmos level=2 m1 out in vdd vdd?m1 L=0.250u?W=0.750u m2 out in 0? 0? m1 L=0.250u?W=0.375u cl out 0 1pf vdd vdd 0 dc 2.5 vin in 0 dc 2.5

组合逻辑电路的设计 一、实验目的 1.掌握组合逻辑电路设计的一般概念和方法。 2.掌握集成组合逻辑电路的使用和设计方法。 3.学习EDA软件Quartus II的基本使用方法。 二、实验预习 阅读《电工电子实验教程》第6.3节中组合逻辑电路的内容。 打印实验指导书,预习实验的内容。 查阅相关芯片的数据手册,了解芯片的逻辑功能、引脚排列及外形结构,完成实验电路设计,画出原理电路,标明芯片型号和引脚。自拟实验步骤和数据表格。 三、实验设备与仪器 数字电路实验箱。 四、实验原理 使用中规模的集成电路设计组合逻辑电路的一般方法为: 第一步:从题目中完成逻辑抽象。把实际问题转换为可行的逻辑设计要求。 第二步:根据逻辑设计的要求建立输入、输出变量,并列出真值表。 第三步:用逻辑代数或卡诺图化简法求出简化的逻辑表达式。并按实际选用逻辑门的类型修改逻辑表达式。不一定要最简形式,应以所要使用的中规模集成芯片的逻辑功能为依据,把要产生的逻辑函数变换为与器件的逻辑函数式类似的形式。对于变换后的逻辑函数式与所选器件的逻辑函数式差别非常大的应考虑更换元器件类型。 第四步:根据简化后的逻辑表达式,画出逻辑图,用标准器件构成逻辑电路。 第五步:用实验来验证设计的正确性。 设计组合逻辑电路的一般步骤如图1所示。 图1 组合逻辑电路设计流程图

五、实验内容 题目A:4人表决电路 设计一个4人表决电路,多数通过(即当四个输入端中有三个或四个为“1”时,输出端才能为“1”),用发光二极管显示表决结果,通过点亮,否决不亮。(要求选用与非门电路实现,74LS10和/或74LS20) 题目B:大月指示器电路 设计一个大月(该月份天数为31)指示器,四个二进制输入变量表示月份,发光二极管表示输出,若该月份月份为大月,则发光二极管亮,其它情况发光二极管不亮(注意任意项的处理,要求使用74LS00和74LS151)。 六、实验要求 从实验内容所列的题目中选择一个题目进行设计,使用中规模集成电路芯片完成设计,具体方案不限。要求确保电路可以完成题目功能,并使用尽可能少的器件。 列出真值表,写出逻辑表达式并根据设计要求进行化简(化简形式根据采用的器件逻辑功能自行决定),全部用门电路实现。 在数字实验系统中完成实际操作,利用实验箱上已连接好的开关电路获得所需的逻辑电平输入,LED指示灯电路完成结果显示。 自行设计测试表格,完成实际电路的测试。 实验室可提供的芯片有:74LS00、74LS10、74LS20、74LS151。 七、实验报告(本部分请附加空白页手写完成) 在实验报告中写出完整的设计思路和设计过程,越详细报告分数起评点越高,内容应包括建立逻辑变量、列真值表、逻辑化简、逻辑表达式变换、电路图设计等。 用要求的器件设计出电路,画出电路图。 列出元器件清单。 写出实验结果及分析。 写出实验体会总结。 有能力的同学可画出仿真电路图和仿真结果。

集成电路设计综合实验 题目:集成电路设计综合实验 班级:微电子学1201 姓名: 学号:

集成电路设计综合实验报告 一、实验目的 1、培养从版图提取电路的能力 2、学习版图设计的方法和技巧 3、复习和巩固基本的数字单元电路设计 4、学习并掌握集成电路设计流程 二、实验内容 1. 反向提取给定电路模块(如下图1所示),要求画出电路原理图,分析出其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。 图1 1.1 查阅相关资料,反向提取给定电路模块,并且将其整理、合理布局。 1.2 建立自己的library和Schematic View(电路图如下图2所示)。 图2 1.3 进行仿真验证,并分析其所完成的逻辑功能(仿真波形如下图3所示)。

图3 由仿真波形分析其功能为D锁存器。 锁存器:对脉冲电平敏感,在时钟脉冲的电平作用下改变状态。锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出才会随着数据输入发生变化。简单地说,它有两个输入,分别是一个有效信号EN,一个输入数据信号DATA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程。 只有在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号。其中使能端A 加入CP信号,C为数据信号。输出控制信号为0时,锁存器的数据通过三态门进行输出。所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。锁存,就是把信号暂存以维持某种电平状态。 1.4 生成Symbol测试电路如下(图4所示) 图4

第一章 集成电路的测试 1.集成电路测试的定义 集成电路测试是对集成电路或模块进行检测,通过测量对于集成电路的输出回应和预期输出比较,以确定或评估集成电路元器件功能和性能的过程,是验证设计、监控生产、保证质量、分析失效以及指导应用的重要手段。 .2.集成电路测试的基本原理 输入Y 被测电路DUT(Device Under Test)可作为一个已知功能的实体,测试依据原始输入x 和网络功能集F(x),确定原始输出回应y,并分析y是否表达了电路网络的实际输出。因此,测试的基本任务是生成测试输入,而测试系统的基本任务则是将测试输人应用于被测器件,并分析其输出的正确性。测试过程中,测试系统首先生成输入定时波形信号施加到被测器件的原始输入管脚,第二步是从被测器件的原始输出管脚采样输出回应,最后经过分析处理得到测试结果。 3.集成电路故障与测试 集成电路的不正常状态有缺陷(defect)、故障(fault)和失效(failure)等。由于设计考虑不周全或制造过程中的一些物理、化学因素,使集成电路不符合技术条件而不能正常工作,称为集成电路存在缺陷。集成电路的缺陷导致它的功能发生变化,称为故障。故障可能使集成电路失效,也可能不失效,集成电路丧失了实施其特定规范要求的功能,称为集成电路失效。故障和缺陷等效,但两者有一定区别,缺陷会引发故障,故障是表象,相对稳定,并且易于测试;缺陷相对隐蔽和微观,缺陷的查找与定位较难。 4.集成电路测试的过程 1.测试设备 测试仪:通常被叫做自动测试设备,是用来向被测试器件施加输入,并观察输出。测试是要考虑DUT的技术指标和规范,包括:器件最高时钟频率、定时精度要求、输入\输出引脚的数目等。要考虑的因素:费用、可靠性、服务能力、软件编程难易程度等。 1.测试界面 测试界面主要根据DUT的封装形式、最高时钟频率、ATE的资源配置和界面板卡形等合理地选择测试插座和设计制作测试负载板。

集成电路设计 实验报告 时间:2011年12月

实验一原理图设计 一、实验目的 1.学会使用Unix操作系统 2.学会使用CADENCE的SCHEMA TIC COMPOSOR软件 二:实验内容 使用schematic软件,设计出D触发器,设置好参数。 二、实验步骤 1、在桌面上点击Xstart图标 2、在User name:一栏中填入用户名,在Host:中填入IP地址,在Password:一栏中填入 用户密码,在protocol:中选择telnet类型 3、点击菜单上的Run!,即可进入该用户unix界面 4、系统中用户名为“test9”,密码为test123456 5、在命令行中(提示符后,如:test22>)键入以下命令 icfb&↙(回车键),其中& 表示后台工作,调出Cadence软件。 出现的主窗口所示: 6、建立库(library):窗口分Library和Technology File两部分。Library部分有Name和Directory 两项,分别输入要建立的Library的名称和路径。如果只建立进行SPICE模拟的线路图,Technology部分选择Don’t need a techfile选项。如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的techfile)或Attach to an existing techfile(使用原有的techfile)。 7、建立单元文件(cell):在Library Name中选择存放新文件的库,在Cell Name中输 入名称,然后在Tool选项中选择Composer-Schematic工具(进行SPICE模拟),在View Name中就会自动填上相应的View Name—schematic。当然在Tool工具中还有很多别的

《集成电路设计技术》 实验指导书 编写人:方 元 电子电气工程系 2012年2月

前言 Verilog HDL就是在用途最广泛的C语言的基础上发展起来的一种硬件描述语言,它是由GDA(Gateway Design Automation)公司的PhilMoorby在1983年末首创的,最初只设计了一个仿真与验证工具,之后又陆续开发了相关的故障模拟与时序分析工具。1985年Moorby推出它的第三个商用仿真器Verilog-XL,获得了巨大的成功,从而使得Verilog HDL迅速得到推广应用。1989年CADENCE公司收购了GDA公司,使得Verilog HDL成为了该公司的独家专利。1990年CADENCE公司公开发表了Verilog HDL,并成立LVI组织以促进Verilog HDL 成为IEEE标准,即IEEE Standard 1364-1995。 本实验是在学生拥有集成电路设计概念以及数字电路理论学习的基础上,通过ModelSim EDA仿真工具,编写Verilog HDL语言。这有助于学生们对于课堂上所学习的Verilog HDL语言有一个深入的了解,并最终使得学生们能够学会该语言的基本语法,能够编写一些简单的模块。若今后从事集成电路设计工作,能够通过本次实验初窥门径,为今后的工作打下基础。 通过实验能够掌握Verilog HDL语言的基本语法,基本模块,为以后更加深入的学习数字集成电路设计打下基础。同时,让学生们使用最简单的HDL逻辑仿真工具ModelSim,对EDA工具的使用有一个基本概念,这样在学习其他EDA 工具时就不会那么生疏。 本实验通过4次实验,让同学们掌握Verilog模块化设计的理念,学会使用ModelSim软件,学会通过波形图查看电路的时序与逻辑是否正确。

CMOS放大器设计实验报告 一、实验目的 1.培养学生分析、解决问题的综合能力; 2.熟悉计算机进行集成电路辅助设计的流程; 3.学会适应cadence设计工具; 4.掌握模拟电路仿真方法 6.掌握电子电路、电子芯片底层版图设计原则和方法; 7.掌握使用计算机对电路、电子器件进行参数提取及功能模拟的过程; 8.熟悉设计验证流程和方法。 二、实验原理 单级差分放大器结构如下图所示: 在电路结构中,M2和M3组成了NMOS差分输入对,差分输入与

单端输入相比可以有效抑制共模信号干扰;M0和M1电流镜为有源负载,可将差分输入转化为单端输出;M5管提供恒定的偏置电流。三、实验要求 设计电路使得其达到以下指标: 1.供电电压: 2.输入信号:正弦差分信号 3.共模电压范围为 4.差分模值范围 5.输出信号:正弦信号 6.摆率大于 7.带宽大于 8.幅值增益: 9.相位裕度: 10.功耗: 11.工作温度: 四、差分放大器分析

1、直流分析 为了使电路正常工作,电路中的MOS管都应处于饱和状态。 1.1 M2管的饱和条件: 1.2 M4管的饱和条件: 2.小信号分析 小信号模型如下:

由图可得: 2.1 增益分析 其中 2.2 频率响应分析由小信号模型易知: 其中 3.电路参数计算3.1确定电流 根据摆率指标:

根据功耗指标易知: 根据带宽指标: 综上,取: 3.2宽长比的确定 M4与M5:电流源提供的电流为,参数设为,根据电流镜原理,可以算出 M2与M3: 带入数据可得 取值为20,则取 M0与M1:这两个PMOS管对交流性能影响不大,只要使其下方的

集成电路设计实验报告 院别:电信学院专业:电子科学与技术 班级:电子姓名:学号:组序: 实验(二)题目名称:CMOS反相器的版图设计(PMOS、NMOS) 成绩:教师签名:批改时间: 一、实验目的: 在集成电路设计当中,集成电路设计软件的介入大大的缩短了开发周期,减小了设计风险,使得我们在设计的时候可以发现并改正电路设计上的绝大多数bug。所以说学习设计软件已经成为集成电路设计工程师的必修课。而Ledit软件以其良好的人机操作界面,以及强大的设计规则检查能力而在集成电路的设计当中充当了很重要的角色。在此次试验当中我们需要独立完成CMOS反相器的版图设计,规则检查,以及排除错误工作。从而达到比较熟练的掌握Ledit 的基本功能已经操作方法。 二、实验要求: 如将设计好的电路制成实际使用的集成块,就必须利用版图工具将设计的电路采用标准工艺文件转换成可以制造的版图。然后再将版图提交给集成电路制造厂家(foundry),完成最后的集成块制造,所以画版图的本质就是画电路原理图。 在画版图时,首先要明白工艺文件的含义,每一种工艺文件代表一条工艺线所采用的光刻尺寸,以及前后各个工序等等;其次要懂得所使用的工具步骤及各个菜单及菜单栏的内容,以便熟练使用该软件;最后对所画版图进行验证,确保不发生错误。 此外,还必须了解所使用的版图设计法则,对于不同的工艺尺寸其法则有所不同,这就要求设计者在应用该软件时,必须熟悉相应的设计法则,为完成正确的版图做准备。该实验原理是画常见的CMOS反相器,画版图时要求熟悉CMOS反相器的工艺过程及设计法则。

三、实验方法: 首先在实验一的基础上进一步熟悉L-EDIT版图设计软件的工具及工艺库,比较熟练地掌握该软件画版图的方法。以CMOS反相器为例,在前面画的PMOS、NMOS 的基础上,通过调用将他们组合到一起,再完成整个CMOS反相器的设计,设计完成后运用该软件的设计规则对所画的版图进行DRC验证,并修改不正确的部分,直至设计无错误。 四、实验内容: 1.运行L-Edit程序时,L-Edit会自动将工作文件命名为Layout1.tdb并显示在窗口的标题栏上。 2.另存为新文件:选择执行File/Save As子命令,将自己的工程文件保存在C:\DocumentsandSettings\Administrator\桌面\实验相关\Tanner\Ledit90\Samples\SPR\exam ple1中,在“文件名”文本框中输入新文件名称:NOMS。保存到example目录的原因是防止后面做剖视图的时候没法进行。 3.替换设置信息:选择执行File/Replace Setup子命令打开对话框,单击“From File”栏填充框的右侧的Browser按钮,选择C:\Documents and Settings\Administrator\桌面\实验相关\Tanner\Ledit90\Samples\SPR\example1\lights.tdb文件,如图所示,单击OK就将lights.tdb文件中的格点、图层、以及设计规则等设定应用在当前工程中。 4.画出PMOS:按照实验一的步骤,设计PMOS的版图。并进行相应的规则检查,直到没有错误。画好后如图所示:

《数字集成电路》实验指导书 何爱香 信息与电子工程学院 2013年1月

目录 实验1译码器 (3) 实验2组合逻辑电路..................................................................6实验3半加器...........................................................................8实验4全加器...........................................................................9实验5三进制计数器 (11) 实验6 555多谐振荡器 (13) 实验7电压比较器 (15) 实验8Pspice最坏情况分析 (16)

实验1 译码器 一、 实验目的 1. 理解译码器逻辑功能。 2. 掌握译码器电路设计方法。 二、 实验内容 译码器74155的芯片如下图所示, 逻辑函数式:B A Y += 三、 实验步骤 (1) 在pspice 中,启动Place/Part 命令,出现下图所示的选择框,输入 74155,点击OK 。 (2)控制端1C 设置为高电平,使能端G 1设置为低电平。 在pspice 中,高低电平要用专门的符号来设置,启动Place/Ground 命令,出现下图所示的选择框,在SOURE 库中取“$D_HI ”符号,即为接入高电平,取“$D_LO ”符号,接到电路的输入端,即为接入低电平。 (2) 设置输入信号AB 启动Place/Part 命令,出现下图所示的选择框,输入DigClock 。通过设置时钟信号源参数调整方波的周期可占空比。设置输入信号A 的ONTIME 和OFFTIME 为。设置输入信号B 的ONTIME 和OFFTIME 为1ms 时钟信号源有5个周期参数要设置:

哈尔滨理工大学数字集成电路设计实验报告 学院:应用科学学院 专业班级:电科12 - 1班 学号:32 姓名:周龙 指导教师:刘倩 2015年5月20日

实验一、反相器版图设计 1.实验目的 1)、熟悉mos晶体管版图结构及绘制步骤; 2)、熟悉反相器版图结构及版图仿真; 2. 实验内容 1)绘制PMOS布局图; 2)绘制NMOS布局图; 3)绘制反相器布局图并仿真; 3. 实验步骤 1、绘制PMOS布局图: (1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层; (4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层; (7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察; 2、绘制NMOS布局图: (1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览; 3、绘制反相器布局图: (1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice 模拟; 4. 实验结果 nmos版图