Using ATACS for Verification of Hazard-Freedom of Phased Logic Wrappers

Michael Boyer

Advisor: Cherrice Traver

Union College

Summer 2004

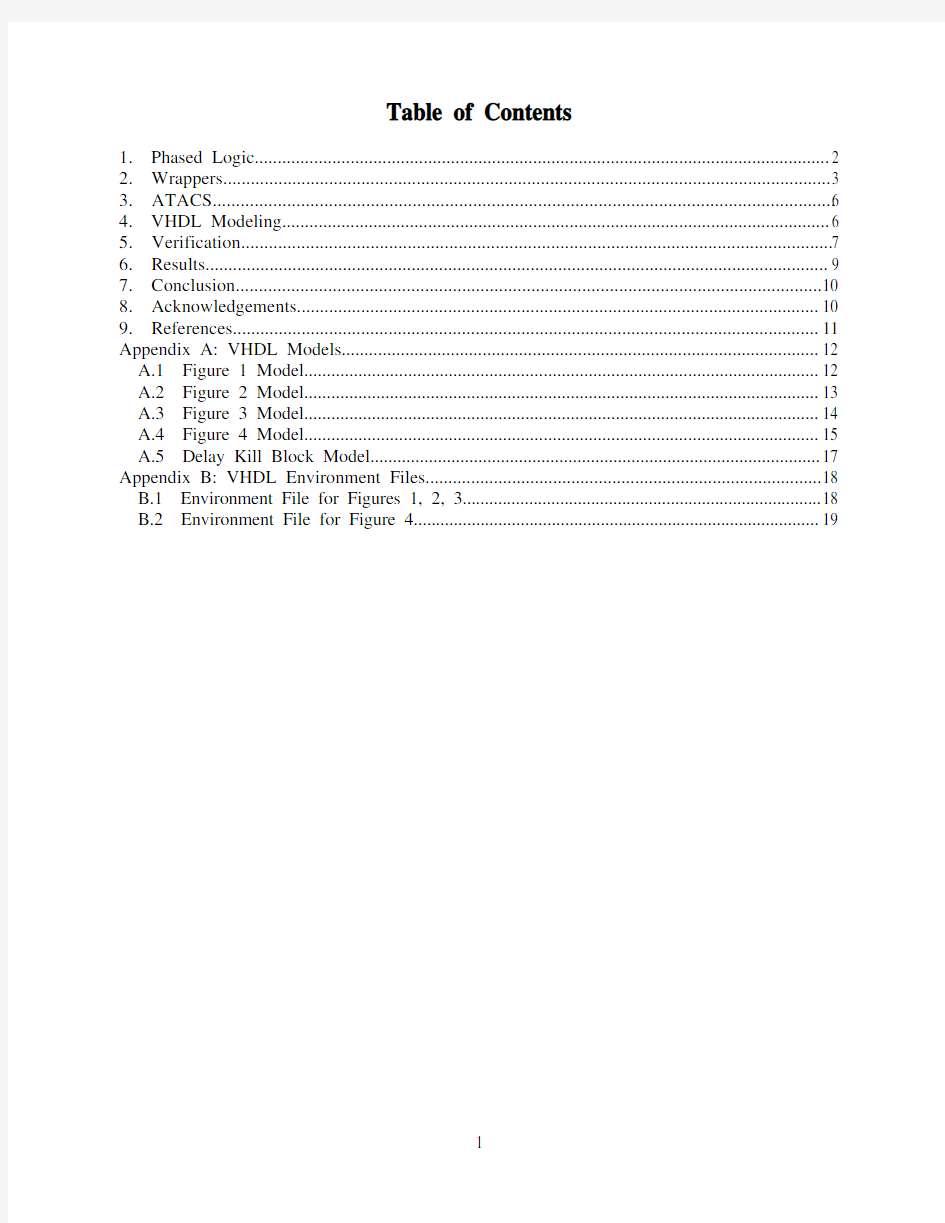

Table of Contents

1. Phased Logic (2)

2. Wrappers (3)

3. ATACS (6)

4. VHDL Modeling (6)

5. Verification (7)

6. Results (9)

7. Conclusion (10)

8. Acknowledgements (10)

9. References (11)

Appendix A: VHDL Models (12)

A.1 Figure 1 Model (12)

A.2 Figure 2 Model (13)

A.3 Figure 3 Model (14)

A.4 Figure 4 Model (15)

A.5 Delay Kill Block Model (17)

Appendix B: VHDL Environment Files (18)

B.1 Environment File for Figures 1, 2, 3 (18)

B.2 Environment File for Figure 4 (19)

1. Phased Logic

Phased Logic (PL) is an asynchronous methodology introduced in [1] that supports the synchronous design paradigm by allowing automated translation from a clocked netlist implementation of a circuit to a self-timed netlist implementation. The fine-grained version of PL uses two wires for every signal; one for data and the other for timing/phase. Each PL signal and PL gate can have one of two phases, either even or odd, using a Level Encoded Dual Rail signaling scheme [2]. When the phase of all of a gate's input signals matches the gate's own internal phase, the gate updates its data output signal and then toggles its phase output signal, a process known as firing. Using the synthesis algorithm in [1] and the addition of feedback signals, we can assure that a synthesized circuit satisfies two important properties: liveness, meaning that there is no way for the flow of data to halt and the circuit to cease operation; and safety, meaning that there is no way for data to be lost between two gates by the sender of the data updating the signal before the receiver has processed it.

Early work with PL utilized a fine-grain mapping technique in which each individual gate in the clocked netlist was mapped directly to a PL gate. More recent work by Reese, Thornton, and Traver [3], however, has utilized a coarse-grain mapping technique in which entire logic blocks in the clocked netlist are enclosed by PL wrapper logic. Because the wrapper logic interfaces between the external PL circuit and the internal logic block, the logic block itself can be reused without modification. The course-grain Phased Logic is very similar to a two-phase micropipeline system [4], but with phase signals taking the place of request signals and feedback signals, where applicable, taking the place of acknowledge signals. There are two types of logic blocks in this methodology [5]: barrier blocks, which contain D-Flip-Flops as well as combinational logic; and through blocks, which contain only combinational logic. Each of these two types is implemented using a different PL wrapper. These PL wrappers are further modified if the block uses time borrowing or early evaluation. Each of the wrapper circuits is described in detail in [5].

Time borrowing is a speed-up technique that can be used when two or more through blocks are connected in series. Normally, a block with a large compute delay will need an equivalently large control delay, but time borrowing allows the control delay through the slow block to be spread to surrounding blocks with smaller compute delays. For example, consider a circuit with only two blocks, A and B, where the output from block A is the input to block B. Assume that block A has a compute delay of 15 ps, block B has a compute delay of 2 ps, and both blocks have a control delay of 5 ps. Without time borrowing, the control delay through block A will have to be increased by 10 ps, creating a total control delay of 20 ps but a total compute delay of only 17 ps. With time borrowing, the compute delay through block A will only be increased by 7 ps, yielding a total control delay of 17 ps and matching the total compute delay. Another speed-up technique, early evaluation, can be used in either barrier or through blocks. Early evaluation can only be used in blocks whose output in certain cases can be determined before all of its inputs have arrived. For example, a block implementing the carry-out from a three-input addition function can determine its output before the carry-in input arrives if its A and B inputs are either both zero or both one. Using early evaluation in a case like this potentially offers a significant speedup.

2. Wrappers

Figure 1 shows the wrapper for through blocks with time borrowing. Separate C-elements are used on the compute path and the control path to ensure that the control path is fast regardless of loading on the latch enable signal. The delay through the control path is important, especially in blocks whose compute delay is relatively small. The delay blocks on the feedback inputs to the lower C-element are necessary to ensure that the data output signal is updated before the phase output signal. The delay block driving the D5 signal in the bottom right corner of the figure is used to lengthen the pulse width of the latch enable signal.

Figure 1: Wrapper for Through Blocks with Time Borrowing

Figure 2 shows the wrapper for through blocks without time borrowing. It is similar to the previous wrapper, except the C-elements are replaced by faster pseudo C-elements (nC-elements), the XOR gates are removed, and there is no delay block to control the pulse width of the latch enable signal. The XOR gates are not needed in this wrapper because the negation of the phase_bar signal, which drives the select inputs to the nC-elements, causes the negation of the nC-element output signals.

Figure 3 shows the wrapper for barrier blocks without early evaluation. Like the previous wrapper, it does not use XOR gates and uses an nC-element instead of a slower full C-element. Unlike the previous wrapper, however, the data output storage is implemented with a DFF instead of a latch. Since this means that both output storage elements are edge-triggered, the two separate nC-elements in the previous wrapper are combined into one nC-element in this wrapper.

Figure 2: Wrapper for Through Blocks without Time Borrowing

Figure 3: Wrapper for Barrier Blocks without Early Evaluation

Figure 4 shows the wrapper for both barrier and through blocks that use early evaluation. The early evaluation wrapper is by far the most complicated wrapper because its behavior in each cycle depends on whether or not early evaluation is used in that cycle. The term “early fire” refers to the wrapper firing with early evaluation; “late fire” refers to the wrapper firing without early evaluation. The input signals are broken up into early inputs and late inputs, with the possibility that an early input is also a late input. The early evaluation (eeval) block below the compute block outputs a one in the cases where early evaluation can be used and outputs a zero otherwise, based on the values of the early inputs; this value is latched by the early evaluation latch (eelatch). When the eelatch output is low, both multiplexors select the Lphs signal from the late C-element and a late fire occurs. In this case, neither the clock nor the feedback output signals are updated until all of the inputs to arrive. When the eelatch output is high, the top multiplexor selects the Tphs signal from the trigger C-element, the bottom multiplexor selects the Lphs_nodly signal from the all-arrived C-element, and an early fire occurs. In this case, the clock signal will go high after the early phase and feedback signals have arrived; it does not need to wait for the late phase signals to arrive. The negation of the feedback output signal in this case, however, does need to wait for all of the input signals to arrive at the all-arrived C-element, but does not need to wait for any of the input signals to propagate through any delay blocks. As soon as feedback has been provided in an early fire, the new feedback signal arriving at the delay kill (dkill) blocks effectively kills the delay through those blocks.

Figure 4: Early Evaluation Wrapper for Barrier and Through Blocks

3. ATACS

Automatic Timed Asynchronous Circuit Synthesis (ATACS) is a tool developed by the Myers Research Group at the University of Utah for the synthesis and verification of timed asynchronous circuits. The use of timed asynchronous circuits allows us to take advantage of known (or assumed) timing information in order to optimize a circuit's performance, as discussed in [6]. ATACS supports a wide range of file types [7]: CSP, handshaking expansion (HSE), VHDL, signal transition graph (STG), burst-mode state machine, (UNC), timed event-rule structure files (ER), timed event/level structure (TEL), and reduced state graph (RSG). We chose to model our circuits exclusively in VHDL because it was the format most familiar to us and was supported by our editing and simulation software. The program supports six different timing methods that affect the verification process: untimed, geometric, POSETs, Bourne Again Geometric (BAG), Bourne Again POSETs (BAP), and BAP Time-Dependent Choice (BAPTDC). The main timing method that we were concerned with was POSETs, which represents timing information using zones and represents timing between events using a POSET matrix.

Although ATACS supports both the synthesis and verification of timed asynchronous circuits, our primary interest for this research was its verification capability. ATACS offers three different types of verification: conformance checking, property checking, and hazard checking. Conformance checking verifies that a specification in one file format and a circuit in another format properly conform to one another. Property checking verifies a Computation Tree Logic (CTL) statement about a circuit. Hazard checking, the type of verification that we used, verifies that there are no hazards present in a circuit. Hazards are defined in [6] as “conditions generated by the structure of the circuit or timing relationships between inputs and propagation delays that can cause incorrect behavior.” [6] describes the two types of hazards: acknowledgment hazards and monotonicity hazards. An acknowledgment hazard occurs when a signal “becomes excited to change to a new value, but its excitation changes value before it can be shown to have stabilized.” A monotonicity hazard occurs when “is supposed to remain stable but it becomes momentarily excited or it is supposed to make a transition which it makes non-monotonically.”

[6] also gives algorithms to check for both of these types of hazards; these processes are automated by ATACS, allowing us to check the hazard freedom of our circuits relatively quickly and easily.

4. VHDL Modeling

Although VHDL models of the PL wrappers already existed, they were unsuitable for use in ATACS. This forced us to write completely new models, making sure that they did not contain any code that was incompatible with ATACS. For example, our original model for the D-Flip-Flops used the Boolean expression clock’event to identify the rising edge of its clock input signal. However, this type of expression is not supported by ATACS. We were forced to come up with an alternative model for the DFF, and eventually decided on a master-slave flip-flop model. This model was chosen because it only relied on the value of the clock signal and not its transitions, and therefore did not require the use of an incompatible expression.

In order to implement the delay ranges required for our analysis, we used the delay function provided by the VHDL package nondeterminism, written by Chris Myers [8]. Given the lower and upper bounds of a time range, delay returns a randomly-chosen time within that range. This function was used to implement the delay ranges for all of the components in our circuits. For the purposes of our research, the delays through the compute blocks were much more significant than what the blocks did. However, we could not ignore their internal operation altogether; in order for them to be modeled properly, each compute block still needed to actually implement a function. For the three non-early evaluation wrappers, their compute blocks simply implemented a two-input AND function. The compute block in the early evaluation wrapper implemented the carry-out from a three-input addition function. Although technically early evaluation can be accomplished using a two-input AND function, with an early fire occurring when the early input is zero, that is not something that would ever be done in the real world.

Before the VHDL models of the wrappers could be verified by ATACS, we had to somehow specify their expected behavior. We accomplished this by modeling the environment for each of the wrappers in VHDL. The purpose of an environment is to assign values to the input signals and define the expected behavior of the output signals. The process of writing the environment files was simplified by using the VHDL handshake package written by Chris Myers [8]. The package features a number of useful functions: assign, which assigns values to signals in parallel after a delay chosen from a certain range; guard, which waits for a signal to attain a certain value; and guard_and, which waits for a set of signals to achieve certain values. The assign function was used to assign values to the input signals, while the guard and guard_and functions were used to specify the expected behavior of the output signals.

We had to make a number of assumptions about the environment in order to properly model them in VHDL. For all of the wrapper circuits, we assumed that the data, phase, and feedback inputs all arrived at the same time. This is a valid assumption because a phase signal cannot arrive before its associated data signal, and a data signal arriving before its associated phase signal cannot possibly introduce a hazard into the circuit. Also, in each of the four wrapper circuits neither the data nor the phase output signals can be updated until all of the feedback signals have arrived, so the circuit effectively waits for the feedback signals before it can proceed. Therefore, the timing of the arrival of the feedback signals has no effect on the hazards present in the circuits. We also assumed a rather large delay between the wrapper firing and receiving new inputs. This is an accurate assumption if the wrapper is connected to at least one other block, as it would be in any real-world application.

The VHDL models for the wrappers and the delay kill block are provided in Appendix A. The VHDL environment files are provided in Appendix B.

5. Verification

As an example of the hazard detection process using ATACS, consider the first wrapper described in this paper, the through block wrapper with time borrowing. Assume that the internal components have the arbitrary ranges of delays show in Figure 5. These ranges are also used in the VHDL model given in Appendix 1. While these specific delay values may or may not represent the delay values that we would find in the real world, the relative order of the values should be accurate. For example, the compute block and the delay blocks have the highest range of delays, while the simple XOR and NOT gates have the lowest range of delays.

Figure 5: Example Delay Values

Using ATACS, we verified that this wrapper circuit is hazard free within these delay ranges. In other words, selecting for each component any delay value within its given range yields a hazard free circuit. We intentionally made these ranges large to demonstrate that the circuit will operate properly within a wide variety of delay values. In order to demonstrate the conditions under which a hazard arises, consider increasing the range of delay values for the compute block from 50-100 ns to 100-200 ns. Running this modified circuit through ATACS yields the error trace shown in Figure 6 (as well as the same data represented graphically) and an error message indicating that the data_out signal is unable to go low. This is due to the fact that the delay through the compute block is long enough that the time from the compute block output signal (D) being updated to the latch enable signal (G) going low is less than the latch’s setup time. Similar errors can be achieved by shortening the delay through the C-element, the XOR gate, or the delay blocks.

!

"

" #$%&'

Figure 6: ATACS Error Trace

6. Results

The automatic hazard detection provided by ATACS gave us the ability to change the component delay ranges for any of the wrappers and promptly verify the hazard-freedom of the resulting circuit. By doing this systematically for each of the wrappers we were able to establish relationships between the component delay ranges and the resulting hazard-freedom of the wrapper. These results are summarized in Figure 7. In these equations, the name of a component (i.e. D3, xorG, etc.) is used to represents the range of delays for that component. The min() and max() functions represent the minimum and maximum values, respectively, of a given delay range. The min(D1, D2, D3, D4) terms represent the minimum delay through any one of those four delay blocks, because the delay range for each block is assumed to be the same.

Figure 7: Minimum Delay Block Delays Required for Hazard-Free Circuits

The equations are given in the form above, with all of the terms involving delay blocks isolated on the left hand side, because this is the most useful form for the design and implementation of the wrapper circuits. Given the delay ranges for all of the components other than the delay blocks, a designer can easily calculate the minimum required delay through the delay blocks which will still result in a hazard-free circuit. Of course it is suggested that the designer also add a margin to account for discrepancies between predicted delays and the delays of the final physical layout.

It is important to note that using the above equations to design a wrapper will only guarantee the hazard-freedom of the internal operation of the wrapper, not the external circuit as a whole. In order to ensure the proper operation of the entire circuit, we must also adhere to the pre-existing PL timing constraints used in the current mapping process. Specifically, for non-feedback control inputs, the minimum time from the arrival of the input signal to the updating of the clock input of the phase DFF must be greater than or equal to the maximum time from the arrival of the input signal to the updating of the D input of the D-latch. For feedback inputs, the minimum time from the arrival of the input signal to the updating of the clock input of the phase DFF must be greater than or equal to the maximum time from the arrival of the input signal to the updating of the enable input of the D-latch.

For example, for the delays shown in Figure 5, we calculate the minimum required delay through the delay blocks to be 85 ps. Assume that we choose to implement this delay entirely in the D5 block and make the delay through the D1, D2, D3, and D4 blocks zero. Then the phase output signal can be updated in as little as 45 ps after the arrival of the input signals, while it can take up to 130 ps to update the data output signal. This represents a violation of the PL requirement that every block updates its data output signals before or at the same time that it updates its phase output signal. So even though the resulting wrapper circuit will have no internal hazards, hazards may exist when the wrapper is connected to other blocks.

7. Conclusion

The introduction of the asynchronous design methodology known as Phased Logic gave digital designers a powerful new alternative to the traditional synchronous design approach. PL’s support for the automated translation from a clocked netlist to a self-timed netlist greatly simplifies the asynchronous design process and allows asynchronous designers to use existing synchronous development tools. The extension of PL to its current coarse-grain implementation represented yet another simplification of the design process, because it allows existing logic blocks to be enclosed by wrapper logic with no modification to their internal structure. In addition, adhering to the PL timing constraints guarantees the hazard-free operation of the resulting circuit at the block level. Until now, however, there existed no timing constraints governing the internal operation of the wrapper circuits. This research is an attempt to fill that void and simplify the PL design process even further. Using VHDL models of the PL wrapper circuits and the automated hazard-checking in ATACS, we were able to produce equations for each wrapper specifying the minimum delay through the delay blocks required to guarantee hazard-freedom. Using these equations along with the PL timing constraints that are currently implemented in the mapping tool will guarantee the correct and hazard-free operation of a coarse-grain Phased Logic circuit.

8. Acknowledgements

I would like to thank Chris Meyers at the University of Utah, not only for his role in the development of ATACS and related VHDL packages, but also for his personal assistance during all stages of this research. I would also like to thank Bob Reese at Mississippi State University for his help in understanding the Phased Logic wrapper circuits. This research was funded by a grant from IBM/SRC.

9. References

[1]Daniel H. Linder and James C. Harden, "Phased Logic: Supporting the Synchronous Design

Paradigm with Delay-Insensitive Circuitry." IEEE Transactions on Computers, Vol. 45, No.

9, September 1996.

[2]M.E. Dean, T.E. Williams, and D.L. Dill, “Efficient Self-Timing with Level-Encoded 2-

Phase Dual-Rail (LEDR),” in Advanced Research in VLSI, 1991.

[3]Robert B. Reese, Mitchell A. Thornton, and Cherrice Traver, "A Course-Grain Phased Logic

CPU", 9th IEEE International Symposium on Asynchronous Circuits and Systems (Async 2003), Vancouver, Canada.

[4]Sutherland, “Micropipelines”, Communications of the ACM, Vol 32, No. 6, June 1989, pp.

720-738.

[5]Robert B. Reese, Mitchell A. Thornton, and Cherrice Traver, “Async 2004 Tutorial – Phased

Logic”, Workshop Notes, 10th International Symposium on Advanced Research in

Asynchronous Circuits and Systems, Crete, Greece, April 2004.

[6]Curtis A. Nelson, Chris J. Meyers, and Tomohiro Yoneda, "Efficient Verification of Hazard-

Freedom in Gate-Level Timed Asynchronous Circuits", 2003 International Conference on Computer-Aided Design, November 2003.

[7]Myers Research Group, “The ATACS User’s Manual”, University of Utah,

https://www.doczj.com/doc/1510787815.html,/tools/atacsman.html

[8]Myers, Chris. Asynchronous Circuit Design. New York: Wiley, 2001.

Appendix A: VHDL Models

A.1 Figure 1 Model

( & )

*# ) +$,-./ 0 ( & +1

2 3

4 ! 4 3

4 ) )4 3

2

*

5 5 5

6 3

5 5

6 3

5 6 13

3

7

85 8 5 8 5 8 5 8 5 8"5 5 9# 5 9# 6 6: ; ;3

/ 5 / 5 5 <5 9# 5 9# 5 6 6: ; ;3

2 7 *& : 5 = : 1

& 2 6 6: " 3

= 2 6 6: 3

& 8" 6 6: " 3

= 8" 6 6: 3

& ) 6 6: " 3

= ) 6 6: 3

& / 6 6: 3

= / 6 6: 3

& / 6 6: 3

= / 6 6: 3

& > < 6 6: "3

= > < 6 6: "3

& > / 6 6: "3

= > / 6 6: "3

& 6 6: "3

= 6 6: "3

& 6 6: 3

= 6 6: 3

& 6 6: 3 ? * 21 : 2

= 6 6: "3

) )

8 @: 2*& ) 5 = ) 13

2

8 @: 2*& 25 = 213

8 @: 2*& 25 = 213

8 @: 2*& 25 = 213

8 @: 2*& 25 = 213

8" @: 2*& 8"5 = 8"13

< @: / > 8" 2*& > <5 = > <13

@: / > 8" 2*& > /5 = > /13

* 7 1

@: 2*& 5 = 13

)

/ @: * * * 1 * / 1 1 * 1 1 2*& / 5 = / 13

/ @: * * ***8 8 1 8 1 8 1 * / 1 1 ***8 8 1 8 1 8 1 1 2*& / 5 = / 13

)

@: ; ; 2*& 5 = 1 < : ; ; 8 : ; ;

; ; 2*& 5 = 1 < : ; ; 8 : ; ;

2*& 5 = 13

)

@: ; ; 2*& 5 = 1 : ; ;

9# 2*& 5 = 13

@: ; ; 2*& 5 = 1 : ; ;

9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; : ; ; ; ; 2*& 5 = 1 : ; ; : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; 9# : ; ; ; ; 2*& 5 = 1 : ; ; 9# : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; : ; ; ; ; 2*& 5 = 1 : ; ; : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; 9# : ; ; ; ; 2*& 5 = 1 : ; ; 9# : ; ; 9# 2*& 5 = 13

7 3

A.2 Figure 2 Model

( & )

*# A ) +$,-./ 0 ( & +1

2 3

4 ! 4 3

4 ) )4 3

2 A

*

5 5 5

6 3

5 5

6 3

5 6 13

A3

7 A

85 8 5 8 5 8 5 8 5 5 9# 5 9# 6 6: ; ;3

5 <5 9# 5 9# 5

6 6: ; ;3

2 7 *& : 5 = : 1

& 2 6 6: B 3

= 2 6 6: 3

& ) 6 6: " 3

= ) 6 6: 3

& ) 6 6: "3

= ) 6 6: 3

& 6 6: "3

= 6 6: "3

& 6 6: 3

= 6 6: 3

& 6 6: 3 ? * 21 : 2

= 6 6: "3

) )

8 @: 2*& ) 5 = ) 13

2

8 @: 2*& 25 = 213

8 @: 2*& 25 = 213

8 @: 2*& 25 = 213

8 @: 2*& 25 = 213

* 7 1

@: 2*& 5 = 13

* ) 1

< @: 2*& ) 5 = ) 1 : ; ;

* 1 2*& ) 5 = ) 13

@: ***8 8 1 8 1 8 1 2*& ) 5 = ) 1 : ; ;

*8 8 8 8 1 2*& ) 5 = ) 13

)

@: ; ; 2*& 5 = 1 < : ; ; 8 : ; ;

; ; 2*& 5 = 1 < : ; ; 8 : ; ;

2*& 5 = 13

)

@: ; ; 2*& 5 = 1 : ; ;

9# 2*& 5 = 13

@: ; ; 2*& 5 = 1 : ; ;

9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; : ; ; ; ; 2*& 5 = 1 : ; ; : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; 9# : ; ; ; ; 2*& 5 = 1 : ; ; 9# : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; : ; ; ; ; 2*& 5 = 1 : ; ; : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; 9# : ; ; ; ; 2*& 5 = 1 : ; ; 9# : ; ; 9# 2*& 5 = 13

7 3

A.3 Figure 3 Model

( & 2 7

*# ! ) +$,-./ 0 ( & +1

2 3

4 ! 4 3

4 ) )4 3

2 !

*

5 5 5

6 3

5 5

6 3

5 6 13

!3

7 !

85 8 5 8 5 5 9# 5 9# 5 9# 5 9# 6 6: ; ;3

5 9# 5 9# 5

6 6: ; ;3

2 7 *& : 5 = : 1

& 2 6 6: 3

= 2 6 6: " 3

& ) 6 6: " 3

= ) 6 6: 3

& ) 6 6: "3

= ) 6 6: 3

& 6 6: "3

= 6 6: "3

& 6 6: 3 ? * 21 : 2

= 6 6: "3

) )

8 @: 2*& ) 5 = ) 13

2

8 @: 2*& 25 = 213

8 @: 2*& 25 = 213

* / ) 1

@: 8 8 2*& ) 5

= ) 1

: ; ;

*8 8 1 2*& ) 5

= ) 13

* 7 1

@: 2*& 5 = 13

)

9# @: ; ; 2*& 5 = 1 : ; ; 8 : ; ;

; ; 2*& 5 = 1 : ; ; 8 : ; ;

9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; 9# : ; ;

; ; 2*& 5 = 1 : ; ; 9# : ; ;

9# 2*& 5 = 13

@: ; ; 2*& 5 = 1 : ; ;

9# 2*& 5 = 13

)

9# @: ; ; 2*& 5 = 1 : ; ; : ; ; ; ; 2*& 5 = 1 : ; ; : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; : ; ; ; ; 2*& 5 = 1 : ; ; : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; 9# : ; ; ; ; 2*& 5 = 1 : ; ; 9# : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; 9# : ; ; ; ; 2*& 5 = 1 : ; ; 9# : ; ; 9# 2*& 5 = 13

@: ; ; 2*& 5 = 1 : ; ; 9# 2*& 5 = 13

@: ; ; 2*& 5 = 1 : ; ; 9# 2*& 5 = 13

7 3

A.4 Figure 4 Model

( & 2 7

*# B ) +$,-./ 0 ( & +1

2 3

4 ! 4 3

4 ) )4 3

2 B

*

5 5 5 5

6 3

5 5 5

6 3

5 5

6 13

B3

7 B

85 8 5 8 5 5 ) >5 5 9#5 9# 6 6: ; ;3

8C 5 8C 5 8C 5 DD 85 DD 95 & 5 & 2 6 6: ; ;3

9# 5 9# 5 5 0 6 6: ; ;3

2 7 *& : 5 = : 1

& 2 6 6: " 3

= 2 6 6: 3

& ) 6 6: " 3

= ) 6 6: 3

& 7 6 6: "3

= 7 6 6: " 3

& / 6 6: 3

= / 6 6: 3

& / 6 6: 3

= / 6 6: 3

& / 6 6: 3

= / 6 6: 3

& > 6 6: "3

= > 6 6: "3

& 6 6: "3

= 6 6: "3

& 6 6: 3

= 6 6: 3

& 6 6: 3 ? * 21 : 2

= 6 6: "3

& ) > 6 6: 3

= ) > 6 6: 3

)

*

5 6 3

6 13

) 3

) )

8 @: * 1 * 1 * 1

2*& ) 5 = ) 13

2 7

DD 8 @: * > 1 2*& 7 5 = 7 13

2 7

DD 9 @: ; ; 2*& 5 = 1 *0 > & 1 : ; ; DD 8 : ; ;

; ; 2*& 5 = 1 *0 > & 1 : ; ; DD 8 : ; ;

DD 9 2*& 5 = 13

2

8 @: 2*& 25 = 213

8 @: 2*& 25 = 213

2

6

) *

: 5

: 5

: 8C 13

6

) *

: 5

: 5

: 8C 13

6

) *

: 5

: 5

: 8C 13

/ )

0 @: * * *& 8 8 1 * 0 1 1 *& 8 8 1 1 2*& / 5 = / 13

& @: * * ** 0 1 8C 8C 8C 1 * & 1 1 ** 0 1 8C

8C 8C 1 1 2*& / 5 = / 13

& 2 @: * * ** & 1 0 1 *

& 21 1 ** & 1 0 1 1

2*& / 5 = / 13

) >

) > @: ; ; 2*& ) >5 = ) >1 DD 9 : ; ; & : ; ; ; ; 2*& ) >5 = ) >1 DD 9 : ; ; & : ; ; ; ; 2*& ) >5 = ) >1 DD 9 : ; ; & 2 : ; ; ; ; 2*& ) >5 = ) >1 DD 9 : ; ; & 2 : ; ; ) > 2*& ) >5 = ) >13

@: ; ; 2*& ) >5 = ) >1 DD 9 : ; ; & : ; ; ; ; 2*& ) >5 = ) >1 DD 9 : ; ; & : ; ; ; ; 2*& ) >5 = ) >1 DD 9 : ; ; 0 : ; ; ; ; 2*& ) >5 = ) >1 DD 9 : ; ; 0 : ; ; 2*& ) >5 = ) >13

> * 1

@: ) > > 2*& > 5 = > 13

* 7 1

@: 2*& 5 = 13

)

@: ; ; 2*& 5 = 1 : ; ; 8 : ; ;

; ; 2*& 5 = 1 : ; ; 8 : ; ;

2*& 5 = 13

)

@: ; ; 2*& 5 = 1 : ; ; 9# 2*& 5 = 13

@: ; ; 2*& 5 = 1 : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; : ; ; ; ; 2*& 5 = 1 : ; ; : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; 9# : ; ; ; ; 2*& 5 = 1 : ; ; 9# : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; : ; ; ; ; 2*& 5 = 1 : ; ; : ; ; 9# 2*& 5 = 13

9# @: ; ; 2*& 5 = 1 : ; ; 9# : ; ; ; ; 2*& 5 = 1 : ; ; 9# : ; ; 9# 2*& 5 = 13

7 3

A.5 Delay Kill Block Model

2 3

4 ! 4 3

4 ) )4 3

2

*

5 6 3

6 13

3

7

$ 5 $ 5 $ 6 3

E 5 E 5 E 6 3

2 7 *& : 5 = : 1

& 6 6: "3

= 6 6: " 3

& 6 6: "3

= 6 6: " 3

& ) > 6 6: 3

= ) > 6 6: 3

$.8

$ @: 2*& 5 = 13

$ @: $ 2*& 5 = 13

$ @: $ 2*& 5 = 13

FG

E @: 2*& 5 = 13

E @: E 2*& 5 = 13

E @: E 2*& 5 = 13

) >

@: ; ; 2*& ) >5 = ) >1 : ; ; E : ; ;

; ; 2*& ) >5 = ) >1 : ; ; E : ; ;

; ; 2*& ) >5 = ) >1 : ; ; $ : ; ;

; ; 2*& ) >5 = ) >1 : ; ; $ : ; ;

2*& ) >5 = ) >13

7 3

Appendix B: VHDL Environment Files

B.1 Environment File for Figures 1, 2, 3

D 7 ) ( & 6 H I )

H I ) H I 2 7

2 3

4 ! 4 3

4 ) )4 3

4 4 3

2 7 )

7 ) 3

7 7 )

)

*

5 5 5

6 3

5 5

6 3

5 6 13

) 3

5 5 5

6 3

5 5 5 5

6 3

6

) *

: 5

: 5

: 5

: 5

: 5

: 5

: 5

: 5

: 13

* 5 ; ;5 5 13

* 5 ; ;5 5 5 5 ; ;5 5 13

* 5 ; ;5 5 5 5 ; ;5 5 13

* 5 ; ;5 5 5 5 ; ;5 5 13

* 5 ; ;13

2* 5 " 13

* 5 ; ;5 5 13

7

* 5 ; ;5 5 5 5 ; ;5 5 13

7

* 5 ; ;5 5 5 5 ; ;5 5 13

7

* 5 ; ;5 5 5 5 ; ;5 5 13

* 5 ; ;5 5 ; ;13

2* 5 " 13

7

* 5 ; ;5 5 5 5 ; ;5 5 13

7

* 5 ; ;5 5 5 5 ; ;5 5 13

7

* 5 ; ;5 5 5 5 ; ;5 5 13

* 5 ; ;5 5 ; ;13

2* 5 " 13

3

3

7 3

B.2 Environment File for Figure 4

D 7 ) ( & 2 7

2 3

4 ! 4 3

4 ) )4 3

4 4 3

2 7 ) B

7 ) B3

7 B 7 ) B

) B

*

5 5 5 5

6 3

5 5 5

6 3

5 5

6 13

) 3

5 5 5 5 5

6 3 5 5 5 5 5 6 3

B 6 B

) *

: 5

: 5

: 5

: 5

: 5

: 5

: 5

: 5

: 5

: 5

: 5

: 13

* 5 ; ;5 5 13

* 5 ; ;5 5 13

* 5 ; ;5 5 5 5 ; ;5 5 5 5 ; ;5 5 13

* 5 ; ;5 5 5 5 ; ;5 5 13

* 5 ; ;13

2*" 5 " 13

* 5 ; ;5 5 13

D$G&- #%GD

7

* 5 ; ;5 5 5 5 ; ;5 5 13

7

* 5 ; ;5 5 5 5 ; ;5 5 5 5 ; ;5 5 13

7

* 5 ; ;5 5 5 5 ; ;5 5 13

* 5 ; ;5 5 ; ;13

2*" 5 " 13

&$0D #%GD

7

“的、地、得”的用法和区别 导入(进入美妙的世界啦~) “的、地、得”口诀儿歌 的地得,不一样,用法分别记心上, 左边白,右边勺,名词跟在后面跑。 美丽的花儿绽笑脸,青青的草儿弯下腰, 清清的河水向东流,蓝蓝的天上白云飘, 暖暖的风儿轻轻吹,绿绿的树叶把头摇, 小小的鱼儿水中游,红红的太阳当空照, 左边土,右边也,地字站在动词前, 认真地做操不马虎,专心地上课不大意, 大声地朗读不害羞,从容地走路不着急, 痛快地玩耍来放松,用心地思考解难题, 勤奋地学习要积极,辛勤地劳动花力气, 左边两人双人得,形容词前要用得, 兔子兔子跑得快,乌龟乌龟爬得慢, 青青竹子长得快,参天大树长得慢, 清晨锻炼起得早,加班加点睡得晚, 欢乐时光过得快,考试题目出得难。 知识典例(注意咯,下面可是黄金部分!) 的、地、得 “的”、“地”、“得”的用法区别本是中小学语文教学中最基本的常识,但在使用中也最容易发生混淆,再加上一段时间里,中学课本中曾将这三个词的用法统一为“的”,因此造成了很多人对它们的用法含混不清进而乱用一通的现象。

一、“的、地、得”的基本概念 1、“的、地、得”的相同之处。 “的、地、得”是现代汉语中高频度使用的三个结构助词,都起着连接作用;它们在普通话中都读轻声“de”,没有语音上的区别。 2、“的、地、得”的不同之处。 吕叔湘、朱德熙所著《语法修辞讲话》认为“的”兼职过多,负担过重,而力主“的、地、得”严格分工。50 年代以来的诸多现代汉语论著和教材,一般也持这一主张。从书面语中的使用情况看,“的”与“地”、“得”的分工日趋明确,特别是在逻辑性很强的论述性、说明性语言中,如法律条款、学术论著、外文译著、教科书等,更是将“的”与“地”、“得”分用。 “的、地、得”在普通话里都读轻声“de”,但在书面语中有必要写成三个不同的字:在定语后面写作“的”,在状语后面写作“地”,在补语前写作“得”。这样做的好处,就是可使书面语言精确化。 二、“的、地、得”的用法 1、的——定语的标记,一般用在主语和宾语的前面。“的”前面的词语一般用来修饰、限制“的”后面的事物,说明“的”后面的事物怎么样。结构形式一般为:形容词、名词(代词)+的+名词。如: ①颐和园(名词)的湖光山色(主语)美不胜收。 ②她是一位性格开朗的女子(名词,宾语)。 2、地——状语的标记,一般用在谓语(动词、形容词)前面。“地”前面的词语一般用来形容“地”后面的动作,说明“地”后面的动作怎么样。结构方式一般为:形容词(副词)+地+动词(形容词)。如: ③她愉快(形容词)地接受(动词,谓语)了这件礼物。 ④天渐渐(时间副词)地冷(形容词,谓语)起来。 3、得——补语的标记,一般用在谓语后面。“得”后面的词语一般用来补充说明“得”前面的动作怎么样,结构形式一般为:动词(形容词)+得+副词。如: ⑤他们玩(动词,谓语)得真痛快(补语)。

分考点1 表示时间的介词 Point 1 at, in, on 的用法 (1)at 的用法 At 表示时间点,用于具体的时刻(几点,正午,午夜,黎明,拂晓,日出,日落等),或把某一时间看作某一时刻的词之前以及某些节假日的词之前。 at 6:00 在6点钟 At noon 在中午 At daybreak 在拂晓 At down 在黎明 At Christmas 在圣诞节 【特别注意】在以下的时间短语中,at 表示时间段。 At dinner time 在(吃)晚饭时 At weekends/ the weekend 在周末 (2)in 的用法 ①表示时间段,与表示较长一段时间的词搭配,如年份,月份,季节,世纪,朝代,还可以用于泛指的上午、下午、傍晚等时间段的词前。 In 2009 在2009年 In April 在四月 In the 1990s 在20世纪90年代 In Tang Dynasty 在唐朝 In the morning在上午 ②后接时间段,用于将来时,表示“在一段时间之后”。 The film will begin in an hour. 电影将于一个小时之后开始。 【特别注意】当时间名词前有this,that,last,next,every,each,some等词修饰时,通常不用任何介词。 This morning 今天上午last year 去年 (3)on 的用法 ①表示在特定的日子、具体的日期、星期几、具体的某一天或某些日子。 On September the first 在9月1号 On National Day 在国庆节 We left the dock on a beautiful afternoon. 我们在一个明媚的下午离开了码头。 ②表示在具体的某一天的上午、下午或晚上(常有前置定语或后置定语修饰)。 On Sunday morning 在星期日的早上 On the night of October 1 在10月1号的晚上 【特别注意】“on +名词或动名词”表示“一...就...”. On my arrival home/ arriving home, I discovered they had gone. 我一到家就发现他们已经离开了。 Point 2 in,after 的用法 In 和after都可以接时间段,表示“在...之后”,但in 常与将来时连用,after 常与过去时连用。 We will meet again in two weeks.

英语介词用法大全 TTA standardization office【TTA 5AB- TTAK 08- TTA 2C】

介词(The Preposition)又叫做前置词,通常置于名词之前。它是一种虚词,不需要重读,在句中不单独作任何句子成分,只表示其后的名词或相当于名词的词语与其他句子成分的关系。中国学生在使用英语进行书面或口头表达时,往往会出现遗漏介词或误用介词的错误,因此各类考试语法的结构部分均有这方面的测试内容。 1. 介词的种类 英语中最常用的介词,按照不同的分类标准可分为以下几类: (1). 简单介词、复合介词和短语介词 ①.简单介词是指单一介词。如: at , in ,of ,by , about , for, from , except , since, near, with 等。②. 复合介词是指由两个简单介词组成的介词。如: Inside, outside , onto, into , throughout, without , as to as for , unpon, except for 等。 ③. 短语介词是指由短语构成的介词。如: In front of , by means o f, on behalf of, in spite of , by way of , in favor of , in regard to 等。 (2). 按词义分类 {1} 表地点(包括动向)的介词。如: About ,above, across, after, along , among, around , at, before, behind, below, beneath, beside, between , beyond ,by, down, from, in, into , near, off, on, over, through, throught, to, towards,, under, up, unpon, with, within , without 等。 {2} 表时间的介词。如: About, after, around , as , at, before , behind , between , by, during, for, from, in, into, of, on, over, past, since, through, throughout, till(until) , to, towards , within 等。 {3} 表除去的介词。如: beside , but, except等。 {4} 表比较的介词。如: As, like, above, over等。 {5} 表反对的介词。如: againt ,with 等。 {6} 表原因、目的的介词。如: for, with, from 等。 {7} 表结果的介词。如: to, with , without 等。 {8} 表手段、方式的介词。如: by, in ,with 等。 {9} 表所属的介词。如: of , with 等。 {10} 表条件的介词。如:

英语单词惯用法集锦 习惯接动词不定式的动词(V to inf) adore(vi极喜欢) dread (vt.不愿做,厌恶)plan 计划 afford(+to,vt有条件,能承担)endeavour (vt,竭力做到,试图或力图)prefer(vt.宁可;宁愿(选择);更喜欢)agree 同意endure(忍受.cannot ~ to) prepare准备 aim (vi[口语]打算:) engage (vi.保证,担保;) presume(vt.冒昧;敢于[用于第一人称时为客套话]:) appear (vi.似乎;显得) essay(vt.尝试,试图) pretend(vt.自命;自称;敢于;妄为) apply (申请)expect(期望,希望)proceed(开始,着手,)arrange (vi.做安排,(事先)筹划)fail (vt.未做…;疏忽)promise(许诺,保证做 ask (要求)forget (vt. 忘记)purpose (vt.决心,打算) beg (vt.正式场合的礼貌用语]请(原谅),请(允许):I beg to differ.恕我不能赞同)guarantee(保证,担保)refuse(拒绝)bear 承受,忍受hate([口语]不喜欢;不愿意;)regret (vt. 抱歉;遗憾)begin help (有助于,促进)remember(记住) bother (vi.通常用于否定句]麻烦,费心)hesitate(vi.犹豫;有疑虑,不愿)scheme(策划做)care (vt.想要;希望;欲望[后接不定式,常用于否定、疑问及条件句中])hope (vt.希望,盼望,期待)seek(vt.谋求,图谋[后接不定式]) cease (停止; 不再(做某事)[正式] intend (打算;想要)seem(似乎,好像[后接不定式或从句];觉得像是,以为[ choose (意愿;选定;决定)itch start开始claim (vt. 主张;断言;宣称) continue (继续)like 喜欢swear(vt.起誓保证;立誓要做(或遵守) dare (vt.敢,敢于,勇于,胆敢)long(vi.渴望;热望;极想) decline(vt.拒绝,拒不(做、进入、考虑等) manage(设法完成某事)threaten(vt.威胁,恐吓,恫吓)deign (屈尊做)mean(有意[不用进行时)trouble(vi.费心,费神;麻烦)demand(vi.要求,请求:)need (需要)try(设法做) deserve (应得) neglect (疏忽) undertake(承诺,答应,保证) desire (希望渴望)offer(表示愿意(做某事),自愿;)venture(冒险(做某事))determine(vi.决心,决意,决定,)omit (疏忽,忘记)want 想要 die (誓死做)pine (渴望)wish (希望) 习惯接“疑问词+动词不定式”的动词(有时也包括VN wh-+to do) advise 建议explain 解释perceive 觉察,发觉 answer 答复find 得知,察觉persuade 说服,劝说;使某人相信 ask 询问,问forget 忘记phone 打电话 assure 保证guess 臆测,猜度pray 祈祷 beg 请求,恳求hear 小心聆听(法庭案件)promise 允诺 conceive 想象,设想imagine 以为,假象remember记得 consider 考虑,思考indicate 暗示remind 提醒,使想起 convince 使相信inform告知通知instruct告知,教导 see 看看,考虑,注意decide 解决,决定know 学得,得知 show 给人解释;示范;叙述;discover发现;知道learn 得知,获悉 signal以信号表示doubt 怀疑,不相信look 察看;检查;探明 strike 使想起;使突然想到;使认为suggest 提议,建议tell 显示,表明;看出,晓得;warn 警告,告诫think 想出;记忆,回忆;想出,明白wonder 纳闷,想知道 wire 打电报telegraph 打电报 习惯接动名词的动词(包括v+one’s/one+v+ing) acknowledge 认知,承认…之事实escape免除,避免omit疏忽,忽略 admit 承认,供认excuse 原谅overlook 放任,宽容,忽视adore (非正式)极为喜欢fancy 构想,幻想,想想postpone 延期,搁置 advise 劝告,建议finish完成prefer较喜欢 appreciate 为…表示感激(或感谢)forbid 不许,禁止prevent预防 avoid 逃避forget 忘记prohibit 禁止,妨碍

的、地、得的用法和区别 的、地、得的用法和区别老班教育 一、的、地、得的基本概念 1、的、地、得的相同之处。 的、地、得是现代汉语中高频度使用的三个结构助词,都起着连接作用;它们在普通话中都读轻声de,没有语音上的区别。 2、的、地、得的不同之处。 吕叔湘、朱德熙所著《语法修辞讲话》认为的兼职过多,负担过重,而力主的、地、得严格分工。50 年代以来的诸多现代汉语论著和教材,一般也持这一主张。从书面语中的使用情况看,的与地、得的分工日趋明确,特别是在逻辑性很强的论述性、说明性语言中,如法律条款、学术论著、外文译著、教科书等,更是将的与地、得分用。 的、地、得在普通话里都读轻声de,但在书面语中有必要写成三个不同的字:在定语后面写作的,在状语后面写作地,在补语前写作得。这样做的好处,就是可使书面语言精确化。 二、的、地、得的用法 (一)、用法 1、的——定语的标记,一般用在主语和宾语的前面。的前面的词语一般用来修饰、限制的后面的事物,说明的后面的事物怎么样。 结构形式一般为:形容词、名词(代词)+的+名词。如: 颐和园(名词)的湖光山色(主语)美不胜收。 她是一位性格开朗的女子(名词,宾语)。 2、地——状语的标记,一般用在谓语(动词、形容词)前面。地前面的词语一般用来形容地后面的动作,说明地后面的动作怎么样。 结构方式一般为:形容词(副词)+地+动词(形容词)。如: 她愉快(形容词)地接受(动词,谓语)了这件礼物。 天渐渐(时间副词)地冷(形容词,谓语)起来。 3、得——补语的标记,一般用在谓语后面。得后面的词语一般用来补充说明得前面的动作怎么样。 结构形式一般为:动词(形容词)+得+副词。如: 他们玩(动词,谓语)得真痛快(补语)。 她红(形容词,谓语)得发紫(补语)。 (二)、例说 的,一般用在名词和形容词的后面,用在描述或限制人物、事物时,形容的词语与被形容的词语之间,表示一种描述的结果。如:漂亮的衣服、辽阔的土地、高大的山脉。结构一般为名词(代词或形容词)+的+名词。如,我的书、你的衣服、他的孩子,美丽的景色、动听的歌曲、灿烂的笑容。 地,用法简单些,用在描述或限制一种运动性质、状态时,形容的词语与被形容的词语之间。结构通常是形容词+地+动词。前面的词语一般用来形容后面的动作。一般地的后面只跟动词。比如高兴地跳、兴奋地叫喊、温和地说、飞快地跑;匆匆地离开;慢慢地移动......... 得,用在说明动作的情况或结果的程度时,说明的词语与被说明的词语之间,后面的词语一般用来补充和说明前面的情况。比如。跑得飞快、跳得很高、显得高雅、显得很壮、馋得直流口水、跑得快、飞得高、走得慢、红得很……得通常用在动词和形容词(动词之间)。

英语常用介词用法与辨析 ■表示方位的介词:in, to, on 1. in 表示在某地范围之内。如: Shanghai is/lies in the east of China. 上海在中国的东部。 2. to 表示在某地范围之外。如: Japan is/lies to the east of China. 日本位于中国的东面。 3. on 表示与某地相邻或接壤。如: Mongolia is/lies on the north of China. 蒙古国位于中国北边。 ■表示计量的介词:at, for, by 1. at表示“以……速度”“以……价格”。如: It flies at about 900 kilometers a hour. 它以每小时900公里的速度飞行。 I sold my car at a high price. 我以高价出售了我的汽车。 2. for表示“用……交换,以……为代价”。如: He sold his car for 500 dollars. 他以五百元把车卖了。 注意:at表示单价(price) ,for表示总钱数。 3. by表示“以……计”,后跟度量单位。如: They paid him by the month. 他们按月给他计酬。 Here eggs are sold by weight. 在这里鸡蛋是按重量卖的。 ■表示材料的介词:of, from, in 1. of成品仍可看出原料。如: This box is made of paper. 这个盒子是纸做的。 2. from成品已看不出原料。如: Wine is made from grapes. 葡萄酒是葡萄酿成的。 3. in表示用某种材料或语言。如: Please fill in the form in pencil first. 请先用铅笔填写这个表格。 They talk in English. 他们用英语交谈(from 。 注意:in指用材料,不用冠词;而with指用工具,要用冠词。请比较:draw in penc il/draw with a pencil。 ■表示工具或手段的介词:by, with, on 1. by用某种方式,多用于交通。如by bus乘公共汽车,by e-mail. 通过电子邮件。

with的用法大全----四级专项训练with结构是许多英语复合结构中最常用的一种。学好它对学好复合宾语结构、不定式复合结构、动名词复合结构和独立主格结构均能起很重要的作用。本文就此的构成、特点及用法等作一较全面阐述,以帮助同学们掌握这一重要的语法知识。 一、 with结构的构成 它是由介词with或without+复合结构构成,复合结构作介词with或without的复合宾语,复合宾语中第一部分宾语由名词或代词充当,第二部分补足语由形容词、副词、介词短语、动词不定式或分词充当,分词可以是现在分词,也可以是过去分词。With结构构成方式如下: 1. with或without-名词/代词+形容词; 2. with或without-名词/代词+副词; 3. with或without-名词/代词+介词短语; 4. with或without-名词/代词+动词不定式; 5. with或without-名词/代词+分词。 下面分别举例:

1、 She came into the room,with her nose red because of cold.(with+名词+形容词,作伴随状语) 2、 With the meal over , we all went home.(with+名词+副词,作时间状语) 3、The master was walking up and down with the ruler under his arm。(with+名词+介词短语,作伴随状语。) The teacher entered the classroom with a book in his hand. 4、He lay in the dark empty house,with not a man ,woman or child to say he was kind to me.(with+名词+不定式,作伴随状语) He could not finish it without me to help him.(without+代词 +不定式,作条件状语) 5、She fell asleep with the light burning.(with+名词+现在分词,作伴随状语) 6、Without anything left in the cupboard, she went out to get something to eat.(without+代词+过去分词,作为原因状语) 二、with结构的用法 在句子中with结构多数充当状语,表示行为方式,伴随情况、时间、原因或条件(详见上述例句)。

1、keep ①keep + 形容词表示“保持” Please keep quite. 请保持安静。 ②keep + 宾语+ 形容词(或介词短语)表示“把……保持在某一状态” We must do everything we can to keep the air clean. 我们必须尽一切所能保持空气清洁。 ③keep sb doing sth 表示“让某人做某事” ——只能用现在分词作宾语补足语,不能用不定式。 He kept us waiting for two hours. 他让我们等了两个小时。 He kept us to wait for two hours. (错误) ④keep on doing sth和keep doing sth 表示“继续做某事,反复做某事”,可换用。 但keep on doing 更强调动作的反复性或做事人的决心。 He keeps on phoning me, but I don’t want to talk to him. Though he failed 3 times, he kept on trying. 他老是给我打电话,但我不想同他讲话。虽然他已失败了3次,但他仍继续干下去。 keep doing sth 经常用于静态动词。 He kept lying in bed all day long. 他整天都躺在床上。 ⑤keep …from doing sth 表示“阻止,使免于” He kept them from fishing in the lake. 他不让他们在那个湖里捕鱼。 2、may not / mustn’t / needn’t / wouldn’t ①may not be 是may be的否定式,意为“可能不是,也许不是” He may be there.他可能在那里。He may not be there.他可能不在那里。 ②must 意为“必须”,mustn’t 意为“千万不可,绝对不可” 所以Must we/I ……?的否定回答要用needn’t—意为“不必” -Must we get there before 11 o’clock? -No, we needn’t. ③wouldn’t = would not 意为“不会,不愿” I wouldn’t say no. 3、do ①do表示“做”,做某事,常指某种不具体的活动;make表示“制作”,指做出某种具体的东西。

《“的、地、得”的用法》语文微课教案 一、教学背景 在语言文字规范化大背景下,帮助学生解决应用“的地得”的疑惑与困难。 二、设计思路 针对学生对于“的地得”的误用与忽视展开教学,规范结构助词“的地得”的使用。按照“问题的提出、问题的分析、问题的解决”的思路展开教学,总结归纳优化的方式方法。 三、教学目标 1、知道“怎么样的什么、怎么样地干什么、干得怎么样”三种固定搭配。 2、掌握“的、地、得”的区别与联系。 3、运用小儿歌“动前土、名前白、行动后面双人来”的口诀帮助正确使用“的、地、得”。 四、教学重难点 1、知道“的、地、得”的区别。 2、在实际情境中正确运用“的、地、得”。 五、教学时间 8分钟微课堂 六、教学适用对象 义务教育九年制内的学生 七、教学准备

多媒体课件、录屏软件 八、教学设计与过程 开场白: 同学们好!今天我们一起来学习“的、地、得”的正确用法。首先我们来了解一下它们的区别。 1、相同之处:原来它们都是念轻声“de”,都是结构助词,起连接作用。 2、不同之处:在书面语中要写成三个不同的字,而且它们的搭配及用法也各不相同。 (1)怎么样的什么 (2)怎样样地干什么 (3)干得怎么样 下面我们就来学习一下它们的正确用法。 白勺“的”的结构是用“形容词或名词或代词+的+名词”来表示,而我们最常见,用得最多的还是“形容词+的+名词”的结构。 而土也“地”的用法可以用“形容词+地+动词”的结构来表示。 双人“得”是用“动词+得+形容词”的结构来表示 3、练习巩固 (1)形近区分 静静(的)河面静静(地)写字欢乐(的)山谷

欢乐(地)歌唱满意(地)点头满意(的)作品 (2)类别区分 1)跑(得)飞快飞快(地)跑 2)愉快(的)旅行旅行(得)愉快 3)强烈(的)渴望强烈(地)渴望 (3)综合杂糅 小雏鹰飞到大树的上方,高兴地喊起来:“我真的会飞啦!而且飞(得)很高呢!” 小结:能填对这个句子的你肯定就已经学会它们的用法了! 4、特殊情况 质疑:假如遇到特殊情况怎么办呢? 我从书包里拿出书交给她们,她们高兴得.围着我跳起舞来。(出自二年级上册《日记两则》) (1)质疑:为什么这里要使用“得”呢? (2)释疑:原来这里强调的是心情,动词在后,形容词在前,相当于后置,“得”修饰“跳舞”而非“围”。现在你明白了吧? 5、小结归纳: 怎么样,你们学会了吗?为了让同学们能够更快的记住它们的用法,老师送给大家一首口诀来帮助你们熟记三个“的”的正确使用方法:动前土、名前白、行动后面双人来。

——45个基本介词的用法 1、about 【原始含义】 a-b-out “A在B外面” 【引申含义】 [prep] (1)在…到处,在…各处here and there eg: We wandered about the town for an hour or so. He looked about the room. (2)在…附近next to a place eg. She lives about the office. (3)关于in connection with eg: a book about English study I don’t know what you are talking about. [adv] (1)大约close to eg: We left there about 10 o’clock. It costs about 500 dollars. (2)到处,各处 eg: The children were rushing about in the garden. (3)在附近 eg : There is no food about. 【常见搭配】 作介词时的搭配: 一.动词+(about+名词) (1)arrange (about sth) 安排关于某事(2)argue (about sth) 讨论某事 (3)ask (about sth) 询问关于某事(4)boast (about sb/sth) 吹嘘... (5)care (about sb/sth)关心…,对…感兴趣(6)chat(about sth) 谈论某事(7)complain(about sb/sth) 抱怨… (8)dream (about sb/sth) 梦见某人/某物(9)go (about sth) 着手做...;从事...

with用法归纳 (1)“用……”表示使用工具,手段等。例如: ①We can walk with our legs and feet. 我们用腿脚行走。 ②He writes with a pencil. 他用铅笔写。 (2)“和……在一起”,表示伴随。例如: ①Can you go to a movie with me? 你能和我一起去看电影'>电影吗? ②He often goes to the library with Jenny. 他常和詹妮一起去图书馆。 (3)“与……”。例如: I’d like to have a talk with you. 我很想和你说句话。 (4)“关于,对于”,表示一种关系或适应范围。例如: What’s wrong with your watch? 你的手表怎么了? (5)“带有,具有”。例如: ①He’s a tall kid with short hair. 他是个长着一头短发的高个子小孩。 ②They have no money with them. 他们没带钱。 (6)“在……方面”。例如: Kate helps me with my English. 凯特帮我学英语。 (7)“随着,与……同时”。例如: With these words, he left the room. 说完这些话,他离开了房间。 [解题过程] with结构也称为with复合结构。是由with+复合宾语组成。常在句中做状语,表示谓语动作发生的伴随情况、时间、原因、方式等。其构成有下列几种情形: 1.with+名词(或代词)+现在分词 此时,现在分词和前面的名词或代词是逻辑上的主谓关系。 例如:1)With prices going up so fast, we can't afford luxuries. 由于物价上涨很快,我们买不起高档商品。(原因状语) 2)With the crowds cheering, they drove to the palace. 在人群的欢呼声中,他们驱车来到皇宫。(伴随情况) 2.with+名词(或代词)+过去分词 此时,过去分词和前面的名词或代词是逻辑上的动宾关系。

一动词加-ing 的情况 consider, suggest/advise,look forward to, excuse/pardon admit,delay/put off,fancy avoid,miss,keep/keep on,practise deny,finish,enjoy/appreciate forbid,imagine,risk can't help,mind,allow/permit,escape 考虑建议盼原谅, 承认推迟没得想. 避免错过继续练, 否认完成就欣赏. 禁止想象才冒险, 不禁介意准逃亡. 如:建议:advise,suggest,冒险:risk,献身:devote oneself to 二动词后加doing 和加to do sth. 意思不一样的情况 ①remember doing指记住过去做过的事,remember to do指记住将来要做的事,表示“不要忘记”。 ②forget doing表示忘记过去做过的事,forget to do表示“没有想起做某事”。 ③mean doing表示“意味着做某事”,mean to do表示“打算做某事”。 ④regret doing表示对已做过的事感到后悔,regret to do表示对将要做的事表示遗憾。 ⑤stop doing表示“停止做某事”,stop to do是停止做正在做的事以便去做另外一件事,这里的to do不是stop的宾语而是stop的目的状语。 ⑥try doing表示“尝试做某事”,try to do表示“设法、试图做某事”。 ⑦go on doing表示继续做同一件事,go on to do表示做完一件事后,接下去做另外一件事。 三动词后加to do sth. afford负担得起agree同意appear似乎,显得arrange安排 ask问attempt企图beg请求begin开始 choose选择claim要求decide决定demand要求 desire愿望determine决定expect期望fail不能 forget忘记happen碰巧hate憎恨,厌恶hesitate犹豫 hope希望intend想要learn学习long渴望 love爱manage设法mean意欲,打算need需要 neglect忽视offer提供omit忽略,漏other扰乱;烦恼

介词with的用法大全 With是个介词,基本的意思是“用”,但它也可以协助构成一个极为多采多姿的句型,在句子中起两种作用;副词与形容词。 with在下列结构中起副词作用: 1.“with+宾语+现在分词或短语”,如: (1) This article deals with common social ills, with particular attention being paid to vandalism. 2.“with+宾语+过去分词或短语”,如: (2) With different techniques used, different results can be obtained. (3) The TV mechanic entered the factory with tools carried in both hands. 3.“with+宾语+形容词或短语”,如: (4) With so much water vapour present in the room, some iron-made utensils have become rusty easily. (5) Every night, Helen sleeps with all the windows open. 4.“with+宾语+介词短语”,如: (6) With the school badge on his shirt, he looks all the more serious. (7) With the security guard near the gate no bad character could do any thing illegal. 5.“with+宾语+副词虚词”,如: (8) You cannot leave the machine there with electric power on. (9) How can you lock the door with your guests in? 上面五种“with”结构的副词功能,相当普遍,尤其是在科技英语中。 接着谈“with”结构的形容词功能,有下列五种: 一、“with+宾语+现在分词或短语”,如: (10) The body with a constant force acting on it. moves at constant pace. (11) Can you see the huge box with a long handle attaching to it ? 二、“with+宾语+过去分词或短语” (12) Throw away the container with its cover sealed. (13) Atoms with the outer layer filled with electrons do not form compounds. 三、“with+宾语+形容词或短语”,如: (14) Put the documents in the filing container with all the drawers open.

pretend三种易混淆不定式的用法 今天给大家带来了pretend三种易混淆不定式的用法,我们一起来学习吧,下面就和大家分享,来欣赏一下吧。 pretend三种易混淆不定式的用法 1. pretend to do sth .这个短语的意思是假装(将要)去做什么事情,适用于将来时态动作将来假装要去做但不一定去做的状态。 举例: If youpretend to know what you dont know,youll only make afool of yourself.不懂装懂就会闹笑话。(suri的回答) Child pretend to be mother and father in kindergarten.孩子在幼稚园里面假扮父亲和母亲(表将来)(JasoOon的回答) 2. pretend to have done sth .这个短语的意思是假装已经做过了某事,强调事情的一个完成的状态,侧重于假装的事情已经做好了。 举例:I pretend tohave seen nothing,but I cant.我假装自己没有看到任何东西,但是我做不到(侧重于一个完成时态,已经试图去假装没有看到)

she pretended to have finished the homeworkwhen she went out and played.当她出门玩的时候她假装自己已经完成了家庭作业。(假装做作业这个动作已经在出门玩之前做完了)(JasoOon的回答)以及怀陌的回答:When the teacher came in,he pretended to havefinished the homework.当老师进来的时候他假装自己已经完成家庭作业了,两者有异曲同工之妙。 3. pretendtobe doing sth 这个短语的意思是假装正在做某事,强调动作的一个进行时态。 举例:They pretend to be reading books when the teacher sneakingly stands at the back door.当老师偷偷地站在后门的时候他们假装正在读书(读书与老师站在后门都是过去进行时 态)(JasoOon的回答) Asmanypeople do,youoftenpretend to be doingwork when actuallyyou arejust wasting time online.像很多人一样,你经常假装正在工作,其实是在上网。 群主补充:昨天和今天已提交作业的同学,做得都很好,全部授予小红花。希望你们再接再厉,不要松懈哟。所以下周一出题者为所有已提交作业的同学或者你们选出的代表。

“的、地、得”的用法教案 教学目标: 1.能通过看视频知道“的、地、得”的用法区别。 2.能在小组合作中正确掌握“的、地、得”的用法。 3.能正确熟练地运用“的、地、得”。 教学重点:通过看视频知道“的、地、得”的用法区别。 教学难点:正确熟练地运用“的、地、得”。 教学过程: 一、导入(板书课题:“的、地、得”的用法“的、地、得”) 这三个字认识吧!虽然它们都有一个相同的读音de,但用法却不一样,可不能把他们用错了。究竟他们的用法有什么不同,我们来听听他们的故事吧! 二、看微视频,学习“的、地、得”的用法区别。 三、小结: 1.孩子们,刚才看了视频知道他们是谁吗?(白勺的,土也地,双人得。) (1)白勺的是个杂货铺老板,她的店里都有什么?(彩色的毛巾美味的汉堡结实的帐篷舒适的儿童车捕捉风的网会唱歌的小树开个没完的花朵优美动听的歌曲飘来飘去的云……)还可能有什么? 你们一定会发现,白勺的的用法有什么特点?(后面是名词。)板书:名词 (2)土也地是个运动男孩,他喜欢?(悠闲地散步欢快地跳舞兴奋地跳跃开心地捕蝴蝶看图书踢球骑自行洗澡吃冰淇淋……)他还可能喜欢干什么呢?你发现了吗?土也地的用法特点?(后面是动词。)板书:动词 (3)双人得呢?她是个总喜欢评价别人的小妹妹。(球踢得真棒舞跳得精彩长得好高呀……) 她可能还怎么评价别人?(歌唱得动听饭吃得很饱人长得漂亮)你们会发现,双人得的前面通常都是——动词。板书:动词 2.小结:所以,他们的用法也很简单,区别就在这里。 (白勺的用在名词前面;土也地用在动词前面;双人得用在动词后面。)你明白了吗? 四、我来考考你们,看哪一组完成得又对又快! 1.菜鸟级练习 2.老鸟级练习 3.大虾级练习 五、总结

介词at的基本用法: 一、at引导的时间短语通常可表示: 1.在几点几分,例如:at one o’clock(在一点钟) I usually make the bed at one o’clock.. 2.在用餐时间,例如:at lunchtime(在午餐时间) 3.在某个节日,例如:at Christmas 在圣诞节的时候 4.在某个年龄的时候,例如:at the age of 12。在12岁的时候 5.一天中的某段较短的时间,例如:at noon在中午at night在夜里 二、at也可引导地点短语,常用于小地点之前,例如: at the bus stop在汽车站at the butcher’s 在肉店里at school在学校里at home在家里 介词on的基本用法: 一、on可引导地点短语,表示“在…上面”,例如:on the table在桌子上 二、on也可引导时间短语,通常有以下用法: 1.用于“星期”和“月份”中的任何一天之前,例如:On Monday在星期一on April 1st. 2.用于某个“星期几”当天的某段时间,例如:on Monday morning在星期一上午 3.用于具体某一天之前,例如:on that day在那一天On my birthday在我的生日那天 On Christmas day在圣诞节那天 介词in的基本用法: 一、in可引导地点短语,常表示“在…里面”,例如:in the bag在袋子里 二、in引导的时间短于通常有以下用法: 1.在某个世纪,例如:in the 21st century在21世纪 2.在某一年,例如:in 1995在1995年 3.在某一个季节,例如:in spring在春季 4.在某一个月份,例如:in March在三月里 5.在某段时期,例如:in the holidays在假期里 6.在某个持续几天的节日里,例如:in Easter Week在复活周 7.在一天中的某段时间,例如:in the morning在上午(早晨)

介词“with”的用法 1、同, 与, 和, 跟 talk with a friend 与朋友谈话 learn farming with an old peasant 跟老农学习种田 fight [quarrel, argue] with sb. 跟某人打架 [争吵, 辩论] [说明表示动作的词, 表示伴随]随着, 和...同时 change with the temperature 随着温度而变化 increase with years 逐年增加 be up with the dawn 黎明即起 W-these words he left the room. 他说完这些话便离开了房间。2 2、表示使用的工具, 手段 defend the motherland with one s life 用生命保卫祖国 dig with a pick 用镐挖掘 cut meat with a knife 用刀割肉3

3、说明名词, 表示事物的附属部分或所具有的性质]具有; 带有; 加上; 包括...在内 tea with sugar 加糖的茶水 a country with a long history 历史悠久的国家4 4、表示一致]在...一边, 与...一致; 拥护, 有利于 vote with sb. 投票赞成某人 with的复合结构作独立主格,表示伴随情况时,既可用分词的独立结构,也可用with的复合结构: with +名词(代词)+现在分词/过去分词/形容词/副词/不定式/介词短语。例如: He stood there, his hand raised. = He stood there, with his hand raise.他举手着站在那儿。 典型例题 The murderer was brought in, with his hands ___ behind his back A. being tied B. having tied C. to be tied D. tied 答案D. with +名词(代词)+分词+介词短语结构。当分词表示伴随状况时,其主语常常用