很多人觉得FPGA难学,难点在于FPGA的硬件特性和FPGA之外的东西,如硬件编程思想,并行编程,时序分析等,本文就时序分析进行讲解,讲解时序分析的基础,内容主要为建立时间和保持时间的分析。并且举例简单说明DT6000S项目采用的时序分析.

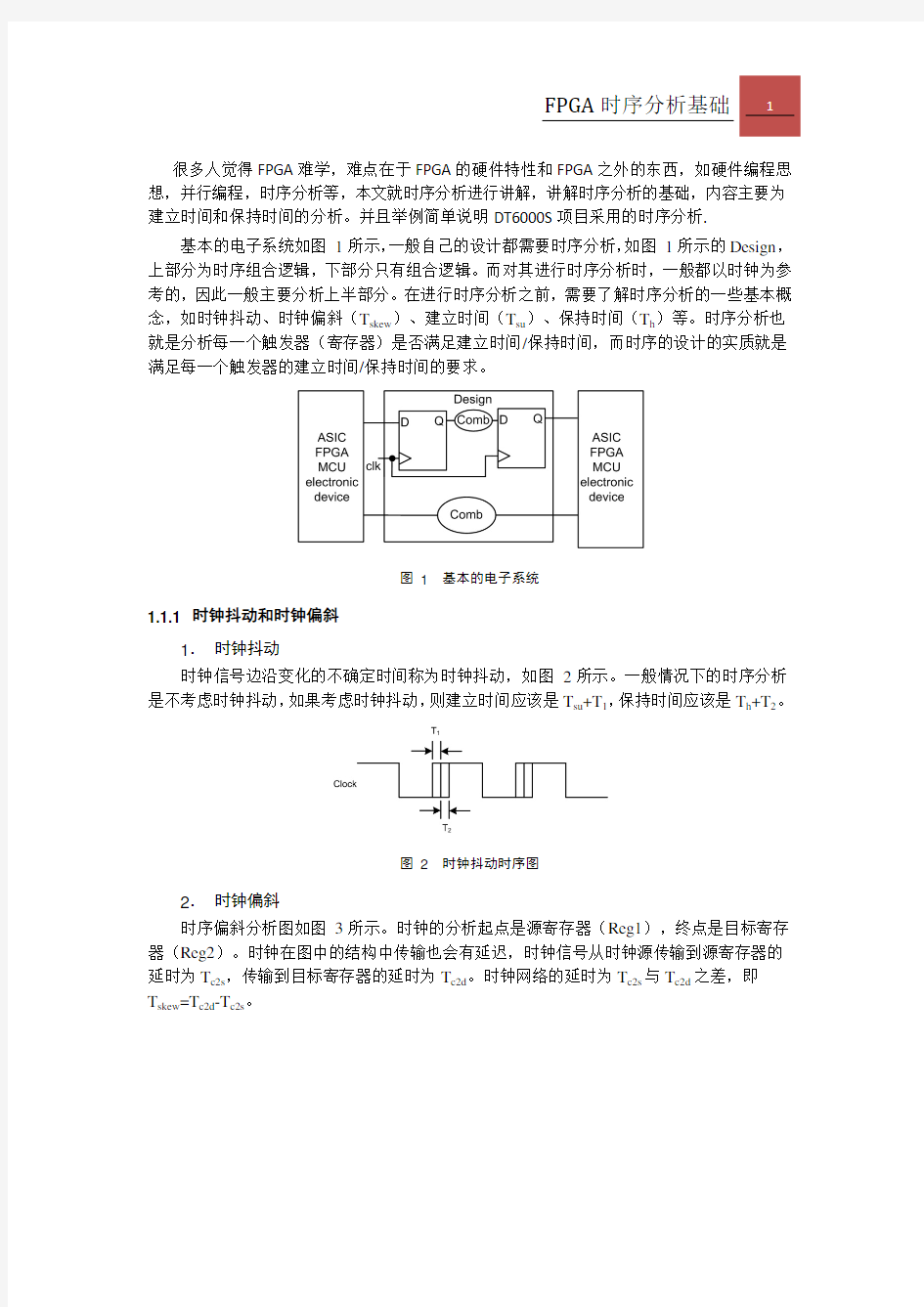

基本的电子系统如图1所示,一般自己的设计都需要时序分析,如图1所示的Design,上部分为时序组合逻辑,下部分只有组合逻辑。而对其进行时序分析时,一般都以时钟为参考的,因此一般主要分析上半部分。在进行时序分析之前,需要了解时序分析的一些基本概念,如时钟抖动、时钟偏斜(T skew)、建立时间(T su)、保持时间(T h)等。时序分析也就是分析每一个触发器(寄存器)是否满足建立时间/保持时间,而时序的设计的实质就是满足每一个触发器的建立时间/保持时间的要求。

图 1 基本的电子系统

1.1.1 时钟抖动和时钟偏斜

1.时钟抖动

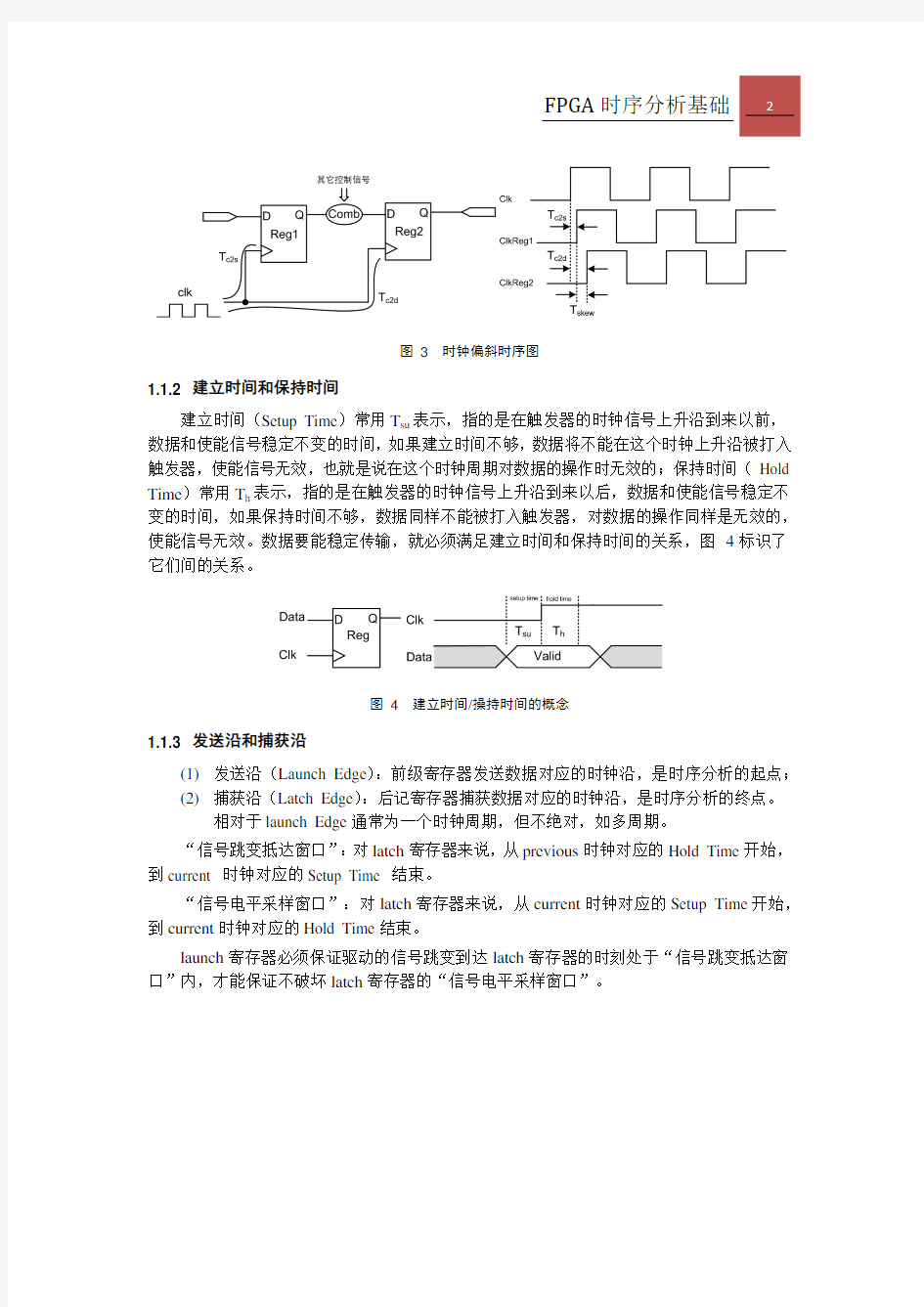

时钟信号边沿变化的不确定时间称为时钟抖动,如图2所示。一般情况下的时序分析是不考虑时钟抖动,如果考虑时钟抖动,则建立时间应该是T su+T1,保持时间应该是T h+T2。

图 2 时钟抖动时序图

2.时钟偏斜

时序偏斜分析图如图3所示。时钟的分析起点是源寄存器(Reg1),终点是目标寄存器(Reg2)。时钟在图中的结构中传输也会有延迟,时钟信号从时钟源传输到源寄存器的延时为T c2s,传输到目标寄存器的延时为T c2d。时钟网络的延时为T c2s与T c2d之差,即

T skew=T c2d-T c2s。

图 3 时钟偏斜时序图

1.1.2 建立时间和保持时间

建立时间(Setup Time)常用T su表示,指的是在触发器的时钟信号上升沿到来以前,数据和使能信号稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器,使能信号无效,也就是说在这个时钟周期对数据的操作时无效的;保持时间(Hold Time)常用T h表示,指的是在触发器的时钟信号上升沿到来以后,数据和使能信号稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器,对数据的操作同样是无效的,使能信号无效。数据要能稳定传输,就必须满足建立时间和保持时间的关系,图4标识了它们间的关系。

图 4 建立时间/操持时间的概念

1.1.3 发送沿和捕获沿

(1)发送沿(Launch Edge):前级寄存器发送数据对应的时钟沿,是时序分析的起点;

(2)捕获沿(Latch Edge):后记寄存器捕获数据对应的时钟沿,是时序分析的终点。

相对于launch Edge通常为一个时钟周期,但不绝对,如多周期。

“信号跳变抵达窗口”:对latch寄存器来说,从previous时钟对应的Hold Time开始,到current 时钟对应的Setup Time 结束。

“信号电平采样窗口”:对latch寄存器来说,从current时钟对应的Setup Time开始,到current时钟对应的Hold Time结束。

launch寄存器必须保证驱动的信号跳变到达latch寄存器的时刻处于“信号跳变抵达窗口”内,才能保证不破坏latch寄存器的“信号电平采样窗口”。

图 5 Launch Edge和Latch Edge

1.1.4 数据和时钟的时序分析

如图6所示,为分析建立时间/保持时间的基本电路图。T clk1为Reg1的时钟延时,T clk2为Reg2的时钟延时,T co为Reg1固有延时,T data为Reg1的到Reg2之间组合逻辑的延时,T su为Reg2的建立时间,T h为Reg2的保持时间,设时钟clk周期为T,这里分析数据的建立时间和保持时间。

图 6 基本电路图

1.建立时间的分析

如图7所示,建立时间的分析是以第一个launch Edge为基准,在Latch Edge查看结果。建立时间的裕量(T为时钟周期):

Setup Stack = (T+T clk2) – T su – (T clk1+T co+T data)

假设△T = T clk2-Tclk1,则:

Setup Stack = (T+ T) – T su – (T co+T data)

可见△T<0影响建立时间,使建立时间的要求更加苛刻。因此对于△T尽量避免,采用同步单时钟,并且尽量采用全局的时钟信号,这样△T几乎为0,,△T的影响几乎不存在,可以忽略不计。

如果建立时间的裕量Setup Stack小于0,则不满足建立时间,也就会产生不稳定态,并通过寄存器传输下去。

图 7 建立时间时序分析图

2.保持时间的分析

如图8所示,保持时间的分析是以第二个launch Edge为基准,在Latch Edge查看结果。保持时间的裕量:

Hold Stack = (T clk1+T co+T data) – T clk2 – T h

假设△T = T clk2-T clk1,则:

Hold Stack = (T co+T data) – △T – T h

可见△T>0影响保持时间,使保持时间的要求更加苛刻。。因此对于△T尽量避免,采用同步单时钟,并且尽量采用全局的时钟信号,这样△T几乎为0,,△T的影响几乎不存在,可以忽略不计。

如果保持时间的裕量Hold Stack小于0,则不满足保持时间,也就会产生不稳定态,并

通过寄存器传输下去。

图 8 保持时间时序分析图

1.1.5 DT6000S项目实例

DT6000S项目上有4路光以太网接口连接到FPGA,由FPGA进行实现MAC层和解码IEC61850的SV和GOOSE。以太网PHY通过MII接口和FPGA,因此FPGA与外部的接口有4路MII接口。项目初期是实现1路光以太网接口,并且验证功能正确之后,但是后期变成的4路光以太网时,总会存在1路光以太网通信不正常。经过分析得到是FPGA通MII接口和PHY的时序不满足。如图9所示为MII接口的时序图,时序不满足分为TX_CLK 和RX_CLK。

其一是PHY输出的TX_CLK和FPGA依据TX_CLK产生的TXD[3:0]&TX_EN延时大,主要延时为内部逻辑的延时,PCB延时小并且一致,导致PHY的TX_CLK的建立时间不满足,从而导致发送数据错误。

其二是PHY输出的RX_CLK和RXD[3:0]&RX_DV&RX_ER到FPGA内部同步触发器的延时之差太大,导致FPGA内部同步触发器的RX_CLK的建立时间不满足,从而导致接收数据错误。

因此FPGA在综合时需要添加约束,使之时序满足要求,约束的条件为TXD[3:0]和TX_EN的输出延时要少。RX_CLK和RXD[3:0]&RX_DV&RX_ER路径延时之差要小。添

加约束之后,4路MII接口的光以太网数据通信就正常了。

图 9 MII时序图

正文结语:(阐明消息所述意义,使读者对消息的理解、感受加深,得到启示。)本文阐述了时序分析基础,说明概念的同时进行了时序分析,通过时序分析理解建立时间和保持时间。也通过在DT6000S项目上的实例说明,时序分析的重要性。

底部广告:

TimeQuest快速入门 简介 本教程介绍用TimeQuest Analyzer进行时序约束和静态时序分析的必要步骤。所用示例文件在\qdesigns\fir_filter文件夹下。 TimeQuest约束步骤 下面的步骤描述了用TimeQuest对设计进行时序约束的步骤,每一步操作包含GUI和Command-line的操作方法。 第1步:在QuartusII中打开&建立工程 启动QuartusII软件,在\qdesigns\fir_filter文件夹下打开工程compile_fir_filter.qpf。 第2步:设置TimeQuest Analyzer 默认状态下,QuartusII使用Classic Timing Analyzer作为默认的时序分析工具。需要在QuatusII中进行如下设置将TimeQuest Analyzer设为当前工程的时序分析器。 在【Assignment】菜单下单击【Settings】,在【Category】列表中展开【Timing Analysis Processing】,选择【Use TimeQuest Analyzer during compilation】,然后点击【OK】即可。 第3步:进行初始的编译 在将时序约束应用到设计之前,需要为TimeQuest创建初始的数据。初始数据是通过post-map结果产生的。步骤如下: 在【Processing】菜单栏下,选择【Start】/【Start Analysis&Synthesis】。 通过运行【Analysis&Synthesis】产生post-map数据。 还可以用post-fit网表来产生初始数据。但是创建post-map数据所用时间更少,而且post-map数据对本设计示例工程来说已经够用。 第4步:启动TimeQuest Analyzer 为了创建并验证时序约束,需要启动TimeQuest Analyzer。在【Tools】菜单下,单击【TimeQuest Analyzer】启动TimeQuest Analyzer。 第5步:创建Post-Map时序网表 在指定时序要求前,需要首先创建一个时序网表。可以从post-map或post-fit 数据中创建时序网表(见第3步)。利用post-map数据创建时序网表的方法为:在【netlist】菜单下,单击【Create Timing Netlist】,在弹出的对话框中,选择【Input netlist type】下的【Post-Map】,单击【OK】。 不能通过【Task】面板下的【Create Timing Netlist】命令来创建post-map网表。在默认情况下,【Create Timing Netlist】需要post-fit数据。

校外IC后端实践报告 本教程通过对synopsys公司给lab进行培训,从verilog代码到版图整个流程(固然只是基本流程,由于真正一种大型设计不是那么简朴就完毕),此教程目就是为了让人们尽快理解数字IC设计大概流程,为后来学习建立一种基本。此教程只是本人摸索实验成果,并不代表内容都是对的,只是为了阐明大概流程,里面一定尚有诸多未完善并且有错误地方,我在此后学习当中会对其逐个完善和修正。 此后端流程大体涉及一下内容: 1.逻辑综合(工具DC 逻辑综合是干吗就不用解释了把?) 2.设计形式验证(工具formality) 形式验证就是功能验证,重要验证流程中各个阶段代码功能与否一致,涉及综合前RTL代码和综合后网表验证,由于如今IC设计规模越来越大,如果对门级网表进行动态仿真话,会耗费较长时间(规模大话甚至要数星期),这对于一种对时间规定严格(设计周期短)asic 设计来说是不可容忍,而形式验证只用几小时即可完毕一种大型验证。此外,由于版图后做了时钟树综合,时钟树插入意味着进入布图工具本来网表已经被修改了,因此有必要验证与本来网表是逻辑等价。 3.静态时序分析(STA),某种限度上来说,STA是ASIC设计中最重要环节,使用primetime 对整个设计布图前静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。 (PR后也需作signoff时序分析) 4.使用cadence公司SOCencounter对综合后网表进行自动布局布线(APR) 5.自动布局后来得到详细延时信息(sdf文献,由寄生RC和互联RC所构成)反标注到网 表,再做静态时序分析,与综合类似,静态时序分析是一种迭代过程,它与芯片布局布线联系非常紧密,这个操作普通是需要执行许多次才干满足时序需求,如果没违规,则进入下一步。 6.APR后门级功能仿真(如果需要)

建立时间和保持时间关系详解 图1 建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器; 保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。 如图1 。数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间。 个人理解: 1、建立时间(setup time)触发器在时钟沿到来之前,其数据的输入端的数据必须保持不变的时间;建立时间决定了该触发器之间的组合逻辑的最大延迟。 2、保持时间(hold time)触发器在时钟沿到来之后,其数据输入端的数据必须保持不变的时间;保持时间决定了该触发器之间的组合逻辑的最小延迟。 关于建立时间保持时间的考虑 华为题目:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。组合逻辑电路最大延迟为T2max,最小为T2min。问:触发器D2的建立时间T3和保持时间T4应满足什么条件? 分析: Tffpd:触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化并且稳定,也可以理解为触发器的输出延时。 Tcomb:触发器的输出经过组合逻辑所需要的时间,也就是题目中的组合逻辑延迟。 Tsetup:建立时间 Thold:保持时间 Tclk:时钟周期 建立时间容限:相当于保护时间,这里要求建立时间容限大于等于0。 保持时间容限:保持时间容限也要求大于等于0。

时序分析基础与时钟约束实例(1) 文中实例配套SF-CY3开发套件。更多内容请参考《SF-CY3 FPGA套件开发指南》。 何谓静态时序分析(STA,Static Timing Analysis)? 首先,设计者应该对FPGA内部的工作方式有一些认识。FPGA的内部结构其实就好比一块PCB板,FPGA的逻辑阵列就好比PCB板上的一些分立元器件。PCB通过导线将具有相关电气特性的信号相连接,FPGA也需要通过内部连线将相关的逻辑节点导通。PCB板上的信号通过任何一个元器件都会产生一定的延时,FPGA的信号通过逻辑门传输也会产生延时。PCB的信号走线有延时,FPGA的信号走线也有延时。这就带来了一系列问题,一个信号从FPGA的一端输入,经过一定的逻辑处理后从FPGA的另一端输出,这期间会产生多大的延时呢?有多个总线信号从FPGA的一端输入,这条总线的各个信号经过逻辑处理后从FPGA 的另一端输出,这条总线的各个信号的延时一致吗?之所以关心这些问题,是因为过长的延时或者一条总线多个信号传输时间的不一致,不仅会影响FPGA本身的性能,而且也会给FPGA之外的电路或者系统带来诸多问题。 言归正传吧,之所以引进静态时序分析的理论也正是基于上述的一些思考。它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分析。分析的最终结果当然是要求系统时序满足设计者提出的要求。 下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中找到了如图所示的一些可能的布局布线方式。那么,怎样的布局布线能够达到系统的要求呢?仔细分析一番,发现所有路径的延时可能为14ns、15ns、16ns、17ns、18ns,有两条路径能够满足要求,那么最后的布局布线就会选择满足要求的两条路径之一。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,即有约束才会有分析。若设计者不添加时序约束,那么时序分析就无从谈起。特权同学常常碰见一些初学者在遇到问题时不问青红皂白就认为是时序问题,实际上只有在添加了时序约束后,系统的时序问题才有可能暴露出来。 下面我们再来看一个例子,我们假设有4个输入信号,经过FPGA内部一些逻辑处理后输出。FPGA内部的布线资源有快有慢之分,好比国道和高速公路。通过高速通道所需要的路径延时假设为3ns-7ns,但只有两条可用;而通过慢速通道的路径延时则>10ns。

FPGA静态时序分析模型——寄存器到寄存器 1. 适用范围 本文档理论适用于Actel FPGA并且采用Libero软件进行静态时序分析(寄存器到寄存器)。 2. 应用背景 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。STA作为FPGA设计的主要验证手段之一,不需要设计者编写测试向量,由软件自动完成分析,验证时间大大缩短,测试覆盖率可达100%。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告。 进行静态时序分析,主要目的就是为了提高系统工作主频以及增加系统的稳定性。对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。通过附加约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。 3. 理论分析 3.1 静态时序分析的理论基础知识 在进行正确的时序分析前,我们必须具备基本的静态时序的基本知识点,不然看着编译器给出的时序分析报告犹如天书。如图3.1所示,为libero软件给出的寄存器到寄存器模型的时序分析报告的截取,接下来我们会弄清楚每个栏目的数据变量的含义,以及计算方法。 图3.1 libero静态时序分析报告 3.1.1 固定参数launch edge、latch edge、Tsu、Th、Tco概念

1. launch edge 时序分析起点(launch edge):第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点。 2. latch edge 时序分析终点(latch edge):数据锁存的时钟边沿,也是静态时序分析的终点。 3. Clock Setup Time (Tsu) 建立时间(Tsu):是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器。如图3.2所示: 图3.2 建立时间图解 4. Clock Hold Time (Th) 保持时间(Th):是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。保持时间示意图如图3.3所示: 图3.3 保持时间图解 5. Clock-to-Output Delay(tco) 数据输出延时(Tco):这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间

基本后端流程(漂流&雪拧) ----- 2010/7/3---2010/7/8 本教程将通过一个8*8的乘法器来进行一个从verilog代码到版图的整个流程(当然只是基本流程,因为真正一个大型的设计不是那么简单就完成的),此教程的目的就是为了让大家尽快了解数字IC设计的大概流程,为以后学习建立一个基础。此教程只是本人探索实验的结果,并不代表内容都是正确的,只是为了说明大概的流程,里面一定还有很多未完善并且有错误的地方,我在今后的学习当中会对其逐一完善和修正。 此后端流程大致包括一下内容: 1.逻辑综合(逻辑综合是干吗的就不用解释了把?) 2.设计的形式验证(工具formality) 形式验证就是功能验证,主要验证流程中的各个阶段的代码功能是否一致,包括综合前RTL代码和综合后网表的验证,因为如今IC设计的规模越来越大,如果对门级网表进行动态仿真的话,会花费较长的时间(规模大的话甚至要数星期),这对于一个对时间要求严格的asic设计来说是不可容忍的,而形式验证只用几小时即可完成一个大型的验证。另外,因为版图后做了时钟树综合,时钟树的插入意味着进入布图工具的原来的网表已经被修改了,所以有必要验证与原来的网表是否逻辑等价。 3.静态时序分析(STA),某种程度上来说,STA是ASIC设计中最重要的步骤,使用primetime对整个设 计布图前的静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。(PR后也需作signoff 的时序分析) 4.使用cadence公司的SOCencounter对综合后的网表进行自动布局布线(APR) 5.自动布局以后得到具体的延时信息(sdf文件,由寄生RC和互联RC所组成)反标注到网表,再做静 态时序分析,与综合类似,静态时序分析是一个迭代的过程,它与芯片布局布线的联系非常紧密,这个操作通常是需要执行许多次才能满足时序需求,如果没违规,则进入下一步。 6.APR后的门级功能仿真(如果需要) 7.进行DRC和LVS,如果通过,则进入下一步。 8.用abstract对此8*8乘法器进行抽取,产生一个lef文件,相当于一个hard macro。 9.将此macro作为一个模块在另外一个top设计中进行调用。 10.设计一个新的ASIC,第二次设计,我们需要添加PAD,因为没有PAD,就不是一个完整的芯片,具体 操作下面会说。 11.重复第4到7步

1. 适用范围 本文档理论适用于Actel FPGA并且采用Libero软件进行静态时序分析(寄存器到寄存器)。 2. 应用背景 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。STA作为FPGA设计的主要验证手段之一,不需要设计者编写测试向量,由软件自动完成分析,验证时间大大缩短,测试覆盖率可达100%。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告。 进行静态时序分析,主要目的就是为了提高系统工作主频以及增加系统的稳定性。对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。通过附加约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。 3. 理论分析 3.1 静态时序分析的理论基础知识 在进行正确的时序分析前,我们必须具备基本的静态时序的基本知识点,不然看着编译器给出的时序分析报告犹如天书。如图3.1所示,为libero软件给出的寄存器到寄存器模型的时序分析报告的截取,接下来我们会弄清楚每个栏目的数据变量的含义,以及计算方法。 图3.1 libero静态时序分析报告 3.1.1 固定参数launch edge、latch edge、Tsu、Th、Tco概念 1. launch edge 时序分析起点(launch edge):第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点。

2. latch edge 时序分析终点(latch edge):数据锁存的时钟边沿,也是静态时序分析的终点。 3. Clock Setup Time (Tsu) 建立时间(Tsu):是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器。如图3.2所示: 图3.2 建立时间图解 4. Clock Hold Time (Th) 保持时间(Th):是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。保持时间示意图如图3.3所示: 图3.3 保持时间图解 5. Clock-to-Output Delay(tco) 数据输出延时(Tco):这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。 3.1.2 Clock skew 时钟偏斜(clock skew):是指一个时钟源到达两个不同寄存器时钟端的时间偏移,如图3.4所示:

1.在quartus中对设计进行时序分析 2.1TimeQuest 工具 Quartus? II TimeQuest Timing Analyzer是一个功能强大的ASIC型时序分析工具,能够以工业标准方法论来约束,分析和报告用户设计中所有逻辑的时序性能。这个工具是一个严格的静态工具,使用时不需要搭建硬件环境及进行调试。本节将介绍如何使用Quartus II TimeQuest Timing Analyzer工具的图形化功能来约束,分析及报告设计中的时序结果。 使用这个工具,我们要指定初始时序信息,包括时钟,时序例外以及信号传输中的到达和要求的时间。我们通过后缀名为sdc(Synopsys Design Constraints)的文件来指定时序要求,然后The Quartus II Fitter将优化逻辑布局等来满足我们的时序要求。 在时序分析过程中,Quartus II TimeQuest Timing Analyzer分析设计中的每一条时序路径,计算每条路径的延迟,检查是否存在时序违例,并且报告时序结果。一旦发现时序违例,可以精确定位到违例路径的时序细节,然后用户约束它以纠正违例。如果时序分析没有报告违例,那么恭喜你,在这个器件中的逻辑行为将与你的设计意图一致。 使用TimeQuest分析设计时序的一般步骤为: 图使用TimeQuest分析设计时序的一般步骤第一次编译时我们需要得到没有设置约束的时序结果,有助于我们给设计添加约束。第二次编译的时序需要把包含指定时序要求的文件(后缀为sdc 的文件)添加到工程文件中执行编译,这样工具就能够按照我们的时序要求来进行映射了。 2.2timequest快速入门示例 下面我们按照altera公司所给的timequest快速入门教程示例来讲解该时序分析工具的大致用法。使用的工具是目前使用最广泛的quartusII9.1版本

静态时序分析中路径延时的计算 静态时序分析工具一般将电路网表看成一个拓扑图,图中的节点(node)代表电路中的引脚(pin)。节点之间的边(edge)表示时序弧(timing arc),有两种: # 连线延时(net delay)---驱动引脚(drive pin)和扇出(fanout)之间的连接 # 单元延时(cell delay)---输入引脚(input pin)和输出引脚(output pin)之间的连接 延时计算就是计算每条时序弧的值,可能是单元延时也可能是连线延时。通过累计这些延时可以计算时序路径(timing delay)的上升延时(rise delay)或下降延时(fall delay)。 正函数时序弧(positive unate timing arc): 将上升延时和上升延时相加,下降延时和下降延时相加。例如一个AND门单元延时和连线延时。 负函数时序弧(negative unate timing arc): 将新得到的上升延时和原来的下降延时相加,而新得到的下降延时和原来的上升延时相加。例如NAND门。 非函数时序弧(non-unate timing arc): 将原来的延时和新得到的最差情况延时(worst-case delay)相加。非函数时序弧出现在不能从输入量的变化预测输出端逻辑值变化的地方,例如XOR门。 下图展示了一个电路逻辑网络是如何转化成一张时序图的: 非线性延时模型(nonlinear delay model): 非线性模型是供应商以查表(lookup table)形式在工艺库中提供的延时信息,它和时序分析计算有着紧密的联系。 总的延时包含了单元延时和连线延时:

静态时序分析(Static Timing Analysis)基础及应用 ◎陈麒旭 前言 在制程进入深次微米世代之后,芯片(IC)设计的高复杂度及系统单芯片(SOC)设计方式兴起。此一趋势使得如何确保IC质量成为今日所有设计从业人员不得不面临之重大课题。静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者的时序环境下正常工作,对确保IC质量之课题,提供一个不错的解决方案。然而,对于许多IC设计者而言,STA是个既熟悉却又陌生的名词。本文将力求以简单叙述及图例说明的方式,对STA的基础概念及其在IC设计流程中的应用做详尽的介绍。 什么是STA? STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。以分析的方式区分,可分为Path-Based及Block-Based两种。 先来看看Path-Based这种分析方式。如图一所示,信号从A点及B点输入,经由4个逻辑闸组成的电路到达输出Y点。套用的Timing Model标示在各逻辑闸上,对于所有输入端到输出端都可以找到相对应的延迟时间。而使用者给定的Timing Constraint为: 1.信号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。 2.信号B到达电路输入端的时间点为5(AT=5)。 3.信号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

现在我们针对P1及P2两条路径(Path)来做分析。P1的起始点为A,信号到达时间点为2。经过第1个逻辑闸之后,由于此闸有2单位的延迟时间,所以信号到达此闸输出的时间点为4(2+2)。依此类推,信号经由P1到达输出Y的时间点为7(2+2+3)。在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。 按照同样的方式可以得到信号经由路径B到达输出Y的时间点为11(5+1+3+2),照样和上述第三项Timing Constraint比对,我们可以得知对P2这个路径而言,Timing 是不满足使用者要求的。 对图一的设计而言,总共有6个信号路径。对于采用Path-Based分析方式的STA 软件来说,它会对这6个信号路径作逐一的分析,然后记录下结果。IC设计者藉由检视其分析报告的方式来判断所设计的电路是否符合给定的Timing Constraint。由于最常用来做静态时序分析验证核可(STA Signoff)的EDA软件PrimeTime?采用Path-Based的分析方式,所以本文将以Path-Based的分析方式介绍为主。 再来看看Block-Based的分析方式。此时时序信息(Timing Information)的储存不再是以路径为单位,而是以电路节点(Node)为单位。由Timing Constraint我们仅能得知A节点的AT为2,B节点的AT为5以及Y节点的RT为10。Block-Based的分析方式会找出每个节点的AT和RT,然后比对这两个数值。当RT的值大于AT时表示信号比Timing Constrain中要求的时间还早到达,如此则Timing是满足的,反之则不满足。 STA资料准备 在做STA之前,我们必须对其准备工作有充分的了解。STA所需的资料如图三所示,以下我们分项说明。其中Design Data部分,由于Block Model和STA软件相关性太高,我们不在此加以说明,请直接参阅您STA软件的使用手册。

1引言 在集成电路设计过程中,模拟方法是应用最多的验证时序正确与否的手段,然而,模拟方法在微系统芯片(SoC)时代正面临严竣的挑战。传统的逻辑模拟方法虽然比较快,但需要输入向量作为激励,给使用带来很多不便;更为严重的是其精度不够高,不能处理SoC时代越来越严重的互连线的耦合电容、电感效应。电路模拟方法虽然能非常精确地计算SoC时代的各种效应,但其速度太慢,容量也太小。静态时序分析技术通过提取整个电路的所有时序路径,计算信号沿(上升沿或下降沿)在传播过程的延时,然后检查在最坏情况下电路中是否存在建立时间和保持时间不满足要求的器件,从而确认被验证的电路是否存在时序问题。它们又分别通过对最大路径延迟和最小路径延迟的分析得到。静态时序分析不需要输入向量、运行速度快、占用内存少,因而成为SoC时代最主要的时序验证手段。延时计算和最长/最短路径分析是静态时序分析的关键。由于互连线结构 [1]对门延时的影响非常大,必须在门延时模型中充分考虑这一因素才能确保静态分析结果的正确性。 本文提出新的Π模型方法,结合了门的等效电容[3]来计算门的延时,我们的方法结合门的互连线负载的拓扑结构和门负载三阶矩求解的方法,采用[4]中提出的等效电容的求解公式,求出门延时计算模型,相比上述两种方法,在静态时序分析中更为合理。 2新的门延时模型 2.1 新的门延时模型 在[4]中,作者提出了利用Π型的RC模型来近似门的互连线输出负载,同时考虑了负载的屏蔽效应。用该模型等价地计算出门输出驱动点导纳函数前三阶系数。 图1中Y(s)表示准确的RC树的驱动点导纳函数,在s=0的Taylor展开式表示如下:

将门的输出的RC树的互连线负载等效负载为Π模型,如图2。 通过Π模型得到的门输出驱动点导纳函数和Y (s)的前三项对比得出: 尽管以往模型能够很好地表示等效的输出驱动点导纳函数,但是利用等效电容计算的门延时结果并不理想,所以我们提出了新的模型。模型中电容的值也采用门输出驱动点导纳函数和 RC树的驱动点导纳函数前三阶近似相等原理[4] 推出来,设该驱动点导纳函数为Yπ的Taylor展开式: 考虑到互连线金属电阻的屏蔽效应以及互连线的分布特性,对于模型中的电阻R1而言,如图3所示,需要求RC树的等效电阻,采用的方法是,将分支中的接地电容去掉,而保留串联的电阻,这时电路中的电阻连接主要以节点之间的串并联的形式出现,则等效电阻 Req, 在[4]中,我们可以看到R1 一般取12/25Req,所以我们新的模型,如图4:

摘要: 本文介绍了数字集成电路设计中静态时序分析(Static Timing Analysis)和形式验证(Formal Verification)的一般方法和流程。这两项技术提高了时序分析和验证的速度,在一定程度上缩短了数字电路设计的周期。本文使用Synopsys 公司的PrimeTime进行静态时序分析,用Formality进行形式验证。由于它们都是基于Tcl(Tool Command Language)的工具,本文对Tcl也作了简单的介绍。 关键词: 静态时序分析形式验证 PrimeTime Formality Tcl

目录 第一章绪论 (1) 1.1 静态时序分析 1.2 时序验证技术 第二章PrimeTime简介 (3) 2.1 PrimeTime的特点和功能 2.2 PrimeTime进行时序分析的流程 2.3 静态时序分析中所使用的例子 2.4 PrimeTime的用户界面 第三章Tcl与pt_shell的使用 (6) 3.1 Tcl中的变量 3.2 命令的嵌套 3.3 文本的引用 3.4 PrimeTime中的对象 3.4.1 对象的概念 3.4.2 在PrimeTime中使用对象 3.4.3 针对collection的操作 3.5 属性 3.6 查看命令 第四章静态时序分析前的准备工作 (12) 4.1 编译时序模型 4.1.1 编译Stamp Model 4.1.2 编译快速时序模型 4.2 设置查找路径和链接路径 4.3 读入设计文件 4.4 链接 4.5 设置操作条件和线上负载 4.6 设置基本的时序约束 4.6.1 对有关时钟的参数进行设置 4.6.2 设置时钟-门校验 4.6.3 查看对该设计所作的设置 4.7 检查所设置的约束以及该设计的结构 第五章静态时序分析 (18) 5.1 设置端口延迟并检验时序 5.2 保存以上的设置 5.3 基本分析 5.4 生成path timing report 5.5 设置时序中的例外 5.6 再次进行分析 第六章 Formality简介 (22)

第三章FPGA开发基础 一.FPGA开发方法 1)原理图设计 1.元件和()都是元件库中的结构单元。() a)宏 b)Silces c)CLB d)IOB 2.()有固定映射和相对布局。() a)相关布局宏 b)IP CORE c)软宏 d)HDL代码 3.请问下面哪一项不是Xilinx FPGA的主要组成部分.() A)可编程输入输出单元 B)基本可编程逻辑单元 C)嵌入式块RAM D)查找表 4.请问下列哪一项属于Xilinx FPGA的芯片。() A)Stratix B)Spartan C)APEX D)MAX 5.下面有关Xilinx FPGA Spartan芯片说法错误的是。() A)主要面向低成本的中低端应用 B)采用了先进的45nm制造技术 C)Spartan-3E内有专用乘法器 D)Spartan-3E内有专用块RAM资源 6.下列说法正确的是。() A)从IP核的提供方式上,可以分为软核,硬核和固核。 B)Isimulator属于ISE自带的仿真工具,其功能比ModelSim更加强大。 C)Isimulator的默认仿真时间为10us。 D)不能通过FPGA Editor在目标器件上增加探针来监测信号状态。 7.下列说法错误的是。() A)适当的使用全局时钟约束可以提高系统的性能。 B)静态时序分析可以对综合后的HDL代码进行关键路径分析。 C)对HDL代码进行综合时,XST不会对代码进行综合优化,该过程由后续 floorplaner软件进行。 D)可以通过使用PACE对FPGA的设计布局进行改变。 8.现在市场主流的Xilinx FPGA中的LUT是几输入的?() A)3 B)4

入门:FPGA时序分析基础与时钟约束实例 2013-07-16 何谓静态时序分析(STA,Static Timing Analysis)? 首先,设计者应该对FPGA内部的工作方式有一些认识。FPGA的内部结构其实就好比一块PCB 板,FPGA的逻辑阵列就好比PCB板上的一些分立元器件。PCB通过导线将具有相关电气特性的信号相连接,FPGA也需要通过内部连线将相关的逻辑节点导通。PCB板上的信号通过任何一个元器件都会产生一定的延时,FPGA的信号通过逻辑门传输也会产生延时。PCB的信号走线有延时,FPGA的信号走线也有延时。这就带来了一系列问题,一个信号从FPGA的一端输入,经过一定的逻辑处理后从FPGA的另一端输出,这期间会产生多大的延时呢?有多个总线信号从FPGA的一端输入,这条总线的各个信号经过逻辑处理后从FPGA的另一端输出,这条总线的各个信号的延时一致吗?之所以关心这些问题,是因为过长的延时或者一条总线多个信号传输时间的不一致,不仅会影响FPGA本身的性能,而且也会给FPGA之外的电路或者系统带来诸多问题。 言归正传吧,之所以引进静态时序分析的理论也正是基于上述的一些思考。它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分析。分析的最终结果当然是要求系统时序满足设计者提出的要求。 下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中找到了如图所示的一些可能的布局布线方式。那么,怎样的布局布线能够达到系统的要求呢?仔细分析一番,发现所有路径的延时可能为14ns、15ns、16ns、17ns、18ns,有两条路径能够满足要求,那么最后的布局布线就会选择满足要求的两条路径之一。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,即有约束才会有分析。若设计者不添加时序约束,那么时序分析就无从谈起。特权同学常常碰见一些初学者在遇到问题时不问青红皂白就认为是时序问题,实际上只有在添加了时序约束后,系统的时序问题才有可能暴露出来。 下面我们再来看一个例子,我们假设有4个输入信号,经过FPGA内部一些逻辑处理后输出。FPGA内部的布线资源有快有慢之分,好比国道和高速公路。通过高速通道所需要的路径延时假设为3ns-7ns,但只有两条可用;而通过慢速通道的路径延时则>10ns。

第七章 QUARTUS II 入门指南7.1 QUARTUS II软件简介 7.2 QUARTUS II基本设计流程 7.3 原理图输入设计方法 7.4 嵌入式逻辑分析仪SignalTap II的使用 7.5 宏功能模块的应用

7.1 QUARTUS II软件简介 Quartus II是Altera公司推出的CPLD/FPGA开发工具,Quartus II提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;芯片(电路)平面布局连线编辑;LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块。 7.1.1 QUARTUS II基本特点 功能强大的逻辑综合工具; 完备的电路功能仿真与时序逻辑仿真工具; 定时/时序分析与关键路径延时分析; 可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析; 支持软件源文件的添加和创建,并将它们链接起来生成编程文件; 使用组合编译方式可一次完成整体设计流程; 自动定位编译错误; 高效的期间编程与验证工具; 可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件; 能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件。 7.1.2 QUARTUS II系统安装 1、QUARTUS II安装 Quartus II 系统要求较高的系统配置,配置过低将使得编译过程十分缓慢。对于安装Quartus II 7.2版本的系统必须满足以下最低要求: z硬件:运行速度为866MHz或更快Pentium III 以上计算机,系统内存容量大于256M。 z操作系统:Microsoft Windows 2000或Microsoft Windows XP。 安装QuartusII 之前建议浏览一下安装文件夹下的帮助文件及注意事项。实际安装过程比较简单:z运行Install.exe; z选择Install Quartus II Software,以后全部“Next”; z Finish 结束。

FPGA学习步骤,我的体会 FPGA在目前应用领域非常,在目前的单板设计里面,几乎都可以看到它的身影。从简单的逻辑组合,到高端的图像、通信协议处理,从单片逻辑到复杂的ASIC原型验证,从小家电到航天器,都可以看到FPGA应用,它的优点在这里无庸赘述。从个人实用角度看,对于学生,掌握FPGA可以找到一份很好的工作,对于有经验的工作人员,使用fgpa可以让设计变得非常有灵活性。掌握了fpga的设计,单板硬件设计就非常容易(不是系统设计),特别是上大学时如同天书的逻辑时序图,看起来就非常亲切。但fpga的入门却有一定难度,因为它不像软件设计,只要有一台计算机,几乎就可以完成所有的设计。fpga的设计与硬件直接相关,需要实实在在的调试仪器,譬如示波器等。这些硬件设备一般比较昂贵,这就造成一定的入门门槛,新人在入门时遇到一点问题或者困难,由于没有调试设备,无法定位问题,最后可能就会放弃。其实这时如果有人稍微指点一下,这个门槛很 容易就过去。 我用FPGA做设计很多年了,远达不到精通的境界,只是熟悉使用,在这里把我对fpga的学习步骤理解写出来,仅是作为一个参考,不对的地方,欢迎大家讨 论和指正。 1、工欲善其事,必先利其器。

计算机必不可少。目前FPGA应用较多的是Altera 和xilinx这两个公司,可以选择安装quartusII或者ISE 软件。这是必备的软件环境。 硬件环境还需要下载器、目标板。虽然有人说没有下载器和目标板也可学习fpga,但那总是纸上谈兵。这就像谈女朋友,总是嘴上说说,通个电话,连个手都没牵,能说人家是你朋友?虽说搭建硬件环境需要花费,但想想,硬件环境至多几百元钱,你要真的掌握FPGA的设计,起薪比别人都不止高出这么多。这点花费算什么? 2、熟悉verilog语言或者vhdl语言,熟练使用 quartusII或者ISE软件。 VHDL和verilog各有优点,选择一个,建议选择verilog。熟练使用设计软件,知道怎样编译、仿真、下载 等过程。 起步阶段不希望报一些培训班,除非你有钱,或者运气好,碰到一个水平高、又想把自己的经验和别人共享的培训老师,不然的话,培训完后总会感觉自己是一个冤大头。入门阶段可以在利用网络资源完成。 3、设计一个小代码,下载到目标板看看结果 此时可以设计一个最简答的程序,譬如点灯。如

第六章门级静态时序分析 PrimeTime 一、PrimeTime简介 PrimeTime是Synopsys的一个单点的全芯片、门级静态时序分析器。它能分析大规模、同步、数字ASICS的时序。PrimeTime工作在设计的门级层次,并且和Synopsys 其它工具整合得很紧密。 基本特点和功能: 时序检查方面: 建立和保持时序的检查(Setup and hold checks) 重新覆盖和去除检查(Recovery and removal checks) 时钟脉冲宽度检查(Clock pulse width checks) 时钟门锁检查(Clock-gating checks) 设计检查方面: 没有时钟端的寄存器 没有时序约束的结束点(endpoint) 主从时钟分离(Master-slave clock separation) 有多哥时钟的寄存器 对层次敏感的时钟(Level-sensitive clocking) 组合电路的反馈环(Combinational feedback loops) 设计规则检查,包括最大电容(maximum capacitance)、最大传输时间(maximum transition)和最大扇出(maximum fanout) PrimeTime 时序分析流程和方法: 在时序分析之前需要做的步骤: 1、建立设计环境 -建立搜索路径(search path)和链接路径(link path) -读入设计和库 -链接顶层设计 -建立运作条件、连线负载模型、端口负载、驱动和传输时间 2、说明时序声明(约束) -定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency) -说明输入、输出端口的延时 3、说明时序例外情况(timing exceptions) -多周期路径(multicycle paths) -不合法路径(false paths) -说明最大和最小延时、路径分割(path segmentation)和失效弧(disabled arcs) 4、进行分析和生成报告 -检查时序 -生成约束报告 -生成路径时序报告

基本后端流程(漂流&雪拧) 2010/7/32010/7/8 本教程将通过一个8*8的乘法器来进行一个从代码到版图的整个流程(当然只是基本流程,因为真正一个大型的设计不是那么简单就完成的),此教程的目的就是为了让大家尽快了解数字设计的大概流程,为以后学习建立一个基础。此教程只是本人探索实验的结果,并不代表内容都是正确的,只是为了说明大概的流程,里面一定还有很多未完善并且有错误的地方,我在今后的学习当中会对其逐一完善和修正。 此后端流程大致包括以下内容: 1.逻辑综合(逻辑综合是干吗的就不用解释了把?) 2.设计的形式验证(工具) 形式验证就是功能验证,主要验证流程中的各个阶段的代码功能是否一致,包括综合前代码和综合后网表的验证,因为如今设计的规模越来越大,如果对门级网表进行动态仿真的话,会花费较长的时间(规模大的话甚至要数星期),这对于一个对时间要求严格(设计周期短)的设计来说是不可容忍的,而形式验证只用几小时即可完成一个大型的验证。另外,因为版图后做了时钟树综合,时钟树的插入意味着进入布图工具的原来的网表已经被修改了,所以有必要验证与原来的网表是逻辑等价的。 3.静态时序分析(),某种程度上来说,是设计中最重要的步骤,使用对整个设计布图前 的静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。(后也需作的时序分析) 4.使用公司的对综合后的网表进行自动布局布线() 5.自动布局以后得到具体的延时信息(文件,由寄生和互联所组成)反标注到网表,再做 静态时序分析,与综合类似,静态时序分析是一个迭代的过程,它与芯片布局布线的联系非常紧密,这个操作通常是需要执行许多次才能满足时序需求,如果没违规,则进入下一步。 6.后的门级功能仿真(如果需要) 7.进行和,如果通过,则进入下一步。 8.用对此8*8乘法器进行抽取,产生一个文件,相当于一个。 9.将此作为一个模块在另外一个设计中进行调用。 10.设计一个新的,第二次设计,我们需要添加,因为没有,就不是一个完整的芯片,具体操 作下面会说。 11.重复第4到7步

Static Timing Analyzer Using PrimeTime Dec 23 2007 Presented by zhao icdesign_zhao@https://www.doczj.com/doc/1813296119.html,

Agenda )Basic Flow Advanced Analysis Summary Example

STA instruction Static timing analysis concept ?Verifies timing (setup, hold …) ?Is exhaustive ?Uses formal, mathematical techniques instead of vectors ?Does not use dynamic logic simulation STA : Easier, faster debugging of your design timing

Comprehensive Timing Checks Many types of timing and design rule checks ?Timing checks can be delay calculated or SDF annotated ?Setup and hold check ?Design rule checks consistent with DC, PC, Astro

Basic Timing Analysis Flow Using PrimeTime Setup Design Environment ?Search path, link path ?Read designs, libraries, then link ?Read sdf and set operation condition, environment setting Specify Timing Assertions ?Clock period/waveform/uncertainty/latency ?Input/output delays Specify Timing Exceptions ?Multi-cycle paths and False paths ?Min/max delays, segmentation, disabled arcs Perform Analysis, Create Reports ?Check timing ?Timing reports and constraint reports ?Bottleneck and coverage analysis reports