CD4053引脚图及功能表

- 格式:doc

- 大小:69.50 KB

- 文档页数:2

CC4053------三2选1模拟开关简要说明:CC4053 是三2通道数字控制模拟开关,有三个独立的数字控制输入端1C~3C和INH输入,具有低导通阻抗和很低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰-峰值至20V的模拟信号。

例如,若VDD=+5V,VSS=0,VEE=-13.5V,则0~5V的数字信号可控制-13.5~4.5V的模拟信号。

这些开关电路在整个VDD-VSS和VDD-VEE电源范围内具有极低的静态功耗,与控制信号的逻辑状态无关。

当INH输入端=“1”时,所有的通道截止。

二位二进制信号选通4通道中的一通道,可连接该输入端至输出。

CC4053提供了16引线多层陶瓷双列直插(D)、熔封陶瓷双列直插(J)、塑料双列直插(P)和陶瓷片状载体(C)4种封装形式。

推荐工作条件:电源电压范围…………3V~15V输入电压范围…………0V~V DD工作温度范围M类…………-55℃~125℃E类………….-40℃~85℃极限值:电源电压…...-0.5V~18V输入电压……-0.5V~V DD+0.5V输入电流…………….±10mA储存温度…………-65℃~150℃引出端符号:1C~3C 控制端I0/O0~I1/O1 输入输出端INH 禁止端O/I 公共输出/输入端V DD正电源V EE模拟信号地Vss 数字信号地逻辑符号:引出端排列(俯视):逻辑表达式:t R =t F =20nS;C L =50pF t PLH t PHL 传输延迟时间(导通或截止) (最大)A->I/O A->O /I -0 0 0 -50 0 0 05.0 10.015.05.0-720 320 240 450 -nSt R =t F =20nS;C L =50pFRL=10k Ω t PLH t PHL 传输延迟时间(导通) (最大)INH->I/O INH->O/I-0 0 0 -100 0 0 0 5.0 10.015.05.0 - 720 320 240 400- nS控制部分(C、INH)t R =t F =20nS;C L =50pFRL=300Ω t PLHt PHL 传输延迟时间(关态) (最大)INH->I/O INH->O/I-0 0 0 -100 0 0 05.0 10.015.05.0-450 210 160 300 - nSC I 输入电容(最大) C 、INH --7.5- pF*峰-峰电压对称值为(V DD-V EE)/2 **两通道的末端逻辑图:。

CD4051 CD4052 CD4053中文资料PDF 引脚功能CD4051/CC4051是单8通道数字控制模拟电子开关,有三个二进控制输入端A、B、C和I NH输入,具有低导通阻抗和很低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰值至2 0V的模拟信号。

例如,若VDD=+5V,VSS=0,VEE=-13.5V,则0~5V的数字信号可控制-13.5~4.5V的模拟信号。

这些开关电路在整个VDD-VSS和VDD-VEE电源范围内具有极低的静态功耗,与控制信号的逻辑状态无关。

当INH输入端=“1”时,所有的通道截止。

三位二进制信号选通8通道中的一通道,可连接该输入端至输出。

CD4052/CC4052是一个差分4通道数字控制模拟开关,有A、B两个二进制控制输入端和INH输入,具有低导通阻抗和很低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰峰值至20V的模拟信号。

例如,若V DD=+5V,VSS=0,VEE=-13.5V,则0~5V的数字信号可控制-13.5~4.5V的模拟信号,这些开关电路在整个VDD-VSS和VDD-VEE电源范围内具有极低的静态功耗,与控制信号的逻辑状态无关,当INH输入端=“1”时,所有通道截止。

二位二进制输入信号选通4对通道中的一通道,可连接该输入至输出。

CD4053/CC4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。

例如若VDD=+5,VSS=0,VEE=-13.5V,则0~5V的数字信号可控制-13.5~4.5V的模拟信号。

这些开关电路在整个VDD-VSS和VDD-VEE电源范围内具有极低的静态功耗,与控制信号的逻辑状态无关。

当INH输入端=“1”时,所有通道截止。

控制输入为高电平时,“0”通道被选,反之,“1”通道被选。

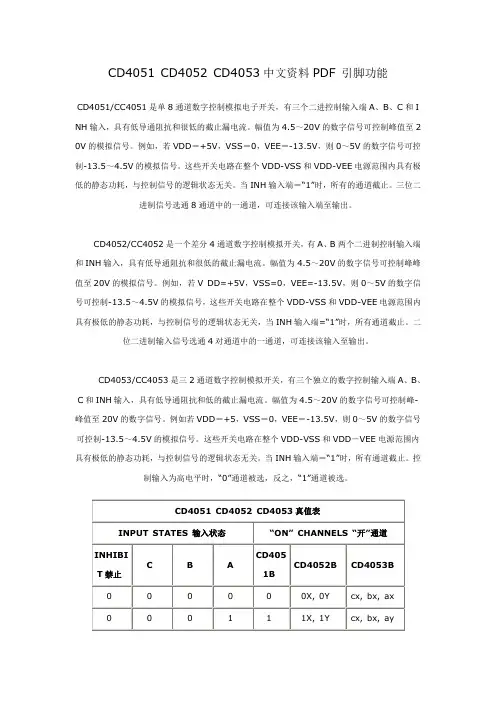

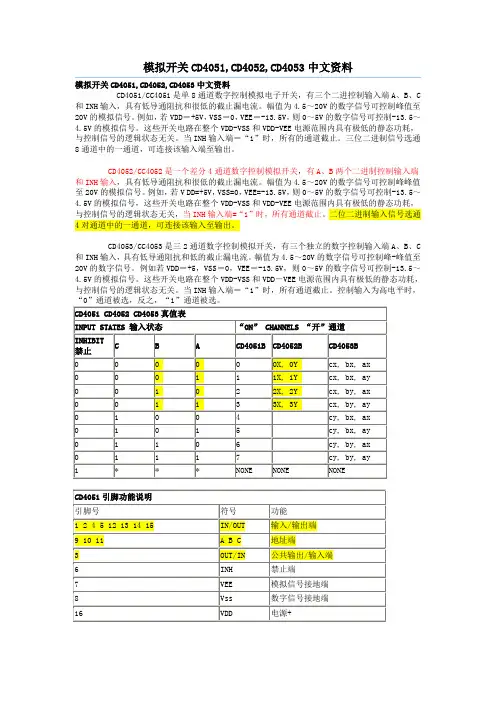

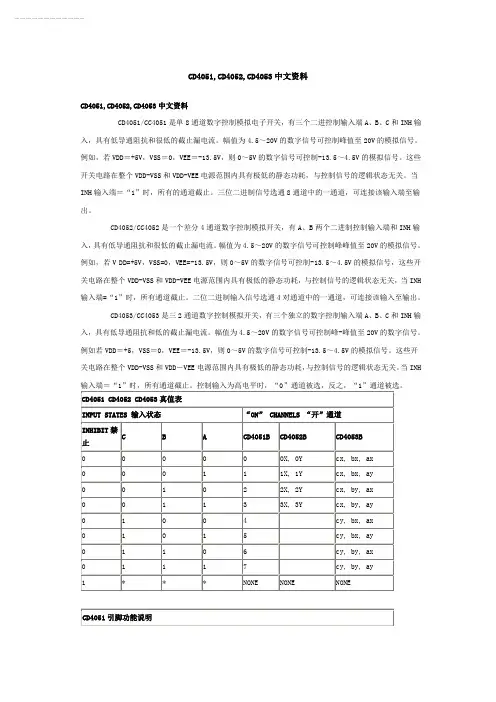

CD4051引脚图CD4052引脚图CD4053引脚图CD4051逻辑图CD4052逻辑图CD4053逻辑图切换时间波形图Absolute Maximum Ratings 绝对最大额定值:Recommended Operating Conditions 建议操作条件:DC Electrical Characteristics 直流电气特性:DC Electrical Characteristics 直流电气特性:AC Electrical Characteristics 交流电气特性:相关下载:cd4051中文资料,。

目录摘要 (2)一、总体论述 (2)1.1设计任务 (3)1.2输入要求 (3)1.3输出要求 (3)1.4性能指标 (3)1.5理论电路功能 (3)1.6实际电路功能 (3)二、方案选择 (3)三、各单元电路设计 (3)3.1分频器 (4)3.2选频电路 (5)3.3射极跟随器 (6)3.4数字键控制开关 (7)四、总电路图及仿真波形 (8)五、运行描述 (10)六、制作调试过程 (10)七、器件清单 (11)八、设计总结 (11)九、参考文献 (12)摘要本设计主要是采用Proteus 来实现2FSK调制,并绘制出解调前后的时域波形。

用Proteus 实现2FSK仿真,可以为硬件电路实现提供理论依据。

通过仿真展示了2FSK实现的设计思路及具体过程,并更充分地了解其调制与解调的过程。

关键字:Proteus 2FSK 仿真一、总体论述1.1、设计任务使用proteus仿真软件进行2FSK调制电路的仿真,熟悉2FSK调制电路的原理,其中有分频器、滤波器、射极跟随器的设计,并在此基础上做出实物1.2、输入要求在输入+5V的情况下,输入CLK和AK信号。

1.3、输出要求在输入+5V的情况下,输入CLK和AK信号,CLK信号在通过分频器后形成两个不同频率的信号,通过开关选择电路输出这两个不同的独立的频率,在每个码元期间输出这两个频率之一,形成疏密相间的正弦波。

1.4、性能指标1.5、理论电路的功能在输入+5V的情况下,输入CLK和AK信号,输出两个不同的独立的频率,在每个码元期间输出这两个频率之一,形成疏密相间的正弦波。

1.6、实际电路的功能在输入+5V的情况下,输入CLK和AK信号,输出两个不同的独立的频率,在每个码元期间输出这两个频率之一,形成疏密相间的正弦波,但波形有所失真。

二、方案选择2FSK信号的产生方法主要有两种。

第一种是用二进制基带矩形脉冲信号去调制一个调频器,如(a)图所示,使其能够输出两个不同频率的码元。

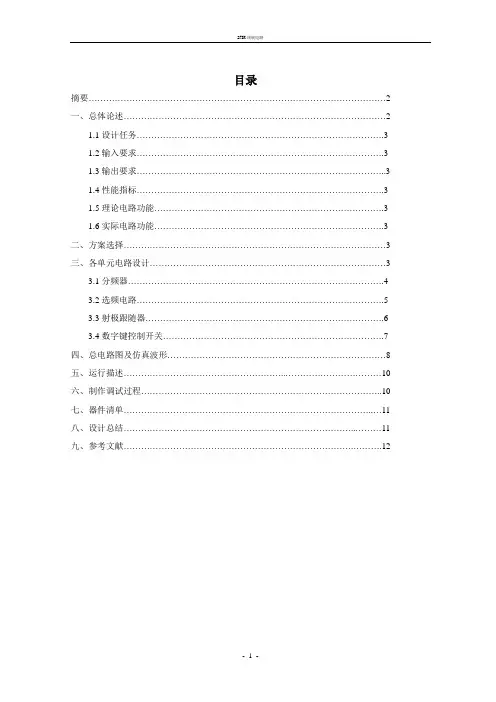

CD4000:双三输入或非门CD4001:四双输入或非门CD4002双四输入或非门CD4006:18位静态移位寄存器//当D1为高(低)时clk给四个脉冲D1+4为高(低),相当于延迟四个脉冲cd4007:双互补对加反相器CD4008:并行进位输出全加器CD4009:六缓相器/转换-倒相CD4010:六缓相器/转换-正相CD4011四2输入端与非门CD4012双4输入端与非门CD4013双主-从D型触发器CD4014 8位串入/并入-串出移位寄存器CD4015双4位串入/并出移位寄存器CD4016四传输门CD4017十进制计数/分配器CD4018可预制1/N计数器//当PE为高时并行输入数据,与clk无关,PE为低时D输入并移位CD4019四与或选择器CD4020 14级串行二进制计数/分频器clk给八个下降沿Q3开始计数CD4021 08位串入/并入-串出移位寄存器当9脚为同时D5-D7并行输入数据且与时钟无关,当其为低电平时从D4数据开始移位,SIN数据迟后六个脉冲CD402八进制计数/分配器CD4023三3输入端与非门CD4024 7级二进制串行计数/分频器CD4025三3输入端或非门CD4026十进制计数/7段译码器当2和15为低3为高时,数码管随脉冲0-1-2…9-02脚为高电平时计数锁存脚5.4.14一般为高显9时5脚为低显2时14脚为低4脚与3脚一至CD4027双J-K触发器CD4028 BCD码十进制译码器当jk同时为1时Qn+1=Qn’CD4029可预置可逆计数器CD4030四异或门当输入全部为低时,只给clk时钟,输出从9到0计数co平时为高输出为0时其为低,当只有10脚为高时给Clk电路从0到9计数,co只在显9时为低。

5脚为高电平则锁存。

1脚为高则并行置数·CD4033 十进制计数/7段译码器CD4034 8位通用总线寄存器CD4035 4位并入/串入-并出/串出移位寄存CD4038三串行加法器CD4040 12级二进制串行计数/分频器CD4041四同相/反相缓冲器脚1为脚3的同相输出,脚2为脚3的反相输出CD4042四锁存D型触发器CD4043 4三态R-S锁存触发器("1"触发) CD4044四三态R-S锁存触发器("0"触发) CD4046锁相环\\见资料CD4047无稳态/单稳态多谐振荡器\\见资料CD4048 4输入端可扩展多功能门\\见资料CD4049六反相缓冲/变换器CD4050六同相缓冲/变换器CD4051八选一模拟开关CD4052双4选1模拟开关6脚为低电平时有效;6脚为低电平时无效CD4053三组二路模拟开关只要A为1,NH CD4054 液晶显示驱动器为低x=x1;若A为0;INH为低不管BCX=x0CD4055 BCD-7段译码/液晶驱动器CD4056液晶显示驱动器当6脚为高电平时输出反码CD4059“N”分频计数器CD4060 14级二进制串行计数/分频器CD4063四位数字比较器CD4066四传输门CD4067 16选1模拟开关CD4068八输入端与非门/与门4069六反相器CD4070四异或门CD4071四2输入端或门CD4072双4输入端或门CD4073三3输入端与门CD4075三3输入端或门CD4076四D寄存器\\见资料CD4077四2输入端异或非门CD4078 8输入端或非门/或门CD4081四2输入端与门CD4082双4输入端与门CD4093四2输入端施密特触发器CD4085双2路2输入端与或非门CD4094 8位移位存储总线寄存器CD4095 3输入端J-K触发器STB为高时则将移位的数据显示出来,STB为低时输出保持不变,移位在工作只是没有显出来,要等到下次STB为高时才显出来,相当于74595的两个时钟CD4096 3输入端J-K触发器CD4098双单稳态触发器CD4099 8位可寻址锁存器CD40105先入先出FI-FD寄存器CD40106六施密特触发器CD40110十进制加/减,计数,锁存,译码驱动CD40160可预置BCD加计数器CD40161可预置4位二进制加计数器CD40162 BCD加法计数器CD40163 4位二进制同步计数器CD40174六锁存D型触发器CD40175四D型触发器CD40192可预置BCD CD40193可预置4位二进制CD40194 4位并入/串入-并加/减计数器(双时钟) 加/减计数器出/串出移位寄存CD4502可选通三态输出六反相/缓冲器CD4503六同相三态缓冲器CD4508双4位锁存D型触发器//12脚为低反相CD4510可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512八路数据选择器CD4513 BCD锁存,7段CD4514 4位锁存,4线-16CD4515 4位锁存,4线-16 译码,驱动器(消隐) 线译码器线译码器CD4516可预置4位二进制加/减计数器CD4518双BCD同步加计数器CD4520双4位二进制同步加计数器CD4522可预置BCD同步1/N计数器CD4526可预置4位二进制同步1/N计数器CD4528双单稳态触发器CD4529双四路/单八路模拟开关CD4530双5输入端优势逻辑门CD4532 8位优先编码器CD4538精密双单稳CD4539双四路数据选择器CD4541 可编程序振荡/计时器CD4543BCD七段锁存译码,驱动器CD4553三位BCD计数器CD4555双二进制四选一译码器/分离器CD4556双二进制四选CD4560 "N"BCD加法器CD4584六施密特触发器一译码器/分离器CD4585 4位数值比较器。

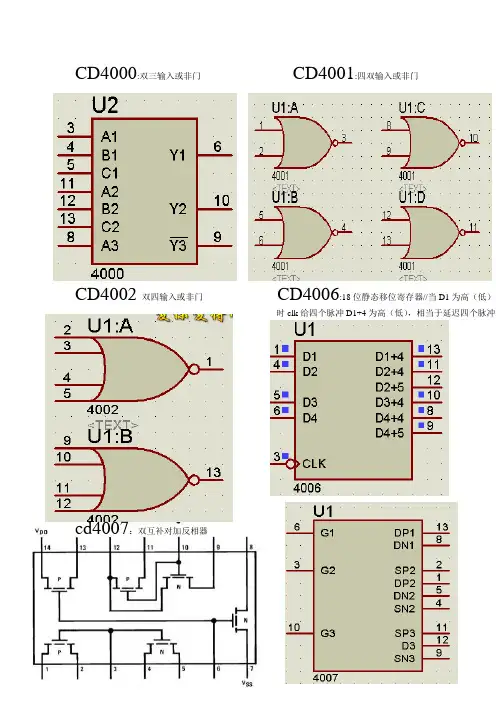

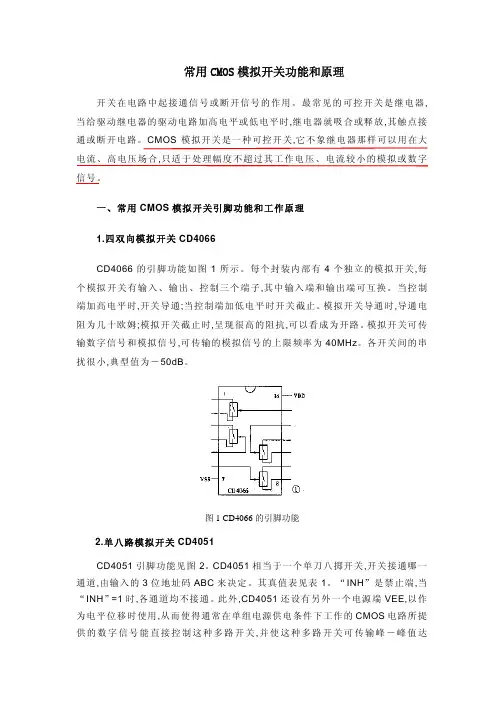

常用CMOS模拟开关功能和原理(4066,4051-53)开关在电路中起接通信号或断开信号的作用。

最常见的可控开关是继电器,当给驱动继电器的驱动电路加高电平或低电平时,继电器就吸合或释放,其触点接通或断开电路。

CMOS模拟开关是一种可控开关,它不象继电器那样可以用在大电流、高电压场合,只适于处理幅度不超过其工作电压、电流较小的模拟或数字信号。

一、常用CMOS模拟开关引脚功能和工作原理1.四双向模拟开关CD4066CD4066的引脚功能如图1所示。

每个封装内部有4个独立的模拟开关,每个模拟开关有输入、输出、控制三个端子,其中输入端和输出端可互换。

当控制端加高电平时,开关导通;当控制端加低电平时开关截止。

模拟开关导通时,导通电阻为几十欧姆;模拟开关截止时,呈现很高的阻抗,可以看成为开路。

模拟开关可传输数字信号和模拟信号,可传输的模拟信号的上限频率为40MHz。

各开关间的串扰很小,典型值为-50dB。

2.单八路模拟开关CD4051CD4051引脚功能见图2。

CD4051相当于一个单刀八掷开关,开关接通哪一通道,由输入的3位地址码ABC来决定。

其真值表见表1。

“INH”是禁止端,当“INH”=1时,各通道均不接通。

此外,CD4051还设有另外一个电源端VEE,以作为电平位移时使用,从而使得通常在单组电源供电条件下工作的CMOS电路所提供的数字信号能直接控制这种多路开关,并使这种多路开关可传输峰-峰值达15V的交流信号。

例如,若模拟开关的供电电源VDD=+5V,VSS=0V,当VEE=-5V时,只要对此模拟开关施加0~5V的数字控制信号,就可控制幅度范围为-5V~+5V的模拟信号。

表13.双四路模拟开关CD4052CD4052的引脚功能见图3。

CD4052相当于一个双刀四掷开关,具体接通哪一通道,由输入地址码AB来决定。

其真值表见表2。

表24.三组二路模拟开关CD4053CD4053的引脚功能见图4。

CD4053内部含有3组单刀双掷开关,3组开关具体接通哪一通道,由输入地址码ABC来决定。

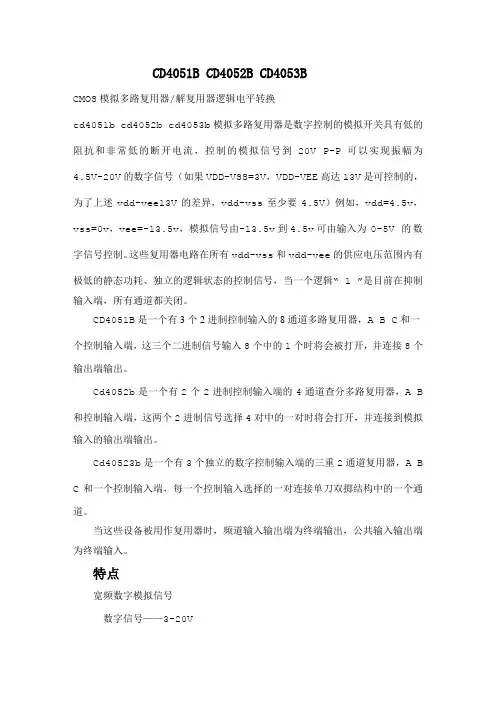

CD4051B CD4052B CD4053BCMOS模拟多路复用器/解复用器逻辑电平转换cd4051b cd4052b cd4053b模拟多路复用器是数字控制的模拟开关具有低的阻抗和非常低的断开电流,控制的模拟信号到20V P-P可以实现振幅为4.5V-20V的数字信号(如果VDD-VSS=3V,VDD-VEE高达13V是可控制的,为了上述vdd-vee13V的差异,vdd-vss至少要4.5V)例如,vdd=4.5v,vss=0v,vee=-13.5v,模拟信号由-13.5v到4.5v可由输入为0-5V的数字信号控制。

这些复用器电路在所有vdd-vss和vdd-vee的供应电压范围内有极低的静态功耗、独立的逻辑状态的控制信号,当一个逻辑“ 1 ”是目前在抑制输入端,所有通道都关闭。

CD4051B是一个有3个2进制控制输入的8通道多路复用器,A B C和一个控制输入端,这三个二进制信号输入8个中的1个时将会被打开,并连接8个输出端输出。

Cd4052b是一个有2个2进制控制输入端的4通道查分多路复用器,A B 和控制输入端,这两个2进制信号选择4对中的一对时将会打开,并连接到模拟输入的输出端输出。

Cd40523b是一个有3个独立的数字控制输入端的三重2通道复用器,A B C和一个控制输入端,每一个控制输入选择的一对连接单刀双掷结构中的一个通道。

当这些设备被用作复用器时,频道输入输出端为终端输出,公共输入输出端为终端输入。

特点宽频数字模拟信号数字信号——3-20V模拟信号——≦20Vp-p*低开起电阻,125Ω(典型的)超过15V p-p 输入信号范围VDD-VEE = 18V*高关闭电阻,在VDD-VEE = 18V时沟道电流损失±100pA*逻辑电平转换成数字信号的处理(VDD-VEE=3V—20V)以开关模拟信号20Vp-p VDD-VEE=20V*开关匹配特性,rON = 5Ω(VDD-VEE = 15)*在所有控制输入和控制条件下有非常低的静态功耗,0.2μW 在VDD-VSS = VDD-VEE = 10V*二进制地址译码芯片*5V 10V 15V的参数评级*10%测试静态电流在20V*在18V的全套封装中,最大输入电流1mA,温度范围,100nA在18V和25oC *为消除沟道转换重叠,先开后合应用*模拟和数字复用及解复用*A/D D/A转换*门控信号。

模拟开关CD4051,CD4052,CD4053中文资料模拟开关CD4051,CD4052,CD4053中文资料CD4051/CC4051是单8通道数字控制模拟电子开关,有三个二进控制输入端A、B、C和INH 输入,具有低导通阻抗和很低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰值至20V的模拟信号。

例如,若VDD=+5V,VSS=0,VEE=-13.5V,则0~5V的数字信号可控制-13.5~4.5V 的模拟信号。

这些开关电路在整个VDD-VSS和VDD-VEE电源范围内具有极低的静态功耗,与控制信号的逻辑状态无关。

当INH输入端=“1”时,所有的通道截止。

三位二进制信号选通8通道中的一通道,可连接该输入端至输出。

CD4052/CC4052是一个差分4通道数字控制模拟开关,有A、B两个二进制控制输入端和INH 输入,具有低导通阻抗和很低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰峰值至20V 的模拟信号。

例如,若V DD=+5V,VSS=0,VEE=-13.5V,则0~5V的数字信号可控制-13.5~4.5V 的模拟信号,这些开关电路在整个VDD-VSS和VDD-VEE电源范围内具有极低的静态功耗,与控制信号的逻辑状态无关,当INH输入端=“1”时,所有通道截止。

二位二进制输入信号选通4对通道中的一通道,可连接该输入至输出。

CD4053/CC4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH 输入,具有低导通阻抗和低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰-峰值至20V 的数字信号。

例如若VDD=+5,VSS=0,VEE=-13.5V,则0~5V的数字信号可控制-13.5~4.5V 的模拟信号。

这些开关电路在整个VDD-VSS和VDD-VEE电源范围内具有极低的静态功耗,与控制信号的逻辑状态无关。

当INH输入端=“1”时,所有通道截止。

CD4051,CD4052,CD4053中文资料CD4051,CD4052,CD4053中文资料CD4051/CC4051是单8通道数字控制模拟电子开关,有三个二进控制输入端A、B、C和INH输入,具有低导通阻抗和很低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰值至20V的模拟信号。

例如,若VDD=+5V,VSS=0,VEE=-13.5V,则0~5V的数字信号可控制-13.5~4.5V的模拟信号。

这些开关电路在整个VDD-VSS和VDD-VEE电源范围内具有极低的静态功耗,与控制信号的逻辑状态无关。

当INH输入端=“1”时,所有的通道截止。

三位二进制信号选通8通道中的一通道,可连接该输入端至输出。

CD4052/CC4052是一个差分4通道数字控制模拟开关,有A、B两个二进制控制输入端和INH输入,具有低导通阻抗和很低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰峰值至20V的模拟信号。

例如,若V DD=+5V,VSS=0,VEE=-13.5V,则0~5V的数字信号可控制-13.5~4.5V的模拟信号,这些开关电路在整个VDD-VSS和VDD-VEE电源范围内具有极低的静态功耗,与控制信号的逻辑状态无关,当INH 输入端=“1”时,所有通道截止。

二位二进制输入信号选通4对通道中的一通道,可连接该输入至输出。

CD4053/CC4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。

例如若VDD=+5,VSS=0,VEE=-13.5V,则0~5V的数字信号可控制-13.5~4.5V的模拟信号。

这些开关电路在整个VDD-VSS和VDD-VEE电源范围内具有极低的静态功耗,与控制信号的逻辑状态无关。

当INHCD4051逻辑图CD4051引脚图CD4052逻辑图 CD4052引脚图CD4053逻辑图 CD4053引脚图。

本页已使用福昕阅读器进行编辑。

福昕软件(C)2005-2007,版权所有,仅供试用。

常用CMOS模拟开关功能和原理开关在电路中起接通信号或断开信号的作用。

最常见的可控开关是继电器,当给驱动继电器的驱动电路加高电平或低电平时,继电器就吸合或释放,其触点接通或断开电路。

CMOS模拟开关是一种可控开关,它不象继电器那样可以用在大电流、高电压场合,只适于处理幅度不超过其工作电压、电流较小的模拟或数字信号。

一、常用CMOS模拟开关引脚功能和工作原理1.四双向模拟开关CD4066CD4066的引脚功能如图1所示。

每个封装内部有4个独立的模拟开关,每个模拟开关有输入、输出、控制三个端子,其中输入端和输出端可互换。

当控制端加高电平时,开关导通;当控制端加低电平时开关截止。

模拟开关导通时,导通电阻为几十欧姆;模拟开关截止时,呈现很高的阻抗,可以看成为开路。

模拟开关可传输数字信号和模拟信号,可传输的模拟信号的上限频率为40MHz。

各开关间的串扰很小,典型值为-50dB。

图1 CD4066的引脚功能2.单八路模拟开关CD4051CD4051引脚功能见图2。

CD4051相当于一个单刀八掷开关,开关接通哪一通道,由输入的3位地址码ABC来决定。

其真值表见表1。

“INH”是禁止端,当“INH”=1时,各通道均不接通。

此外,CD4051还设有另外一个电源端VEE,以作为电平位移时使用,从而使得通常在单组电源供电条件下工作的CMOS电路所提供的数字信号能直接控制这种多路开关,并使这种多路开关可传输峰-峰值达15V的交流信号。

例如,若模拟开关的供电电源VDD=+5V,VSS=0V,当VEE=-5V时,只要对此模拟开关施加0~5V的数字控制信号,就可控制幅度范围为-5V~+5V的模拟信号。

图2 CD4051引脚功能表1 CD4051真值表3.双四路模拟开关CD4052CD4052的引脚功能见图3。

CD4052相当于一个双刀四掷开关,具体接通哪一通道,由输入地址码AB来决定。

cd4053工作原理CD4053是一种常用的集成电路芯片,它可以实现模拟信号的多路复用和解复用功能。

本文将详细介绍CD4053的工作原理及其应用。

CD4053是一种集成电路开关,其内部包含三个独立的双二极管开关。

每个开关都有一个控制引脚,通过控制引脚的高低电平来控制开关的通断状态。

当控制引脚为高电平时,开关闭合,模拟信号可以通过开关传输;当控制引脚为低电平时,开关断开,模拟信号无法通过开关传输。

CD4053的工作原理可以分为两个方面来说明。

首先是控制信号的作用。

CD4053的控制引脚可以接受来自其他电路的控制信号,通过这些控制信号的高低电平来控制开关的通断状态。

这样就可以实现多路复用和解复用功能。

例如,当控制引脚A为高电平,控制引脚B和C为低电平时,开关S1闭合,模拟信号可以从引脚Y1传输到引脚Z1,实现了多路复用功能。

当控制引脚A为低电平,控制引脚B为高电平,控制引脚C为低电平时,开关S2闭合,模拟信号可以从引脚Y2传输到引脚Z2,实现了解复用功能。

其次是CD4053内部的结构。

CD4053内部包含三个独立的开关,每个开关都有一个控制引脚和两个信号引脚。

这些开关由二极管和场效应晶体管组成。

当控制引脚为高电平时,二极管导通,场效应晶体管闭合,信号可以通过开关传输。

当控制引脚为低电平时,二极管截止,场效应晶体管断开,信号无法通过开关传输。

CD4053的应用非常广泛。

它可以用于模拟信号的选择、开关和路由等应用场景。

例如,在音频系统中,可以使用CD4053来实现声音的选择和混音功能。

在电视机中,可以使用CD4053来实现不同信号源的切换和选择。

在通信系统中,可以使用CD4053来实现信号的分配和选择。

此外,CD4053还可以用于数据采集、仪器仪表和自动控制等领域。

CD4053是一种常用的集成电路芯片,它可以实现模拟信号的多路复用和解复用功能。

通过控制引脚的高低电平来控制开关的通断状态,从而实现信号的选择、开关和路由等应用。

主要介绍用集成电路CD4053实现的模拟开关型防抖动电路1引言当机械开关工作时,其开关触点的闭合和张开,都会产生随机性的机械抖动,给电路产生不希望的振荡脉冲和干扰。

因此,防抖动电路和防抖动软件成为计算机外设的重要接口部分。

常见的防抖动电路用的集成片较多,电路也较复杂,市场上也能买到防抖动的专用集成片,成本都比较高。

下面介绍两个用模拟开关CD4053实现的防抖动电路。

2输出互补式模拟开关型防抖动电路图1(a)是用1只CD4053、3只电阻器(R1~R3)和1只电容器C等构成的防抖动电路。

CD4053中的3个模拟开关(G1~G3)都是双向单刀双掷模拟开关,用单电源电压VDD供电。

模拟开关G3的1端作为输入端接地,0端也作为输入端接电压VDD,输出端Q相对于其控制端Q呈倒相门工作状态。

同样模拟开关G2的1端作为输入端经电阻器R2接地,0端也作为输入端经电阻器R3接电压VDD,输出端Q相对于其控制端Q也呈倒相门工作状态。

模拟开关G2、G3的输出端和控制端相互交连,构成了一个S—R双稳触发器,触发信号S和R分别设在模拟开关G2的1输入端和0输入端,其工作的真值表如表1所示。

模拟开关G1的公用端作为输入信号VI的输入端;0端作为触发信号S的输出端,连到模拟开关G2的1输入端;1端作为触发信号R的输出端,连到模拟开关G2的0输入端。

模拟开关G2的输出端Q经电阻器R1和电容器C构成的积分器连到模拟开关G1的控制端A。

要选择电阻器R1~R3的参数使R1>>R2=R3>>RON,其中RON是模拟开关G2的导通电阻,约为300Ω;同时还要选择电容器C,使时间常数R1C足够大于输入信号VI边沿振荡的时间。

(a)防抖动电路(B)工作时序图图1输出互补式模拟开关型防抖动电路及其工作时序图表1真值表在加电的瞬间,输入信号VI=0,由于电容器C上的电压不能突变,故使模拟开关G1控制端A的电压VA=0,因此,模拟开关G1的0输出端S导通在输入端VI=0电位上,1输出端R经电阻器R3接电压VDD。

题目数控增益放大器研究摘要数控增益放大器是集计算机技术、电子技术、数控技术为一体的机电一体化高科技产品,具有安全性高,使用方便等优点。

本论文从数控增益放大器功能,硬件电路设计,单元电路设计软件控制等几部分,分别论述这一系统。

本系统考虑到数控增益放大器成本及体积因素,在设计数控增益放大器部分时,以CD612/614等集成电路为核心,芯片部分由C D4051.8051等构成。

数控增益放大器设计综合应用之前所学的单片机、微机控制、电路设计等方面的知识。

运行表明,其性能高,使用灵活性好,安全系数高,成本则相对较小,被广泛应用。

关键词:CD612/614 :74L373:CD4051 前言Topic numerical control gain amplifier researchAbstractThe numerical control gain amplifier is the collection computertechnology, the electronic technology, the numerical controltechnology is a body integration of machinery high tech product, hasthe security to be high, merit and so on easy to operate. The presentpaper from the numerical control gain amplifier function, the hardwarecircuit design, the unit circuit design software control and so onseveral parts, separately elaborates this systemThis system considered numerical control gain amplifier cost and bulkfactor, when design numerical control gain amplifier part, takeintegrated circuit and so on the CD612/614 as the core, the chippartially and so on constitutes by CD4051.8051Before numerical control gain amplifier design synthesis applicationstudies aspect and so on monolithic integrated circuit, microcomputercontrol, circuit design knowledge. The movement indicated, itsperformance high, use flexibility good, safety coefficient high, thecost then relative is smaller, is widely applied.Key word: CD612/614: 74L373: CD4051前言(放在目录后)(??数控增益放大器)随着近代超大规模集成电路的出,微处理器及其外围芯片有了迅速的发展。