课程名称:数字逻辑电路设计实践实验名称:组合逻辑电路设计

时序逻辑电路

1、

实验目的

1. 掌握时序逻辑电路的一般设计过程;

2. 掌握时序逻辑电路的时延分析方法,了解时序电路对时钟信号相关参数的基本要求;

3. 掌握时序逻辑电路的基本调试方法;

4. 熟练使用示波器和逻辑分析仪观察波形图,并会使用逻辑分析仪做状态分析。

2、 实验原理 详见书103~147

3、

实验内容

1. 广告流水灯

a. 实验要求

用触发器、组合函数器件和门电路设计一个广告流水灯,该流水等由8个LED 组成,工作时始终为1暗7亮,且这一个暗灯循环右移。

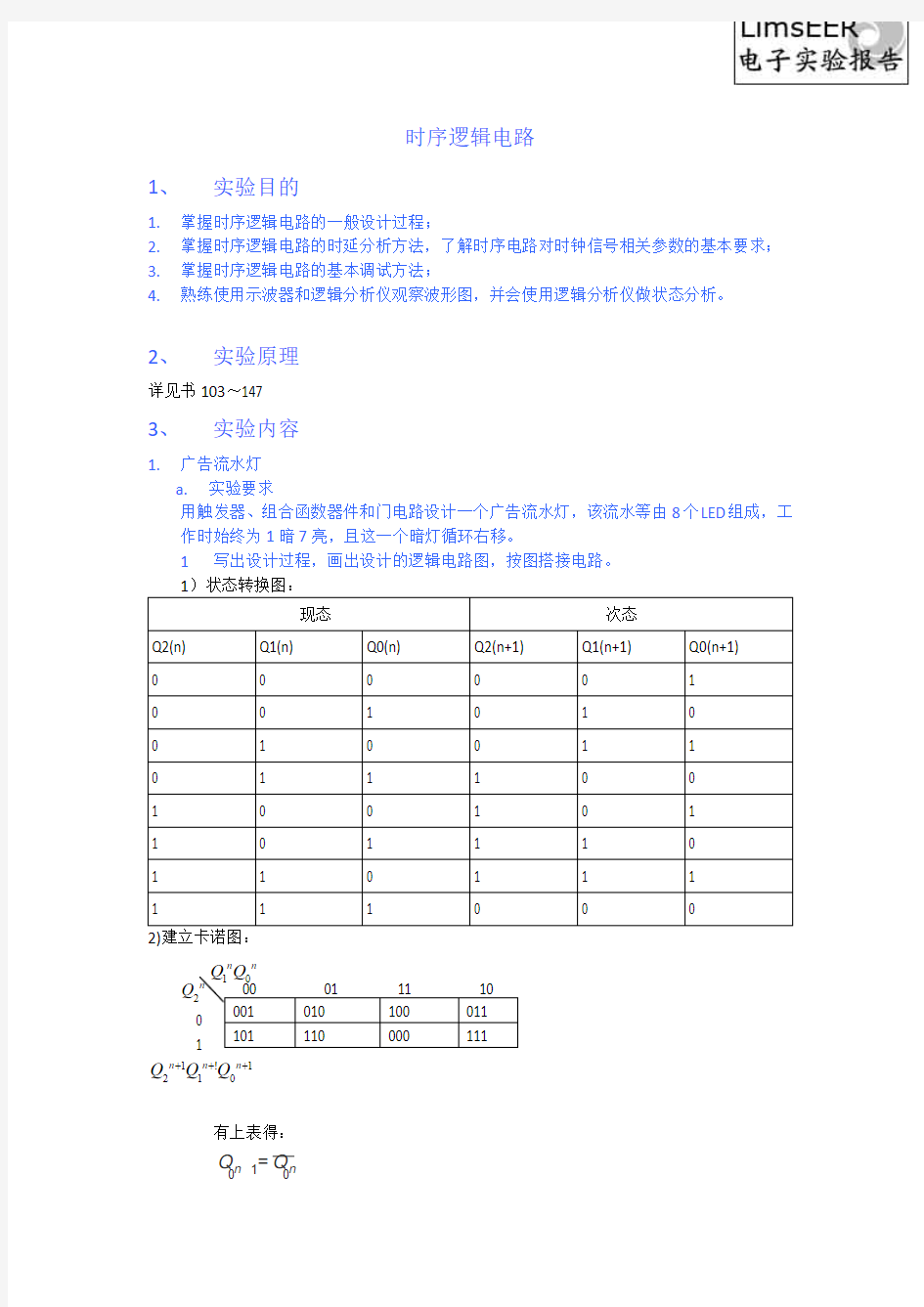

1 写出设计过程,画出设计的逻辑电路图,按图搭接电路。 1)状态转换图: 现态 次态 Q2(n) Q1(n) Q0(n) Q2(n+1) Q1(n+1) Q0(n+1) 0 0 0 0 0

1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 1 0 0 1 0 0 1 0 1 1 0 1 1 1 0 1 1 0 1 1 1 1

1

1

2)建立卡诺图:

001 010 100 011 101 110

000

111

1!1

210n n n Q Q Q +++

有上表得:

Q 0n 1=Q 0

n 0

1

00 01 11 10 2

n

Q 10n n

Q Q

Q 1n 1=Q 0n ⊕Q 1

n

Q 2n 1=Q 0n Q 1n ⊕Q 2n =Q 0n Q 1n ⊕Q 2

n 因此,需要三个D 触发器来实现时序电路,三个D 触发器分别对应Q0、Q1、Q2 通过一片74LS138 3-8线译码器将Q2Q1Q0所对应的二进制码输出转化为相应的0~7号LED 灯的输入电平。

2 将单脉冲加到系统时钟端,静态验证实验电路。

3 将TTL 连续脉冲信号加到系统时钟端,用示波器和逻辑分析仪观察并记录时钟脉

冲CLK 、触发器的输出端Q2、Q1、Q0和8个LED 上的波形。 b . 实验数据 ① 设计电路。

U1A

74ALS74AN

1D

2

1Q

5

~1Q

6

~1CLR

1

1CLK 3

~1PR

4U2A 74ALS74AN

1D

2

1Q

5

~1Q

6

~1CLR 1

1CLK 3

~1PR

4

U3B

74ALS74AN

1D

2

1Q

5

~1Q

6

~1CLR

1

1CLK 3

~1PR

4U4A

74ALS86N

U5B

74ALS86N

U6A

74LS04N

U7A

74LS00N VCC

5V

1

45

78U9

74LS138N

Y015Y114Y213Y312Y411Y510Y69Y7

7

A 1

B 2

C 3G16~G2A 4~G2B

5

6

23

VCC VCC 5V

VCC

LED

② 静态验证 (自拟表格)

将3-8译码器的15Y ~0Y 输出端,从左到右依次接测试箱上的8个LED 灯80~L L ,3个D 触发器共同接箱上经消抖处理的当脉冲信号(上升沿触发)。依次按动单脉冲按钮,得以下结果。见表1.

表1.广告流水灯静态验证结果

次序 L8 L7 L6 L5 L4 L3 L2 L1 1 暗 亮 亮 亮 亮 亮 亮 亮 2 亮 暗 亮 亮 亮 亮 亮 亮 3 亮 亮 暗 亮 亮 亮 亮 亮 4 亮 亮 亮 暗 亮 亮 亮 亮 5 亮 亮 亮 亮 暗 亮 亮 亮 6

亮

亮

亮

亮

亮

暗

亮

亮

7 亮 亮 亮 亮 亮 亮 暗 亮 8 亮 亮 亮 亮 亮 亮 亮 暗 9 暗

亮

亮

亮

亮

亮

亮

亮

分析:可见暗灯从左往右按顺序移动,并且到最右端会返回到最左端循环移动。说明3-8译码器的15Y ~0Y 输出端依次为低电平有效,说明电路中3个D 触发器的确实现了模8循环计数功能,说明实验成功。

③ 动态验证 波形记录:

其中D1~D8为译码器输出到发光二极管的信号,D9为时钟;D10~D12为译码器输入信号;

2. 序列发生器

a. 实验要求

分别用MSI 计数器和移位寄存器设计一个具有自启动功能的01001序列信号发生器。 ① 写出设计过程,画出电路逻辑图。

1)计数器实现采用的是方法是计数器结合译码器:

首先是用74161实现模五功能,采用的是输出0100时同步置数,回到0000状态。

译码器部分则是将模五计数器输出低三位作为译码器输入,由于译码器输出是低电平有效,因此将Y1‘,Y4'通过与非门输出,作为信号发生器。

2)移位寄存器实现: 考虑自启动功能华后,

列出状态转移表:为了简化实验电路图,在无效状态时将S1,D 0

状态设为表中

值:

(以QA 为序列信号发出端)

顺

序 Q C

Q B

Q A

D 0

S1

功能 有 效 状 态

1 1 0 1 0

右移 1 1 0 1 0

右移 2 0 1

0 0 右移 3 1 0 0 1 0 右移 4

0 0 1 0 1 置数 无 效 状 态

5 1 1 1 0 0 右移 6

0 0 0 1 0 置数 7 0

1

1

右移

建立卡诺图: D:

1 0 0 1 1

1

得逻辑表达式为:

C A

D Q Q

S1:

1 1 0 0 0 0 0 0

0 1

00 01 11 10 C

Q

B A

Q Q 0

1 00 01 11 10 C

Q B A

Q Q

根据S1和C B A Q Q Q 、、关系容易得到:

1B C

S Q Q

② 搭接电路,并用单脉冲静态验证实验结果。

③ 加入TTL 连续脉冲,用双踪示波器和逻辑分析仪观察并记录时钟脉冲CLK 、序列输出端的波形。

实验数据

① 设计电路。

1)MSI 计数器电路图:(改进)

U1

74LS161N

QA 14QB 13QC 12QD 11RCO

15

A 3

B 4

C 5

D 6

ENP 7

ENT 10

~LOAD 9~CLR 1CLK

2

U2

74LS138N

Y015Y114Y213Y312Y411Y510Y69Y7

7

A 1

B 2

C 3G16~G2A 4~G2B

5

sA

74LS20N

2

U4A 74LS04N

3

4

567

VCC

5V

VCC D

1

2)移位寄存器设计:

U1

74LS194D

A 3

B 4

C 5

D 6SL 7QA 15QB 14QC 13QD

12

SR 2

~CLR 1S09

S110CLK

11

VCC

5V

VCC U2A 74LS00D U3A

74LS00D

U4A

74LS04N U5B 74LS04N

U6C 74LS04N

U7B 74LS04N

U8A

74LS04N 24

5

6

7

8

3

9

10

XFG1

Agilent

11

1

D

② 静态验证 (自拟表格) 分析:

其中Q1为信号输出,D表示移位的输入信号

③动态验证

波形记录:

其中D11为序列发生器;D15为扫描信号

3.分频器

a.实验要求

设计一个分频器。要求将频率为32768Hz的方波信号变成32.768Hz的方波信号,其中32768Hz的方波信号需要自己通过电路产生。

① 根据实验要求,拟出设计方案。

分频器的设计思路是基于计数器实现的,本题要求分频系数为1000,因此采用需要设计一个模1000的计数器。

方案1:分别用74LS161设计三个模10的计数器,并将其级联(进位信号控制使能端)。但是由于此时其占空比为1/1000,用GW2000不易观察到脉冲波形,所以改用方案2。

方案2:仍采用三个模10级联而成,但此时模10计数器是通过74LS161产生的模5计数器与D —S 触发器级联产生的,因此三个模10计数器级联以后,每个模10计数器输出都是占空比为50%,易观察。设计电路图如下:

② 根据设计方案选择器件,并查阅所用器件的功能表和引脚图。 ③ 写出设计过程,画出电路逻辑图和实验接线图并标出引脚号。 ④ 用逻辑分析仪观察时钟脉冲CLK 和各计数器输出端的波形。

⑤ 用逻辑分析仪对时钟脉冲CLK 和各计数器输出端的信号做状态分析。 b. 实验数据 ① 设计电路。

U5

74LS161N

QA 14QB 13QC 12QD 11RCO

15

A 3

B 4

C 5

D 6ENP 7ENT 10~LOAD 9~CLR 1

CLK

2

VCC

5V

U6A 74LS04N

U7A

74LS74N

1D

2

1Q

5

~1Q

6

~1CLR 1

1CLK

3

~1PR 43

1

VCC 2

U1

74LS161N

QA 14QB 13QC 12QD 11RCO

15

A 3

B 4

C 5

D 6

ENP 7ENT 10~LOAD 9~CLR 1

CLK

2

VCC

5V

U2A 74LS04N

U3A

74LS74N

1D

2

1Q

5

~1Q

6

~1CLR 1

1CLK 3

~1PR 46VCC 0

5

4

U4

74LS161N

QA 14QB 13QC 12QD 11RCO

15

A 3

B 4

C 5

D 6

ENP 7ENT 10~LOAD 9~CLR 1

CLK

2

VCC

5V

U8A 74LS04N

U9A

74LS74N

1D

2

1Q

5

~1Q

6

~1CLR 1

1CLK 3

~1PR

49VCC 0

8

7

10

11

12

1/1000

② 静态验证

(自拟表格)

顺序

D

C

B

A

RCO

0 0 0 0 0 0 1 0 0 0 1 0 2 0 0 1 0 0 3 0 0 1 1 0 4 0 1 0 0 0 5 0 1 0 1 0 6 0 1 1 0 0 7 0 1 1 1 0 8 1 0 0 0 0 9

1

1

10 1 0 1 0 0

11 1 0 1 1 0

12 1 1 0 0 0

13 1 1 0 1 0

14 1 1 1 0 0

15 1 1 1 1 1

分析:灰色部分为我们采用的实现模五功能的部分

③动态验证

波形记录:

上图分别实现模100与模1000;

状态分析:略

4.行列式键盘识别电路

a.实验要求

设计一个电路,当按下4×4矩阵键盘中的任何一个键时,在数码管上显示相应的键值。其中键码可通过ROM查表的方式来实现,数码管可选择是BCD输入还是七段输入,实验箱上的4×4键盘上拉电阻已经在内部连接好。

①根据实验要求,拟出设计方案。

②根据设计方案选择器件,并查阅所用器件的功能表和引脚图。

③写出设计过程,画出电路逻辑图和实验接线图并标出引脚号。

1)功能分析:本题可分为三个模块:扫描电路,消抖电路,寄存器

2)模块实现:

A)消抖电路:

采用一个D触发器,加100Hz的时钟信号。D触发器的输出控制的寄存器的置数功能和扫描电路的扫描功能。当有键按下时,触发器控制扫描电路停止扫描,控制寄存器保存信号。

B)寄存器:采用两个74LS161实现

C)扫描信号电路:

要实现0111,1011,1101,1110的循环扫描,采用移位寄存器实现,考虑其自启动功能,1)其转态转移图如下:

ROM 表如下:

根据状态图再划出真值表就可以得到状态方程:0012Q Q Q Q (A7~A4对应键盘上row1~row4; A3~A0对应键盘上的col1~col4 ) A A 7 A A 6 A A 5 A A 4 A A 3 A A 2 A A 1 A A 0 I/O I/O3~I/O0 2位十六进制表示 3 2 1

1 10 00 11 11 1 0 1 1 0 1

0 1

0 0 00 00 00 00 11 11 1 1 1 0 0 1

0 1 0 0 00 01 01 00 11 11 1 1 1 1 0 0

0 1

0 0 01 00 02 00 11 11 1 1 1 1 0 1

0 0

0 0 01 01 03 01 10 11 1 0 1 1 0 1

0 1

0 1 00 00 04 01 10 11 1 1 1 0 0 1

0 1

0 1 00 01 05 01

10

11

1

1

1 1

0 0 0 1

1

01

06

1111

0110 0111

1101 0101 1010 0100

1011 1000 0010

1001 0011

1100

1110

0000 1000 0001

01 10 11 1 1 1 1 0 1 0 0 0 1 01 01 07 01 11 10 1 0 1 1 0 1 0 1 1 0 00 00 08 01 11 10 1 1 1 0 0 1 0 1 1 0 00 01 09 01 11 10 1 1 1 1 0 0 0 1 1 0 01 00 0A 01 11 10 1 1 1 1 0 1 0 0 1 0 01 01 0B 01 11 11 0 0 1 1 0 1 0 1 1 1 00 00 0C 01 11 11 0 1 1 0 0 1 0 1 1 1 00 01 0D 01 11 11 0 1 1 1 0 0 0 1 1 1 01 00 0E 01

11

11

1

1 1

0 1

0 0

1

1

01

1

0F

④ 用逻辑分析仪观察时钟脉冲CLK 和各计数器输出端的波形。

⑤ 用逻辑分析仪对时钟脉冲CLK 和各计数器输出端的信号做状态分析。 b. 实验数据 ① 设计电路。

U1

74LS194N

A 3

B 4

C 5

D 6SL 7QA 15QB 14QC 13QD

12

SR 2

~CLR 1S09S110CLK

11

U2A

74LS20N

4row0row1row2row3

U3A

74LS20N

col0 col1 col2 col3

U4A 74LS74N

1D

21Q

5

~1Q

6

~1C L R

1

1C L K

3

~1P R

4

9

U5

74LS161N

QA 14QB 13QC 12QD 11RCO

15

A 3

B 4

C 5

D 6ENP 7ENT 10~LOAD 9~CLR 1

CLK

2

U6

74LS161N

QA 14QB 13QC 12QD 11RCO

15

A 3

B 4

C 5

D 6

ENP 7ENT

10~LOAD 9~CLR 1

CLK

2

1

2

3

11

567

8

100Hz

U7A 74LS04N 10

12

0100Hz 100Hz 100Hz

②静态验证

(自拟表格)

分析:

输出状态符合设计;

③动态验证

波形记录:

由于篇幅有限,下面显示1,2,3的动态波形;

其中D7为时钟,D15~D12为col3~col1;

D11~D8为row3~row1;

三幅图分别显示了,11101110,11101101,11101011;

选做实验:

1.序列检测器

实验要求

用触发器设计一个1011序列检查器,要求电路对串行输入序列进行检测,当连续检测到4个码元符合检测器的检测码1011时,检测器输出为1(注意:前一个1011序列的最后一个码元不能作为本次1011序列的第一个码元)

①使用静态(单步)的测试方法,画出图4.4.1所示的输入、输出时间关系图。

CLK

X

Z

②对串行输入序列101101101101010011011进行检测,记录检测结果。

b. 实验数据

①设计电路。

②静态验证

(自拟表格)

分析:

③动态验证

波形记录:

由于时间限制,本选做实只完成了设计部分:

设计过程如下:

一、确定电路的状态转换和状态表

由于是设计一个四位序列检测器,因此可以根据已出现的前三位和现在出现的一位进行判断是否为序列1011,而前三位状态可以设为Y,有八种可能,分别设为A、

B、C、D、E、F、G、H,输入的最后一位为X,输出是否为所要的状态Z;

建立状态表如下,

现态次态输出

X=0 X=1 X=0 X=1 A(000) A B 0 0

B(001) C D 0 0

C(010) E F 0 0

D(011)G H 0 0

E(100) A B 0 0

F(101) C D 0 1

G(110) E F 0 0

H(111)G H 0 0

由状态表可以看到,状态A、E,状态C、G,状态D、H在不同输入下都有相同的次态和输出,所以可以将其等同为一个状态,等效后又发现B、D等效,再次变换后得到,

现态

次态

输出

X=0

X=1 X=0 X=1 A (000) A B 0 0 B (001) C B 0 0 C (010) A F 0 0 F (101) C

B

1

二、 状态转换真值表、卡诺图

外输入 现态

n X n 2Q n

1Q

次态 外输出

n+12

Q

n+1

1

Q Z

0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 0 0 0 0 1 1 1 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 1 1 0 1 1 1

0 1 1

n+12

Q 卡诺图:

0 1 1 0 0

1

n+11

Q 卡诺图:

0 0 0 0 1

1

1

1

Z 卡诺图: 0 0 0 0 0

1

三、 建立方程组

由上述的卡诺图可以得到方程如下:

n+1n n n

2121n+11n n 21

Q XQ XQ Q ;Q X;Z XQ Q =+==

0 1

X

00 01 11 10 n n

21

Q Q 0 1

X

00 01 11 10 n n 21

Q Q 0 1

X 00 01 11 10

n n 21Q Q

四、 画出逻辑图如下:

U1A

74LS74N

1D

2

1Q

5

~1Q

6

~1CLR 1

1CLK 3

~1PR

4

U2B

74LS74N

1D

2

1Q

5

~1Q

6

~1CLR

1

1CLK 3

~1PR

4

U3A

74LS20N

U4A

74LS20N

U5A

74LS04N U6A 74LS00N

VCC

5V

U7A

74LS00N

VCC 5V

XFG1

Agilent

X

Z

为了使前一个1011序列的最后一个码元不能作为本次1011序列的第一个码元,电路图中使用输出Z 来控制两个触发器的清零端,一旦检测出1011,就回到初始状态0000;

四、思考题

1、 一个12进制加法计数器和一个12分频器有何区别? 答:加法计数器要求是递增计数,而分频器可以递增,也可以递减;

2、 用逻辑分析仪观察内容2中的波形时,为了能观察到输出信号的一个周期,应选择何种触发方式比较好。

答:外触发,使用内触发时看到的波形一般不稳定;采用外触发时,一个时钟周期会有一个状态的产生,使图像比较稳定。