单板设计电路

单板硬件设计(硬件设计)

电源滤波:

1·输入侧电源的滤波:

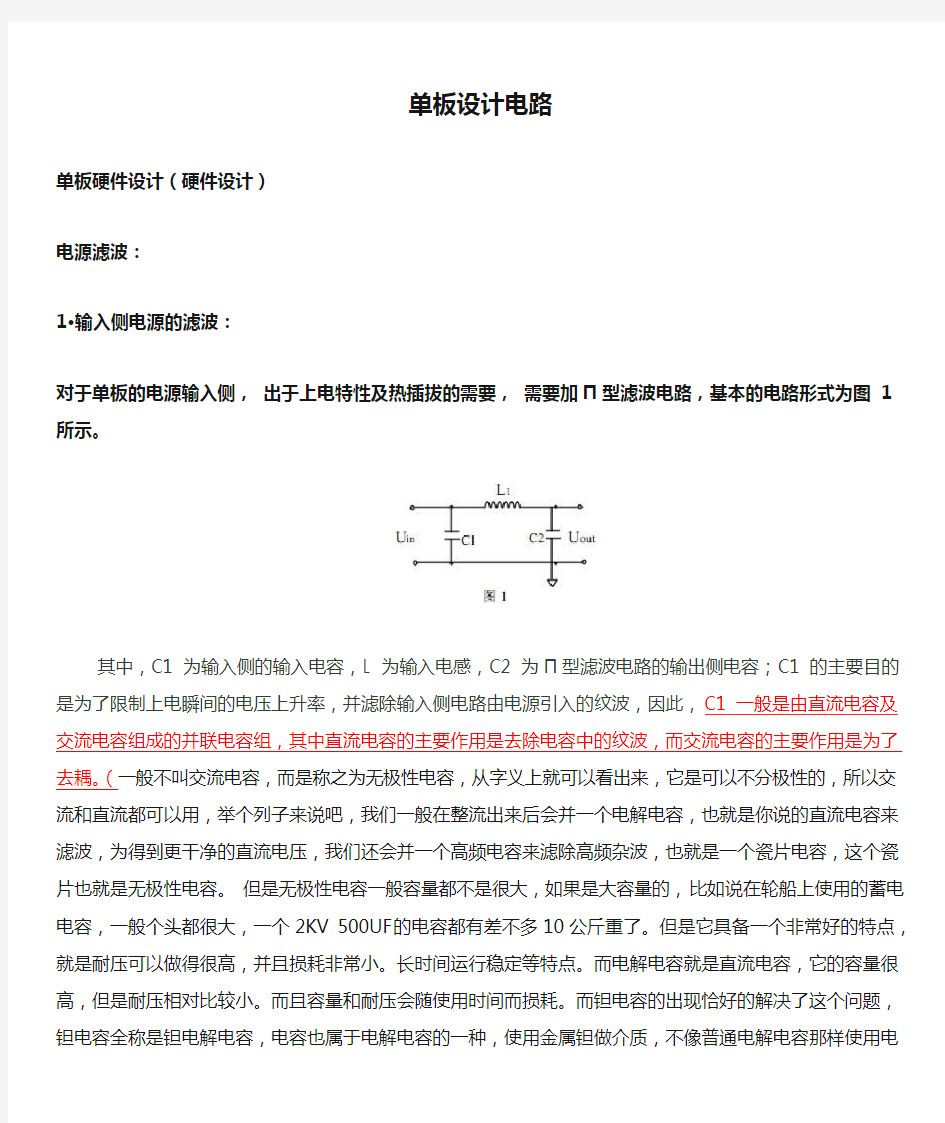

对于单板的电源输入侧,出于上电特性及热插拔的需要,需要加П型滤波电路,基本的电路形式为图1所示。

其中,C1 为输入侧的输入电容,L 为输入电感,C2 为П型滤波电路的输出侧电容;C1 的主要目的是为了限制上电瞬间的电压上升率,并滤除输入侧电路由电源引入的纹波,因此,C1 一般是由直流电容及交流电容组成的并联电容组,其中直流电容的主要作用是去除电容中的纹波,而交流电容的主要作用是为了去耦。(一般不叫交流电容,而是称之为无极性电容,从字义上就可以看出来,它是可以不分极性的,所以交流和直流都可以用,举个列子来说吧,我们一般在整流出来后会并一个电解电容,也就是你说的直流电容来滤波,为得到更干净的直流电压,我们还会并一个高频电容来滤除高频杂波,也就是一个瓷片电容,这个瓷片也就是无极性电容。但是无极性电容一般容量都不是很大,如果是大容量的,比如说在轮船上使用的蓄电电容,一般个头都很大,一个2KV 500UF的电容都有差不多10公斤重了。但是它具备一个非常好的特点,就是耐压可以做得很高,并且损耗非常小。长时间运行稳定等特点。而电解电容就是直流电容,它的容量很高,但是耐压相对比较小。而且容量和耐压会随使用时间而损耗。而钽电容的出现恰好的解决了这个问题,钽电容全称是钽电解电容,电容也属于电解电容的一种,使用金属钽做介质,不像普通电解电容那样使用电解液,,钽电容不需像普通电解电容那样使用镀了铝膜的电容纸烧制,电阻本身几乎没有电感,但也限制了它的容量。此外,钽电容内部没有电解液,很适合在高温下工作。钽电容的特点是寿命长、电容器耐高温、准确度高、滤高频改波性能极好,不过容量较小、价格也比铝电容贵,而且耐电压及电流能力较弱。三极管它被应用于大容量滤波的地方,像CPU插槽附近就看到钽电容的身影,多同陶瓷电容,电解电容配合使用或是应用于电压、钽电容电流不大的地方。)

从参数及器件选择上,输入侧一般选取钽电容,去耦电容的值为0.01uf ~1uf之间,针式或贴片均可,但从生产工艺的角度,则以选取贴片为佳,推荐的参数为直流电容10uf,交流电容0.1uf。

电感的作用为抑制电流变化率,电感越大,抑制效果越好,但同时电感太大时的上电特性不好,上电及下电时,电感两端会产生反电势,这样会对后面的负载产生影响,故参数不宜过大,因而推荐的参数为10uH。

输出侧的电容不仅要完成去耦及滤纹波的作用,而且还须维持滤波后电平不受电感反电势的影响,兼顾考虑板内负载大小及板内其他去耦电容的数量,推荐参数为直流电容10uf,交流电容0.01~1uf。

带电插拔座

带电插拔座的特性是先使地线连接,然后电源部分再上电,这样使得热插拔的上电过程有序,避免了电源上电不均衡所带来的冲击。

而在系统调试中,一些单板的热插拔成为了一种经常且必要的行为,而热插拔所带来的电流及电压冲击是极其巨大的,这时对单板的损伤是由电流及电压变化率过快所造成的,而对系统的冲击是由负载的突变造成的,因此,遏制电流、电压变化率,减轻负载突变是热插拔的先决条件,但单靠П型滤波电路是不够的,这样需要有热插拔的单板必须加带电插拔座。

上下拉电阻:

1·上拉电阻的选取原则:

A·提高灌电流的能力:

单板内部的器件功耗及驱动能力各不相同,这样在器件连接时的灌电流能力不尽相同,连接上会有驱动问题,此时需要加上拉电阻。B·电平兼容:

板内或板间器件选取各不相同,信号电平特性各不相同,出于兼容性的考虑,须加上拉电阻以保证兼容性。

C·电平稳态的特性:

个别器件在上电时要求某些管脚的初始电平固定为高,此时必须加上拉电阻以保证器件能够正常的工作。

D·器件及参数选取:

对于A,B,一般的上拉电阻选取2K~1M 欧姆,视负载情况而定,重负载时电阻应选取靠近下限,轻负载时选取上限,这里的负载以器件功耗指标来确定;对于上述C 的情况,则以该种器件的数据特性来决定。器件一般以金属膜的电阻或阻排为准。

2·下拉电阻的选取原则:

A·电平兼容:

板内或板间器件选取各不相同,信号电平特性各不相同,出于兼容性的考虑,须加下拉电阻以保证兼容性。

B·端接:

板内或板间的信号频率较高或信号上升沿较陡时,需要加端接电阻下拉到地,一般此时经常性的会再串入一个适当的电容。

C·电平稳态特性:

个别器件在上电时要求某些管脚的初试电平固定为低,此时必须加下拉电阻以保证器件能够正常的工作。

D·器件及参数选取:

对于A,下拉电阻一般选取1K~100K欧姆,视负载电平情况而定,CMOS 电平的负载,电阻应选取下限,TTL 电平时选取上限,这里的电平以负载指标来确定;对于上述 B 的情况,一般选取75~150 欧姆的电阻;对于上述C 的情况,则以该种器件的数据特性来决定;器件一般以金属膜的电阻或阻排为准。

ID的标准电路

ID 即为单板的板位信号,一般用来作邮箱地址译码选择,ID 信号在母板上接VCC 或GND,所以在单板上需作处理,典型电路如下:

高速时钟线设计

在PCB 布线中对高速时钟信号线,应少打过孔,减少线径变化层次,维持线宽一致性,不用T 型接头分支,增加时钟线与其它线的间距,减少平行走线,条件允许的情况下,在时钟线两侧加上地线隔离。另外可采用终端匹配技术消除反射。

(1)始端串阻

在驱动端,加一个小阻值串阻,反射将发生在负载端,目的是确保反射波不会从源端再反射回来。串阻的值须满足下列等式:Rs≥Z T--Tout

Rs--串阻 Z T-线的特性阻抗 Rout-源端输出阻抗

串阻方式对每根时钟线只需一个电阻,几乎没有直流功耗,而且电阻还起着限流作用,减小地线反冲。但是反射仍然有可能发生,沿线也将存在中间电压,因此,这种方式不适合分布式负载。另外,高的电阻值还会减少时钟波形的幅度和增加上升时间(在驱动端的接口芯片应为74AC16244 系列芯片)。

(2)终端并联AC 方式

在负载端并联一个RC,电容值的选取一定要非常小心,它的值必须大得能够吸收传输波的能量,但又一定要小得不会损害信号的上升时间,通常用小于50PF的电容。电阻值RL大约等于ZT(几十欧姆左右)。

并接RL方式对时钟线来说很少采用,对信号的上升时间损害较大,但它没有DC 功耗,能够消除长线的反射。

总的来说,终端匹配技术,常用来防止电压反射,减小上冲和下冲,防止时钟错误和损害片子。对一个系统来说,可选的终端匹配技术有很多,但要确保终端元件尽量靠近源端(串阻)或靠近负载端(并接RC),这样可以减小诱导电感,使匹配有效。

接口驱动及支持芯片

这里所说的接口主要是指总线(地址总线,数据总线等),从驱动能力和速度上综合考虑,对地址总线、控制总线和时钟信号等统一采用TI 公司的74AC16244;对双向的数据总线采用TI公司的74AC16245。

禁止选用74FCT16244 或74FCT16245系列芯片。

复位电路

复位电路采用AD公司的复位电路芯片ADM708,常用电路如下:

/MR 为复位信号输入端,低电平有效。它可以直接和手动复位开关相连,也可以接由逻辑电路产生的软复位信号,或二者的组合。Watchdog 电路

根据清除Watchdog 方法的不同,常用到两种Watchdog 电路。

1)利用并行口某一位对Watchdog 进行清除,电路原理如下:

这种电路的特点是对Watchdog 不能进行开、关,CTL 脚为高或为低电平超过一定时间就会引起Watchdog 触发,避免了因CPU死机Watchdog造成被长期清除的现象。

2)Watchdog占用CPU的地址空间,电路原理如下:

这种电路的特点是对Watchdog 可以灵活地进行开、关。并且只要Watchdog 打开,如果没有定时清Watchdog,就一定会造成Watchdog 触发,不会出现Watchdog 无法触发的现象。

电容滤波是有频段的,很多人以为电容是越大越好,其实不然,每个电容有一定的滤波频段,大电容滤低频,小电容滤高频,主要是根据电容的谐振频点来决定,电容在谐振频率点处有最佳的滤波效果!在以谐振点为中心的一段频段之内有较好的滤波效果,其他部分滤波效果不佳!电容的谐振点与电容的容值以及ESL(等效串联电感)相关,具体大家可以查一下网上资料,以及会议学校学习串联谐振电路的理论分析就会知道!通常我们建议在电源端口增加UF级别电容来滤波几百KHZ到5MHZ之间的差模干扰,原因就是UF级别电容谐振点在1MHZ左右。另外建议加在高频数字电路上我们建议加1nF贴片电容,原因就是1nf电容的谐振频率在100MHZ之间,不同厂家

谐振频点有所不同,这样比较好滤波几十MHZ到200MHZ干扰,有利与EMI问题解决!

电容作用

1)滤波

滤波是电容的作用中很重要的一部分。几乎所有的电源电路中都会用到。从理论上(即假设电容为纯电容)说,电容越大,阻抗越小,通过的频率也越高。但实际上超过1uF的电容大多为电解电容,有很大的电感成份,所以频率高后反而阻抗会增大。有时会看到有一个电容量较大电解电容并联了一个小电容,这时大电容通低频,小电容通高频。电容的作用就是通高阻低,通高频阻低频。电容越大低频越容易通过,电容越大高频越容易通过。具体用在滤波中,大电容(1000uF)滤低频,小电容(20pF)滤高频。

曾有网友将滤波电容比作“水塘”。由于电容的两端电压不会突变,由此可知,信号频率越高则衰减越大,可很形象的说电容像个水塘,不会因几滴水的加入或蒸发而引起水量的变化。它把电压的变动转化为电流的变化,频率越高,峰值电流就越大,从而缓冲了电压。滤波就是充电,放电的过程

2)旁路

旁路电容是为本地器件提供能量的储能器件,它能使稳压器的输出均匀化,降低负载需求。就像小型可充电电池一样,旁路电容能够被充电,并向器件进行放电。为尽量减少阻抗,旁路电容要尽量靠近负载器件的供电电源管脚和地管脚。这能够很好地防止输入值过大而导致的地电位抬高和噪声。地弹是地连接处在通过大电流毛刺时的电压降。

3)去藕

去藕,又称解藕。从电路来说,总是可以区分为驱动的源和被驱动的负载。如果负载电容比较大,驱动电路要把电容充电、放电,才能完成信号的跳变,在上升沿比较陡峭的时候,电流比较大,这样驱动的电流就会吸收很大的电源电流,由于电路中的电感,电阻(特别是芯片管脚上的电感,会产生反弹),这种电流相对于正常情况来说实际上就是一种噪声,会影响前级的正常工作。这就是耦合。去藕电容就是起到一个电池的作用,满足驱动电路电流的变化,避免相互间的耦合干扰。将旁路电容和去藕电容结合起来将更容易理解。旁路电容实际也是去藕合的,只是旁路电容一般是指高频旁路,也就是给高频的开关噪声提高一条低阻抗泄防途径。高频旁路电容一般比较小,根据谐振频率一般是0.1u,0.01u等,而去耦合电容一般比较大,是10uF或者更大,依据电路中分布参数,以及驱动电流的变化大小来确定。旁路是把输入信号中的干扰作为滤除对象,而去耦是把输出信号的干扰作为滤除对象,防止干扰信号返回电源。这应该是他们的本质区别。

去耦电路也称退藕电路!是为消除放大器级间自激回授因起的阻塞振荡而设置的!通常是由LC,RC.C 等接地回路组成.集成电路的接地退藕电容就是此意! 去耦电路也称退藕电路!是为消除放大器级间自激回授因起的阻塞振荡而设置的!通常是由LC,RC.C等接地回路组成.集成电路的接地退藕电容就是此意!

4)储能

储能型电容器通过整流器收集电荷,并将存储的能量通过变换器引线传送至电源的输出端。电压额定值为40~450VDC、电容值在220~150 000uF之间的铝电解电容器(如EPCOS公司的B43504或B43505)是较为常用的。根据不同的电源要求,器件有时会采用串联、并联或其组合的形式,对于功率级超过10KW的电源,通常采用体积较大的罐形螺旋端子电容器。

2、应用于信号电路,主要完成耦合、振荡/同步及时间常数的作用:

1)耦合

举个例子来讲,晶体管放大器发射极有一个自给偏压电阻,它同时又使信号产生压降反馈到输入端形成了输入输出信号耦合,这个电阻就是产生了耦合的元件,如果在这个电阻两端并联一个电容,由于适当容量的电容器对交流信号较小的阻抗,这样就减小了电阻产生的耦合效应,故称此电容为去耦电容。

2)振荡/同步

包括RC、LC振荡器及晶体的负载电容都属于这一范畴。

3)时间常数

这就是常见的R、C 串联构成的积分电路。当输入信号电压加在输入端时,电容(C)上的电压逐渐上升。而其充电电流则随着电压的上升而减小。电流通过电阻(R)、电容(C)的特性通过下面的公式描述:

i = (V/R)e-(t/CR)

回答者:hzqh1024|六级| 2009-9-22 09:20 滤波:多用于直流电路,引入滤波电容的原因是要获得平滑稳定的电压,因为电容两端的电压不能突变,所以它能抑制电压的波动,使电压变得平稳光滑。

去耦:也叫退耦,主要作用有两个:1、去除器件之间的交流射频耦合。它能将器件的电源端上瞬间的尖峰、毛刺对地短路掉。理论上,频率越高,需要的去耦电容越小。

旁路:旁路电容的作用是将回路中不需要的交流信号对地短路掉。

你的说法理论上没有错,但是几乎没有人去这么说。

电容在耦合的时候当然是串联在电路中的,如果它并联在器件之间,那到底是谁和谁耦合?去耦当然是并联在器件的两端,注明:电源端和地线,在具体运用的时候记得电容要尽量靠近电源端,去耦效果好,这是经验。旁路一般是把电阻和电容并联在一起,然后串联在某个回路中,通常这么用。

这个问题没有具体的答案。很难计算。但理论上肯定是频率越高需要的电容越小的,因为频率越高,电容的容抗越小,电路中的交流干扰成分对地短路的程度越高,也就是衰减越大,这是我们想要的,但在实际的运用中,同样的频率,用0.1uF的电容和用0.01uF的电容效果几乎是一样的,谁也没办法解释,但通常有经验的工程师都喜欢用0.1uF,记住就可以了。

在晶振两端对地接电容是为了校正时钟波形。晶振和集成电路内部的电路组成震荡器,这两个小电容就是配合这个振荡器工作用的,也可以说是振荡器的一部分。12M的晶振不一定非要用20P的,具体用多大的电容取决于你的芯片,比如51单片机要30pF,AVR单片机要22pF,这个和晶振的频率没有关系的。

问题四后面的那句话没有分析明白,请说的清楚一点,你模拟的电路中有晶振么?有晶振的话就不用任何输入波形,没有的话直接给12M的方波信号源就可以了,但是要在XTAL1和XTAL2中选一个,这两个中肯定有一个可以直接输入外部之中频率,具体哪一个,你需要查一下器件资料,直接用12M方波的信号源接到这个引脚上就可以了。

标签:电容

关于滤波电容、去耦电容、旁路电容作用

滤波电容用在电源整流电路中,用来滤除交流成分。使输出的直流更平滑。

去耦电容用在放大电路中不需要交流的地方,用来消除自激,使放大器稳定工作。

旁路电容用在有电阻连接时,接在电阻两端使交流信号顺利通过。

1.关于去耦电容蓄能作用的理解

1)去耦电容主要是去除高频如RF信号的干扰,干扰的进入方式是通过电磁辐射。

而实际上,芯片附近的电容还有蓄能的作用,这是第二位的。

你可以把总电源看作密云水库,我们大楼内的家家户户都需要供水,

这时候,水不是直接来自于水库,那样距离太远了,

等水过来,我们已经渴的不行了。

实际水是来自于大楼顶上的水塔,水塔其实是一个buffer的作用。

如果微观来看,高频器件在工作的时候,其电流是不连续的,而且频率很高,

而器件VCC到总电源有一段距离,即便距离不长,在频率很高的情况下,

阻抗Z=i*wL+R,线路的电感影响也会非常大,

会导致器件在需要电流的时候,不能被及时供给。

而去耦电容可以弥补此不足。

这也是为什么很多电路板在高频器件VCC管脚处放置小电容的原因之一

(在vcc引脚上通常并联一个去藕电容,这样交流分量就从这个电容接地。)

2)有源器件在开关时产生的高频开关噪声将沿着电源线传播。去耦电容的主要功能就是提供一个局部的直流电源给有源器件,以减少开关噪声在板上的传播和将噪声引导到地

2.旁路电容和去耦电容的区别

去耦:去除在器件切换时从高频器件进入到配电网络中的RF能量。去耦电容还可以为器件供局部化的DC电压源,它在减少跨板浪涌电流方面特别有用。

旁路:从元件或电缆中转移出不想要的共模RF能量。这主要是通过产生AC旁路消除无意的能量进入敏感的部分,另外还可以提供基带滤波功能(带宽受限)。

我们经常可以看到,在电源和地之间连接着去耦电容,它有三个方面的作用:一是作为本集成电路的蓄能电容;二是滤除该器件产生的高频噪声,切断其通过供电回路进行传播的通路;三是防止电源携带的噪声对电路构成干扰。

在电子电路中,去耦电容和旁路电容都是起到抗干扰的作用,电容所处的位置不同,称呼就不一样了。对于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除,而去耦(decoupling)电容也称退耦电容,是把输出信号的干扰作为滤除对象。

滤波电容用在电源整流电路中,用来滤除交流成分。使输出的直流更平滑。

去耦电容用在放大电路中不需要交流的地方,用来消除自激,使放大器稳定工作。

耦合电容隔直流通交流

旁路电容用在有电阻连接时,接在电阻两端使交流信号顺利通过。

滤波电容用在电源上,使电源更平滑,没有杂波;

去耦电容用在直流信号反馈上,去掉交流耦合信号;

旁路电容用在直流通路连接时提高交流信号通过率的。

什么是整流:

整流:利用二极管的单相导电性,将交流电改变为单向脉动的直流电的过程。

交流电变直流电叫整流.整流电路由整流变压器,半导体器件-二极管或可控硅和滤波器等组成.

整流二极管:一种将交流电能转变为直流电能的半导体器件。通常它包含一个PN结,有阳极和阴极两个端子。其结构如图1所示。P区的载流子是空穴,N区的载流子是电子,在P区和N区间形成一定的位垒。外加使P区相对N区为正的电压时,位垒降低,位垒两侧附近产生储存载流子,能通过大电流,具有低的电压降(典型值为0.7V),称为正向导通状态。若加相反的电压,使位垒增加,可承受高的反向电压,流过很小的反向电流(称反向漏电流),称为反向阻断状态。整流二极管具有明显的单向导电性,其伏安特性和电路符号如图2所示。整流二极管可用半导体锗或硅等材料制造。硅整流二极管的击穿电压高,反向漏电流小,高温性能良好。通常高压大功率整流二极管都用高纯单晶硅制造。这种器件的结面积较大,能通过较大电流(可达上千安),但工作频率不高,一般在几十千赫以下。整流二极管主要用于各种低频整流电路。整流桥:

一:成本节约

现象一:这些拉高/拉低的电阻用多大的阻值关系不大,就选个整数5K吧

点评:市场上不存在5K的阻值,最接近的是4.99K(精度1%),其次是5.1K(精度5%),其成本分别比精度为20%的4.7K高4倍和2倍。20%精度的电阻阻值只有1、1.5、2.2、3.3、4.7、6.8几个类别(含10的整数倍);类似地,20%精度的电容也只有以上几种值,如果选了其它的值就必须使用更高的精度,成本就翻了几倍,却不能带来任何好处。

现象二:面板上的指示灯选什么颜色呢?我觉得蓝色比较特别,就选它吧

点评:其它红绿黄橙等颜色的不管大小(5MM以下)封装如何,都已成熟了几十年,价格一般都在5毛钱以下,而蓝色却是近三四年才发明的东西,技术成熟度和供货稳定度都较差,价格却要贵四五倍。目前蓝色指示灯只用在不能用其它颜色替代的场合,如显示视频信号

等。

现象三:这点逻辑用74XX的门电路搭也行,但太土,还是用CPLD吧,显得高档多了点评:74XX的门电路只几毛钱,而CPLD至少也得几十块,(GAL/PAL虽然只几块钱,但公司不推荐使用)。成本提高了N倍不说,还给生产、文档等工作增添数倍的工作。

现象四:我们的系统要求这么高,包括MEM、CPU、FPGA等所有的芯片都要选最快的点评:在一个高速系统中并不是每一部分都工作在高速状态,而器件速度每提高一个等级,价格差不多要翻倍,另外还给信号完整性问题带来极大的负面影响。

现象五:这板子的PCB设计要求不高,就用细一点的线,自动布吧

点评:自动布线必然要占用更大的PCB面积,同时产生比手动布线多好多倍的过孔,在批量很大的产品中,PCB 厂家降价所考虑的因素除了商务因素外,就是线宽和过孔数量,它们分别影响到PCB的成品率和钻头的消耗数量,节约了供应商的成本,也就给降价找到了理由。

现象六:程序只要稳定就可以了,代码长一点,效率低一点不是关键

点评:CPU的速度和存储器的空间都是用钱买来的,如果写代码时多花几天时间提高一下程序效率,那么从降低CPU主频和减少存储器容量所节约的成本绝对是划算的。CPLD/FPGA设计也类似。

二:低功耗设计

现象一:我们这系统是220V供电,就不用在乎功耗问题了

点评:低功耗设计并不仅仅是为了省电,更多的好处在于降低了电源模块及散热系统的成本、由于电流的减小也减少了电磁辐射和热噪声的干扰。随着设备温度的降低,器件寿命则相应延长(半导体器件的工作温度每提高10度,寿命则缩短一半)

现象二:这些总线信号都用电阻拉一下,感觉放心些

点评:信号需要上下拉的原因很多,但也不是个个都要拉。上下拉电阻拉一个单纯的输入信号,电流也就几十微安以下,但拉一个被驱动了的信号,其电流将达毫安级,现在的系统常常是地址数据各32位,可能还有244/245隔离后的总线及其它信号,都上拉的话,几瓦的功耗就耗在这些电阻上了(不要用8毛钱一度电的观念来对待这几瓦的功耗)。

现象三:CPU和FPGA的这些不用的I/O口怎么处理呢?先让它空着吧,以后再说

点评:不用的I/O口如果悬空的话,受外界的一点点干扰就可能成为反复振荡的输入信号了,而MOS器件的功耗基本取决于门电路的翻转次数。如果把它上拉的话,每个引脚也会有微安级的电流,所以最好的办法是设成输出(当然外面不能接其它有驱动的信号)

现象四:这款FPGA还剩这么多门用不完,可尽情发挥吧

点评:FGPA的功耗与被使用的触发器数量及其翻转次数成正比,所以同一型号的FPGA在不同电路不同时刻的功耗可能相差100倍。尽量减少高速翻转的触发器数量是降低FPGA功耗的根本方法。

现象五:这些小芯片的功耗都很低,不用考虑

点评:对于内部不太复杂的芯片功耗是很难确定的,它主要由引脚上的电流确定,一个ABT16244,没有负载的话耗电大概不到1毫安,但它的指标是每个脚可驱动60毫安的负载(如匹配几十欧姆的电阻),即满负荷的功耗最大可达60*16=960mA,当然只是电源电流这么大,热量都落到负载身上了。

现象六:存储器有这么多控制信号,我这块板子只需要用OE和WE信号就可以了,片选就接地吧,这样读操作时数据出来得快多了。

点评:大部分存储器的功耗在片选有效时(不论OE和WE如何)将比片选无效时大100倍以上,所以应尽可能使

用CS来控制芯片,并且在满足其它要求的情况下尽可能缩短片选脉冲的宽度。

现象七:这些信号怎么都有过冲啊?只要匹配得好,就可消除了

点评:除了少数特定信号外(如100BASE-T、CML),都是有过冲的,只要不是很大,并不一定都需要匹配,即使匹配也并非要匹配得最好。象TTL的输出阻抗不到50欧姆,有的甚至20欧姆,如果也用这么大的匹配电阻的话,那电流就非常大了,功耗是无法接受的,另外信号幅度也将小得不能用,再说一般信号在输出高电平和输出低电平时的输出阻抗并不相同,也没办法做到完全匹配。所以对TTL、LVDS、422等信号的匹配只要做到过冲可以接受即可。

现象八:降低功耗都是硬件人员的事,与软件没关系

点评:硬件只是搭个舞台,唱戏的却是软件,总线上几乎每一个芯片的访问、每一个信号的翻转差不多都由软件控制的,如果软件能减少外存的访问次数(多使用寄存器变量、多使用内部CACHE等)、及时响应中断(中断往往是低电平有效并带有上拉电阻)及其它争对具体单板的特定措施都将对降低功耗作出很大的献。

三:系统效率

现象一:这主频100M的CPU只能处理70%,换200M主频的就没事了

点评:系统的处理能力牵涉到多种多样的因素,在通信业务中其瓶颈一般都在存储器上,CPU再快,外部访问快不起来也是徒劳。

现象二:CPU用大一点的CACHE,就应该快了

点评:CACHE的增大,并不一定就导致系统性能的提高,在某些情况下关闭CACHE反而比使用CACHE还快。原因是搬到CACHE中的数据必须得到多次重复使用才会提高系统效率。所以在通信系统中一般只打开指令CACHE,数据CACHE即使打开也只局限在部分存储空间,如堆栈部分。同时也要求程序设计要兼顾CACHE的容量及块大小,这涉及到关键代码循环体的长度及跳转范围,如果一个循环刚好比CACHE大那么一点点,又在反复循环的话,那就惨了。

现象三:这么多任务到底是用中断还是用查询呢?还是中断快些吧

点评:中断的实时性强,但不一定快。如果中断任务特别多的话,这个没退出来,后面又接踵而至,一会儿系统就将崩溃了。如果任务数量多但很频繁的话,CPU的很大精力都用在进出中断的开销上,系统效率极为低下,如果改用查询方式反而可极大提高效率,但查询有时不能满足实时性要求,所以最好的办法是在中断中查询,即进一次中断就把积累的所有任务都处理完再退出。

现象四:存储器接口的时序都是厂家默认的配置,不用修改的

点评:BSP对存储器接口设置的默认值都是按最保守的参数设置的,在实际应用中应结合总线工作频率和等待周期等参数进行合理调配。有时把频率降低反而可提高效率,如RAM的存取周期是70ns,总线频率为40M时,设3个周期的存取时间,即75ns即可;若总线频率为50M时,必须设为4个周期,实际存取时间却放慢到了80ns。现象五:一个CPU处理不过来,就用两个分布处理,处理能力可提高一倍

点评:对于搬砖头来说,两个人应该比一个人的效率高一倍;对于作画来说,多一个人只能帮倒忙。使用几个CPU 需对业务有较多的了解后才能确定,尽量减少两个CPU间协调的代价,使1+1尽可能接近2,千万别小于1。

现象六:这个CPU带有DMA模块,用它来搬数据肯定快

点评:真正的DMA是由硬件抢占总线后同时启动两端设备,在一个周期内这边读,那边些。但很多嵌入CPU内的DMA只是模拟而已,启动每一次DMA之前要做不少准备工作(设起始地址和长度等),在传输时往往是先读到芯片内暂存,然后再写出去,即搬一次数据需两个时钟周期,比软件来搬要快一些(不需要取指令,没有循环跳转等额外工作),但如果一次只搬几个字节,还要做一堆准备工作,一般还涉及函数调用,效率并不高。所以这种DMA只对大数据块才适用。

四:信号完整性

现象一:这些信号都经过仿真了,绝对没问题

点评:仿真模型不可能与实物一模一样,连不同批次加工的实物都有差别,就更别说模型了。再说实际情况千差万别,仿真也不可能穷举所有可能,尤其是串扰。曾经有一教训是某单板只有特定长度的包极易丢包,最后的原因是长度域的值是0xFF,当这个数据出现在总线上时,干扰了相邻的WE信号,导致写不进RAM。其它数据也会对WE产生干扰,但干扰在可接受的范围内,可是当8位总线同时由0边1时,附近的信号就招架不住了。结论是仿真结果仅供参考,还应留有足够的余量。

现象二:100M的数据总线应该算高频信号,至于这个时钟信号频率才8K,问题不大

点评:数据总线的值一般是由控制信号或时钟信号的某个边沿来采样的,只要争对这个边沿保持足够的建立时间和保持时间即可,此范围之外有干扰也罢过冲也罢都不会有多大影响(当然过冲最好不要超过芯片所能承受的最

大电压值),但时钟信号不管频率多低(其实频谱范围是很宽的),它的边沿才是关键的,必须保证其单调性,并且跳变时间需在一定范围内。

现象三:既然是数字信号,边沿当然是越陡越好

点评:边沿越陡,其频谱范围就越宽,高频部分的能量就越大;频率越高的信号就越容易辐射(如微波电台可做成手机,而长波电台很多国家都做不出来),也就越容易干扰别的信号,而自身在导线上的传输质量却变得越差,因此能用低速芯片的尽量使用低速芯片,。

现象四:为保证干净的电源,去偶电容是多多益善

点评:总的来说去偶电容越多电源当然会更平稳,但太多了也有不利因素:浪费成本、布线困难、上电冲击电流太大等。去偶电容的设计关键是要选对容量并且放对地方,一般的芯片手册都有争对去偶电容的设计参考,最好按手册去做。

现象五:信号匹配真麻烦,如何才能匹配好呢?

点评:总的原则是当信号在导线上的传输时间超过其跳变时间时,信号的反射问题才显得重要。信号产生反射的原因是线路阻抗的不均匀造成的,匹配的目的就是为了使驱动端、负载端及传输线的阻抗变得接近,但能否匹配得好,与信号线在PCB上的拓扑结构也有很大关系,传输线上的一条分支、一个过孔、一个拐角、一个接插件、不同位置与地线距离的改变等都将使阻抗产生变化,而且这些因素将使反射波形变得异常复杂,很难匹配,因此高速信号仅使用点到点的方式,尽可能地减少过孔、拐角等问题。

五:可靠性设计

现象一:这块单板已小批量生产了,经过长时间测试没发现任何问题

点评:硬件设计和芯片应用必须符合相关规范,尤其是芯片手册中提到的所有参数(耐压、I/O电平范围、电流、时序、温度PCB布线、电源质量等),不能光靠试验来验证。公司有不少产品都有过惨痛的教训,产品卖了一两年,IC厂家换了个生产线,咱们的板子就不转了,原因就是人家的芯片参数发生了点变化,但并没有超出手册的范围。如果你以手册为准,那他怎么变化都不怕,如果参数变得超出手册范围了还可找他索赔(假如这时你的板子还能转,那你的可靠性就更牛了)。

现象二:这部分电路只要要求软件这样设计就不会有问题

点评:硬件上很多电气特性直接受软件控制,但软件是经常发生意外的,程序跑飞了之后无法预料会有什么操作。设计者应确保不论软件做什么样的操作硬件都不应在短时间内发生永久性损坏。

现象三:用户操作错误发生问题就不能怪我了

点评:要求用户严格按手册操作是没错的,但用户是人,就有犯错的时候,不能说碰错一个键就死机,插错一个插头就烧板子。所以对用户可能犯的各种错误必须加以保护。

现象四:这板子坏的原因是对端的板子出问题了,也不是我的责任

点评:对于各种对外的硬件接口应有足够的兼容性,不能因为对方信号不正常,你就歇着了。它不正常只应影响到与其有关的那部分功能,而其它功能应能正常工作,不应彻底罢工,甚至永久损坏,而且一旦接口恢复,你也应立即恢复正常。

单板/驱动软件详细设计说明书 CJ-7.3-54 v1.0 普天信息技术研究院 200X年月XX日

修订历史记录

编制 审查 审核 批准 文档评审负责人:参加评审人员:

目录 1引言 (4) 1.1编写目的 (4) 1.2背景 (4) 1.3定义 (4) 1.4设计依据 (5) 2软件系统结构 (5) 2.1功能需求 (5) 2.2子模块划分 (6) 2.3子模块间关系 (13) 3公共数据结构 (14) 4程序设计说明 (14) 4.1程序1设计说明 (14) 4.1.1程序描述 (14) 4.1.2功能 (14) 4.1.3性能 (14) 4.1.4输入 (14) 4.1.5输出 (14) 4.1.6算法 (14) 4.1.7流程 (14) 4.2程序2设计说明 (14) 5模块重用说明 (15)

1引言 1.1编写目的 〖说明编写这份软件详细设计说明书的目的〗 本文档是以RFID读卡器硬件结构为基础,以《RFID读卡器需求分析说明书》和《RFID读卡器软件概要设计说明书》为指导编写而成。本文档旨在分析RFID读卡器需求的基础上,定义各个功能模块的实现方式与具体函数,以达到实际应用的目的。同时也为RFID读卡器后期的软件升级和维护提供便利。 1.2背景 〖说明待开发软件(子)系统的名称和此软件(子)系统所属大系统的名称; 说明任务的来源(开发背景和市场背景)等;该软件(子)系统与大系统中其他子系统的关系。〗 RFID读卡器通常使用无线电调制方式和卡片进行信息交换,通常根据以下几种标准来设计,即ISO/IEC10536标准、ISO/IEC14443标准、ISO/IEC15693标准。 根据ISO/IEC10536标准设计的卡称为"密耦合卡",对应的阅读器也相应遵循ISO/IEC10536标准设计;根据ISO/IEC14443标准设计的卡是近耦合卡,对应的阅读器遵循ISO/IEC14443标准设计;根据ISO/IEC15693标准设计的卡是遥耦合卡,对应的阅读器遵循ISO/IEC15693标准设计。遥耦合卡比近耦合卡具有更远的读卡距离,但二者均采用13.56MHz工作频率,均具有防冲突机制。RFID读卡器的设计还应该考虑具体的行业应用规范,比如金融行业的中国银联《非接触IC卡读卡器技术规范》或支持某些特殊应用协议,比如PC/SC协议。 本产品是针对金融服务业开发的RFID读卡器,配合我们自主研发的大容量智能存储卡的推广应用。 本文档是在RFID读卡器硬件设计、外观设计已经完成,系统需求与概要设计已经确定的背景下完成的。 1.3定义 〖列出本文档中所用到的专门术语的定义和缩写词的原意〗 RFID R adio Frequency Identification 无线射频身份识别 APDU Application Protocol Data Unit应用协议数据单元

电子技术课程设计 题目: 班级: 姓名: 合作者:

数字电子钟计时系统 一、设计要求 用中、小规模集成电路设计一台能显示时、分、秒的数字电子钟,基本要求如下: 1、采用LED显示累计时间“时”、“分”、“秒”。 2、具有校时功能。 二、设计方案 数字电子钟主要由振荡器、分频器、计数器、译码器、显示器等几部分组成,其整体框图为 其中,秒信号发生器为:

由石英晶体发出32768Hz的振荡信号经过分频器,即CD4060——14级串行二进制计数器/分频器和振荡器,输出2Hz 的振荡信号传入D触发器,经过2分频变为秒信号输出。 校时电路为: 当K1开启时,与非门一端为秒信号另一端为高电位,输出即为秒信号秒计数器正常工作,当K1闭合,秒信号输出总为0,实现秒暂停。 当K2/K3开启时,分信号/时信号输入由秒计数器输出信号及高电平决定,所以输出信号即为分信号/时信号,当K2/K3闭合时,秒信号决定分信号/时信号输出,分信号/时信号输出与秒信号频率一致, 以实现分信号/时信号的加速校时。 秒、分计数器——60进制

首先,调节CD4029的使能端,使其为十进制加法计数器。将输入信号脉冲输入第一个 计数器(个位计数器)计十个数之后将,进位输出输给下一个计数器(十位计数器)的进位 输入实现十秒计数。当计数器的Q1,Q2输出均为1时经过与门电路,输出高电平,作为分 脉冲或时脉冲并同时使两计数器置零。 时计数器——24进制 时脉冲 首先,调节CD4029的使能端,使其为十进制加法计数器。将输入信号脉冲输入第一个 计数器(个位计数器)计十个数之后将,进位输出输给下一个计数器(十位计数器)的进位 输入实现十秒计数。当十位计数器Q1和个位计数器Q2输出均为1时经过与门电路,输出 高电平使两计数器置零。 译码显示电路

硬件设计流程 一、硬件设计 1.1单板设计需求 单板设计之前需要明确单板的设计需求。单板的功能属性。单板的设计目的,使用场合,具体需求包括: 1.单板外部接口的种类,接口的数量,电气属性即电平标准。 2.单板内部的接口种类,电气属性。 3.单板外部输入电源大小 4.单板的尺寸 5.单板的使用场合,防护标准 若设计中需要用到CPU,需要确定设计中需要用到的FLASH大小和需求的内存的大小和CPU的处理能力。单板设计需求中需要明确单板的名字和版本并且要以文档的形式表现出来,是后续单板设计和追溯的主要依据。 单板设计需求完成之后,需要召开项目评审会,需要对设计需求说明中各类需求逐个确认。当各类需求均满足设计需要时则进入下一步。 1.2 单板设计说明 单板需求明确后,需要开始编写单板设计说明。其中需要包括单板设计所需要的各种信息如: 1.单板设计详细方案,需要具体到用到什么芯片,什么接口。 2.器件选型,器件选型需要满足设计的需求。 3.单板功耗、单板选型之后需要确定单板的功耗,为单板散热和电源设计提供依据 4.电源设计、电源设计需要包含单板中需要用到的各类电源。若相同的电源需要做隔离 的需要做需要详细指出。 5.时钟设计,单板若是用到多种时钟,则需要描述时钟的设计方法,时钟拓扑。 6.单板的实际尺寸 7.详细描述各个功能模块给出详细的设计方法 8.详细描述各接口的设计方法和接口的电气属性。 若设计模块有多种设计方法,选择在本设计中最佳的设计方案。若软件对单板中用到的器件有独特的要求,需要明确指出(如对某些制定管脚的使用情况)。除了各个功能模块之外单板设计说明中需要详细描述接口的防护方法。设计说明需要以文档的形式给出,是单板设计过程中重要的文档,其中需要包括单板的名称和单板的版本。如果有条件单板设计说明完成后项目中进行评审。 1.3原理图设计 设计说明完成之后就要开始单板的原理图设计,单板设计说明是单板原理图设计的重要依据。原理图设计之气需要确定单板设计用用到的各个器件原理图库中是否具有原理图符号,如果没有需要提前绘制。新绘制的原理图符号需要反应器件的电气属性,器件型号,最好包含品号信息,绘制完成之后将其放到相应的库中,原理图设计需要包含: 1.各个器件接口的正确电气连接。 2.原理图中的各个器件需要有单独的位号。 3.原理图中需要包含安装孔和定位孔。 4.原理图中的兼容设计或者在实际应用中不需要焊接的器件需要在原理图中明确标出。 原理图的名字需要和单板的名字一致。考虑到单板上所用器件可能会有较长的采购周

xxx 有限公司产品版本密级文档中心 产品名称:共 18页 XX 单板硬件调试和单元测试报告 (仅供内部使用 ) 拟制 : 日期:yyyy-mm-dd 审核 : 日期:yyyy-mm-dd 审核 : 日期:yyyy-mm-dd 批准 : 日期:yyyy-mm-dd

日期版本描述作者 2001-06-08 1.00 初稿完成作者名yyyy-mm-dd 1.01 修改 XXX 作者名yyyy-mm-dd 1.02 修改 XXX 作者名????????yyyy-mm-dd 2.00 修改 XXX 作者名

1概述 6 1.1基本情况介绍 6 1.2单板模块划分 6 1.3调试测试组网图 6 1.4调试时间、地点及人员 6 2调试测试用例记录 6 2.1功能部分调试 6 2.1.1模块 1 6 2.1.1.1调试用例 1 6 2.1.1.2调试用例 2 6 模块 2 6 2.1.2 2.1.3问题列表7 2.2信号质量测试用例7 电源8 2.2.1 2.2.1.1测试数据8 2.2.1.2测试波形及分析8 2.2.1.3问题列表8 逻辑信号9 2.2.2 2.2.2.1测试结果9 2.2.2.2测试波形及分析9 2.2.2.3问题列表9 2.2.3时钟信号10 2.2. 3.1测试结果10 2.2. 3.2实测波形及分析10 2.2. 3.3问题列表10 2.3时序测试用例10 2.3.1CPU 接口部分时序11 2.3.1.1测试结果11 2.3.1.2测试时序及分析11 2.3.2业务接口部分时序11 2.3.2.1测试结果11 2.3.2.2测试时序及分析12 2.3.3问题列表12 2.4失效器件原因分析12 3调试测试总结12 3.1调试测试结果12 3.2遗留问题报告13 3.3调试测试经验总结14 4其他14 5评审报告14

常用数字仪表的使用 实验内容: 1.参考“仪器操作指南”之“DS1000操作演示”,熟悉示数字波器的使用。 2.测试示波器校正信号如下参数:(请注意该信号测试时将耦合方式设置为直流耦合。 峰峰值(Vpp),最大值(Vmax),最小值(Vmin), 幅值(Vamp),周期(Prd),频率(Freq) 顶端值(Vtop),底端值(Vbase),过冲(Overshoot), 预冲(Preshoot),平均值(Average),均方根值(Vrms),即有效值 上升时间(RiseTime),下降时间(FallTime),正脉宽(+Width), 负脉宽(-Width),正占空比(+Duty),负占空比(-Duty)等参数。 3.TTL输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低 电平是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V。 请采用函数信号发生器输出一个TTL信号,要求满足如下条件: ①输出高电平为3.5V,低电平为0V的一个方波信号; ②信号频率1000Hz; 在示波器上观测该信号并记录波形数据。

集成逻辑门测试(含4个实验项目) (本实验内容选作) 一、实验目的 (1)深刻理解集成逻辑门主要参数的含义和功能。 (2)熟悉TTL 与非门和CMOS 或非门主要参数的测试方法,并通过功能测试判断器件好坏。 二、实验设备与器件 本实验设备与器件分别是: 实验设备:自制数字实验平台、双踪示波器、直流稳压电源、数字频率计、数字万用表及工具; 实验器件:74LS20两片,CC4001一片,500Ω左右电阻和10k Ω左右电阻各一只。 三、实验项目 1.TTL 与非门逻辑功能测试 按表1-1的要求测74LS20逻辑功能,将测试结果填入与非门功能测试表中(测试F=1、0时,V OH 与V OL 的值)。 2.TTL 与非门直流参数的测试 测试时取电源电压V CC =5V ;注意电流表档次,所选量程应大于器件电参数规范值。 (1)导通电源电流I CCL 。测试条件:输入端均悬空,输出端空载。测试电路按图1-1(a )连接。 (2)低电平输入电流I iL 。测试条件:被测输入端通过电流表接地,其余输入端悬空,输出空载。测试电路按图1-1(b )连接。 (3)高电平输入电流I iH 。测试条件:被测输入端通过电流表接电源(电压V CC ),其余输入端均接地,输出空载。测试电路按图1-1(c )连接。 (4)电压传输特性。测试电路按图1-2连接。按表1-2所列各输入电压值逐点进行测量,各输入电压值通过调节电位器W 取得。将测试结果在表1-2中记录,并根据实测数据,做出电压传输特性曲线。然后,从曲线上读出V OH ,V OL ,V on ,V off 和V T ,并计算V NH ,V NL 等参数。 表1-1 与非门功能测试表

****产品详细设计报告 目录 1概述 6 1.1 背景 6 1.2 产品功能描述 6 1.3 产品运行环境说明 6 1.4 重要性能指标 6 1.5 产品功耗 6 1.6 必要的预备知识(可选) 6 2 产品各单元详细说明 6 2.1 产品功能单元划分和功能描述 6 2.2 单元详细描述 7 2.2.1 单元1 7

2.2.2 单元2 7 2.2.3 单元N (8) 2.3 产品各单元间配合描述 8 2.3.1 总线设计 8 2.3.2 时钟设计 8 2.3.3 产品上电、休眠、复位设计 8 2.3.4 各单元间的时序关系 9 2.3.5 产品整体可测试性设计 9 2.3.6 软件加载方式说明 9 3 产品电源设计说明 9 3.1 产品供电原理框图 9 3.2 产品电源各功能模块详细设计 9 4 产品接口说明 10 4.1 产品单元内部接口 10 4.2 对外接口说明 10 4.3 软件接口 10 4.4 调测接口 11

5 产品可靠性、可维护性设计说明 11 5.1 产品可靠性设计 11 5.1.1 关键器件及相关信息 11 5.1.2 关键器件可靠性设计说明 11 5.1.3 关键信号时序要求 12 5.1.4 信号串扰、毛刺、过冲及保障措施: 12 5.1.5 其他重要信号及相关处理方案 12 5.1.6 机械应力 12 5.1.7 可加工性 12 5.1.8 电应力 12 5.1.9 环境应力 12 5.1.10 温度应力 13 5.2 产品可维护性设计说明 13 6 EMC、ESD、防护及安规设计说明 13 6.1 产品电源、地的分配图 13 6.2 关键器件和关键信号的EMC设计 13 6.3 防护设计 13

详细设计说明书 1.导言(Introduction) 本章对该文档的目的、功能范围、术语、相关文档、参考资料、版本更新进行说明。 1.1 目的(Purpose) 本文档的目旨在推动软件工程的规范化,使设计人员遵循统一的详细设计书写规范,节省制作文档的时间,降低系统实现的风险,做到系统设计资料的规范性与全面性,以利于系统的实现、测试、维护、版本升级等。详细设计的详细程度,应达到可以编写程序的程度。 1.2 范围(Scope) 本文档用于软件设计阶段的详细设计,它的上游(依据的基线)是《概要设计说明书》,它的下游是源程序清单及单元测试计划,并为单元测试报告提供测试依据。该范围应覆盖《概要设计说明书》中的功能点列表、性能点列表、接口列表。软件详细设计的范围是:各子系统的公用模块实现设计、专用模块实现设计、存储过程实现设计、触发器实现设计、外部接口实现设计、部门角色授权设计、其他详细设计等。 按照3层结构(B/A/S)的布局,详细设计应从下面3个方面进行。数据库服务器上的面向数据的设计:数据字典物理设计、基本表物理设计、中间表物理设计(报表设计)、临时表物理设计、视图物理设计、存储过程物理设计、触发器物理设计。应用服务器上的面向业务逻辑的设计:接口数据设计、中间件设计、数据通信传输设计、可视构件设计、非可视构件设计、角色授权设计、功能点设计(功能点列表设计)。浏览器上的面向对象的设计:录入修改界面设计、浏览查询界面设计、登录注册界面设计、信息发布界面设计。 1.3 术语定义(Terms Glossary) 术语定义,如表6-16所示。 表6-16 术语定义 1.4 参考资料(References) [1] 《概要设计说明书》 [2] 《需求分析说明书》 [3] 《软件合同》

实验一:功率的测定以及仿真 1.仿真实验目的 (1)验证各电阻的功率和电压源的功率,并且验证整个电路输出功率和吸收功率相等,即整个电路功率守恒; (2)、学习利用仿真仪表分析检验各电阻功率和对电压表电流表的运用。 2.实验原理及说明 A. 本次实验的电路图以及连接方式如图1.1所示:利用环路电流法可列出方程 B. )(36_)(31234232131=?-?++=??+R R R R V R R R i i i i l l i l 图1.1 C .电路连接好之后,按照电流表和电压表的示数,根据I U P ?=可以算出电压源的功率,再根据连接在各电阻上的功率表,读出各电阻的功率 321,,P P P ,根据4321P +++=P P P P 吸收可以算出电路吸收的功 率;根据I U P P ?==电源释放可以算出电路释放的功率。 .若释放吸收P P =,则说明整个电路吸收与释放的功率相等。 3.仿真实验的步骤与内容 按照原理图1.1所示,连接电路,如下图1.2所示 读数,如下图1.3所示我们可以得到:U=36.0V,I=9.0A,又由0 )(36_)(31234232131=?-?++=??+R R R R V R R R i i i i l l i l 计算出实 验一致。

36V I U =?=释放P ; 4321P +++=P P P P 吸收=424323222121I R I R I R I R +++=162+18+108+36=324W 由上可得,释放 吸收P P =,所以整个电路是功率守恒的R12Ω XMM1 R2 2Ω V136 V XWM1 V I XWM2 V I XWM3 V I R3 3Ω XWM4 V I R44Ω U1 DC 1e-009Ohm 0.000 A + - 图1.2 图1.3

实验一组合逻辑电路设计 一、实验目的 1、熟悉应用中小规模数字集成电路的工程技术; 2、掌握组合逻辑电路的设计方法。 二、设计步骤 对于某些对象的启动/停止或者打开/闭合等一类二值控制问题(电气工程称之为乒乓控制),往往可以抽象归纳成为逻辑问题。使用数字逻辑电路实现解决这一逻辑问题的电路系统,即可实现逻辑控制。使用小规模(SSI)数字集成电路进行组合逻辑电路设计的步骤是: 1、分析实际问题进行逻辑抽象:定义输入或输出变量并进行逻辑赋值,即确定True (1)或False (0)表示的含义。在此基础上列出逻辑真值表。 2、由真值表写出逻辑函数表达式并化简为最简式。 3、按照化简后的表达式画出逻辑函数原理图。 为了降低电路成本、便于系统安装和未来维修,有经验的工程师常常设法用尽可能少的数字集成电路种类和芯片数目来实现设计。因此2,3两步骤应统筹考虑。 4、查阅集成电路手册确定电路中所使用的芯片型号和具体的引脚连 接关系。 5、正确地焊接(连接)电路,在确认无误后上电试验,测试电路的逻辑关系是否实现真值表(解决逻辑问题)。当然,这需要解决全部有关逻辑变量的状态设定和输出逻辑状态的测试问题。值得说明,一种专门测试逻辑电平的常用工具是“逻辑笔”。 三、设计要求 请设计组合逻辑电路解决如下逻辑问题: 1、某竞技运动项目设主裁判一名,副裁判两名。比赛规则是:主裁判和至少一名副裁判判定某运动员胜利,则该运动员取胜。设计实现电子裁判机。 2、某储液罐设有大小各一个补液泵和高、中、低液位传感器。三个传感器都在页面低于其监测的位置时发出信号,否则没有信号输出。由于结构上的原因,高位传感器不会出故障;其余两个传感器在液面高于其监测位置时决不会产生错误的信号输出,但却可能在故障时发不出信号来。设计电路系统实现如下控制要求:液面达到或超过高位时补液泵全停;液面低于高位而高于中位时,小泵启动工作,大泵停止;液面低于中位而高于低位时,大泵启动工作,小泵停止;液面低于低位时,大小两泵同时启动工作。在实现上述控制要求的同时给出传感器发生故障的报警信号。

SUCHNESS 硬件设计文档 型号:GRC60定位终端 编号: 机密级别:绝密机密内部文件 部门:硬件组 拟制:XXXX年 XX月 XX日 审核:年月日 标准化:年月日 批准:年月日

文档修订历史记录

目录 1系统概述 (3) 2系统硬件设计 (3) 2.1硬件需求说明书 (3) 2.2硬件总体设计报告 (3) 2.3单板总体设计方案 (3) 2.4单板硬件详细设计 (3) 2.5单板硬件过程调试文档 (3) 2.6单板硬件测试文档 (4) 3系统软件设计 (4) 3.1单板软件详细设计 (4) 3.2单板软件过程调试报告 (4) 3.3单板系统联调报告 (4) 3.4单板软件归档详细文档 (4) 4硬件设计文档输出 (4) 4.1硬件总体方案归档详细文档 (4) 4.2硬件信息库 (5) 5需要解决的问题 (5) 6采购成本清单 (5)

1系统概述 2系统硬件设计 2.1、硬件说明书 硬件需求说明书是描写硬件开发目标,基本功能、基本配置,主要性能指标、运行环境,约束条件以及开发经费和进度等要求,它的要求依据是产品规格说明书和系统需求说明书。它是硬件总体设计和制订硬件开发计划的依据,具体编写的内容有:系统工程组网及使用说明、硬件整体系统的基本功能和主要性能指标、硬件分系统的基本功能和主要性能指标以及功能模块的划分等 2.2、硬件总体设计报告 硬件总体设计报告是根据需求说明书的要求进行总体设计后出的报告,它是硬件详细设计的依据。编写硬件总体设计报告应包含以下内容:系统总体结构及功能划分,系统逻辑框图、组成系统各功能模块的逻辑框图,电路结构图及单板组成,单板逻辑框图和电路结构图,以及可靠性、安全性、电磁兼容性讨论和硬件测试方案等 2.3、单板总体设计方案 在单板的总体设计方案确定后出此文档,单板总体设计方案应包含单板版本号,单板在整机中的位置、开发目的及主要功能,单板功能描述、单板逻辑框图及各功能模块说明,单板软件功能描述及功能模块划分、接口简单定义与相关板的关系,主要性能指标、功耗和采用标准 2.4、单板硬件详细设计 在单板硬件进入到详细设计阶段,应提交单板硬件详细设计报告。在单板硬件详细设计中应着重体现:单板逻辑框图及各功能模块详细说明,各功能模块实现方式、地址分配、控制方式、接口方式、存贮器空间、中断方式、接口管脚信号详细定义、时序说明、性能指标、指示灯说明、外接线定义、可编程器件图、功能模块说明、原理图、详细物料清单以及单板测试、调试计划。有时候一块单板的硬件和软件分别由两个开发人员开发,因此这时候单板硬件详细设计便为软件设计者提供了一个详细的指导,因此单板硬件详细设计报告至关重要。尤其是地址分配、控制方式、接口方式、中断方式是编制单板软件的基础,一定要详细写出。

- 详细设计说明书的主要内容及写作要求 编写目的 详细设计(又可称程序设计机)说明书编制的目的是说明一个软件系统各个层次中的每个程序(每个模块或子程序)的实际考虑,为程序员编写程序提供依据。 如果一个软件系统比较简单,层次很少,本文件可以不单独编写,和概要设计机说明书中不重复部分合并编写,文档名称为《软件设计说明书》。 主要内容及写作要求 详细设计说明书主要内容及写作要求如下: 1 引言 目的 。 说明编制本详细设计说明书的目的。 背景 列出本项目的任务提出者、项目负责人、系统分析员、系统设计员、程序设计员、程序员、资料员以及与本项目开展工作直接有关的人员和用户。 参考资料 A. 列出本项目经核准的任务书或合同和上级机关的批文。 B. 列出编写本设计说明书时参考的文件、资料、技术标准以及它们的作者、标题、编号、发布日期和出版单位等。 术语 列出本详细设计说明书中专门术语的定义和英文缩写词的原词组。 ; 2.软件结构 用图表(常用系统流程图的层次结构表示)的形式列出本软件的各模块和程序单元的名称以及它们的相互关系。 3 模块设计说明 模块 n结构(n是模块序号) 将概要设计产生的功能模块进行细化,形成若干个可编程的程序单元(用图表形式给出程序单元的结构)。 算法 给出选用的算法和数学公式。 : 数据结构 用图表描述数据结构。 程序逻辑 用框图或过程性描述语言的形式表示各程序单元的控制流程(常用程序流程图表示)。存储分配和数组分配 确定每个模块的存储量及数组定义。 单元说明 A. 程序单元标识; }

B. 调用方式; A.参数说明。 4、数据结构设计 数据结构与模块的关系 用图表描述数据结构与模块的关系。 逻辑机结构设计 列出所使用的数据结构中每个数据项、记录和文件的标识、定义、长度、及它们之间的关系。 给出所用数据库的数据模式。 物理结构设计 列出所使用的数据结构中每个数据项的存储要求、访问方法、存取单位和存取物理关系等。

东南大学电工电子实验中心 实验报告 课程名称:电子电路实验 第 3 次实验 实验名称:三极管放大电路设计 院(系):吴健雄学院专业:电类强化班 姓名:梅王智汇学号:61012215 实验室: 101 实验组别: 同组人员:实验时间:2014年 5 月 4 日评定成绩:审阅教师:

实验三 三极管放大电路设计 一、实验目的 1. 掌握单级放大电路的设计、工程估算、安装和调试; 2. 了解三极管、场效应管各项基本器件参数、工作点、偏置电路、输入阻抗、输出阻抗、 增益、幅频特性等的基本概念以及测量方法; 3. 了解负反馈对放大电路特性的影响。 4. 掌握多级放大电路的设计、工程估算、安装和调试; 5. 掌握基本的模拟电路的故障检查和排除方法,深化示波器、稳压电源 、交流毫伏表、 函数发生器的使用技能训练。 二、预习思考: 1. 器件资料: 上网查询本实验所用的三极管9013的数据手册,画出三极管封装示意图,标出每个管脚的名称,将相关参数值填入下表: 2. 偏置电路: 图3-3中偏置电路的名称是什么?简单解释是如何自动调节晶体管的电流I C 以实现稳定直流工作点的作用的,如果R 1、R 2取得过大能否再起到稳定直流工作点的作用,为什么? 答:该偏置电路是分压偏置电路,利用R1,R2对电源电压进行了分压,保证了基极电压稳定为:2 12 BQ CC R U V R R = +。这样就为电路提供了稳定的工作点。就是当环境 温度升高时,I CQ ≈I EQ 增加,U EQ =I EQ R E 增大,由于U BQ 的基本固定,U BEQ =U BQ -U EQ 减小,又使I EQ 减小,抑制I CQ 增加,通过这样的自动调节就稳定了静态工作点。 如果R1,R2取值过大,以至于接近输入电阻R i ,就会导致流入基极的电流不可忽略,工作点不稳定。 3. 电压增益:

产品设计过程——硬件开发 ●课程简介: 本课程以产品设计过程为主线,详细讲解产品设计过程中的各个环节,帮助学员理解产品开发流程,树立按流程办事和流程优化的思想,更好地开展工作。 ●适合对象:硬件研发类新员工 ●培训目标: 学完本课程后,学员能够达到:了解产品设计过程,并在实际工作中能够按流程办事。 ●课程要点: 硬件工程师职责与基本技能 硬件开发规范化管理的重要性 硬件开发过程及文档规范详解 与硬件开发相关的流程文件介绍

产品设计过程——硬件开发 第一章硬件工程师职责与基本技能 第一节硬件工程师职责 一个技术领先、运行可靠的硬件平台是公司产品质量的基础,硬件工程师职责神圣,责任重大。 1、硬件工程师应勇于尝试新的先进技术之应用,在产品硬件设计中大胆创新。 2、坚持采用开放式的硬件架构,把握硬件技术的主流和未来发展,在设计中考 虑将来的技术升级。 3、充分利用公司现有的成熟技术,保持产品技术上的继承生。 4、在设计中考虑成本,控制产品的性能价格比达到最优。 5、技术开放,资源共享,促进公司整体的技术提升。 第二节硬件工程师的基本素质与技术 硬件工程师应掌握如下基本技能: 1、由需求分析至总体方案、详细设计的设计创造能力; 2、熟练运用设计工具,设计原理图,EPLD,FPGA调试程序的能力; 3、运用仿真设备,示波器,逻辑分析仪调测硬件的能力; 4、掌握常用的标准电路的设计能力,如CPU电路,WDT电路,滤波电路,高 速信号传输线的匹配电路等; 5、故障定位,解决问题的能力; 6、文档的写作能力; 7、接触供应商,保守公司机密的技能。

第二章硬件开发规范化管理 第一节硬件开发规范化管理的重要性 在公司的规范化管理中,硬件开发的规范化是一项重要内容。硬件开发规范化管理是在公司的《硬件开发流程》及相关的《硬件开发文档编制规范》,《PCB 投板流程》等文件中规划的。硬件开发流程是指导硬件工程师按规范化方式进行开发的准则,规范了硬件开发的全过程。硬件开发流程制定的目的是规范硬件开发过程控制,硬件开发质量,确保硬件开发能按预定目的完成。 硬件开发流程不但规范化了硬件开发的全过程,同时也从总体上,规定了硬件开发所完成的任务。做为一名硬件工程师深刻领会硬件开发流程中各项内容,在日常工作中自觉按流程办事,是非常重要的,否则若大一个公司就会走向混乱。所有硬件工程师应把学流程、按流程办事、发展完善流程、监督流程的执行作为自己的一项职责,为公司的管理规范化做出的贡献。 总之,硬件开发流程是硬件工程师规范日常开发工作的重要依据,全体硬件工程师必须认真学习。 第二节硬件开发过程详解 硬件开发过程对硬件开发的全过程进行了科学分解,规范了硬件开发的五大任务,也划分硬件开发的五大阶段。 1、硬件需求分析 2、硬件系统设计 3、硬件开发及过程控制 4、系统联调 5、文档归档及验收申请 硬件开发真正起始应在立项后,即接到立项任务书后,但在实际工作中,许多项目在立项之前已做了大量硬件设计工作。立项完成后,项目组就已有了产品规格说明书,系统需求说明书及项目总体方案书,这些文件都已进行过评审。 1、硬件需求分析

宿舍管理系统 详细设计说明书 注:对应模块界面图由组员各自完成2013 年12 月 1 日

1.引言 1.1编写目的 编写本详细设计说明书的目的主要是详细说明宿舍管理系统系统的结构和内部设计,在总体设计说明书的基础上进一步细化系统,提供详细的模块和界面设计,为程序开发提供直接的支持。 本说明书主要面向系统分析人员、程序员和以后的系统维护人员。作为程序员开发系统的根本依据和在系统维护阶段,维护人员对系统实施维护的参考资料。 1.2背景 a.系统的名称:宿舍管理系统 b.任务提出者与开发者:李彬,刘泽中 用户:宿舍管理员和学生 1.3定义 2. 系统的结构 系统的功能模块图如下图 2.1:

图2.1 系统功能模块图 多层架构关系图如下图 2.2 查询学生信息 修改学生信息 添加学生信息 删除学生信息 查询宿舍信息 添加宿舍信息 删除宿舍信息 添加管理员信息 查询水电费信息 用户登录 管理员信息管理 学生信息管理 宿舍信息管理 水电费信息管理 宿舍管理系统 修改密码

图2.2 多层架构关系图 根据图2.1功能结构图和图2.2多层架构关系图可得到如下图2.3所示的系统结构设计图:

3.系统的模块设计 3.1数据库连接模块(sqlconnection)设计说明 3.1.1模块名称;数据库连接模块 3.1.2模块描述: 在.NET中如果采用https://www.doczj.com/doc/144406088.html,与数据库进行连接,可以采用以下4个接口对象之一: System.data.oledb.oledbconnection System.data.sqlclient.sqlconnection System.data.odbc.odbcconnection System.data.oracleclient.oracleconnection 由于数据库使用的是Microsoft SQL Server,所以使用SQL Server .NET Framework数据提供程序中的SqlConnection对象进行数据连接。 3.1.3 模块功能:与数据库进行连接。 3.1.4 模块算法: public void sqlconnectionopen() { Sqlconnection conn = new sqlconnection(); Conn.connectionstring = “user id = admin;password = ; initial catalog = 宿舍管理系统;datasource = localhost;connect timeout = 20”;

实验一原理图输入方式设计数字逻辑电路 一、实验目的: 1、了解基本组合逻辑电路的原理及利用Quartus II 软件进行设计的一般方法。 2、熟悉Quartus II 原理图输入法的设计流程,掌握编辑、编译和仿真的方法。 3、掌握原理图的层次化设计方法。 4、了解Quartus II 软件的编程下载及引脚锁定的方法。 5、了解Quartus II宏功能模块的使用方法。 二、实验的硬件要求: 1、EDA/SOPC实验箱。 2、计算机。 三、实验原理 见附件《Quartus设计的一般步骤》、《元件例化和调用的操作步骤》、《QuartusII基于宏功能模块的设计》 四、实验内容: 1、用原理图方式设计1位二进制半加器半加器。 新建一个工程“HalfAdder”,选择芯片“Cyclone III EP3C16Q240C8”,建立原理图如图1-1,保存为“HalfAdder.BDF”。 图1-1 半加器电路图 编译工程。 建立波形文件,对半加器电路分别进行时序仿真和功能仿真,其波形如下: 图1-2半加器时序仿真波形,注意观察输出延时,以及毛刺的产生原因 图1-3半加器功能仿真波形 2、原理图层次化设计。 新建一工程,取名“FullAdder”;将上面设计的半加器“HalfAdder.BDF”复制到当前工程目录,并生成“符号元件”HalfAdder.BSF。 建立一个原理图文件,取名“FullAdder.BDF”,利用“符号元件”HalfAdder.BSF及其它元件设计全加器电路如下图:

用功能仿真测试全加器的逻辑功能。 图1-5 全加器功能仿真波形 图1-6是输入输出信号与FPGA连接示意图,图中用到了“拨档开关”作为输入,“LED 显示模块”显示输出值。表1-1是本实验连接的FPGA管脚编号。

硬件详细设计报告模版

(公司标识,位于文档首页的左上角)XXXX设计报告(题目,宋体小一,居中) 项目名称XXXX 文档编号 版本号VX.X.X 作者XXX

版权所有(版权声明,宋体五号) 大连互联天下科技发展有限公司 本资料及其包含的所有内容为大连互联天下科技发展有限公司(大连互联天下)所有,受中国法律及适用之国际公约中有关著作权法律的保护。未经大连互联天下书面授权,任何人不得以任何形式复制、传播、散布、改动或以其它方式使用本资料的部分或全部内容,违者将被依法追究责任。

文档更新记录

目录 1引言(使用本文档中的一级标题,格式不可手动修改) (7) 1.1版本处理(使用本文档中的二级标题,格式不 可手动修改) (7) 1.2编写目的 7 1.3预期的读者和阅读建议 7 1.4术语、定义和缩略语 7 1.5相关参考资料 8 2基本描述 (9) 2.1设计的基本要求 9 2.2单板运行环境描述 9 2.3单板工作条件限制 9 2.4单板主要性能指标 9 3模块的功能描述 (10) 3.1结构描述 10 3.2模块描述

10 3.2.1电源模块(使用本文档中的三级标题) 10 3.2.2功能块描述 10 3.3单板重用模块说明 11 4接口设计 (12) 4.1单板接口图 12 4.1.1外部接口设计 12 4.1.2内部接口设计 13 4.2板间接口(可选) 13 5实施 (14) 5.1系统电源方案 14 5.1.1各模块供电及功耗计算 14 5.1.2单板电源电压、功率分配表 14 5.1.3外部电源供电方案 15 5.1.4电源备份方案(可选) 16

电子电器硬件开发详细流程一、硬件开发基本任务 ●硬件需求分析 ●硬件系统设计 ●硬件开发及过程控制 ●系统联调 ●文档归档及验收申请 二、硬件开发详细流程 硬件需求分析内容 1.基本配置及其互联方法 2.运行环境 3.硬件整体系统的基本功能及主要性能指标 4.硬件分系统的基本功能及主要性能指标 5.功能模块的划分 6.关键技术攻关 7.外购硬件的名称型号、生产单位、主要技术指标 8.主要仪器设备 9.公司内部合作以及与外部的合作 10.可靠性、稳定性、可行性论证 11.电源、工艺结构设计 12.硬件测试方案 硬件总体设计报告

1.系统功能及性能指标 2.系统总体结构图及功能划分 3.单板命名 4.系统逻辑框图 5.组成系统各功能模块框图、电路结构图及单板组成 6.单板逻辑框图及电路结构图 7.关键技术讨论 8.关键器件 单板总体设计方案 1.单板在整机中的位置 2.单板功能描述 3.单板尺寸 4.单板逻辑图及功能模块说明 5.单板软件方能描述 6.单板软件功能模块划分 7.接口定义及相关板的关系 8.重要性能指标、功耗及采用标准 单板硬件详细设计 1.单板整体功能的详细描述及模块的精确划分 2.接口的详细设计 3.关键元器件的功能描述、评审、选择 4.符合规范的原理图及PCB图

5.PCB板的测试及测试计划 单板软件详细设计 1.详细设计细节:中断、主程序功能、子程序功能、入口参 数、出口参数、局部变量、函数调用 2.软件流程图 3.通讯协议:物理层、链路层通讯协议定义、高层通讯协议 定义。 单板硬件过程调试文档 1.单板功能模块划分 2.单板模块调试进度 3.调试中的问题和解决方法 4.原是数据记录、系统方案修改说明 5.单板方案修改说明 6.元器件更换说明 7.原理图、PCB板修改说明 8.调试工作阶段总结 9.下阶段调试计划 10.调试方案修改说明 单板软件过程调试文档 1.单板功能模块划分及功能模块调试进度 2.单板调试中出现的问题及解决办法 3.下阶段调试计划

上海电力学院 本科课程设计 电路计算机辅助设计 (1) 院系:电力与自动化工程学院 专业年级(班级): 学生姓名:学号: 指导教师: 成绩: 年月日 教师评语:

目录 (一)电路模型和电路定律及功率测量,含受控源电路分析仿真-----------------------------------------------------------------------1 (二)戴维宁定理诺顿定理结点电压法及回路电流法的仿真----------------------------------------------------------------------4 (三)运算放大器电路分析仿真 ----------------------------------------------------------------------8 (四)正弦稳态电路的分析(1、谐振电路) ---------------------------------------------------------------------10(五)三相交流稳态电路辅助分析仿真 ---------------------------------------------------------------------14(六)非正弦交流电路的分析仿真 ---------------------------------------------------------------------17(七)正弦稳态电路分析仿真(2、互感电路仿真) ---------------------------------------------------------------------24

电子科技大学成都学院 (微电子技术系) 实验报告书 课程名称:电路原理图设计及Hspice 学号: 姓名: 教师: 年06月15日 实验一基本电路图的Hspice仿真 实验时间:同组人员: 一、实验目的 1.学习用Cadence软件画电路图。 2.用Cadence软件导出所需的电路仿真网表。 3.对反相器电路进行仿真,研究该反相器电路的特点。 二、实验仪器设备 Hspice软件、Cadence软件、服务器、电脑 三、实验原理和内容 激励源:直流源、交流小信号源。 瞬态源:正弦、脉冲、指数、分线段性和单频调频源等几种形式。 分析类型:分析类型语句由定义电路分析类型的描述语句和一些控制语句组成,如直流分析(.OP)、交流小信号分析(.AC)、瞬态分析(.TRAN)等分析语句,以及初始状态设置(.IC)、选择项设置(.OPTIONS)等控制语句。这类语句以一个“.”开头,故也称为点语句。其位置可以在标题语句之间的任何地方,习惯上写在电路描述语句之后。 基本原理:(1)当UI=UIL=0V时,UGS1=0,因此V1管截止,而此时|UGS2|> |UTP|,所以V2导通,且导通内阻很低,所以UO=UOH≈UDD,即输出电平. (2)当UI=UIH=UDD时,UGS1=UDD>UTN,V1导通,而UGS2=0<|UTP|,因此V2截止。此时UO=UOL≈0,即输出为低电平。可见,CMOS反相器实现了逻辑非的功能. 四、实验步骤

1.打开Cadence软件,画出CMOS反相器电路图,导出反相器的HSPICE网表文件。 2.修改网表,仿真出图。 3.修改网表,做电路的瞬态仿真,观察输出变化,观察波形,并做说明。 4.对5个首尾连接的反相器组成的振荡器进行波形仿真。 5.分析仿真结果,得出结论。 五、实验数据 输入输出仿真: 网表: * lab2c - simple inverter .options list node post .model pch pmos .model nch nmos *.tran 200p 20n .dc vin 0 5 1m sweep data=w .print v(1) v(2) .param wp=10u wn=10u .data w wp wn 10u 10u 20u 10u 40u 10u 40u 5u .enddata vcc vcc 0 5 vin in 0 2.5 *pulse .2 4.8 2n 1n 1n 5n 20n cload out 0 .75p m1 vcc in out vcc pch l=1u w=wp m2 out in 0 0 nch l=1u w=wn .alter vcc vcc 0 3 .end 图像: 瞬态仿真: 网表: * lab2c - simple inverter .options list node post .model pch pmos .model nch nmos .tran 200p 20n .print tran v(1) v(2) vcc vcc 0 5 vin in 0 2.5 pulse .2 4.8 2n 1n 1n 5n 20n cload out 0 .75p m1 vcc in out vcc pch l=1u w=20u