VerilogHDL与SystemC的语法等效性

- 格式:pdf

- 大小:269.98 KB

- 文档页数:5

systemverilog 可综合语法-概述说明以及解释1.引言1.1 概述SystemVerilog是一种硬件描述语言,其可综合语法用于描述硬件设计的行为和结构。

可综合语法是指在编写SystemVerilog代码时,能够被综合工具翻译成底层硬件电路,并最终映射到FPGA或ASIC等可编程器件上的语法规则和风格。

因此,可综合语法在硬件设计中起着至关重要的作用。

在硬件设计中,可综合语法使设计工程师能够通过代码描述硬件的功能和结构,包括处理器、逻辑电路、存储器等。

通过使用可综合语法,设计工程师可以更加灵活地实现各种功能和性能要求,同时也能提高设计的可维护性和可重用性。

SystemVerilog的可综合语法特点是其结构化的设计风格,丰富的数据类型和内置的高级语言功能。

与传统的硬件描述语言相比,SystemVerilog提供了更多的抽象层次和编程特性,可以更高效地完成复杂的硬件设计任务。

例如,SystemVerilog支持面向对象的设计方法,可以使用类和对象对设计进行建模和封装。

此外,SystemVerilog还提供了多种数据类型和运算符,使设计工程师可以更方便地处理各种数据和信号。

综上所述,可综合语法在SystemVerilog中具有重要的地位和作用。

通过使用可综合语法,设计工程师能够更加方便地描述和实现各种硬件功能,提高设计的效率和可靠性。

在今后的硬件设计中,可综合语法的应用将更加广泛,并且不断发展和完善,以满足不断变化的设计需求。

1.2 文章结构文章结构部分的内容可以包括以下内容:文章结构的目的是为了给读者提供清晰的导航和理解文章的逻辑框架。

通过合理的结构,读者可以更好地理解文章的目的和内容,并能够有序地阅读和理解整个文档。

本文的结构如下:第一部分是引言部分,用于介绍文章的背景和相关信息。

在引言部分,我们将概述SystemVerilog可综合语法的定义和作用,并介绍本文的结构和目的。

第二部分是正文部分,主要内容是关于SystemVerilog可综合语法的定义和特点。

系统Verilog是一种硬件描述语言(HDL),用于描述数字电路。

它包含了Verilog的所有特性,并添加了一些新的特性。

这些新的特性包括在设计中引入了数据类型的定义,更好地支持设计的抽象,以及更自然地支持设计的层次式描述。

在本文中,我们将深入了解System Verilog标准。

1. 介绍System Verilog标准System Verilog是IEEE标准1800,最初是由Accellera组织进行开发的。

它于2005年发行,是Verilog HDL的扩展,它添加了许多新的特性,使得它更适合于硬件验证和设计。

2. System Verilog的特性System Verilog添加了许多新的特性,以提高Verilog HDL的功能。

其中一些主要特性包括:a. 对象导向编程:System Verilog引入了面向对象的编程范式,使得设计和验证更加抽象和灵活。

b. 增强了数据类型和操作:System Verilog引入了更多的数据类型和操作,更好地支持设计和验证的需求。

c. 增加了随机性:System Verilog引入了随机性,使得验证更加全面和高效。

3. System Verilog在硬件验证中的应用System Verilog的特性使得它在硬件验证中应用广泛。

它提供了丰富的验证方法和工具,包括:a. 事务级建模(TLM):System Verilog提供了TLM的支持,使得验证更加抽象和高效。

b. Constrained随机验证:System Verilog引入了constrained random的验证方法,使得验证更加全面和高效。

c. Coverage驱动验证:System Verilog提供了coverage驱动的验证方法,使得验证更加全面和高效。

4. System Verilog在硬件设计中的应用除了在硬件验证中应用广泛外,System Verilog在硬件设计中也有着广泛的应用。

SystemVerilog语言知识介绍SystemVerilog是一种硬件描述与验证语言(HDVL),它基于IEEE 1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包含扩充了C语言数据类型、结构、压缩与非压缩数组、接口、断言等等,这些都使得SystemVeri log在一个更高的抽象层次上提高了设计建模的能力。

Syst emVerilog由Accellera开发,它要紧定位在芯片的实现与验证流程上,并为系统级的设计流程提供了强大的连接能力。

下面我们从几个方面对SystemVerilog所作的增强进行简要的介绍,期望能够通过这个介绍使大家对SystemVeril og有一个概括性的熟悉。

1. 接口(Interface)Verilog模块之间的连接是通过模块端口进行的。

为了给构成设计的各个模块定义端口,我们务必对期望的硬件设计有一个全面的认识。

不幸的是,在设计的早期,我们很难把握设计的细节。

而且,一旦模块的端口定义完成后,我们也很难改变端口的配置。

另外,一个设计中的许多模块往往具有相同的端口定义,在Verilog中,我们务必在每个模块中进行相同的定义,这为我们增加了无谓的工作量。

SystemVerilog提供了一个新的、高层抽象的模块连接,这个连接被称之接口(Interface)。

接口在关键字interfac e与endinterface之间定义,它独立于模块。

接口在模块中就像一个单一的端口一样使用。

在最简单的形式下,一个接口能够认为是一组线网。

比如,能够将PCI总线的所有信号绑定在一起构成一个接口。

通过使用接口,我们在进行一个设计的时候能够不需要首先建立各个模块间的互连。

随着设计的深入,各个设计细节也会变得越来越清晰,而接口内的信号也会很容易地表示出来。

当接口发生变化时,这些变化也会在使用该接口的所有模块中反映出来,而无需更换每一个模块。

下面是一个接口的使用实例:实际上,SystemVerilog的接口不仅仅能够表示信号的绑定与互连。

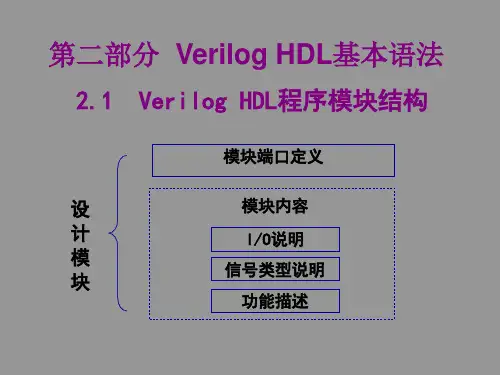

VerilogHDL语法基础⼀个复杂电路的完整Verilog HDL模型是由若个Verilog HDL 模块构成的,每⼀个模块⼜可以由若⼲个⼦模块构成。

利⽤Verilog HDL语⾔结构所提供的这种功能就可以构造⼀个模块间的清晰层次结构来描述极其复杂的⼤型设计。

每个模块的内容都是嵌在module和endmodule两个语句之间,每个模块实现特定的功能,模块是可以进⾏层次嵌套的。

每个模块⾸先要进⾏端⼝定义.并说明输⼊(input)和输出(output),然后对模块的功能进⾏逻辑描述。

Verilog HDL程序的书写格式⾃由,⼀⾏可以写⼏个语句,⼀个语句也可以分多⾏写。

除了endmodule语句外,每个语句的最后必须有分号。

⼀个模块是由两部分组成的,⼀部分描述接⼝;另⼀部分描述逻辑功能,即定义输⼊是如何影响输出的。

模块(block)的组成Verilog HDL结构完全嵌在module和endmodule声明语句之间,每个Verilog程序包括4个主要部分:端⼝定义,I/O说明,信号类型声明和功能描述。

module<模块名>(<端⼝列表>);端⼝说明(input,output,inout)参数定义(可选)数据类型定义连续赋值语句(assign)过程块(initial 和 always)⾏为描述语句低层模块实例任务和函数延时说明块endmodule模块声明模块声明包括模块名和端⼝列表。

其格式如下:module 模块名(端⼝1,端⼝2,端⼝3,…);模块结束的标志为关键字:endmodule。

端⼝定义input(输⼊端⼝),output(输出端⼝)和inout(双向端⼝)。

格式如下:input 端⼝名1,端⼝名2,………,端⼝名N; //输⼊端⼝output 端⼝名1,端⼝名2,………,端⼝名N; //输出端⼝inout 端⼝名1,端⼝名2,………,端⼝名N; //输⼊输出端⼝也可以写在端⼝声明语句⾥,其格式如下(为了代码的可读性,⼀般不这么写):module module_name(input port1,input port2,…output port1,output port2… );信号类型说明信号可以分为端⼝信号和内部信号;1. 所有信号都必须进⾏数据类型的定义,如寄存器类型(reg等),连线类型(wire等);2. 如果信号没有定义数据类型,则综合器将其默认为wire型;3. 端⼝的位宽最好定义在端⼝定义中,不要放在数据类型定义中;4. 不能将input和inout类型声明为reg型;模块的端⼝表⽰的是模块的输⼊和输出⼝名,也就是说,它与别的模块联系端⼝的标识。

SystemC 的验证方法和流程介绍1 引言当前集成电路制造技术迅速发展,SoC(system-on-chip)设计已经成为集成电路设计的发展方向。

随着SoC 设计的复杂度提高,在开发SoC 的过程中,验证工作越发重要和繁重,所占的开销占据总开销的40%70%。

SoC 设计的验证过程不但影响到芯片的成功设计,而且影响到芯片的上市时间,因此验证的正确性及其耗时的缩短成为了SoC 设计的关键。

传统设计中,系统级设计使用高级语言C/C++等描述功能模块的算法,验证的时候使用硬件描述语言(VHDL 或Verilog HDL)。

系统验证之前必须通过手工将原始的C/C++代码转换为VHDL/Verilog HDL 代码,这个转换过程耗时大并且容易产生错误。

在系统验证过程中,使用传统硬件描述语言对复杂模块的验证需要耗费大量时间。

为了提高系统级验证效率,本文针对视频芯片中的运动估计与补偿单元模块(MECU)提出了基于SystemC 的验证方法和流程。

该方法大大缩短了系统验证的搭建时间和系统验证过程的时间。

本文利用SystemC 支持设计者在不同抽象级建模的特点,给MECU 添加了低抽象级接口,使该单元能够和视频芯片内部其它模型通讯以便完成整个芯片的系统级验证。

本文最后的仿真结果证明了该设计流程的有效性。

2 SystemC 语言SystemC 是由C++衍生而来,本质是在C++的基础上添加了硬件扩展库和仿真核,这使SystemC 可以在不同抽象级对复杂电子系统建模。

它既可以描述纯功能的模型和系统体系结构,又可以描述软硬件的具体实现,进行软硬件的协同验证。

SystemC 包括以下建模元素:*模块(module)相当于C++的类定义,是一个可以多层次的实体。

一个模块可以嵌套其他模块和一些进程,是SystemC 里面最基本的单元。

*进程(process)用来描述模块的功能,包含于模块中。

进程是由事件(event)来触发的,这种触发的方式使进程可以并行执行,实现了硬件系统的并行特性,SystemC 包括三种不同的进程。

vhdl和systemverilog混合编译摘要:一、前言二、VHDL 和SystemVerilog 的概述三、混合编译的原理和优势四、混合编译的方法和步骤五、混合编译的实践应用六、总结正文:一、前言随着集成电路的复杂度不断增加,硬件描述语言(HDL)在电路设计中的地位越来越重要。

VHDL 和SystemVerilog 作为两种常用的硬件描述语言,各自有着独特的优势。

为了充分利用这两种语言的特点,混合编译成为了一个热门话题。

二、VHDL 和SystemVerilog 的概述1.VHDL(VHSIC 硬件描述语言)是一种基于文本的硬件描述语言,由美国国防部高级研究计划局(DARPA)于1980 年代开发。

它主要应用于数字电路和模拟混合信号电路的设计。

2.SystemVerilog 是C 语言的扩展,由Accellera 标准化组织于1995 年推出。

它主要用于验证、仿真和测试电路设计。

三、混合编译的原理和优势1.混合编译的原理:混合编译是指在同一个项目中使用VHDL 和SystemVerilog 两种语言进行编程,通过编译器将两种语言的源代码编译成目标文件,最终实现整个系统的功能。

2.优势:混合编译可以充分发挥两种语言的优势,实现更高效、更灵活的设计。

例如,VHDL 适用于描述复杂的数字电路,而SystemVerilog 在验证方面的功能更强。

四、混合编译的方法和步骤1.创建项目:首先创建一个包含VHDL 和SystemVerilog 源文件的项目。

2.编写VHDL 代码:在项目中编写VHDL 代码,实现数字电路的设计。

3.编写SystemVerilog 代码:在项目中编写SystemVerilog 代码,实现验证、仿真和测试功能。

4.配置编译器:选择合适的编译器,配置编译器参数,以支持VHDL 和SystemVerilog 的混合编译。

5.编译:编译项目,生成目标文件。

6.仿真和验证:使用仿真工具对设计进行仿真和验证。

SystemC和SystemVerilog的比较时间:2010-03-18 20:49来源:未知作者:admin 点击:356次SystemC、SystemVerilog已经继VHDL和Verilog之后,成为HDL仿真工具支持的语言。

但截至目前,Verilog依然是使用最广泛的语言,而SystemVerilog是Verilog的超集,因此SystemVerilog的发展本身就是Verilog的SystemC、SystemVerilog已经继VHDL和Verilog之后,成为HDL仿真工具支持的语言。

但截至目前,Verilog依然是使用最广泛的语言,而SystemVerilog是Verilog的超集,因此SystemVerilog的发展本身就是Verilog的发展。

就SystemC和SystemVerilog这两种语言而言, SystemC是C++在硬件支持方面的扩展,而SystemVerilog扩展了Verilog在面向对象和验证平台方面的适用扩展。

而这两种语言均支持诸如信号、事件、接口和面向对象的概念,但每一种语言又均拥有自己明确的应用重点:● SystemC特别适合建模体系结构,开发事务处理级(TL)模型和在验证中描述软件的行为。

对于具有很强C++实力的团队和有基于C/C++ IP 集成要求(如处理器仿真器),以及为早期软件开发设计的虚拟原型来说,SystemC特别适合。

● SystemVerilog是进行RTL设计的最佳语言,不仅在于其描述真实硬件和断言的能力,还在于对工具支持方面的考虑。

同时,SystemVerilog也提供了建模抽象模型和先进的验证平台语言特征,例如受限制随机激励生成、功能覆盖或断言。

对于那些没有C/C++IP 集成要求的项目来讲比较合适,毕竟可以使用一种语言完成全部设计。

当然,SystemC可以用于验证平台和描述RTL结构,而SystemVerilog也可以用于编写高层事务处理级模型。

SystemVerilog标准手册一、概述SystemVerilog是一种硬件描述和验证语言,它结合了Verilog HDL和VHDL的特性,并增添了许多新的功能和特性。

SystemVerilog的标准手册是SystemVerilog语言的权威参考资料,它详细说明了SystemVerilog的语法、语义和用法规范。

二、内容1. 语言基础SystemVerilog标准手册包含了SystemVerilog语言的基础知识,如数据类型、变量定义、控制结构、函数和任务等。

在这一部分,读者可以了解到SystemVerilog的基本语法和语言特性,为后续的学习和应用打下坚实的基础。

2. 对象和类SystemVerilog引入了面向对象的编程思想,允许用户定义自定义类型、类和对象。

SystemVerilog标准手册详细介绍了对象和类的定义、成员函数、继承和多态等相关内容,为用户提供了丰富的编程工具和技巧。

3. 验证方法SystemVerilog不仅可以用于硬件描述,还可以用于硬件验证。

SystemVerilog标准手册介绍了SystemVerilog的验证方法和工具,包括assertion、coverage、constrained randomization等内容,帮助用户编写高效且可靠的验证代码。

4. 高级特性除了基本的语言特性外,SystemVerilog还提供了许多高级的功能和特性,如接口、多线程、并发控制等。

SystemVerilog标准手册深入介绍了这些高级特性的用法和原理,帮助用户更好地理解和应用SystemVerilog语言。

5. 应用实例除了语法和特性的介绍外,SystemVerilog标准手册还提供了大量的实际应用示例,包括硬件描述、验证代码和仿真模型等。

这些应用实例可以帮助用户更直观地了解SystemVerilog语言的实际应用场景,加深对SystemVerilog的理解和掌握。

三、重要性SystemVerilog标准手册是学习和使用SystemVerilog语言的重要参考资料。

在Verilog中,`system`函数用于执行一个系统任务或调用一个系统函数。

它通常用于执行那些需要与外部环境交互的操作,例如读取或写入文件、与网络通信等。

`system`函数的一般语法如下:

```verilog

result = system("command");

```

其中,`command`是要执行的外部命令或系统函数。

`result`是该命令的输出结果。

下面是一个使用`system`函数执行外部命令的示例:

```verilog

module top;

initial begin

$display("Executing external command...");

result = system("ls -l"); // 执行外部命令,获取文件列表

$display("Command output: %s", result);

end

endmodule

```

在上面的示例中,`system("ls -l")`调用了外部命令`ls -l`,该命令用于列出当前目录下的文件列表。

执行结果将被存储在`result`变量中,并使用`$display`函数输出到仿真控制台。

需要注意的是,`system`函数的具体实现可能因仿真器而异。

因此,在使用`system`函数之前,建议先查看所使用的仿真器的文档以了解其支持的系统函数和命令。

C语⾔与verilog 的区别及相互转化1,⾯对C语⾔⽐verilogHDL更加成熟,⽽且更加可靠,因为verilog 的编译,查错⼯具⼤都是商业软件,因此没有像C语⾔⼀样得到⼴泛的应⽤,各种缺陷也较C来说较多。

基于这样的原因,在设计算法的硬件电路块时,⼀般采⽤C语⾔和verilog相结合的⽅式,利⽤C语⾔完善的查错和编译环境,设计者可以先设计出⼀个功能正确的设计单元,以此作为设计⽐较的标准。

然后,把C程序⼀段⼀段地改写成⽤并型结构(类似于Verilog)描述的C程序,此时还是在C的环境⾥,使⽤的依然是C语⾔。

如果运⾏结果都正确,就将C语⾔关键字⽤Verilog相应的关键字替换,进⼊Verilog的环境。

将测试输⼊同时加到C与Verilog 两个单元,将其输出做⽐较。

这样很容易发现问题的所在,然后更正,再做测试,直⾄正确⽆误。

2,C语⾔的代码是⼀⾏⼀⾏执⾏的,属于顺序结构,⽽verilog是⼀种硬件描述语⾔,语句同时进⾏,属于并⾏结构,并且verilog的仿真软件⼤多都是顺序结构的,所以有很多的问题没有办法发现。

3,verilog的输⼊输出函数较少,⽽C却多种多样,因此在转化上存在很⼤的问题。

C函数调⽤是没有时间延时特性的,不同时间调⽤同⼀个函数的功能是⼀样的,⽽Verilog中对模块的不同调⽤是不同的,即使调⽤的是同⼀个模块,必须⽤不同的名字来指定。

Verilog的语法规则很死,限制很多,能⽤的判断语句有限。

仿真速度较慢,查错功能差,错误信息不完整。

仿真软件通常也很昂贵,⽽且不⼀定可靠。

C语⾔没有时间关系,转换后的Verilog程序必须要能做到没有任何外加的⼈⼯延时信号,也就是必须表达为有限状态机,即RTL级的Verilog,否则将⽆法使⽤综合⼯具把Verilog源代码转化为门级逻辑。

4,verilog与C的常⽤关键字相互转化如下:。

vivado中systemverilog混合编译在Vivado中,SystemVerilog混合编译是指将SystemVerilog代码与Verilog代码一起编译和仿真。

Vivado支持这种混合编译,以便您可以在同一个项目中使用两种语言。

以下是混合编译的一般步骤:1. 创建项目:首先,创建一个新的Vivado项目。

这可以通过打开Vivado软件并创建一个新的项目文件来实现。

2. 添加文件:在项目中添加所需的Verilog和SystemVerilog文件。

您可以将文件直接拖放到项目浏览器中,或者通过菜单栏中的“File”>“Add”>“File”来添加。

3. 编写代码:在Verilog和SystemVerilog文件中编写代码。

请注意,混合编译的代码应该遵循一定的规范,以便Vivado可以正确地识别和处理两种语言。

4. 编译和仿真:在Vivado中编译项目。

可以通过菜单栏中的“Run”>“Compile”来执行编译操作。

编译完成后,您可以使用Vivado提供的仿真工具进行仿真。

5. 分析结果:在仿真过程中,您可以查看波形、报告和其它输出文件,以分析设计的性能和正确性。

以下是一些建议,以确保混合编译的顺利进行:-避免在同一个模块中混合使用Verilog和SystemVerilog代码。

尽量将Verilog代码和SystemVerilog代码分别放在不同的模块中。

-使用Vivado提供的预处理器指令来区分Verilog和SystemVerilog代码。

例如,使用``来声明一个模块为SystemVerilog模块。

-确保SystemVerilog模块中的异常处理和监控功能正确实现,以避免编译错误。

-熟悉Vivado的编译器和仿真器,以便在混合编译环境中正确地使用它们。

总之,在Vivado中进行SystemVerilog混合编译需要遵循一定的规范和技巧。

通过遵循这些规范和技巧,您可以充分利用Verilog和SystemVerilog的优势,提高设计开发效率。

SystemC中⽂教程⼀SystemC是什么⾸先, SystemC不是⼀门新的语⾔,⽽是基于C++开发的library;因此,你所熟悉的C++知识都可以在SystemC建模时使⽤;理论上来说,SystemC library和常见的boost库没有任何本质差别。

此外,这也告诉我们只需⼀个⽀持C++的环境,我们就可以进⾏SystemC建模和仿真,⽆需任何其他⼯具,这相⽐其他软硬件建模语⾔来说,所需环境极其简单。

注:最常见的硬件描述语⾔Verilog,它的仿真需要仿真⼯具⽀持,如VCS、modelsim等,它们都是价格昂贵的EDA⼯具,且使⽤复杂。

其次,SystemC是由Accellera组织拥有的开源库,它使⽤Apache 2.0开源协议;Apache2.0协议是⼀种对商业应⽤友好的许可,所以,不论⽤户⽤之开发的产品是否商⽤,都可以放⼼使⽤,不⽤担⼼侵权⾏为。

但是,SystemC是⼲什么⽤的呢?SystemC的命名已经表明了它的⽤途,它是⼀种系统建模语⾔;我们常常⽤系统来形容复杂的东西,⼀台电脑、⼀块芯⽚、⼀个公司都可以称之为⼀个系统。

系统有很多特征,如模块化、并⾏性、通信机制、规则下办事等等。

以电脑为例,CPU、GPU、内存、显⽰器等都是⼀个个独⽴的模块,各⾃完成各⾃的任务;它们总是并⾏⼯作,同时⼜通过接⼝相互通信。

如何为⼀个系统建模呢?原⽣的编程语⾔都是串⾏执⾏的,⽆法建模并⾏系统;即使你建模了⼀个系统,但最终都要在CPU上跑仿真,⽽CPU总是串⾏执⾏的。

我们知道,硬件是⼤量并⾏运⾏单元的组合,必须能够⽀持对并⾏操作的模拟;SystemC正是为此⽽⽣,为软硬件系统建模提供了强有⼒的⽀持。

总结:SystemC是⼀个⽀持系统建模的开源的C++ library;SystmeC的作⽤现代的芯⽚总是包含硬件和软件,软件部分可以是固件或者驱动;芯⽚市场是⼀个充满竞争的市场,⼏乎所有的芯⽚公司对产品都有严格时间规划;如何让产品尽快⾯市,如何减少产品bug⼏乎是所有芯⽚公司都需要⾯对的难题。

System CSystemC是一种基于C++语言的用于系统设计的计算机语言,是用C++编写的一组库和宏。

它是为了提高电子系统设计效率而逐渐发展起来的产物。

IEEE于2005年12月批准了IEEE1666-2005标准。

通常,系统由软件部分和硬件部分组成,系统的一部分功能由软件实现,而另一部分功能则由硬件实现。

早期的系统比较简单,系统工程师将准备设计的系统划分为软件部分和硬件部分,分别由软件工程师和硬件工程师进行设计、仿真、实现和改进,最后再将软件部分和硬件部分结合起来形成系统。

软件工程师使用C 和C++等程序设计语言,因为这些语言专长于描述串行执行的程序,用来仿真软件部分;而硬件工程师则使用VHDL和Verilog等硬件描述语言,因为这些语言专长于描述并行运行的硬件,用来仿真硬件部分。

但是,随着电子系统的不断发展,系统结构越来越复杂,系统元件也越来越多,这就要求系统工程师在先期划分软件和硬件时,就对整个系统性能有很好的了解和掌握,以便更好地划分软件和硬件,减小设计中不必要的失误所带来的损失和风险。

SystemC也就由此孕育而生,因为它能够满足对软件和硬件协同仿真的需求SystemC的名称来自“系统”一词的英语System和“C/C++语言”中的C,以表示它是一种基于C/C++语言的系统设计语言。

许多科学研究团队和计算机辅助设计软件公司一同为SystemC的发展做出了贡献,1999年成立了开源SystemC的开发团队“Open SystemC Initiative (OSCI)”。

2011年11月10, IEEE通过了新SystemC 2011标准:IEEE1666-2011。

参考文献T. Grötker, S. Liao, G. Martin, S. Swan, System Design with SystemC. Springer, 2002. ISBN 1-4020-7072-1J. Bhasker, A SystemC Primer, Second Edition, Star Galaxy Publishing, 2004. ISBN 0-9650391-2-9D. C. Black, J. Donovan, SystemC: From the Ground Up, Springer 2005. ISBN 0-387-29240-3[编辑] 外部链接 SystemC的社区AutoESL From XilinxCatapultC From CalyptoC-to-Silicon From CadenceCynthesizer From Forte随着半导体技术的迅猛发展,Soc已经成为当今集成电路设计的发展方向。

systemverilog 语法SystemVerilog是一个硬件描述语言(HDL),它具有一些基本语法结构,与其他编程语言并无差异。

本文将介绍常见的SystemVerilog 语法。

1. 模块声明SystemVerilog使用模块来描述电路的结构,其中包含了输入端口、输出端口以及内部信号。

下面是一个简单的模块声明示例:module my_module(input input_port, output output_port);// Verilog代码在这里endmodule2. 变量声明变量可分为多种类型:- 整型变量(int):用于整数值。

- 浮点型变量(real):用于浮点值。

- 位变量(bit):只能存储0和1。

- 向量型变量(vector):用于存储多位的值。

下面是声明一个整型变量的示例:int my_variable;3. Control FlowSystemVerilog支持条件和循环语句,使得描述一些分支判断或循环的电路的时候变得更加直观。

- if/else语句:if语句用于条件分支,else语句用于指定当条件不满足时的操作。

下面是if/else语句的基本形式:if (condition) begin// 操作一endelse begin// 操作二end- for循环:for循环让您可以重复执行某些操作,直到满足指定的条件。

下面是for循环语句的一般形式:for(initialization, condition, increment) begin// 操作end其中,初始化指定循环计数器的值,条件指定循环何时结束,增量指定每次循环计数器自增的值。

4. 综合测试(assertions)综合测试是一种在设计中添加的指令,通过检查某些条件是否满足来确保设计的正确性。

可以使用综合测试指令对电路进行严格测试。

下面是一个简单的综合测试指令:assert(signal1 == signal2) else $display("Error");这里的断言语句表示,如果信号signal1不等于信号signal2,则显示错误消息。

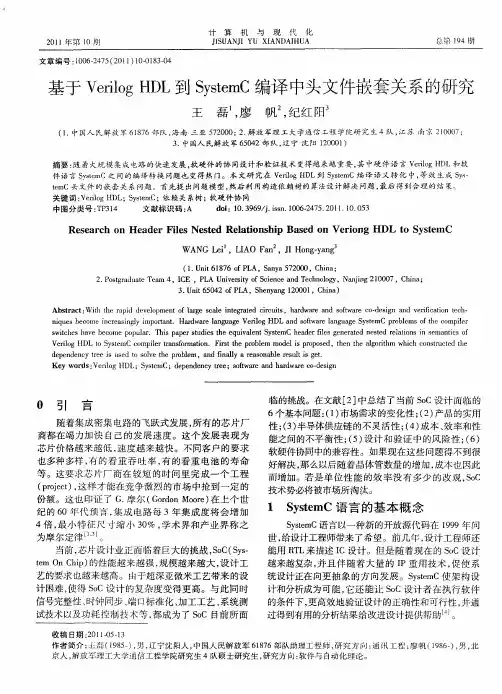

第37卷 第9期2004年9月天 津 大 学 学 报Journal of Tianjin U niversityVol.37 No.9Sep.2004V erilog H DL与SystemC的语法等效性Ξ张雅绮,王 琨,崔志刚(天津大学电子信息工程学院,天津300072)摘 要:针对电子系统设计中使用不同语言制约设计效率的问题,研究了SystemC2.0与Verilog HDL的语法在基本语法结构、时间模型、等待和事件模型、调度模型等方面的等效性,得出如下结论:对于门级以上级别的描述,所有的Verilog HDL的描述总可以在SystemC中找到对应描述;开发EDA设计工具,实现从Verilog HDL描述的知识产权自动转换到SystemC描述是可行的.关键词:系统级描述语言;Verilog HDL;SystemC;语法等效性中图分类号:TN492 文献标志码:A 文章编号:049322137(2004)0920842205Syntax Equivalence of V erilog H DL and SystemCZHAN G Ya2qi,WAN G Kun,CU I Zhi2gang(School of Electronic Information Engineering,Tianjin University,Tianjin300072,China)Abstract:The syntax equivalence of Verilog HDL and SystemC2.0is discussed in detail regard to basic syntax structure,timing model,wait and event module and scheduler module.It is concluded that for gate or upper abstract level of Verilog HDL description,there always exists corresponding SystemC description,and it is fea2 sible to develop an EDA design tool to automatically convert Verilog2based IP to SystemC2based IP.K eyw ords:system level description language;Verilog HDL;SystemC;syntax equivalence 随着片上系统(SoC)[1]设计的复杂程度增加,传统的设计方法已经不能够满足电子系统设计的要求,原因在于系统设计、硬件设计和软件设计使用不同语言,无法进行软硬件协同验证,系统验证成为制约设计效率的主要因素.因而迫切需要一种通用语言,能够完成由软件到硬件、系统到门级各个层次的设计描述和验证,这就是先进的系统设计语言(system level de2 scription language,SLDL). 当前系统设计语言的发展方向为:一是扩展传统的硬件描述语言V HDL和Verilog HDL[2],使其支持抽象数据类型,并具有系统描述能力,这方面最突出的研究成果有Co2Design Automation公司所倡导的Su2 perlog,该语言的创始人之一是Verilog HDL的创建者和黄金仿真器Verilog2XL的设计者Phil Moorby;二是扩展传统的软件语言C和C++,使其支持硬件描述,这方面工作最突出的是SystemC[3].近年来,SystemC 在Synopsys等大公司的支持下得到了很大的发展,并推出了SystemC Compiler,支持SystemC的综合. 由于SystemC具有开放性,可完成软硬件在不同精度级别上的协同设计,这种系统设计语言已经受到各国电子工程师的重视,出现了一些有关V HDL与SystemC[4,5]以及Verilog HDL与SystemC[6,7]的对比与转换的研究.随着SystemC的发展,将有越来越多的硬件设计者希望学习和掌握SystemC,并将Sys2 temC与传统硬件描述语言如V HDL或者Verilog HDL进行对比.更为重要的是希望能够设计出传统硬件描述语言与SystemC之间的自动转换工具,将现有的Verilog HDL或者V HDL完成的设计自动地转换成SystemC模型,使设计事半功倍. SystemC2.0增强了SystemC的系统级描述功能,主要体现在系统可包含软件、硬件以及两者的混合结构,支持用特定的设计方法以及软核来创建模型库并进行模拟,但它仍然不能完成如同Verilog HDL的开关级模拟.因此,有必要深入研究SystemC2.0与Ver2Ξ收稿日期:2003206204;修回日期:2004203211. 作者简介:张雅绮(1945— ),女,教授.ilog HDL的等效性,开发自动转换工具,实现已有的HDLs设计转换.本文探讨了SystemC2.0与Verilog HDL的语法在基本语法结构、时间模型、等待和事件模型、调度模型等方面的等效性,提出了设计和研究Verilog HDL描述的知识产权(IP)自动转换到Sys2 temC描述的可行性.1 基本结构的等效性 Verilog HDL的基本组成结构是模块module,对应的SystemC描述是sc-module.与模块之间相联系的是端口信号的定义.Verilog HDL的输出信号也可以作为输入,而SystemC的断口定义了数据转移的方向,所以对于同样作为输入的Verilog HDL输出信号output,在SystemC中必须定义为inout.Verilog HDL 不支持浮点型的输出,而SystemC则支持,这在Ver2 ilog HDL到SystemC转换的时候不会产生问题,反之则不可以.对于Verilog HDL中的连续赋值语句assign 和always语句,都对应于SystemC的进程process. SytemC的进程有3种:方法进程、线程和钟控线程.方法进程用来进行组合逻辑模拟,线程可用来模拟测试平台,而钟控线程用来模拟同步有限状态机.后两种都是行为模型,至少需要行为级综合工具才能综合.由于方法进程可以用来描述寄存器传输级电路,一般将Verilog HDL中的assign和always语句翻译成方法进程.在always中,可能同时存在对多个寄存器(reg)型变量的阻塞或者非阻塞赋值,但可综合的代码只允许对同一寄存器变量进行非阻塞赋值或者阻塞赋值.对于一个always语句中的所有阻塞赋值语句,应该映射到一个SystemC进程中.对于不同变量的非阻塞赋值,应该映射为不同的SystemC进程. Verilog HDL的initial语句等效于SystemC进程的构造函数;parameter可以用SystemC的类模板实现;文献[6]中建议使用C++的宏来实现门级电路,还提出了一种“信号处理器引擎”方法用以在SystemC中选择支持Ver2 ilog HDL的范围.对于子模块的例化,Verilog HDL和Sys2 temC都支持端口对应和位置映射.2 时间模型的等效性 Verilog HDL与SystemC在定时时间和时钟定义方面差异较大,但都能完成硬件描述中的时序描述. 首先是时钟.在Verilog HDL中没有专门的时钟,用户需要定义一个reg信号来模拟时钟,而SystemC 中则直接定义了结构sc-clock用于定义时钟,例如下述代码1.代码1 V erilog H DL与SystemC时钟定义的等效性Code1 Equivalence of V erilog H DL and SystemCon clock def inition//Verilog HDL//SystemCmodule(clk);//define a20MHz clocksc-clock clk(“clk”,50,0.5,5, false);initial clk=#50;always#25 clk=~clk;endmodule 在Verilog HDL中,用timescale定义缺省的时间单位,在SystemC中使用了sc-set-time-resolution()和sc-set-default-time-unit(),这在功能上与timescale等效.若将时间单位设置为1ns,分辨率为1ps,则代码2描述了时间单位的等效性.代码2 V erilog H DL与SystemC时间单位和时间分辨率定义的等效性Code2 Equivalence of V erilog H DL and SystemCon unit and resolution of time//Verilog HDL//SystemC‘timescale1ns/1pssc-set-time-resolution(1, SC-PS)sc-set-default-time-unit(1, SC-NS)3 等待(w ait)与事件(event)的等效性 为了支持行为级动态建模,Verilog HDL与Sys2 temC都定义了wait函数和事件,当它被执行时将产生时间,触发等待在该事件上的进程继续执行.在Sys2 temC中,wait()只能在线程或者钟控线程内使用,在方法进程内须用与wait()等效的函数next-trigger()描述延迟,如下述的代码3,它描述的是一个延迟器件.值得注意的是,在代码3中,左边的Verilog HDL 代码实际上描述的是传输延迟,右边SystemC描述的是惯性延迟.惯性延迟可能造成极短脉冲的消失,而传输延迟则不会. 在使用next-trigger()描述时序逻辑延迟时,需要将输入信号(代码3中的din)延迟一个时钟周期,仿真结果才会是预期的,但由此会造成综合结果不正确,所・348・ 2004年9月 张雅绮等:Verilog HDL与SystemC的语法等效性以不建议在时序逻辑中使用next-trigger(),这是使用高级语言描述硬件的缺点,SystemC尚不能够描述惯性延迟.代码3 V erilog H DL与SystemC延迟描述的等效性Code3 Equivalence of V erilog H DL and SystemCon delay description//Verilog HDL//SystemC‘define DL Y2#define DL Y2module dff(clk,din,dout);#include“systemc.h”input clk,din;SC-MODUL E(delayer){output dout;sc-in<bool>din;assign sc-out<bool>dout; dout<=#‘DL Y din; endmodule void do it(){next-trigger(DL Y, SC-NS);dout=din;};SC-CTOR(dff){SC-METHOD(do it); sensitiveνdin;}}; 在SystemC中,Event定义一种事件对象,能够激活因遇到wait()或者wait-until()而等待的线程或者钟控线程,wait()函数只在线程或者钟控线程内使用,通常与event对象搭配,如代码4所示.代码4 V erilog H DL的event对象与SystemC的sc-event的等效性(准代码)Code4 Equivalence of event object in V erilog H DLand sc-event in SystemC//Verilog HDL//SystemCmodule tb();#include“systemc.h”event reseted;SC-MODUL E(tb){initial begin sc-event reseted;//code for reset void tb-do-others(){//some reseted; codeend wait(reseted);initial begin//code for after reset disposal};//some code……void tb-rst(){//codes for reset@(reseted);reseted.notify();}//code for after reset SC-STOR(tb);//disposal……{SC-THREAD(tb-do-others);end//sensitivity list……endmodule SC-THREAD(tb-rst);//sensitivity list……}}; 由代码4可以看出,Verilog的动态事件event可以映射到SystemC的对应事件sc-event,SystemC的wait函数支持多种不同的重载参数,如代码5所示.代码5 V erilog H DL和SystemC的w ait()函数Code5 w ait()functions in V erilogH DL and SystemC//Verilog HDL wait-statement//SystemC wait-functionwait(expression)等待条件表达式为真wait();等待敏感表中的事件发生wait(e1);等待事件e1发生wait(e1|e2|e3);等待事件发生wait(e1&e2&e3);等待事件 e1,e2,e3之一发生wait(200,SC-NS);等待事件 e1,e2,e3同时发生wait(200,SC-NS,e1);等待事 件e1发生,直到200nswait(SC-ZERO-TIME);等待 一个Δ周期 代码5列出了部分SystemC的wait()函数支持的重载参数类型.Verilog HDL的wait()函数比较简单,进程执行到wait语句时进入等待状态,直至条件表达式为真时,重新开始启动进程.可以看出,SystemC的wait()函数功能比Verilog HDL更强大.4 仿真调度模型的等效性 仿真调度模型(Scheduler)涉及到代码如何执行,理解它对于Verilog HDL到SystemC的代码转换有重要意义.为了支持寄存器传输级的并行描述,SystemC 采用了与Verilog HDL基本相同的调度模型———基于Δ(delta)延迟.一个Δ周期包括求值和更新两个阶段,在一个时间点上,这样的Δ周期会持续出现,直到在求值前后的结果不再发生变化,而在宏观上,时间并没有前进.代码6中的Verilog HDL程序段在VCS和Verilog2XL不同仿真器环境下,可能得到不一致的仿真结果. 代码6中有可能先执行赋值,也有可能先执行$display.在默认选项下,在Verilog2XL显示的addr 值为x(仿真命令为verilog example.v),VCS中的结果为1(仿真命令为vcs2o example.out example.v,然后执行example.out).仿真结果不同的原因是Verilog2 XL执行完整个initial语句后才对addr赋值,而VCS・448・天 津 大 学 学 报 第37卷 第9期 是在last-addr被赋值后中断initial语句,在执行完对addr赋值后返回initial.如果将代码6中第三和第四行合并为wire addr=last-addr+1,则仿真结果相同.然而依Verilog HDL21995标准,这两种赋值并没有区别,标准中并没有定义initial和assign执行的先后顺序.由于SystemC基于C++,构造函数先于其他成员函数执行,所以不会产生问题.对于SystemC2.0调度模型,在初始化阶段(notify()),所有进程包括方法进程和线程都将被执行一次,这与Verilog HDL和V HDL的调度模型一致.代码6 一段在V CS和V erilog2X L仿真结果不一样的代码Code6 A procedure of having different simulation results using V CS and V erilog2X L tools//Verilog HDL-file:Example.vmodule example integer last-addr; wire[31:0]addr;assign addr=last-addr+1; initial begin last-addr=0;$display(“at time:”,$time,“;the addr changed to:%d”,addr);endendmodule 5 等效性举例 根据上述等效性讨论可知,SystemC继承了C+ +类的语法结构,Verilog HDL则是结构化的硬件描述语言.下面举一个简单的例子,来说明用两种语言对同一逻辑电路进行描述的雷同与差异.一个具有逻辑与、或、或非和取反功能的算术逻辑单元(AL U)的原理如图1所示,两种描述代码示于代码7中.从中可以清楚地看出SystemC与Verilog HDL描述的等效性.图1 一个简单的算术逻辑单元Fig.1 Schematic of a simple A L U代码7 简单的算术逻辑单元代码Code7 Example of descriptions to a simple A L U using V erilog H DL and SystemC//Verilog Code for a simple ALU//SystemC Code for a simple ALUmodule alu-complete(dout,din-a,din-b,enable,opcode)void alu::operate() input[3:0]din-a,din-b;{ input[2:0]opcode;sc-mv<radix-k,width-n>res;//res与操作数宽度相同 input enable;switch(din-sel.read to Int())//读din-sel并转换成整数 output dout;{ reg[3:0]alu-reg;//寄存器数据类型case0://或操作 assign dout=(enable==1)?alu-reg:4’b0;res=din-a.read()|din-b.read();break; always@(opcode or din-a or din-b)case1://异或操作 case(opcode)res=din-a.read()^din-b.read();break; 3’b001:alu-reg=din-a|din-b;//或操作case2://与操作 3’b001:alu-reg=din-a^din-b;//异或操作res=din-a.read()&din-b.read();break; 3’b001:alu-reg=din-a&din-b;//与操作case3://取反操作 3’b001:alu-reg=~din-b;//取反操作res=~din-b.read();break; default:alu-reg=4’b0;//opcode为其他值} end case dout-res.write(res);//写输出结果endmodule}6 结 语 为了开发从传统硬件描述语言描述的知识产权(IP)到新一代描述语言SystemC的代码转换,必须首先研究其等效性.本文研究了Verilog HDL与Sys2 temC2.0从门级描述到系统级描述的语法等效性,并通过一个简单的例子说明了这种等效性.综合上面的・548・ 2004年9月 张雅绮等:Verilog HDL与SystemC的语法等效性讨论和前人的工作可以看出,对于门级以上级别的Verilog HDL 描述,在SystemC 中几乎有所有的对应描述,因此可以设计开发出一种能完成Verilog HDL描述的IP 到SystemC 描述的转换工具.参考文献:[1] Michael K eating ,Pierre Bricaud.Reuse Methodology M an 2ual f or S ystem 2on 2a 2chip Designs.[M ].2nd ed.Boston :K luwer Academic Publishers ,1999.[2] IEEE Standard Hardware Description Language Based onthe Verilog Hardware Description Language[S].IEEE Std 1364—1995,http :∥/reading/ieee/std/dasc/1364—1995.pdf ,2003..[3] Stuart Swan.An Introduction to System 2Level Modeling inSystemC 2.0,http :///white papers/Systemc-wp20.pdf ,2001207.[4] Agliada N ,Fin A ,Fummi F ,et al.On the Reuse of VHDLModules into SystemC Designs ,http :/eda.sci.univr.it/pub 2lications/sdl01.pdf ,2001.[5] Bollano G ,G arino P ,Turolla M ,et al.S ystemC ’s Impacton the Development of IP Libraries ,.pdf/Ipooe.pdf ,2000.[6] Leila Mahmoudi ,Ayough Ali.Verilog2SC :A Methodologyfor Converting Verilog HDL to SystemC[EB/OL ],http :///projects/sitedocs/document/Verilog2SC -tech/en/1.pdf ,2003201225.[7] Synopsys Inc.Describing Synthesizable RTL in SystemC ,http :///products /sld/rtl-systemc.pdf ,2003201215.《纳米技术与精密工程》征稿启事 经国家新闻出版署批准,《纳米技术与精密工程》已于2003年12月成功创刊.目前,该刊已被美国《化学文摘》、《中国核心期刊(遴选)数据库》、《中文科技期刊数据库》、《中国学术期刊(光盘版)数据库》、《中国生物学文摘》等国内外的著名数据库收录. 《纳米技术与精密工程》是纳米技术与精密工程领域专业性学术期刊,主要刊登纳米技术、微机电系统、精密加工和精密测量方面用中、英文撰写的具有创新性的科学研究论文、研究报告以及重要学术问题的讨论等,旨在反映国内外该领域及相关领域的重要科学研究成果,促进学术交流和科学技术发展. 本刊主要栏目为:纳米技术;微机电系统;精密加工;精密测量.欢迎国内外专家、学者踊跃投稿. 来稿请寄(300072)天津市天津大学出版社内《纳米技术与精密工程》编辑部.E 2mail :namijishu @. 诚挚地欢迎您提出宝贵建议,与我们共建一流期刊.・648・天 津 大 学 学 报 第37卷 第9期 。