MSP430寄存器手册

- 格式:pdf

- 大小:2.04 MB

- 文档页数:63

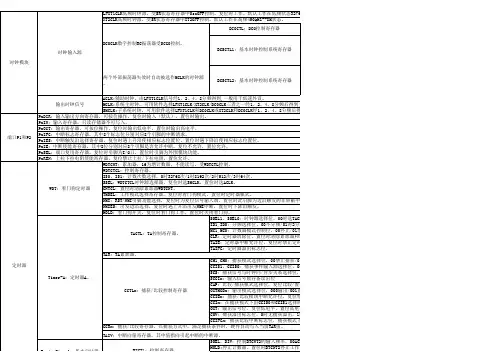

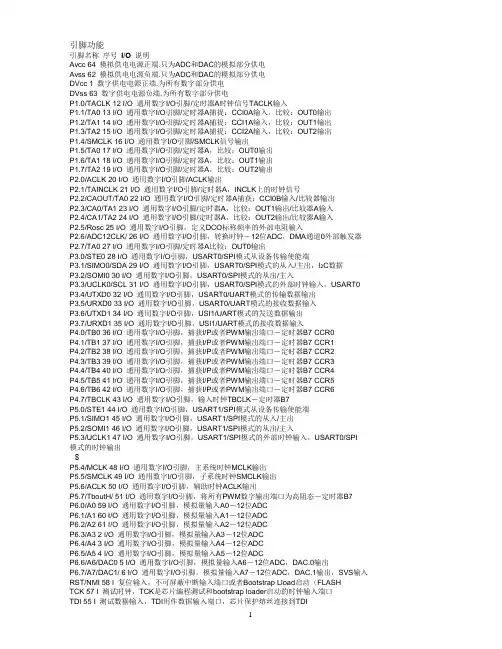

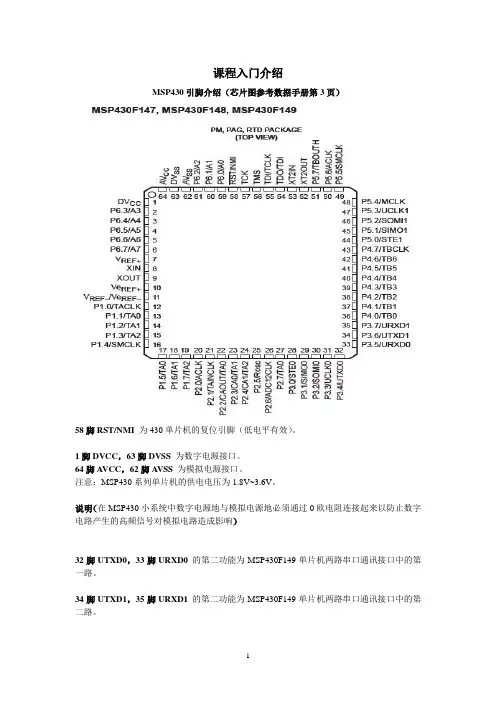

引脚功能引脚名称序号I/O 说明Avcc 64 模拟供电电源正端.只为ADC和DAC的模拟部分供电Avss 62 模拟供电电源负端.只为ADC和DAC的模拟部分供电DVcc 1 数字供电电源正端.为所有数字部分供电DVss 63 数字供电电源负端.为所有数字部分供电P1.0/TACLK 12 I/O 通用数字I/O引脚/定时器A时钟信号TACLK输入P1.1/TA0 13 I/O 通用数字I/O引脚/定时器A捕捉:CCI0A输入,比较:OUT0输出P1.2/TA1 14 I/O 通用数字I/O引脚/定时器A捕捉:CCI1A输入,比较:OUT1输出P1.3/TA2 15 I/O 通用数字I/O引脚/定时器A捕捉:CCI2A输入,比较:OUT2输出P1.4/SMCLK 16 I/O 通用数字I/O引脚/SMCLK信号输出P1.5/TA0 17 I/O 通用数字I/O引脚/定时器A,比较:OUT0输出P1.6/TA1 18 I/O 通用数字I/O引脚/定时器A,比较:OUT1输出P1.7/TA2 19 I/O 通用数字I/O引脚/定时器A,比较:OUT2输出P2.0/ACLK 20 I/O 通用数字I/O引脚/ACLK输出P2.1/TAINCLK 21 I/O 通用数字I/O引脚/定时器A,INCLK上的时钟信号P2.2/CAOUT/TA0 22 I/O 通用数字I/O引脚/定时器A捕获:CCI0B输入/比较器输出P2.3/CA0/TA1 23 I/O 通用数字I/O引脚/定时器A,比较:OUT1输出/比较器A输入P2.4/CA1/TA2 24 I/O 通用数字I/O引脚/定时器A,比较:OUT2输出/比较器A输入P2.5/Rosc 25 I/O 通用数字I/O引脚,定义DCO标称频率的外部电阻输入P2.6/ADC12CLK/ 26 I/O 通用数字I/O引脚,转换时钟-12位ADC,DMA通道0外部触发器P2.7/TA0 27 I/O 通用数字I/O引脚/定时器A比较:OUT0输出P3.0/STE0 28 I/O 通用数字I/O引脚,USART0/SPI模式从设备传输使能端P3.1/SIMO0/SDA 29 I/O 通用数字I/O引脚,USART0/SPI模式的从入/主出,I2C数据P3.2/SOMI0 30 I/O 通用数字I/O引脚,USART0/SPI模式的从出/主入P3.3/UCLK0/SCL 31 I/O 通用数字I/O引脚,USART0/SPI模式的外部时钟输入,USART0 P3.4/UTXD0 32 I/O 通用数字I/O引脚,USART0/UART模式的传输数据输出P3.5/URXD0 33 I/O 通用数字I/O引脚,USART0/UART模式的接收数据输入P3.6/UTXD1 34 I/O 通用数字I/O引脚,USI1/UART模式的发送数据输出P3.7/URXD1 35 I/O 通用数字I/O引脚,USI1/UART模式的接收数据输入P4.0/TB0 36 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR0P4.1/TB1 37 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR1P4.2/TB2 38 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR2P4.3/TB3 39 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR3P4.4/TB4 40 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR4P4.5/TB5 41 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR5P4.6/TB6 42 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR6P4.7/TBCLK 43 I/O 通用数字I/O引脚,输入时钟TBCLK-定时器B7P5.0/STE1 44 I/O 通用数字I/O引脚,USART1/SPI模式从设备传输使能端P5.1/SIMO1 45 I/O 通用数字I/O引脚,USART1/SPI模式的从入/主出P5.2/SOMI1 46 I/O 通用数字I/O引脚,USART1/SPI模式的从出/主入P5.3/UCLK1 47 I/O 通用数字I/O引脚,USART1/SPI模式的外部时钟输入,USART0/SPI 模式的时钟输出- 8 -P5.4/MCLK 48 I/O 通用数字I/O引脚,主系统时钟MCLK输出P5.5/SMCLK 49 I/O 通用数字I/O引脚,子系统时钟SMCLK输出P5.6/ACLK 50 I/O 通用数字I/O引脚,辅助时钟ACLK输出P5.7/TboutH/ 51 I/O 通用数字I/O引脚,将所有PWM数字输出端口为高阻态-定时器B7P6.0/A0 59 I/O 通用数字I/O引脚,模拟量输入A0-12位ADCP6.1/A1 60 I/O 通用数字I/O引脚,模拟量输入A1-12位ADCP6.2/A2 61 I/O 通用数字I/O引脚,模拟量输入A2-12位ADCP6.3/A3 2 I/O 通用数字I/O引脚,模拟量输入A3-12位ADCP6.4/A4 3 I/O 通用数字I/O引脚,模拟量输入A4-12位ADCP6.5/A5 4 I/O 通用数字I/O引脚,模拟量输入A5-12位ADCP6.6/A6/DAC0 5 I/O 通用数字I/O引脚,模拟量输入A6-12位ADC,DAC.0输出P6.7/A7/DAC1/ 6 I/O 通用数字I/O引脚,模拟量输入A7-12位ADC,DAC.1输出,SVS输入RST/NMI 58 I 复位输入,不可屏蔽中断输入端口或者Bootstrap Lload启动(FLASHTCK 57 I 测试时钟,TCK是芯片编程测试和bootstrap loader启动的时钟输入端口TDI 55 I 测试数据输入,TDI用作数据输入端口,芯片保护熔丝连接到TDITDO/TDI 54 I/O 测试数据输出端口,TDO/TDI数据输出或者编程数据输出引脚TMS 56 I 测试模式选择,TMS用作芯片编程和测试的输入端口VeREF+ 10 I/P 外部参考电压的输入VREF+ 7 O 参考电压的正输出引脚VREF-/VeREF- 11 O 内部参考电压或者外加参考电压的引脚XIN 8 I 晶体振荡器XT1的输入端口,可连接标准晶振或者钟表晶振XOUT/TCLK 9 I/O 晶体振荡器XT1的输出引脚或测试时钟输入XT2IN 53 I 晶体振荡器XT2的输入端口,只能连接标准晶振XT2OUT 52 O 晶体振荡器XT2的输出引脚时钟模块76543210 DCO.2DCO.1DCO.0MOD.4MOD.3MOD.2MOD.1MOD.0DCO.0-DCO.4 定义8 种频率之一,可以分段调节DCOCLK 频率,相邻两种频率相差10%。

T EXAS I NSTRUMENTSMPS430系列混合信号微控制器结构及模块用户指南目录1MSP430系列1.1特性与功能1.2系统关键性能1.3MSP430系列的各型号2结构概述2.1CPU2.2代码存储器2.3数据存储器(RAM)2.4运行控制2.5外围模块2.6振荡器、倍频器和时钟发生器3系统复位、中断和运行模式3.1系统复位和初始化3.2中断系统结构3.3中断处理3.3.1SFR中的中断控制位3.3.2外部中断3.4运行模式3.5低功耗模式3.5.1 低功耗模式0与模式1,LPM0和LPM1 3.5.2 低功耗模式2与模式3,LPM2和LPM3 3.5.3 低功耗模式4,LPM43.6 低功耗应用要点4 存储器组织4.1 存储器中的数据4.2 片内ROM组织4.2.1 ROM表的处理4.2.2 计算分支跳转和子程序调用4.3 RAM与外围模块组织4.3.1 RAM4.3.2 外围模块—地址定位4.3.3 外围模块--SFR5 16位CPU5.1 CPU寄存器5.1.1 程序计数器PC5.1.2 系统堆栈指针SP5.1.3 状态寄存器SR5.1.4 常数发生寄存器CG1与CG25.2 寻址模式5.2.1 寄存器模式5.2.2 变址模式5.2.3 符号模式5.2.4 绝对模式5.2.5 间接模式5.2.6 间接增量模式5.2.7 立即模式5.2.8 指令的时钟周期与长度5.3 指令组概述5.3.1 双操作数指令5.3.2 单操作数指令5.3.3 条件跳转5.3.4 模拟指令的短格式5.3.5 其它指令5.4 指令分布6 硬件乘法器6.1 硬件乘法器的操作6.2 硬件乘法器的寄存器6.3 硬件乘法器的SFR位6.4 硬件乘法器的软件限制6.4.1 硬件乘法器软件限制--寻址模式6.4.2 硬件乘法器软件限制--中断程序7 振荡器与系统时钟发生器7.1 晶体振荡器7.2 处理机时钟发生器7.3 系统时钟运行模式7.4 系统时钟控制寄存器7.4.1 模块寄存器7.4.2 与系统时钟发生器相关的SFR位7.5 DCO典型特性8 数字I/O配置8.1 通用端口P08.1.1 P0控制寄存器8.1.2 P0原理图8.1.3 P0中断控制功能8.2 通用端口P1、P28.2.1 P1、P2控制寄存器8.2.2 P1、P2原理图8.2.3 P1、P2中断控制功能8.3 通用端口P3、P48.3.1 P3、P4控制寄存器8.3.2 P3、P4原理图8.4 LCD端口8.5 LCD端口--定时器/端口比较器9 通用定时器/端口模块9.1 定时器/端口模块操作9.1.1 定时器/端口计数器TPCNT1,8位操作9.1.2 定时器/端口计数器TPCNT2,8位操作9.1.3 定时器/端口计数器,16位操作9.2 定时器/端口寄存器9.3 定时器/端口SFR位9.4 定时器/端口在A/D中的应用9.4.1 R/D转换原理9.4.2 分辨率高于8位的转换10 定时器10.1 Basic Timer110.1.1 BasicTimer1寄存器10.1.2 SFR位10.1.3 BasicTimer1操作10.1.4 BasicTimer1操作:LCD时钟信号f LCD 10.2 8位间隔(Interval)定时器/计数器10.2.1 8位定时器/计数器的操作10.2.2 8位定时器/计数器的寄存器10.2.3 与8位定时器/计数器有关的SFR 10.2.4 8位定时器/计数器在UART中的应用10.3 看门狗定时器10.3.1 看门狗定时器寄存器10.3.2 看门狗定时器中断控制功能10.3.3 看门狗定时器操作10.4 8位PWM定时器10.4.1 操作10.4.2 PWM寄存器11 Timer_A11.1 Timer_A的操作11.1.1 定时器操作11.1.2 捕获模式11.1.3 比较器模式11.1.4 输出单元11.2 Timer_A的寄存器11.2.1 Timer_A控制寄存器TACTL11.2.2 捕获/比较控制寄存器CCTL11.2.3 Timer_A中断向量寄存器11.3 Timer_A的应用11.3.1 Timer_A增计数模式应用11.3.2 Timer_A连续模式应用11.3.3 Timer_A增/减计数模式应用11.3.4 Timer_A软件捕获应用11.3.5 Timer_A处理异步串行通信协议11.4 Timer_A的特殊情况11.4.1 CCR0用作周期寄存器11.4.2 定时器寄存器的启/停11.4.3 输出单元Unit012 USART外围接口,UART模式12.1 异步操作12.1.1 异步帧格式12.1.2 异步通信的波特率发生器12.1.3 异步通信格式12.1.4 线路空闲多处理机模式12.1.5 地址位格式12.2 中断与控制功能12.2.1 USART接收允许12.2.2 USART发送允许12.2.3 USART接收中断操作12.2.4 USART发送中断操作12.3 控制与状态寄存器12.3.1 USART控制寄存器UCTL12.3.2 发送控制寄存器UTCTL12.3.3 接收控制寄存器URCTL12.3.4 波特率选择和调制控制寄存器12.3.5 USART接收数据缓存URXBUF12.3.6 USART发送数据缓存UTXBUF12.4 UART模式,低功耗模式应用特性12.4.1 由UART帧启动接收操作12.4.2 UART模式波特率与时钟频率12.4.3 节约MSP430资源的多处理机模式12.5 波特率的计算13 USART外围接口,SPI模式13.1 USART的同步操作13.1.1 SPI模式中的主模式,MM=1、SYNC=1 13.1.2 SPI模式中的从模式,MM=0、SYNC=1 13.2 中断与控制功能13.2.1 USART接收允许13.2.2 USART发送允许13.2.3 USART接收中断操作13.2.4 USART发送中断操作13.3 控制与状态寄存器13.3.1 USART控制寄存器13.3.2 发送控制寄存器UTCTL13.3.3 接收控制寄存器URCTL13.3.4 波特率选择和调制控制寄存器13.3.5 USART接收数据缓存URXBUF 13.3.6 USART发送数据缓存UTXBUF14 液晶显示驱动14.1 LCD驱动基本原理14.2 LCD控制器/驱动器14.2.1 LCD控制器/驱动器功能14.2.2 LCD控制及模式寄存器14.2.3 LCD显示存储器14.2.4 LCD操作软件例程14.3 LCD端口功能14.4 LCD与端口模式混合应用实例15 A/D转换器15.1 概述15.2 A/D转换操作15.2.1 A/D转换15.2.2 A/D中断15.2.3 A/D量程15.2.4 A/D电流源15.2.5 A/D输入端与多路切换15.2.6 A/D接地与降噪15.2.7 A/D输入与输出引脚15.3 A/D控制寄存器16 其它模块16.1 晶体振荡器16.2 上电电路16.3 晶振缓冲输出附录A 外围模块分布附录B 指令组说明附录C EPROM编程本书用途及表述约定MSP430用户指南以方便工程师及程序员使用的方式提供软件和硬件资料,以帮助开发应用MSP430系列的产品。

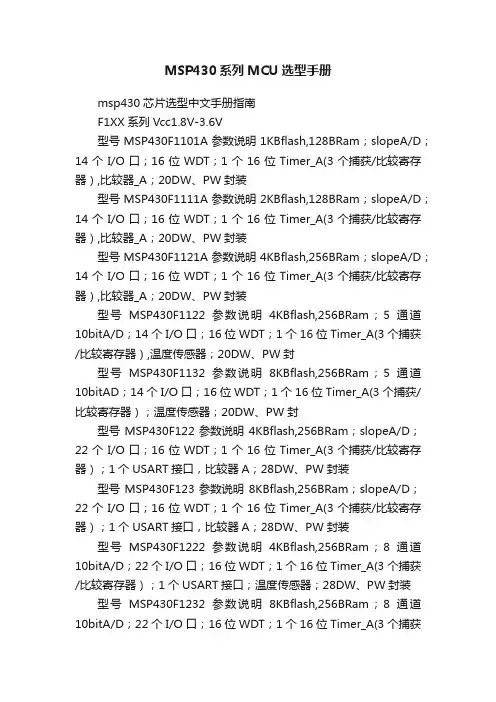

MSP430系列MCU选型手册msp430芯片选型中文手册指南F1XX系列Vcc1.8V-3.6V型号MSP430F1101A参数说明1KBflash,128BRam;slopeA/D;14个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器),比较器_A;20DW、PW封装型号MSP430F1111A参数说明2KBflash,128BRam;slopeA/D;14个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器),比较器_A;20DW、PW封装型号MSP430F1121A参数说明4KBflash,256BRam;slopeA/D;14个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器),比较器_A;20DW、PW封装型号MSP430F1122参数说明4KBflash,256BRam;5通道10bitA/D;14个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器),温度传感器;20DW、PW封型号MSP430F1132参数说明8KBflash,256BRam;5通道10bitAD;14个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);温度传感器;20DW、PW封型号MSP430F122参数说明4KBflash,256BRam;slopeA/D;22个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个USART接口,比较器A;28DW、PW封装型号MSP430F123参数说明8KBflash,256BRam;slopeA/D;22个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个USART接口,比较器A;28DW、PW封装型号MSP430F1222参数说明4KBflash,256BRam;8通道10bitA/D;22个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个USART接口;温度传感器;28DW、PW封装型号MSP430F1232参数说明8KBflash,256BRam;8通道10bitA/D;22个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个USART接口;温度传感器;28DW、PW封装型号MSP430F133参数说明8KBflash,256BRam;8通道12bitA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;比较器_A;温度传感器;64PM封装型号MSP430F135参数说明16KBflash,512BRam;8通道12bitA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;比较器_A;温度传感器;64PM封装型号MSP430F147参数说明32KBflash,1024BRam;8通道12bitA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1471参数说明32KBflash,1024BRam;slopeA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;64PM封装型号MSP430F148参数说明48KBflash,2048BRam;8通道12bitA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1481参数说明48KBflash,2048BRam;slopeA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;64PM封装型号MSP430F149参数说明60KBflash,2048BRam;8通道12bitA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1491参数说明60kflash,2048BRam;slopeA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;64PM封装型号MSP430F155参数说明16KBflash,512BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;I2C;比较器_A;温度传感器;64PM封装型号MSP430F156参数说明24KBflash,512BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;I2C;比较器_A;温度传感器;64PM封装型号MSP430F157参数说明32KBflash,1024BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;I2C;比较器_A;温度传感器;64PM 封装型号MSP430F167参数说明32KBflash,1024BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装型号MSP430F168参数说明48KBflash,2048BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装型号MSP430F169参数说明60KBflash,2048BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1610参数说明32KBflash,5120BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1611参数说明48KBflash,10240BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B (7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1612参数说明55kBflash,5120BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装F21X1系列Vcc1.8V-3.6V型号MSP430F2101参数说明1KBflash,128BRam;slopeA/D;16个I/O口;15/16位WDT;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;BrownoutProtection;20DW、PW、DGV封装型号MSP430F2111参数说明2KBflash,128BRam;slopeA/D;16个I/O口;15/16位WDT;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;BrownoutProtection;20DW、PW、DGV封装型号MSP430F2121参数说明4KBflash,256BRam;slopeA/D;16个I/O口;15/16位WDT;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;BrownoutProtection;20DW、PW、DGV封装型号MSP430F2131参数说明8KBflash,256BRam;slopeA/D;16个I/O口;15/16位WDT;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;BrownoutProtection;20DW、PW、DGV封装F4XX系列Vcc1.8V-3.6VWithLCD驱动型号MSP430F412参数说明4KBflash,256BRam;slopeA/D;48个I/O口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;64PM封装型号MSP430F413参数说明8KBflash,256BRam;slopeA/D;48个I/O口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;64PM封装型号MSP430F415参数说明16kBflash,512BRam;slopeA/D;48个I/O 口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A (3或5个捕获/比较寄存器);比较器_A;64PM 封装型号MSP430F417参数说明32kBflash,1024BRam;slopeA/D;48个I/O口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3或5个捕获/比较寄存器);比较器_A;64PM 封装型号MSP430FE423参数说明8KBflash,256BRam;SD16A/D;Emeter计量模块;14个I/O口;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个USART 接口;温度传感器;64PM封装型号MSP430FE425参数说明16KBflash,512BRam;SD16A/D;Emeter计量模块;14个I/O口;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个USART 接口;温度传感器;64PM封装型号MSP430FE427参数说明32KBflash,1KBRam;SD16A/D;Emeter计量模块;14个I/O口;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个USART 接口;比较器_A;温度传感器;64PM封装型号MSP430F4250参数说明16KBflash,256BRam;32个I/O 口;56段LCD;SD16位ADC (具有内部参考电压);12位DAC,1个16位Timer_A(3个捕获/比较寄存器);温度传感器模块;电源检测功能;48DL封装型号MSP430F4260参数说明24KBflash,256BRam;32个I/O 口;56段LCD;SD16位ADC (具有内部参考电压);12位DAC,1个16位Timer_A(3个捕获/比较寄存器);温度传感器模块;电源检测功能;48DL封装型号MSP430F4270参数说明32KBflash,256BRam;32个I/O 口;56段LCD;SD16位ADC (具有内部参考电压);12位DAC,1个16位Timer_A(3个捕获/比较寄存器);温度传感器模块;电源检测功能;48DL封装型号MSP430FG437参数说明32KBflash,1024BRam;12通道12bitA/D;双12bitD/A;48个I/O口;DMA;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;温度传感器;80PN 封装型号MSP430FG438参数说明48KBflash,2048BRam;12通道12bitA/D;双12bitD/A;48个I/O口;DMA;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;温度传感器;80PN 封装型号MSP430FG439参数说明60KBflash,2048BRam;12通道12bitA/D;双12bitD/A;48个I/O口;DMA;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;温度传感器;80PN 封装型号MSP430FW423参数说明8KBflash,256BRam;slopeA/D;流量测量ScanIF模块;48个I/O口;96段LCD;16位WDT;8bit 基本定时器;1个16位Timer_A(3或5个捕获/比较寄存器);比较器_A;64PM封装型号MSP430FW425参数说明16KBflash,512BRam;slopeA/D;流量测量ScanIF模块;48个I/O口;96段LCD;16位WDT;8bit 基本定时器;1个16位Timer_A(3或5个捕获/比较寄存器);比较器_A;64PM封装型号MSP430FW427参数说明32KBflash,1024BRam;slopeA/D;流量测量ScanIF模块;48个I/O口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3或5个捕获/比较寄存器);比较器_A;64PM封装型号MSP430F435参数说明16KBFlash,512BRam;8通道12bitA/D;48个I/O口;128/160段LCD;16位WDT;8bit基本定时器;16位Timer_A(3个捕获/比较寄存器)_A;16位Timer_B(3个捕获/比较寄存器)_B;1个USART接口;比较器_A;温度传感器;80PN/100PZ封装型号MSP430F436参数说明24KBFlash,1024KRam;8通道12bitA/D;48个I/O口;128/160段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器)_B;1个USART接口;比较器_A;温度传感器;80PN/100PZ封装型号MSP430F437参数说明32KBFlash,1024KRam;8通道12bitA/D;48个I/O口;128/160段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器)_B;1个USART接口;比较器_A;温度传感器;80PN/100PZ封装型号MSP430F447参数说明32KBFlash,1024KRam;8通道12bitA/D;48个I/O口;160段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B (7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;100PZ 封装型号MSP430F448参数说明48KBflash,2048BRam;8通道12bitA/D;48个I/O口;160段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B (7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;100PZ 封装型号MSP430F449参数说明60KBflash,2048BRam;8通道12bitA/D;48个I/O口;160段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B (7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;100PZ 封装型号TSS721AD参数说明M-BUS总线型号TRF6901PT参数说明无线射频率收发芯片。

用于MSP430™的IAR嵌入式工作平台版本3+用户指南Literature Number:ZHCU026XJune2004–Revised November2011内容Preface (5)1现在就开始! (7)1.1软件安装 (8)1.2LED闪烁 (8)1.3光盘和网络上重要的MSP430文档 (9)2开发流程 (10)2.1概述 (11)2.2使用KickStart (11)2.2.1项目设置 (12)2.2.2用于MSP430L092/MSP430C092的附件项目设置 (13)2.2.3从零开始创建一个项目 (15)2.2.4用于LPMx.5调试的附加项目设置 (16)2.2.5MSP430器件的密码保护 (17)2.2.6使用一个现有的IAR V1.x/V2.x/V3.x项目 (18)2.2.7堆栈管理和.xcl文件 (18)2.2.8如何生成德州仪器(TI).TXT(和其它格式)文件 (18)2.2.9示例程序概述 (18)2.3使用C-SPY (18)2.3.1断点类型 (19)2.3.2使用断点 (20)2.3.3使用单步执行 (21)2.3.4使用观察窗口 (21)A常见问题和解答 (23)A.1硬件 (24)A.2程序开发(汇编语言、C语言编译器、连接器) (24)A.3调试中(C-SPY) (26)B FET专用菜单 (30)B.1菜单 (31)B.1.1Emulator→Device Information (31)B.1.2Emulator→Release JTAG on Go (31)B.1.3Emulator→Resynchronize JTAG (31)B.1.4Emulator→Init New Device (31)B.1.5Emulator→Secure-Blow JTAG Fuse (31)B.1.6Emulator→Breakpoint Usage (31)B.1.7Emulator→Advanced→Clock Control (31)B.1.8Emulator→Advanced→Emulation Mode (31)B.1.9Emulator→Advanced→Memory Dump (32)B.1.10Emulator→Advanced→Breakpoint Combiner (32)B.1.11Emulator→State Storage Control (32)B.1.12Emulator→State Storage Window (32)B.1.13Emulator→Sequencer Control (32)B.1.14Emulator→"Power on"Reset (32)B.1.15Emulator→GIE on/off (32)B.1.16Emulator→Leave Target Running (32)B.1.17Emulator→Force Single Stepping (32)文档修订历史记录 (33)图片列表1-1.激活项目 (8)1-2.在Workspace Overview中激活项目 (9)2-1.L092模式 (13)2-2.C092仿真模式 (13)2-3.C092密码 (14)2-4.启用LPMx.5 (16)2-5.LPMx.5通知 (17)2-6.JTAG密码 (17)图表列表2-1.器件架构、断点和其它仿真特性 (19)4图片列表ZHCU026X–June2004–Revised November2011PrefaceZHCU026X–June2004–Revised November2011请先阅读关于本手册这本手册说明了IAR嵌入式工作平台(EW430)(带有MSP430超低功耗微控制器)™的使用方法。

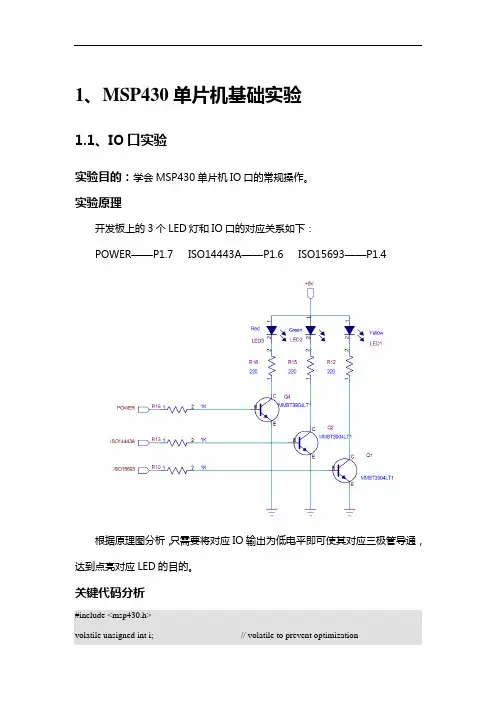

1、MSP430单片机基础实验1.1、IO口实验实验目的:学会MSP430单片机IO口的常规操作。

实验原理开发板上的3个LED灯和IO口的对应关系如下:POWER——P1.7 ISO14443A——P1.6 ISO15693——P1.4根据原理图分析,只需要将对应IO输出为低电平即可使其对应三极管导通,达到点亮对应LED的目的。

关键代码分析#include <msp430.h>volatile unsigned int i; // volatile to prevent optimizationint main(void){WDTCTL = WDTPW + WDTHOLD; // Stop watchdog timerP1DIR |= 0x80; // Set P1.7 to output directionfor (;;){P1OUT ^= 0x80; // Toggle P1.7 using exclusive-ORi = 50000; // Delaydo (i--);while (i != 0);}}对应工程详见:\感知RF2实验光盘2013\RFID技术实验\1-MSP430单片机基础实验\io实验结果POWER对应的LED灯闪烁。

作业1、对其他连个灯进行对应操作;2、流水灯显示编程控制。

1.2、定时器实验实验目的:学会MSP430单片机定时器常规配置及中断操作。

实验原理采用定时器TA溢出中断对LED灯进行取反操作。

关键代码分析#include <msp430.h>int main(void){WDTCTL = WDTPW + WDTHOLD; // Stop WDTP1DIR |= 0x80; // P1.0 outputTACCTL0 = CCIE; // TACCR0 interrupt enabledTACCR0 = 50000;TACTL = TASSEL_2 + MC_2; // SMCLK, contmode__bis_SR_register(LPM0_bits + GIE); // Enter LPM0 w/ interrupt}// Timer A0 interrupt service routine#pragma vector=TIMERA0_VECTOR__interrupt void Timer_A (void){P1OUT ^= 0x80; // Toggle P1.7TACCR0 += 50000; // Add Offset to TACCR0}对应工程详见\感知RF2实验光盘2013\RFID技术实验\1-MSP430单片机基础实验\timer实验结果LED灯快速闪烁,改变TACCR0值,闪烁时间间隔改变。

本文为翻译的MSP430x1xx Family User's Guide家庭用户指南,且只有寄存器的翻译比较准确,其他地方阅读时请自行判断语句的准确性本文为翻译的MSP430x1xx Family User's Guide家庭用户指南,且只有寄存器的翻译比较准确,其他地方阅读时请自行判断语句的准确性本文为翻译的MSP430x1xx Family User's Guide家庭用户指南,且只有寄存器的翻译比较准确,其他地方阅读时请自行判断语句的准确性USART外围接口,I2C模式通用同步/异步接收/传输(USART)外设接口支持USART0 I2C通信。

本章介绍I2C模式。

在I2C模式在MSP430x15x和MSP430x16x器件上实现。

专题页面15.1 I2C模块简介..............................................15-215.2 I2C模块操作..............................................15-415.3 I2C模块寄存器............................................15-2015.3 I2C模块寄存器I2C模块寄存器如表15-4。

表15-4.I2C寄存器注册简称注册类型地址初始状态I2C中断使能 I2CIE 读/写 050hI2C中断标志 I2CIFG 读/写 051hI2C数据计数 I2CNDAT 读/写 052hUSART控制 U0CTL 读/写 070hI2C传输控制 I2CTCTL 读/写 071hI2C数据控制 I2CDCTL 只读 072hI2C预分频器 I2CPSC 读/写 073hI2C SCL高 I2CSCLH 读/写 074hI2C SCL低 I2CSCLL 读/写 075hI2C数据 I2CDRW/ I2CDRB 读/写 076hI2C自己的地址 I2COA 读/写 0118hI2C从地址 I2CSA 读/写 011AhI2C中断向量 I2CIV 只读 011ChU0CTL,UART0控制寄存器,I2C模式rw−0rw−0rw−0rw−0rw−0rw−0rw−0rw−1RXDMAEN 第7位接收DMA能。

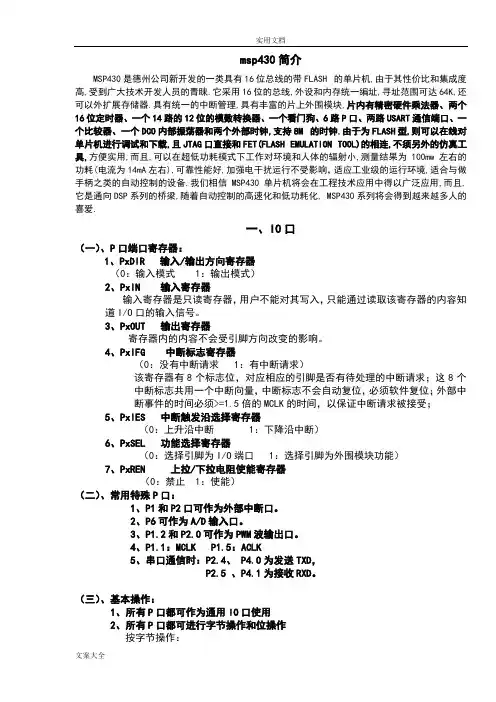

msp430简介MSP430是德州公司新开发的一类具有16位总线的带FLASH 的单片机,由于其性价比和集成度高,受到广大技术开发人员的青睐.它采用16位的总线,外设和内存统一编址,寻址范围可达64K,还可以外扩展存储器.具有统一的中断管理,具有丰富的片上外围模块,片内有精密硬件乘法器、两个16位定时器、一个14路的12位的模数转换器、一个看门狗、6路P口、两路USART通信端口、一个比较器、一个DCO内部振荡器和两个外部时钟,支持8M 的时钟.由于为FLASH型,则可以在线对单片机进行调试和下载,且JTAG口直接和FET(FLASH EMULATION TOOL)的相连,不须另外的仿真工具,方便实用,而且,可以在超低功耗模式下工作对环境和人体的辐射小,测量结果为100mw左右的功耗(电流为14mA左右),可靠性能好,加强电干扰运行不受影响,适应工业级的运行环境,适合与做手柄之类的自动控制的设备.我们相信MSP430单片机将会在工程技术应用中得以广泛应用,而且,它是通向DSP系列的桥梁,随着自动控制的高速化和低功耗化, MSP430系列将会得到越来越多人的喜爱.一、IO口(一)、P口端口寄存器:1、PxDIR 输入/输出方向寄存器(0:输入模式 1:输出模式)2、PxIN 输入寄存器输入寄存器是只读寄存器,用户不能对其写入,只能通过读取该寄存器的内容知道I/O口的输入信号。

3、PxOUT 输出寄存器寄存器内的内容不会受引脚方向改变的影响。

4、PxIFG 中断标志寄存器(0:没有中断请求 1:有中断请求)该寄存器有8个标志位,对应相应的引脚是否有待处理的中断请求;这8个中断标志共用一个中断向量,中断标志不会自动复位,必须软件复位;外部中断事件的时间必须>=1.5倍的MCLK的时间,以保证中断请求被接受;5、PxIES 中断触发沿选择寄存器(0:上升沿中断 1:下降沿中断)6、PxSEL 功能选择寄存器(0:选择引脚为I/O端口 1:选择引脚为外围模块功能)7、PxREN 上拉/下拉电阻使能寄存器(0:禁止 1:使能)(二)、常用特殊P口:1、P1和P2口可作为外部中断口。

MSP430简介(超详细·)msp430简介MSP430是德州公司新开发的⼀类具有16位总线的带FLASH 的单⽚机,由于其性价⽐和集成度⾼,受到⼴⼤技术开发⼈员的青睐.它采⽤16位的总线,外设和内存统⼀编址,寻址范围可达64K,还可以外扩展存储器.具有统⼀的中断管理,具有丰富的⽚上外围模块,⽚内有精密硬件乘法器、两个16位定时器、⼀个14路的12位的模数转换器、⼀个看门狗、6路P⼝、两路USART通信端⼝、⼀个⽐较器、⼀个DCO内部振荡器和两个外部时钟,⽀持8M 的时钟.由于为FLASH型,则可以在线对单⽚机进⾏调试和下载,且JTAG⼝直接和FET(FLASH EMULATION TOOL)的相连,不须另外的仿真⼯具,⽅便实⽤,⽽且,可以在超低功耗模式下⼯作对环境和⼈体的辐射⼩,测量结果为100mw左右的功耗(电流为14mA左右),可靠性能好,加强电⼲扰运⾏不受影响,适应⼯业级的运⾏环境,适合与做⼿柄之类的⾃动控制的设备.我们相信MSP430单⽚机将会在⼯程技术应⽤中得以⼴泛应⽤,⽽且,它是通向DSP 系列的桥梁,随着⾃动控制的⾼速化和低功耗化, MSP430系列将会得到越来越多⼈的喜爱.⼀、IO⼝(⼀)、P⼝端⼝寄存器:1、PxDIR 输⼊/输出⽅向寄存器(0:输⼊模式 1:输出模式)2、PxIN 输⼊寄存器输⼊寄存器是只读寄存器,⽤户不能对其写⼊,只能通过读取该寄存器的内容知道I/O⼝的输⼊信号。

3、PxOUT 输出寄存器寄存器内的内容不会受引脚⽅向改变的影响。

4、PxIFG 中断标志寄存器(0:没有中断请求 1:有中断请求)该寄存器有8个标志位,对应相应的引脚是否有待处理的中断请求;这8个中断标志共⽤⼀个中断向量,中断标志不会⾃动复位,必须软件复位;外部中断事件的时间必须>=1.5倍的MCLK的时间,以保证中断请求被接受;5、PxIES 中断触发沿选择寄存器(0:上升沿中断 1:下降沿中断)6、PxSEL 功能选择寄存器(0:选择引脚为I/O端⼝ 1:选择引脚为外围模块功能)7、PxREN 上拉/下拉电阻使能寄存器(0:禁⽌ 1:使能)(⼆)、常⽤特殊P⼝:1、P1和P2⼝可作为外部中断⼝。

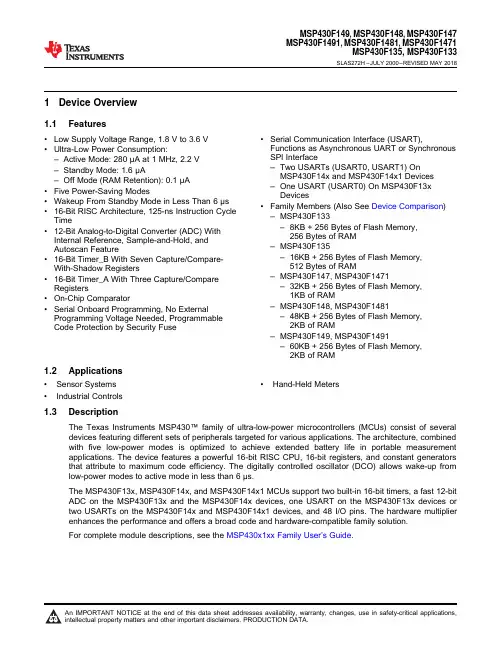

An IMPORTANT NOTICE at the end of this data sheet addresses availability,warranty,changes,use in safety-critical applications,intellectual property matters and other important disclaimers.PRODUCTION DATA.MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 20181Device Overview1.1Features•Low Supply Voltage Range,1.8V to 3.6V •Ultra-Low Power Consumption:–Active Mode:280µA at 1MHz,2.2V –Standby Mode:1.6µA–Off Mode (RAM Retention):0.1µA •Five Power-Saving Modes•Wakeup From Standby Mode in Less Than 6µs •16-Bit RISC Architecture,125-ns Instruction Cycle Time•12-Bit Analog-to-Digital Converter (ADC)With Internal Reference,Sample-and-Hold,and Autoscan Feature•16-Bit Timer_B With Seven Capture/Compare-With-Shadow Registers•16-Bit Timer_A With Three Capture/Compare Registers•On-Chip Comparator•Serial Onboard Programming,No External Programming Voltage Needed,Programmable Code Protection by Security Fuse•Serial Communication Interface (USART),Functions as Asynchronous UART or Synchronous SPI Interface–Two USARTs (USART0,USART1)On MSP430F14x and MSP430F14x1Devices –One USART (USART0)On MSP430F13x Devices•Family Members (Also See Device Comparison )–MSP430F133–8KB +256Bytes of Flash Memory,256Bytes of RAM –MSP430F135–16KB +256Bytes of Flash Memory,512Bytes of RAM–MSP430F147,MSP430F1471–32KB +256Bytes of Flash Memory,1KB of RAM–MSP430F148,MSP430F1481–48KB +256Bytes of Flash Memory,2KB of RAM–MSP430F149,MSP430F1491–60KB +256Bytes of Flash Memory,2KB of RAM 1.2Applications•Sensor Systems •Industrial Controls•Hand-Held Meters1.3DescriptionThe Texas Instruments MSP430™family of ultra-low-power microcontrollers (MCUs)consist of several devices featuring different sets of peripherals targeted for various applications.The architecture,combined with five low-power modes is optimized to achieve extended battery life in portable measurement applications.The device features a powerful 16-bit RISC CPU,16-bit registers,and constant generators that attribute to maximum code efficiency.The digitally controlled oscillator (DCO)allows wake-up from low-power modes to active mode in less than 6µs.The MSP430F13x,MSP430F14x,and MSP430F14x1MCUs support two built-in 16-bit timers,a fast 12-bit ADC on the MSP430F13x and the MSP430F14x devices,one USART on the MSP430F13x devices or two USARTs on the MSP430F14x and MSP430F14x1devices,and 48I/O pins.The hardware multiplier enhances the performance and offers a broad code and hardware-compatible family solution.For complete module descriptions,see the MSP430x1xx Family User’s Guide .XT2IN XT2OUTTMS TCK TDI/TCLK TDO/TDIRST/NMIR 2MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Device Overview Copyright ©2000–2018,Texas Instruments Incorporated(1)For the most current device,package,and ordering information,see the Package Option Addendum in Section 8,or see the TI website at .(2)The sizes shown here are approximations.For the package dimensions with tolerances,see the Mechanical Data in Section 8.Device Information (1)PART NUMBERPACKAGE BODY SIZE (2)MSP430F149IPM LQFP (64)10mm ×10mm MSP430F149IPAG TQFP (64)10mm ×10mm MSP430F1491IRTD VQFN (64)9mm ×9mm1.4Functional Block DiagramsFigure 1-1shows the functional block diagram for the MSP430F13x MCUs.Figure 1-1.Functional Block Diagram,MSP430F13xXT2OUTTMS TCK TDI/TCLK TDO/TDIRST/NMIRR 3MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Device Overview Copyright ©2000–2018,Texas Instruments Incorporated Figure 1-2.Functional Block Diagram,MSP430F14xFigure 1-3shows the functional block diagram for the MSP430F14x1MCUs.Figure 1-3.Functional Block Diagram,MSP430F14x14MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Table of Contents Copyright ©2000–2018,Texas Instruments IncorporatedTable of Contents1Device Overview (1)1.1Features ..............................................11.2Applications ...........................................11.3Description ............................................11.4Functional Block Diagrams (2)2Revision History .........................................53Device Comparison . (6)3.1Related Products (6)4Terminal Configuration and Functions (7)4.1Pin Diagrams .........................................74.2Signal Descriptions (105)Specifications (16)5.1Absolute Maximum Ratings (16)5.2ESD Ratings........................................165.3Recommended Operating Conditions ...............165.4Supply Current Into AV CC and DV CC ExcludingExternal Current .....................................175.5Thermal Resistance Characteristics ................185.6Schmitt-Trigger Inputs –Ports P1,P2,P3,P4,P5,and P6...............................................185.7Standard Inputs –RST/NMI,JTAG (TCK,TMS,TDI/TCLK,TDO/TDI)...............................185.8Inputs –Px.y,TAx,TBx............................185.9Leakage Current ....................................195.10Outputs –Ports P1,P2,P3,P4,P5,and P6.......195.11Output Frequency ..................................195.12Typical Characteristics –Ports P1,P2,P3,P4,P5,and P6Outputs (20)5.13Wake-up Time From LPM3.........................215.14RAM .................................................215.15Comparator_A .......................................215.16Typical Characteristics –Comparator_A ............225.17PUC and POR ......................................235.18DCO Frequency .....................................245.19DCO When Using R OSC .............................255.20Crystal Oscillator,LFXT1...........................265.21Crystal Oscillator,XT2..............................265.22USART0,USART1..................................265.2312-Bit ADC,Power Supply and Input RangeConditions ...........................................275.2412-Bit ADC,External Reference ....................275.2512-Bit ADC,Built-In Reference . (28)5.2612-Bit ADC,Timing Parameters....................305.2712-Bit ADC,Linearity Parameters ...................305.2812-Bit ADC,Temperature Sensor and Built-In V MID315.29Flash Memory .......................................315.30JTAG Interface ......................................325.31JTAG Fuse.........................................326Detailed Description (33)6.1CPU .................................................336.2Instruction set .......................................346.3Operating Modes ....................................346.4Interrupt Vector Addresses ..........................356.5Bootloader (BSL)....................................356.6JTAG Fuse Check Mode ............................366.7Memory ..............................................366.8Peripherals ..........................................406.9Input/Output Diagrams (48)7Device and Documentation Support (59)7.1Getting Started and Next Steps .....................597.2Device Nomenclature ...............................597.3Tools and Software .................................617.4Documentation Support .............................627.5Related Links ........................................637.6Community Resources ..............................637.7Trademarks ..........................................637.8Electrostatic Discharge Caution .....................647.9Export Control Notice ...............................647.10Glossary .............................................648Mechanical,Packaging,and OrderableInformation (65)5MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Revision History Copyright ©2000–2018,Texas Instruments Incorporated 2Revision HistoryNOTE:Page numbers for previous revisions may differ from page numbers in the current version.Changes from February 12,2009to May 23,2018Page•Document format and organization changes throughout ........................................................................1•Added Section 1.2,Applications ....................................................................................................1•Added Section 3,Device Comparison ............................................................................................6•Added Section 5.2,ESD Ratings ..................................................................................................16•Removed note (2)with duplicate information from the f LFXT1parameter in Section 5.3,Recommended OperatingConditions ...........................................................................................................................16•Removed duplicate conditions "XTS =0,SELM =0or 1"from the second row of Test Conditions on the I (AM)parameter in Section 5.4,Supply Current Into AV CC and DV CC Excluding External Current ..............................17•Added Section 5.5,Thermal Resistance Characteristics ......................................................................18•Removed ADC12DIV from the equation in the TYP value of the t CONVERT parameter (because ADC12CLK isafter division)in Section 5.26,12-Bit ADC,Timing Parameters ..............................................................30•Changed all instances of bootstrap loader to bootloader throughout document ............................................35•Added Section 7,Device and Documentation Support (59)6MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Device Comparison Copyright ©2000–2018,Texas Instruments Incorporated(1)For the most current package and ordering information,see the Package Option Addendum in Section 8,or see the TI website at.(2)Package drawings,thermal data,and symbolization are available at .(3)Each number in the sequence represents an instantiation of Timer_A with its associated number of capture/compare registers and PWM output generators available.For example,a number sequence of 3,5would represent two instantiations of Timer_A,the first instantiation having 3and the second instantiation having 5capture/compare registers and PWM output generators,respectively.(4)Each number in the sequence represents an instantiation of Timer_B with its associated number of capture/compare registers and PWM output generators available.For example,a number sequence of 3,5would represent two instantiations of Timer_B,the first instantiation having 3and the second instantiation having 5capture/compare registers and PWM output generators,respectively.3Device ComparisonTable 3-1summarizes the features of the device variants in this data sheet.Table 3-1.Device Comparison (1)(2)Device Flash SRAM Timer_A (3)Timer_B (4)USART COMP_AADC12(Channels)I/Os Package MSP430F14960KB 2KB 372184864-pin PM 64-pin PAG 64-pin RTD MSP430F149160KB 2KB 372184864-pin PM 64-pin RTD MSP430F14848KB 2KB 372184864-pin PM 64-pin PAG 64-pin RTD MSP430F148148KB 2KB 372184864-pin PM 64-pin RTD MSP430F14732KB 1KB 372184864-pin PM 64-pin PAG 64-pin RTD MSP430F147132KB 1KB 372184864-pin PM 64-pin RTD MSP430F13516KB512bytes331184864-pin PM 64-pin PAG 64-pin RTD MSP430F1338KB 256bytes 331184864-pin PM 64-pin PAG 64-pin RTD3.1Related ProductsFor information about other devices in this family of products or related products,see the following links.TI 16-bit and 32-bit microcontrollers High-performance,low-power solutions to enable the autonomousfuture Products for MSP430ultra-low-power microcontrollersOne platform.One ecosystem.Endlesspossibilities.Products for other MSP430microcontrollers MCUs for metrology,monitoring,system control,andcommunications Companion Products for MSP430F149Review products that are frequently purchased or used with thisproduct.Reference Designs The TI Designs Reference Design Library is a robust reference design library thatspans analog,embedded processor,and connectivity.Created by TI experts to help you jump start your system design,all TI Designs include schematic or block diagrams,BOMs,and design files to speed your time to market.171819P5.4/MCLK P5.3P5.2P5.1P5.0P4.7/TBCLK P4.6P4.5P4.4P4.3P4.2/TB2P4.1/TB1P4.0/TB0P3.7P3.6P3.5/URXD0484746454443424140393837363534332012345678910111213141516DV CC P6.3/A3P6.4/A4P6.5/A5P6.6/A6P6.7/A7V REF+XIN XOUT Ve REF+V REF−/Ve REF−P1.0/TACLK P1.1/TA0P1.2/TA1P1.3/TA2P1.4/SMCLK21222324P 5.6/A C L K T D O /T D I 63626160596458A V P 6.2/A 2P 6.1/A 1P 6.0/A 0R S T /N M I T C K T M S P 2.6/A D C 12C L K P 2.7/T A 0P 3.0/S T E 0P 3.1/S I M O 0P 1.7/T A 2P 2.1/T A I N C L K P 2.2/C A O U T /T A 0P 2.3/C A 0/T A 1P 2.4/C A 1/T A 2P 2.5/R o s c 5655545725262728295352P 1.5/T A 0X T 2I N X T 2O U T 515049303132P 3.2/S O M I 0P 3.3/U C L K 0P 3.4/U T X D 0P 5.7/T B O U T HT D I /T C L K P 5.5/S M C L KA V D V P 1.6/T A 1P 2.0/A C L K C CS SS S7MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Terminal Configuration and Functions Copyright ©2000–2018,Texas Instruments Incorporated 4Terminal Configuration and Functions4.1Pin DiagramsFigure 4-1shows the pinout for the MSP430F133and MSP430F135MCUs in the 64-pin PM,PAG,and RTD packages.Figure 4-1.64-Pin PM,PAG,or RTD Package (Top View)for MSP430F133and MSP430F135171819P5.4/MCLK P5.3/UCLK1P5.2/SOMI1P5.1/SIMO1P5.0/STE1P4.7/TBCLK P4.6/TB6P4.5/TB5P4.4/TB4P4.3/TB3P4.2/TB2P4.1/TB1P4.0/TB0P3.7/URXD1P3.6/UTXD1P3.5/URXD0484746454443424140393837363534332012345678910111213141516DV CC P6.3/A3P6.4/A4P6.5/A5P6.6/A6P6.7/A7V REF+XIN XOUT Ve REF+V REF−/Ve REF−P1.0/TACLK P1.1/TA0P1.2/TA1P1.3/TA2P1.4/SMCLK21222324P 5.6/A C L K T D O /T D I 63626160596458A V P 6.2/A 2P 6.1/A 1P 6.0/A 0R S T /N M I T C K T M S P 2.6/A D C 12C L K P 2.7/T A 0P 3.0/S T E 0P 3.1/S I M O 0P 1.7/T A 2P 2.1/T A I N C L K P 2.2/C A O U T /T A 0P 2.3/C A 0/T A 1P 2.4/C A 1/T A 2P 2.5/R o s c 5655545725262728295352P 1.5/T A 0X T 2I N X T 2O U T 515049303132P 3.2/S O M I 0P 3.3/U C L K 0P 3.4/U T X D 0P 5.7/T B O U T HT D I /T C L K P 5.5/S M C L KA V D V P 1.6/T A 1P 2.0/A C L K C CS SS S8MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Terminal Configuration and FunctionsCopyright ©2000–2018,Texas Instruments IncorporatedFigure 4-2shows the pinout for the MSP430F147,MSP430F148,and MSP430F149MCUs in the 64-pin PM,PAG,and RTD packages.Figure 4-2.64-Pin PM,PAG,or RTD Package (Top View)for MSP430F147,MSP430F148,and MSP430F149171819P5.4/MCLK P5.3/UCLK1P5.2/SOMI1P5.1/SIMO1P5.0/STE1P4.7/TBCLK P4.6/TB6P4.5/TB5P4.4/TB4P4.3/TB3P4.2/TB2P4.1/TB1P4.0/TB0P3.7/URXD1P3.6/UTXD1P3.5/URXD0484746454443424140393837363534332012345678910111213141516DV CC P6.3P6.4P6.5P6.6P6.7ReservedXIN XOUT DV SS DV SSP1.0/TACLK P1.1/TA0P1.2/TA1P1.3/TA2P1.4/SMCLK21222324P 5.6/A C L K T D O /T D I 63626160596458A V P 6.2P 6.1P 6.0R S T /N M I T C K T M S P 2.6P 2.7/T A 0P 3.0/S T E 0P 3.1/S I M O 0P 1.7/T A 2P 2.1/T A I N C L K P 2.2/C A O U T /T A 0P 2.3/C A 0/T A 1P 2.4/C A 1/T A 2P 2.5/R o s c 5655545725262728295352P 1.5/T A 0X T 2I N X T 2O U T 515049303132P 3.2/S O M I 0P 3.3/U C L K 0P 3.4/U T X D 0P 5.7/T B O U T HT D I /T C L K P 5.5/S M C L KA V D V P 1.6/T A 1P 2.0/A C L K C CS SS S9MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Terminal Configuration and Functions Copyright ©2000–2018,Texas Instruments Incorporated Figure 4-3shows the pinout for the MSP430F1471,MSP430F1481,and MSP430F1491MCUs in the 64-pin PM and RTD packages.Figure 4-3.64-Pin PM or RTD Package (Top View)for MSP430F1471,MSP430F1481,and MSP430F149110MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Terminal Configuration and FunctionsCopyright ©2000–2018,Texas Instruments Incorporated4.2Signal DescriptionsTable 4-1describes the signals for the MSP430F13x and MSP430F14x MCUs.See Table 4-2for the MSP430F14x1signal descriptions.Table 4-1.Signal Descriptions for MSP430F13x and MSP430F14xSIGNAL NAME PIN NO.I/O DESCRIPTIONAV CC 64Analog supply voltage,positive terminal.Supplies the analog portion of the ADC.AV SS 62Analog supply voltage,negative terminal.Supplies the analog portion of the ADC.DV CC 1Digital supply voltage,positive terminal.Supplies all digital parts.DV SS63Digital supply voltage,negative terminal.Supplies all digital parts.P1.0/TACLK 12I/O General-purpose digital I/O pin Timer_A,clock signal TACLK inputP1.1/TA013I/OGeneral-purpose digital I/O pinTimer_A,capture:CCI0A input,compare:Out0output BSL transmitP1.2/TA114I/O General-purpose digital I/O pinTimer_A,capture:CCI0A input,compare:Out0output BSL transmitP1.3/TA215I/O General-purpose digital I/O pinTimer_A,capture:CCI2A input,compare:Out2output P1.4/SMCLK 16I/O General-purpose digital I/O pin SMCLK signal outputP1.5/TA017I/O General-purpose digital I/O pin Timer_A,compare:Out0output P1.6/TA118I/O General-purpose digital I/O pin Timer_A,compare:Out1output P1.7/TA219I/O General-purpose digital I/O pin Timer_A,compare:Out2output/P2.0/ACLK 20I/O General-purpose digital I/O pin ACLK outputP2.1/TAINCLK21I/OGeneral-purpose digital I/O pin Timer_A,clock signal at INCLK P2.2/CAOUT/TA022I/OGeneral-purpose digital I/O pin Comparator_A outputTimer_A,capture:CCI0B input BSL receiveP2.3/CA0/TA123I/OGeneral-purpose digital I/O pin Timer_A,compare:Out1output Comparator_A inputP2.4/CA1/TA224I/O General-purpose digital I/O pin Timer_A,compare:Out2output Comparator_A inputP2.5/R OSC 25I/O General-purpose digital I/O pininput for external resistor defining the DCO nominal frequency P2.6/ADC12CLK 26I/O General-purpose digital I/O pin Conversion clock for ADC P2.7/TA027I/O General-purpose digital I/O pin Timer_A,compare:Out0outputP3.0/STE028I/O General-purpose digital I/O pinSlave transmit enable for USART0in SPI mode P3.1/SIMO029I/O General-purpose digital I/O pinSlave in/master out of USART0in SPI mode P3.2/SOMI030I/O General-purpose digital I/O pinSlave out/master in of USART0in SPI modeP3.3/UCLK031I/O General-purpose digital I/OUSART0clock:external input in UART or SPI mode,output in SPI mode P3.4/UTXD032I/OGeneral-purpose digital I/O pinTransmit data out for USART0in UART mode11MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Terminal Configuration and Functions Copyright ©2000–2018,Texas Instruments IncorporatedTable 4-1.Signal Descriptions for MSP430F13x and MSP430F14x (continued)SIGNAL NAMEPIN NO.I/O DESCRIPTION (1)MSP430F14x devices onlyP3.5/URXD033I/O General-purpose digital I/O pin Receive data in for USART0in UART mode P3.6/UTXD1(1)34I/O General-purpose digital I/O pin Transmit data out for USART1in UART mode P3.7/URXD1(1)35I/O General-purpose digital I/O pin Receive data in for USART1in UART mode P4.0/TB0.36I/O General-purpose digital I/O pin Timer_B,capture:CCI0A or CCI0B input,compare:Out0output P4.1/TB137I/O General-purpose digital I/O pin Timer_B,capture:CCI1A or CCI1B input,compare:Out1output P4.2/TB238I/O General-purpose digital I/O pin Timer_B,capture:CCI2A or CCI2B input,compare:Out2output P4.3/TB3(1)39I/O General-purpose digital I/O pin Timer_B,capture:CCI3A or CCI3B input,compare:Out3output P4.4/TB4(1)40I/O General-purpose digital I/O pin Timer_B,capture:CCI4A or CCI4B input,compare:Out4output P4.5/TB5(1)41I/O General-purpose digital I/O pin Timer_B,capture:CCI5A or CCI5B input,compare:Out5output P4.6/TB6(1)42I/O General-purpose digital I/O pin Timer_B,capture:CCI6A or CCI6B input,compare:Out6output P4.7/TBCLK43I/O General-purpose digital I/O pin Timer_B,clock signal TBCLK input P5.0/STE1(1)44I/O General-purpose digital I/O pin Slave transmit enable for USART1in SPI mode P5.1/SIMO1(1)45I/O General-purpose digital I/O pin Slave in/master out of USART1in SPI mode P5.2/SOMI1(1)46I/O General-purpose digital I/O pin Slave out/master in of USART1in SPI mode P5.3/UCLK1(1)47I/O General-purpose digital I/O pin USART1clock:external input in UART or SPI mode,output in SPI mode P5.4/MCLK48I/O General-purpose digital I/O pin Main system clock MCLK output P5.5/SMCLK49I/O General-purpose digital I/O pin Submain system clock SMCLK output P5.6/ACLK50I/O General-purpose digital I/O pin Auxiliary clock ACLK output P5.7/TBOUTH51I/O General-purpose digital I/O pin Switch all PWM digital output ports to high impedance for Timer_B7(TB0to TB6)P6.0/A059I/O General-purpose digital I/O pin Analog input A0for ADC P6.1/A160I/O General-purpose digital I/O pin Analog input A1for ADC P6.2/A261I/O General-purpose digital I/O pin Analog input A2for ADC P6.3/A32I/O General-purpose digital I/O pin Analog input A3for ADC P6.4/A43I/O General-purpose digital I/O pin Analog input A4for ADC P6.5/A54I/O General-purpose digital I/O pin Analog input A5for ADC P6.6/A65I/O General-purpose digital I/O pin Analog input A6for ADC P6.7/A76I/O General-purpose digital I/O pinAnalog input A7for ADC12MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Terminal Configuration and Functions Copyright ©2000–2018,Texas Instruments IncorporatedTable 4-1.Signal Descriptions for MSP430F13x and MSP430F14x (continued)SIGNAL NAMEPIN NO.I/O DESCRIPTION RST/NMI58I Reset input Nonmaskable interrupt input port Bootloader start TCK57I Test clock,the clock input port for device programming test and bootloader start TDI/TCLK55I Test data input or test clock input.The device protection fuse is connected to TDI/TCLK.TDO/TDI54I/O Test data output or programming data input TMS56I Test mode select,used as an input port for device programming and test VeREF+10I Input for an external reference voltage to the ADC VREF+7O Output of positive terminal of the reference voltage in the ADC VREF −/VeREF −11I Negative terminal for the ADC reference voltage for both sources,the internal reference voltage or an external applied reference voltage XIN8I Input port for crystal oscillator XT1,standard or watch crystals can be connected XOUT9O Output terminal of crystal oscillator XT1XT2IN53I Input port for crystal oscillator XT2,only standard crystals can be connected XT2OUT52O Output terminal of crystal oscillator XT2QFN Pad NA NA QFN package pad,connect to DV SS13MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Terminal Configuration and Functions Copyright ©2000–2018,Texas Instruments Incorporated Table 4-2describes the signals for the MSP430F14x1MCUs.See Table 4-1for the MSP430F13x and MSP430F14x signal descriptions.Table 4-2.Signal Descriptions for MSP430F14x1SIGNAL NAMEPIN NO.I/O DESCRIPTION AV CC64Analog supply voltage positive terminal AV SS62Analog supply voltage negative terminal DV CC1Digital supply voltage,positive terminal.Supplies all digital parts.DV SS63Digital supply voltage,negative terminal.Supplies all digital parts.P1.0/TACLK12I/O General-purpose digital I/O pin Timer_A,clock signal TACLK input P1.1/TA013I/O General-purpose digital I/O pin Timer_A,capture:CCI0A input,compare:Out0output BSL transmit P1.2/TA114I/O General-purpose digital I/O pin Timer_A,capture:CCI1A input,compare:Out1output P1.3/TA215I/O General-purpose digital I/O pin Timer_A,capture:CCI2A input,compare:Out2output P1.4/SMCLK16I/O General-purpose digital I/O pin SMCLK signal output P1.5/TA017I/O General-purpose digital I/O pin Timer_A,compare:Out0output P1.6/TA118I/O General-purpose digital I/O pin Timer_A,compare:Out1output P1.7/TA219I/O General-purpose digital I/O pin Timer_A,compare:Out2output P2.0/ACLK20I/O General-purpose digital I/O pin ACLK output P2.1/TAINCLK 21I/O General-purpose digital I/O pinTimer_A,clock signal at INCLKP2.2/CAOUT/TA022I/O General-purpose digital I/O pinTimer_A,capture:CCI0B inputComparator_A outputBSL receiveP2.3/CA0/TA123I/O General-purpose digital I/O pinTimer_A,compare:Out1outputComparator_A inputP2.4/CA1/TA224I/O General-purpose digital I/O pinTimer_A,compare:Out2outputComparator_A inputP2.5/R OSC 25I/O General-purpose digital I/O pinInput for external resistor defining the DCO nominal frequencyP2.626I/O General-purpose digital I/O pinP2.7/TA027I/O General-purpose digital I/O pinTimer_A,compare:Out0outputP3.0/STE028I/O General-purpose digital I/O pinSlave transmit enable for USART0in SPI modeP3.1/SIMO029I/O General-purpose digital I/O pinSlave in/master out of USART0in SPI modeP3.2/SOMI030I/O General-purpose digital I/O pinSlave out/master in of USART0in SPI modeP3.3/UCLK031I/O General-purpose digital I/OUSART0clock:external input in UART or SPI mode,output in SPI modeP3.4/UTXD032I/O General-purpose digital I/O pinTransmit data out for USART0in UART modeP3.5/URXD033I/OGeneral-purpose digital I/O pinReceive data in for USART0in UART mode14MSP430F149,MSP430F148,MSP430F147MSP430F1491,MSP430F1481,MSP430F1471MSP430F135,MSP430F133SLAS272H –JULY 2000–REVISED MAY 2018Terminal Configuration and FunctionsCopyright ©2000–2018,Texas Instruments Incorporated Table 4-2.Signal Descriptions for MSP430F14x1(continued)SIGNAL NAMEPIN NO.I/O DESCRIPTION P3.6/UTXD134I/O General-purpose digital I/O pin Transmit data out for USART1in UART mode P3.7/URXD135I/O General-purpose digital I/O pin Receive data in for USART1in UART mode P4.0/TB0.36I/O General-purpose digital I/O pin Timer_B,capture:CCI0A or CCI0B input,compare:Out0output P4.1/TB137I/O General-purpose digital I/O pin Timer_B,capture:CCI1A or CCI1B input,compare:Out1output P4.2/TB238I/O General-purpose digital I/O pin Timer_B,capture:CCI2A or CCI2B input,compare:Out2output P4.3/TB339I/O General-purpose digital I/O pin Timer_B,capture:CCI3A or CCI3B input,compare:Out3output P4.4/TB440I/O General-purpose digital I/O pin Timer_B,capture:CCI4A or CCI4B input,compare:Out4output P4.5/TB541I/O General-purpose digital I/O pin Timer_B,capture:CCI5A or CCI5B input,compare:Out5output P4.6/TB642I/O General-purpose digital I/O pin Timer_B,capture:CCI6A or CCI6B input,compare:Out6output P4.7/TBCLK43I/O General-purpose digital I/O pin Timer_B,clock signal TBCLK input P5.0/STE144I/O General-purpose digital I/O pin Slave transmit enable for USART1in SPI mode P5.1/SIMO145I/O General-purpose digital I/O pin Slave in/master out of USART1in SPI mode P5.2/SOMI146I/O General-purpose digital I/O pin Slave out/master in of USART1in SPI mode P5.3/UCLK147I/O General-purpose digital I/O pin USART1clock:external input in UART or SPI mode,output in SPI mode P5.4/MCLK48I/O General-purpose digital I/O pin Main system clock MCLK output P5.5/SMCLK49I/O General-purpose digital I/O pin Submain system clock SMCLK output P5.6/ACLK50I/O General-purpose digital I/O pin Auxiliary clock ACLK output P5.7/TBOUTH51I/O General-purpose digital I/O pin Switch all PWM digital output ports to high impedance for Timer_B7(TB0to TB6)P6.059I/O General-purpose digital I/O pin P6.160I/O General-purpose digital I/O pin P6.261I/O General-purpose digital I/O pin P6.32I/O General-purpose digital I/O pin P6.43I/O General-purpose digital I/O pin P6.54I/O General-purpose digital I/O pin P6.65I/O General-purpose digital I/O pin P6.76I/O General-purpose digital I/O pin RST/NMI58I Reset input Nonmaskable interrupt input port Bootloader start TCK57I Test clock,the clock input port for device programming test and bootloader start TDI/TCLK55I Test data input or test clock input.The device protection fuse is connected to TDI/TCLK.TDO/TDI54I/O Test data output or programming data input TMS56I Test mode select,used as an input port for device programming and test DV SS10I Connect to DV SS Reserved7Reserved,do not connect externally。

指令集描述P(220—257)* DECX.A目的操作数减1* DECX.[W] 目的操作数减1* DECX.B 目的操作数减1语法DECV.A dstDECX dst 或DECX.W dstDECX.B dst操作dst – 1 →dst仿真SUBX.A#1,dstSUBX #1,dstSUBX.B #1,dst说明目的操作数减1 以前的内容丢失状态位N :结果为负时置位为正时复位Z : dst包含1时置位其他情况时复位C : dst包含0时置位其他情况时复位V : 产生算术溢出时置位其他情况时复位目的操作数的初始值为08000H时置位其他情况时复位方式位OscOff(晶振控制位),CPUOff(CPU控制位)和GIE(中断标志位)不受影响例子目的地址操作数减一DECX.A TONI ; TONI减一* DECDX.[W] 目的操作数减2* DECDX.B 目的操作数减2语法DECDX.A dstDECDX dst or DECDX.W dsDECDX.B dst操作dst - 2 -> dst仿真SUBX.A#2,dstSUBX #2,dstSUBX.B #2,dst说明目的操作数减2 以前的内容丢失状态位N : 结果为负时置位为正时复位Z : dst包含2时置位其他情况时复位C : dst包含0或1时置位其他情况时复位V : dst产生算术溢出时置位其他情况时复位目的操作数的初始值为08001H或08000H时置方式位OscOff, CPUOff 和GIE不受影响例子目的地址操作数减二DECDX.A TONI ; Decrement TONI* INCX.[W] 目的操作数加1* INCX.B 目的操作数加1语法INCX.A dstINCX dst or INCX.W dstINCX.B dst操作dst + 1 →dst仿真ADDX.A#1,dstADDX #1,dstADDX.B #1,dst说明目的操作数加1 以前的内容丢失状态位N : 结果为负时置位为正时复位Z : dst包含0FFFFFH时置位其他情况时复位dst包含0FFFFH时置位其他情况时复位dst包含0FFFH时置位其他情况时复位C: dst包含0FFFFFH时置位其他情况时复位dst包含0FFFFH时置位其他情况时复位dst包含0FFFH时置位其他情况时复位V : dst包含07FFFH时置位其他情况时复位dst包含07FFFH时置位其他情况时复位dst包含07FH时置位其他情况时复位方式位OscOff ,CPUOff 和GIE不受影响例子目的地址操作数加一INCX.A TONI ; Increment TONI (20-bits)* INCDX.A目的操作数加2* INCDX.[W] 目的操作数加2* INCDX.B 目的操作数加2语法INCDX.A dstINCDX dst or INCDX.W dstINCDX.B dst操作dst + 1 →dst仿真ADDX.A#2,dstADDX #2,dstADDX.B #2,dst说明目的操作数加2以前的内容丢失状态位N: 结果为负时置位为正时复位Z : dst包含0FFFFEH时置位其他情况时复位dst包含0FFFEH时置位其他情况时复位dst包含0FEH时置位其他情况时复位C: dst包含0FFFFEH或0FFFFFH时置位其他情况时复位dst包含0FFFEH或0FFFFH时置位其他情况时复位dst包含0FEH或0FFH时置位其他情况时复位V: dst包含07FFFEH或0FFFFH时置位其他情况时复位dst包含07FFEH或0FFFH时置位其他情况时复位dst包含07EH或0FH时置位其他情况时复位方式位OscOff ,CPUOff 和GIE不受影响例子目的地址操作数加二INCDX.B LEO ; Increment LEO by two* INVX.A目的操作数求反* INVX.[W] 目的操作数求反* INVX.B 目的操作数求反语法INVX.A dstINVX dst or INVX.W dstINVX.B dst操作.NOT.dst →dst仿真XORX.A#0FFFFFh,dstXORX #0FFFFh,dstXORX.B #0FFh,dst说明目的操作数取反以前的内容丢失状态位N : 结果为负时置位为正时复位Z :dst 包含0FFFFFH时置位其他情况时复位dst 包含0FFFFH时置位其他情况时复位dst 包含0FFH时置位其他情况时复位C :结果不为零时置位其他情况时复位( = .NOT.Zero )V 初始目的操作数为负时置位其他情况时复位方式位OscOff CPUOff 和GIE不受影响例子R5 求反INVX.A R5 ; R5求反MOVX.A源操作数移至目的操作数MOVX.[W] 源操作数移至目的操作数MOVX.B 源操作数移至目的操作数语法MOVX.A src,dstMOVX src,dst or MOVX.W src,dstMOVX.B src,dst操作src →dst说明源操作数被移至目的操作数源操作数不受影响目的操作数以前的内容丢失状态位N: 不影响状态位Z: 不影响状态位C: 不影响状态位V: 不影响状态位方式位OscOff ,CPUOff 和GIE不受影响例子移动18000H 到EDEMOVX. A#018000h, &EDE ; Move 18000h to EDE例子地起码表EDE(字数据)的内容被复制到表TOM 地址表的长度为030H MOV #EDE, R10 ;准备指针Loop MOV @R10+, TOM-EDE-2(R10) ;将R10 中的指针用于两表DEC R9 ;计数器减1JNZ Loop ;计数器<>0 继续........ ;完成例子地起码表EDE(字数据)的内容被复制到表TOM 地址表的长度为020H MOV #EDE, R10 ;准备指针MOV #020H, R9 ;计数器Loop MOV @R10+, TOM-EDE-2(R10) ;将R10 中的指针用于两表DEC R9 ;计数器减1JNZ Loop ;计数器<>0 继续........ ;完成28种MOVX寻址方式中的10种,一个指令可以使用MOVX,这样可以节省二个字节编码周期。

T EXAS I NSTRUMENTSMSP430系列混合信号微控制器结构及模块用户指南目录1MSP430系列1.1特性与功能1.2系统关键性能1.3MSP430系列的各型号2结构概述2.1CPU2.2代码存储器2.3数据存储器(RAM)2.4运行控制2.5外围模块2.6振荡器、倍频器和时钟发生器3系统复位、中断和运行模式3.1系统复位和初始化3.2中断系统结构3.3中断处理3.3.1SFR中的中断控制位3.3.2外部中断3.4运行模式3.5低功耗模式3.5.1 低功耗模式0与模式1,LPM0和LPM1 3.5.2 低功耗模式2与模式3,LPM2和LPM3 3.5.3 低功耗模式4,LPM43.6 低功耗应用要点4 存储器组织4.1 存储器中的数据4.2 片内ROM组织4.2.1 ROM表的处理4.2.2 计算分支跳转和子程序调用4.3 RAM与外围模块组织4.3.1 RAM4.3.2 外围模块—地址定位4.3.3 外围模块--SFR5 16位CPU5.1 CPU寄存器5.1.1 程序计数器PC5.1.2 系统堆栈指针SP5.1.3 状态寄存器SR5.1.4 常数发生寄存器CG1与CG25.2 寻址模式5.2.1 寄存器模式5.2.2 变址模式5.2.3 符号模式5.2.4 绝对模式5.2.5 间接模式5.2.6 间接增量模式5.2.7 立即模式5.2.8 指令的时钟周期与长度5.3 指令组概述5.3.1 双操作数指令5.3.2 单操作数指令5.3.3 条件跳转5.3.4 模拟指令的短格式5.3.5 其它指令5.4 指令分布6 硬件乘法器6.1 硬件乘法器的操作6.2 硬件乘法器的寄存器6.3 硬件乘法器的SFR位6.4 硬件乘法器的软件限制6.4.1 硬件乘法器软件限制--寻址模式 6.4.2 硬件乘法器软件限制--中断程序7 振荡器与系统时钟发生器7.1 晶体振荡器7.2 处理机时钟发生器7.3 系统时钟运行模式7.4 系统时钟控制寄存器7.4.1 模块寄存器7.4.2 与系统时钟发生器相关的SFR位 7.5 DCO典型特性8 数字I/O配置8.1 通用端口P08.1.1 P0控制寄存器8.1.2 P0原理图8.1.3 P0中断控制功能8.2 通用端口P1、P28.2.1 P1、P2控制寄存器8.2.2 P1、P2原理图8.2.3 P1、P2中断控制功能8.3 通用端口P3、P48.3.1 P3、P4控制寄存器8.3.2 P3、P4原理图8.4 LCD端口8.5 LCD端口--定时器/端口比较器9 通用定时器/端口模块9.1 定时器/端口模块操作9.1.1 定时器/端口计数器TPCNT1,8位操作 9.1.2 定时器/端口计数器TPCNT2,8位操作 9.1.3 定时器/端口计数器,16位操作9.2 定时器/端口寄存器9.3 定时器/端口SFR位9.4 定时器/端口在A/D中的应用9.4.1 R/D转换原理9.4.2 分辨率高于8位的转换10 定时器10.1 Basic Timer110.1.1 BasicTimer1寄存器10.1.2 SFR位10.1.3 BasicTimer1操作10.1.4 BasicTimer1操作:LCD时钟信号f LCD 10.2 8位间隔(Interval)定时器/计数器 10.2.1 8位定时器/计数器的操作10.2.2 8位定时器/计数器的寄存器10.2.3 与8位定时器/计数器有关的SFR 10.2.4 8位定时器/计数器在UART中的应用 10.3 看门狗定时器10.3.1 看门狗定时器寄存器10.3.2 看门狗定时器中断控制功能10.3.3 看门狗定时器操作10.4 8位PWM定时器10.4.1 操作10.4.2 PWM寄存器11 Timer_A11.1 Timer_A的操作11.1.1 定时器操作11.1.2 捕获模式11.1.3 比较器模式11.1.4 输出单元11.2 Timer_A的寄存器11.2.1 Timer_A控制寄存器TACTL11.2.2 捕获/比较控制寄存器CCTL11.2.3 Timer_A中断向量寄存器11.3 Timer_A的应用11.3.1 Timer_A增计数模式应用11.3.2 Timer_A连续模式应用11.3.3 Timer_A增/减计数模式应用11.3.4 Timer_A软件捕获应用11.3.5 Timer_A处理异步串行通信协议 11.4 Timer_A的特殊情况11.4.1 CCR0用作周期寄存器11.4.2 定时器寄存器的启/停11.4.3 输出单元Unit012 USART外围接口,UART模式12.1 异步操作12.1.1 异步帧格式12.1.2 异步通信的波特率发生器12.1.3 异步通信格式12.1.4 线路空闲多处理机模式12.1.5 地址位格式12.2 中断与控制功能12.2.1 USART接收允许12.2.2 USART发送允许12.2.3 USART接收中断操作12.2.4 USART发送中断操作12.3 控制与状态寄存器12.3.1 USART控制寄存器UCTL12.3.2 发送控制寄存器UTCTL12.3.3 接收控制寄存器URCTL12.3.4 波特率选择和调制控制寄存器12.3.5 USART接收数据缓存URXBUF12.3.6 USART发送数据缓存UTXBUF12.4 UART模式,低功耗模式应用特性 12.4.1 由UART帧启动接收操作12.4.2 UART模式波特率与时钟频率12.4.3 节约MSP430资源的多处理机模式 12.5 波特率的计算13 USART外围接口,SPI模式13.1 USART的同步操作13.1.1 SPI模式中的主模式,MM=1、SYNC=1 13.1.2 SPI模式中的从模式,MM=0、SYNC=1 13.2 中断与控制功能13.2.1 USART接收允许13.2.2 USART发送允许13.2.3 USART接收中断操作13.2.4 USART发送中断操作13.3 控制与状态寄存器13.3.1 USART控制寄存器13.3.2 发送控制寄存器UTCTL13.3.3 接收控制寄存器URCTL13.3.4 波特率选择和调制控制寄存器 13.3.5 USART接收数据缓存URXBUF 13.3.6 USART发送数据缓存UTXBUF14 液晶显示驱动14.1 LCD驱动基本原理14.2 LCD控制器/驱动器14.2.1 LCD控制器/驱动器功能14.2.2 LCD控制及模式寄存器14.2.3 LCD显示存储器14.2.4 LCD操作软件例程14.3 LCD端口功能14.4 LCD与端口模式混合应用实例15 A/D转换器15.1 概述15.2 A/D转换操作15.2.1 A/D转换15.2.2 A/D中断15.2.3 A/D量程15.2.4 A/D电流源15.2.5 A/D输入端与多路切换15.2.6 A/D接地与降噪15.2.7 A/D输入与输出引脚15.3 A/D控制寄存器16 其它模块16.1 晶体振荡器16.2 上电电路16.3 晶振缓冲输出附录A 外围模块分布附录B 指令组说明附录C EPROM编程本书用途及表述约定MSP430用户指南以方便工程师及程序员使用的方式提供软件和硬件资料,以帮助开发应用MSP430系列的产品。

MSP430G2553 学习笔记常用赋值运算符:清除:&=~ , 置位:|= , 测试:&= , 取反:A=看门狗模块:WDT (看门狗)IS1,IS0选择看门狗定时器的定时输出, T 是WDTCNT 的输入时钟源周期0 T x 2(15) 1 T x 2(13) 2 T x 2(9) 3T x 2(6)SSEL选择WDTCNT 的时钟源 0 SMCLK 1ACLKIS0、IS1、SSEL 可确定 WDT 定时时间, WDT 只能定时8种和时钟源相关的时间CNTCL当该位为1时,清除WDTCNT TMSEL工作模式选择看门狗模式1定时器模式NMI选择RST/NMI 引脚功能,在 PUC 后被复位0 RST/NMI引脚为复位端NMIES 选择中断的边沿触发方式0 上升沿触发NMI中断1 下降沿触发NMI中断HOLD 停止看门狗定时器工作,降低功耗0 WDT功能激活1 时钟禁止输入,计数停止WDT (看门狗)配置语句WDTCTL=WDTPW+WDTHOLD ;// 将 WDTPW+WDTHOLD 赋值给 WDTCTL,关闭看门狗定时器控制寄存器( Stop watchdogtimer)IE1 |= WDTIE ;// 使能 WDT 中断WDTCTL = WDT_ADL Y_1000 ;//WDT 1 s / 4 间隔计时器WDTCTL = WDTPW + WDTHOLD + WDTNMI + WDTNMIES ;//WDTCTL 由高8位口令和低8位控制命令组成,要写入操作 WDT的控制命令,出于安全原因必须先正确写入高字节看门狗口令。

口令为5AH,如果口令写错将导致系统复位。

读 WDTCTL时不需要口令。

这个控制寄存器还可以用于设置NMI引脚功能。

WDT 看门狗定时器(Watch Dog Timer),这是16位增计数器,由MSP430所选定的时钟电路产生的固定周期时钟信号对计数器进行加法计数。

MSP430F5系列16位超低功耗单片机模块原理第4章PMM 电源管理模块与供电监控版本: 1.0日期: 2008.7.原文: TI slau208.pdf (5xxfamily User's Guide)翻译: 田萍果西安工业大学编辑: DC 微控技术论坛版主注:以下文章是翻译TI slau208.pdf 文件中的部分内容。

由于我们翻译水平有限,有整理过程中难免有所不足或错误;所以以下内容只供参考.一切以原文为准。

文章更新详情请密切留意微控技术论坛。

第11章PMM 电源管理模块与供电监控4.1 电源管理简介电源管理特征:.提供宽的电源电压范围:1.8V-3.6V.产生的核心电压(V CORE):1.4V,1.6V,1.8V和1.9V(典型值).欠压复位(BOR).配有DVCC 和VCORE的电源电压管理.DVCC 和VCORE的电源电压监测有8个可编程级别.软件恢复掉电时系统状态.掉电条件下软件可选择上电复位.上电失败时有I/O保护.软件可选监视状态输出(可选)MSP430主要数字逻辑需要一个低于DVCC允许范围的电压。

因此,电源管理模块集成了一个低压降的电压调整器(LDO),LDO可以产生一个二次核心电压VCORE。

这个核心电压可通过四步编程从而使功耗最低化。

核的最小允许电压依赖于选择的MCLK大小,如4-1图所示。

我们可以管理和监控DV CC and V CORE。

当电压降到特殊阈值以下时管理和监控就工作了。

通常来讲,管理会致使上电复位事件发生(POR),而监控产生中断标志,这时软件就可以处理了。

比如说,DV CC(LDO 的高电平)分别被高电平管理(SVS H)和高电平监测器(SVM H)所管理和监测;V CORE(LDO的低电平)分别被低电平管理(SVS L)和低电平监测器(SVM L)所管理和监测. 电源管理单元框图如图4-2所示。

I/O口和所有模拟单元包括晶振在内都由DV CC供电。

MSP430F552X中文手册及例程一、先写一篇开个头:这样快速闯入MSP430学习过程进入各个电子产品公司的网站,招聘里面嵌入式占据了大半工程师职位。

广义的嵌入式无非几种:传统的什么51单片机、 MSP430称做嵌入式微控制器;ARM是嵌入式微处理器;当然还有DSP;FPGA。

我们现在就不说别的,就说MSP430单片机,多数想学MSP430的童鞋,对89C51内核系列的单片机是很熟悉的,为了加深对MSP430 系列单片机的认识吗,迅速闯入MSP430学习过程,就必须彻底了解MSP430单片机,我们不妨将51单片机和MSP430两者进行一下比较。

第一点, 51内核单片机是8 位单片机。

其指令是采用的被称为“ CISC ”的复杂指令集,共具有111 条指令。

而MSP430 单片机是16 位的单片机,采用了精简指令集( RISC )结构,只有简洁的27 条指令,大量的指令则是模拟指令,众多的寄存器以及片内数据存储器都可参加多种运算。

这些内核指令均为单周期指令,功能强,运行的速度快。

第二点,MCU主要分为两种工作模式:待机与执行。

51内核单片机正常情况下消耗的电流为mA级 ,在掉电状态下,其耗电电流仍约为3mA左右 ;即使在掉电方式下,电源电压可以下降到2V ,但是为了保存内部RAM 中的数据,还需要提供约50uA的电流。

而430单片机功耗是在uA级的,工作电流极小,并且超低功耗,关断状态下的电流仅为0.1μA,待机电流为0.8μA,常规模式下的(250μA/1MIPS@3V),端口漏电流不足50 nA,并可零功耗掉电复位(BOR)。

另外,该芯片属低电器件,仅需1.8~3.6V电压供电,因而可有效降低系统功耗。

MSP430将低功耗模式扩展为7种,分别对应不同应用场合及任务的低功耗方式。

以睡眠模式为例,包括深度睡眠模式RTC:只有时钟在跑而其他都不动,目前,TI宣布其MSP430在RTC模式下最低功耗仅为360nA。

http://www.Microcontrol.cn 微控网 微控网为你准备的MSP430F单片机入门必修课 http://www.Microcontrol.cn 微控网 MSP430F1系列单片机常用模块应用原理

微控网 DC总版主策划 原创于:2006-3-7 最后更新:2010-8-14 V8.3 http://www.Microcontrol.cn 微控网 微控网为你准备的MSP430F单片机入门必修课 为了更好地引导MSP430单片机爱好者的入门,微控设计网为大家整理了一个份MS430单片机入门资料,希望能够帮助到更多的国内单片机爱好者朋友。 如果你在学习或应用MSP430单片机过程中想与同行分享成果或交流技术问题,欢迎进入我们的微控技术论坛。 微控网供应MSP430单片机系列开发工具,欢迎订购。

模块列表 1- 复位模块 2- 时钟模块 3- IO端口模块 4- WDT看门狗模块 5- Timer A定时器模块 6- 比较器A模块 7- ADC12数模转换模块 8- USART串行异步通讯模块 9- CPU模块及全局资料 10-MSP430其它应用介绍 http://www.Microcontrol.cn 微控网

微控网为你准备的MSP430F单片机入门必修课 1-复位模块

MSP430单片机系统复位电路 从上MSP430系统复位电路功能模块图中可以看到了两个复位信号,一个是上电复位信号POR(Power On Reset)和上电清除信号PUC(Power Up Clear)。

POR信号是器件的复位信号,此信号只有在以下的事件发生时才会产生: □器件上电时。

□RST/NMI引脚配置为复位模式,当RST/NMI引脚生产低电平时。 当POR信号产生时,必然会产生PUC信号;而PUC信号的产生时不会产生POR信号。会引起产生PUC信号的事件: □POR信号发生时。

□ 启动看门狗时,看门狗定时器计满时。 □ 向看门狗写入错误的安全参数值时。 □向片内FLASH写入错误的安全参数值时。 MSP430单片机系统复位后器件的初始 当POR信号或PUC信号发生时引起器件复位后,器件的初始化状态为: □RST/NMI引脚配置为复位模式。

□ I/O引脚为输入模式。 http://www.Microcontrol.cn 微控网 微控网为你准备的MSP430F单片机入门必修课 □ 装态寄存器复位。 □ 程序计数器(PC)装入复位向量地址 0xFFFE,CPU从此地址开发始执行。 □其它模块的寄存器初始化,详情请查器件手册。 POR和PUC两者的关系: POR信号的产生会导致“系统复位”并“产生PUC信号”。而PUC信号不会引起POR信号的产生。 无论是POR信号还是PUC信号触发的复位,都会使MSP430从地址0xFFFE处读取复位中断向量,程序从中断向量所指的地址处开始执行。触发PUC信号的条件中,除了POR产生触发PUC信号外,其他的豆科一通过读取相应的中断向量来判断是何种原因引起的PUC信号,以便作出相应的处理。 系统复位(指POR)后的状态为: (1) RST/NMI管脚功能被设置为复位功能; (2)所有I/O管脚被设置为输入; (3)外围模块被初始化,其寄存器值为相关手册上的默认值; (4)状态寄存器SR复位; (5)看门狗激活,进入工作模式; (6)程序计数器PC载入0xFFFE处的地址,微处理器从此地址开始执行程序。

典型的复位电路有一下3种: (1) 在RST/NMI管脚上接100K欧的上拉电阻。 (2)在[1]的基础上再接0.1uf的电容,电容的一端接地,可以使复位更加可靠。 (3)在[2]的基础上,再在电阻上并接一个型号为IN4008的二极管,可以可靠的实现系统断电后立即上电。

2-时钟模块 http://www.Microcontrol.cn 微控网

微控网为你准备的MSP430F单片机入门必修课 MSP430F1XX系列时钟模块图 时基模块结构如上图: MSP430系列单片机基础时钟主要是由低频晶体振荡器,高频晶体振荡器,数字控制振荡器(DCO),锁频环(FLL)及FLL+等模块构成。由于430系列单片机中的型号不同,而时钟模块也将有所不同。虽然不同型号的单片机的时基模块有所不同,但这些模块产生出来的结果是相同的.在MSP430F13、14中是有TX2振荡器的,而MSP430F11X,F11X1中是用LFXT1CLK来代替XT2CLK时钟信号的.在时钟模块中有3个(对于F13,F14)时钟信号源(或2个时钟信号源,对于F11X、F11X1):

1-LFXT1CLK: 低频/高频时钟源.由外接晶体振荡器,而无需外接两个振荡电容器.较常使用的晶体振荡器是32768HZ。 2-XT2CLK: 高频时钟源.由外接晶体振荡器。需要外接两个振荡电容器,较常用的晶体振荡器是8MHZ。 3-DCOCLK: 数字可控制的RC振荡器。 http://www.Microcontrol.cn 微控网 微控网为你准备的MSP430F单片机入门必修课 MSP430单片机时钟模块提供3个时钟信号输出,以供给片内各部电路使用。 1-ACLK: 辅助时钟信号.由图所示,ACLK是从FLXT1CLK信号由1/2/4/8分频器分频后所得到的.由BCSCTL1寄存器设置DIVA相应为来决定分频因子.ACLK可用于提供CPU外围功能模块作时钟信号使用.

2-MCLK: 主时钟信号.由图所示,MCLK是由3个时钟源所提供的。他们分别是LFXT1CLK,XT2CLK(F13、F14,如果是F11,F11X1则由LFXT1CLK代替),DCO时钟源信号提供.MCLK主要用于MCU和相关系统模块作时钟使用。同样可设置相关寄存器来决定分频因子及相关的设置。

3-SMCLK: 子系统时钟,SMCLK是由2个时钟源信号所提供.他们分别是XT2CLK(F13、F14)和DCO,如果是F11、F11X1则由LFXT1CLK代替TX2CLK。同样可设置相关寄存器来决定分频因子及相关的设置。

MSP430X1X1系列产品中,其中XT1时钟源引脚接法有如3种应用。F13、14的XT1相同。需要注意的是,LFXT1只有工作在高频模式下才需要外接电容。 对以引脚较少的MSPX1XX系列产品中有着不同时基模块,具体如下: MSP430X11X1:LFXT1CLK , DCO

MSP430F12X: LFXT1CLK , DCO MSP430F13X/14X/15X/16X:LFXT1CLK , DCO , XT2CLK MSP430F4XX: LFXT1CLK , DCO , XT2CLK , FLL+ 时钟发生器的原理说明: 问题的提出:1、高频、以便能对系统硬件请求和事件作出快速响应 2、低频率,以便将电流消耗降制至最少 3、稳定的频率,以满足定时器的应用。 4、低Q值振荡器,以保证开始或停止操作没有延时 MSP430采用了一个折衷的办法:就是用一个低频晶镇振,将其倍频在高频的工作频率上。一般采用这种技术的实用方法有两种,一个是说、锁相环、 一个是锁频环,而锁相环采用模拟的控制容易引起“失锁”和易引起电容量的改变。而TI采用的是锁频环技术,它采用数字控制器DCO和频率积分来产 生高频的运行时钟频率。

低功耗设置的技巧问题: 1、LPM4:在振荡器关闭模式期间,处理机的所有部件工作停止,此时电流消 耗最小。此时只有在系统上电电路检测到低点电平或任一请求异步响应中断的外部中断事件时才会从新工作。因此在设计上应含有可能需要用到的外部中断才采用这种模式。否则发生不可预料的结果。 2、LPM3:在DC发生器关闭期间,只有晶振是活动的。但此时设置的基本时序条件的DC发生器的DC电流被关闭。由于此电路的高阻设计,使功耗被抑制。注:当从DC关闭到启动DC0要花一端时间 (ns-us) 3、LPM2:在此期间,晶镇振和DC发生器是工作的,所以可实现快速启动。 4、LPM1:在此振荡器已经工作,所以不存在启动时间延时问题。

结合上述特点,在写程序时要综合考虑低功好耗特性,对外部事件的安排也很 重要。你必须在功能实现上综合考虑才能达到你预期的效果。使用C语言可用如下的语http://www.Microcontrol.cn 微控网 微控网为你准备的MSP430F单片机入门必修课 句:_BIS_SR(LMP3_bits)和_BIC_SR(LPM3 bits) LPM3和LPM3_EXIT 它们的定义是一样的。这里说明在C语言环境中有些定义的函数是不可见的。但你可以从 in430.h文件看到它们的定义。

DCOCTL DCO控制寄存器 7 6 5 4 3 2 1 0 DCO.2 DCO.1 DCO.0 MOD.4 MOD.3 MOD.2 MOD.1 MOD.0

DCO.0-DCO.4 定义8种频率之一,可以分段调节DCOCLK频率,相邻两种频率相差10%。而频率由注入直流发生器的电流定义。

MOD.0-MOD.4 定义在32个DCO周期中插入的Fdco+1周期个数,而在下的DCO周期中为Fdco周期,控制改换DCO和DCO+1选择的两种频率。如果DCO常数为7,表示已经选择最高频率,此时不能利用MOD.0-MOD.4进行频率调整。

BCSCTL1 基本时钟系统控制寄存器1 7 6 5 4 3 2 1 0 XT2OFF TXS DIVA.1 DIVA.0 XT5V Rsel.2 Resl.1 Resl.0

XT2OFF 控制XT2振荡器的开启与关闭。 TX2OFF=0,XT2振荡器开启。 TX2OFF=1,TX2振荡器关闭(默认为TX2关闭)

XTS 控制LFXT1 工作模式,选择需结合实际晶体振荡器连接情况。 XTS=0,LFXT1 工作在低频模式(默认)。 XTS=1,LFXT1 工作在高频模式(必须连接有高频相应的高频时钟源)。

DIVA.0 DIVA.1 控制ACLK分频。 0 不分频(默认) 1 2分频 2 4分频 3 8分频

XT5V 此位设置为0。 Resl1.0,Resl1.1,Resl1.2 三位控制某个内部电阻以决定标称频率。 Resl=0,选择最低的标称频率。 …….. Resl=7,选择最高的标称频率。

BCSCTL2 基本时钟系统控制寄存器2 7 6 5 4 3 2 1 0 SELM.1 SELM.0 DIVM.1 DIVM.0 SELS DIVS.1 DIVS.0 DCOR

SELM.1 SELM.0 选择MCLK时钟源