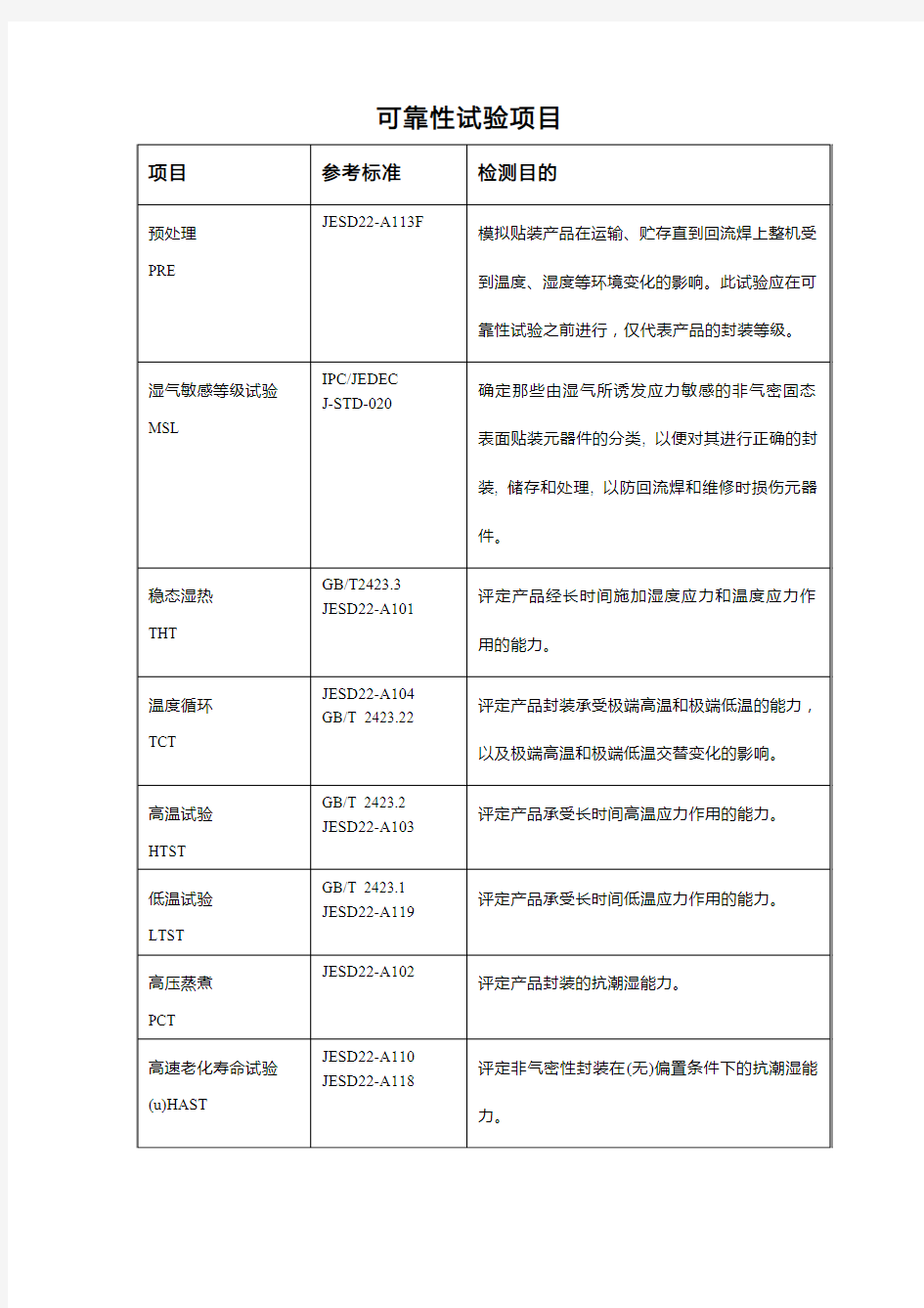

可靠性试验项目 项目 参考标准 检测目的

预处理PRE JESD22-A113F

模拟贴装产品在运输、贮存直到回流焊上整机受

到温度、湿度等环境变化的影响。此试验应在可

靠性试验之前进行,仅代表产品的封装等级。

湿气敏感等级试验MSL IPC/JEDEC

J-STD-020

确定那些由湿气所诱发应力敏感的非气密固态

表面贴装元器件的分类, 以便对其进行正确的封

装, 储存和处理, 以防回流焊和维修时损伤元器

件。

稳态湿热THT GB/T2423.3

JESD22-A101

评定产品经长时间施加湿度应力和温度应力作

用的能力。

温度循环TCT JESD22-A104

GB/T 2423.22

评定产品封装承受极端高温和极端低温的能力,

以及极端高温和极端低温交替变化的影响。

高温试验HTST GB/T 2423.2

JESD22-A103

评定产品承受长时间高温应力作用的能力。

低温试验LTST GB/T 2423.1

JESD22-A119

评定产品承受长时间低温应力作用的能力。

高压蒸煮PCT JESD22-A102

评定产品封装的抗潮湿能力。

高速老化寿命试验(u)HAST JESD22-A110

JESD22-A118

评定非气密性封装在(无)偏置条件下的抗潮湿能

力。

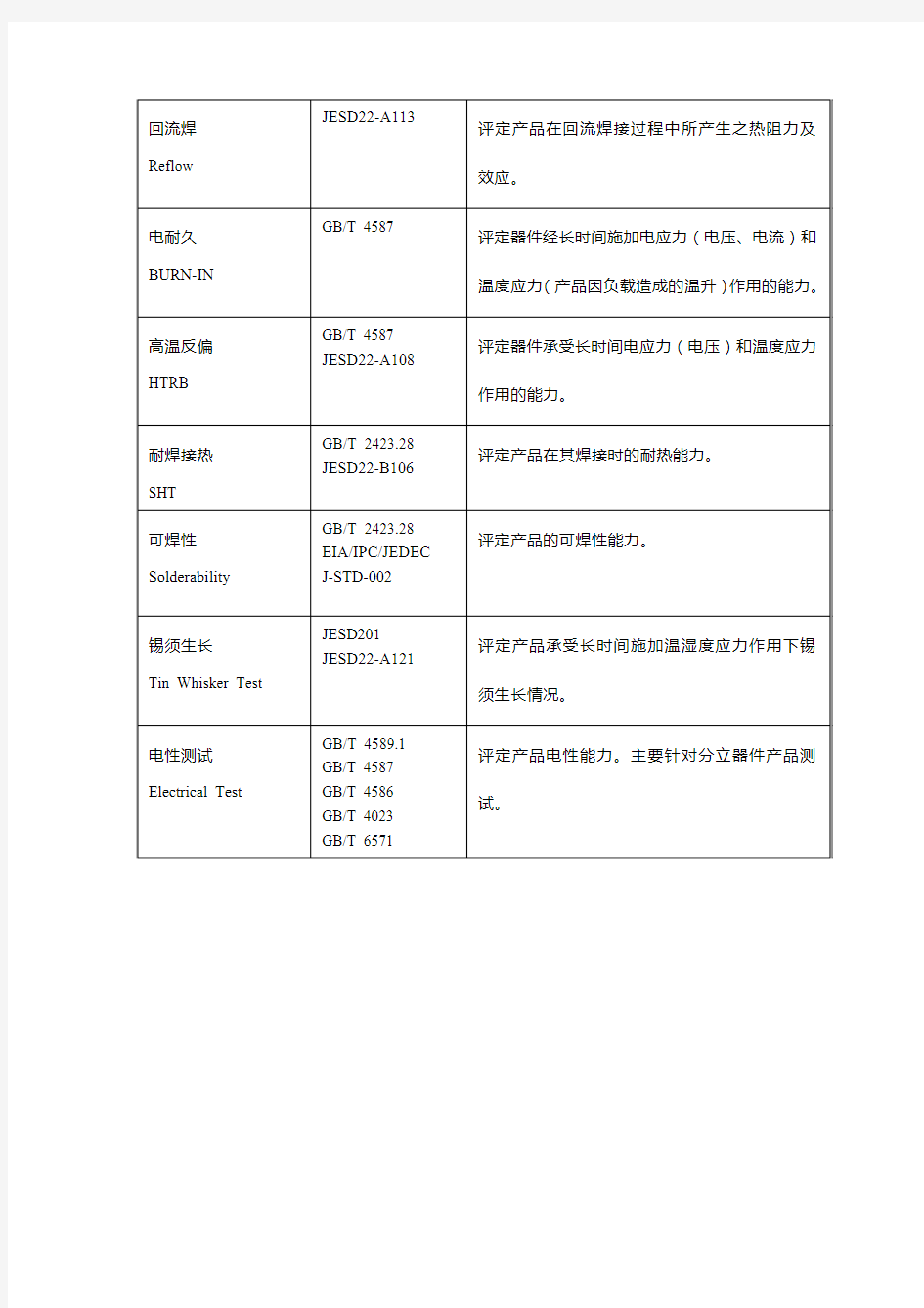

回流焊Reflow JESD22-A113

评定产品在回流焊接过程中所产生之热阻力及

效应。

电耐久BURN-IN GB/T 4587

评定器件经长时间施加电应力(电压、电流)和

温度应力(产品因负载造成的温升)作用的能力。

高温反偏HTRB GB/T 4587

JESD22-A108

评定器件承受长时间电应力(电压)和温度应力

作用的能力。

耐焊接热SHT GB/T 2423.28

JESD22-B106

评定产品在其焊接时的耐热能力。

可焊性Solderability GB/T 2423.28

EIA/IPC/JEDEC

J-STD-002

评定产品的可焊性能力。

锡须生长

Tin Whisker Test JESD201

JESD22-A121

评定产品承受长时间施加温湿度应力作用下锡

须生长情况。

电性测试Electrical Test GB/T 4589.1

GB/T 4587

GB/T 4586

GB/T 4023

GB/T 6571

评定产品电性能力。主要针对分立器件产品测

试。

可靠性试验项目 项目 参考标准 检测目的 预处理PRE JESD22-A113F 模拟贴装产品在运输、贮存直到回流焊上整机受 到温度、湿度等环境变化的影响。此试验应在可 靠性试验之前进行,仅代表产品的封装等级。 湿气敏感等级试验MSL IPC/JEDEC J-STD-020 确定那些由湿气所诱发应力敏感的非气密固态 表面贴装元器件的分类, 以便对其进行正确的封 装, 储存和处理, 以防回流焊和维修时损伤元器 件。 稳态湿热THT GB/T2423.3 JESD22-A101 评定产品经长时间施加湿度应力和温度应力作 用的能力。 温度循环TCT JESD22-A104 GB/T 2423.22 评定产品封装承受极端高温和极端低温的能力, 以及极端高温和极端低温交替变化的影响。 高温试验HTST GB/T 2423.2 JESD22-A103 评定产品承受长时间高温应力作用的能力。 低温试验LTST GB/T 2423.1 JESD22-A119 评定产品承受长时间低温应力作用的能力。 高压蒸煮PCT JESD22-A102 评定产品封装的抗潮湿能力。 高速老化寿命试验(u)HAST JESD22-A110 JESD22-A118 评定非气密性封装在(无)偏置条件下的抗潮湿能 力。

回流焊Reflow JESD22-A113 评定产品在回流焊接过程中所产生之热阻力及 效应。 电耐久BURN-IN GB/T 4587 评定器件经长时间施加电应力(电压、电流)和 温度应力(产品因负载造成的温升)作用的能力。 高温反偏HTRB GB/T 4587 JESD22-A108 评定器件承受长时间电应力(电压)和温度应力 作用的能力。 耐焊接热SHT GB/T 2423.28 JESD22-B106 评定产品在其焊接时的耐热能力。 可焊性Solderability GB/T 2423.28 EIA/IPC/JEDEC J-STD-002 评定产品的可焊性能力。 锡须生长 Tin Whisker Test JESD201 JESD22-A121 评定产品承受长时间施加温湿度应力作用下锡 须生长情况。 电性测试Electrical Test GB/T 4589.1 GB/T 4587 GB/T 4586 GB/T 4023 GB/T 6571 评定产品电性能力。主要针对分立器件产品测 试。

?从大的方面来讲,晶圆生产包括晶棒制造和晶片制造两大步骤,它又可细分为以下几道主要工序(其中晶棒制造只包括下面的第一道工序,其余的全部属晶片制造,所以有时又统称它们为晶柱切片后处理工序): 晶棒成长--> 晶棒裁切与检测--> 外径研磨--> 切片--> 圆边--> 表层研磨--> 蚀刻--> 去疵--> 抛光--> 清洗--> 检验--> 包装 1 晶棒成长工序:它又可细分为: 1)融化(Melt Down) 将块状的高纯度复晶硅置于石英坩锅内,加热到其熔点1420°C以上,使其完全融化。 2)颈部成长(Neck Growth) 待硅融浆的温度稳定之后,将〈1.0.0〉方向的晶种慢慢插入其中,接着将晶种慢慢往上提升,使其直径缩小到一定尺寸(一般约6mm左右),维持此直径并拉长 100-200mm,以消除晶种内的晶粒排列取向差异。 3)晶冠成长(Crown Growth) 颈部成长完成后,慢慢降低提升速度和温度,使颈部直径逐渐加大到所需尺寸(如 5、6、8、12吋等)。 4)晶体成长(Body Growth) 不断调整提升速度和融炼温度,维持固定的晶棒直径,只到晶棒长度达到预定值。 5)尾部成长(Tail Growth) 1

当晶棒长度达到预定值后再逐渐加快提升速度并提高融炼温度,使晶棒直径逐渐变小,以避免因热应力造成排差和滑移等现象产生,最终使晶棒与液面完全分离。到此即得到一根完整的晶棒。 2 晶棒裁切与检测(Cutting & Inspection) 将长成的晶棒去掉直径偏小的头、尾部分,并对尺寸进行检测,以决定下步加工的工艺参数。 3 外径研磨(Su rf ace Grinding & Shaping) 由于在晶棒成长过程中,其外径尺寸和圆度均有一定偏差,其外园柱面也凹凸不平,所以必须对外径进行修整、研磨,使其尺寸、形状误差均小于允许偏差。 4 切片(Wire Saw Sl ic ing) 由于硅的硬度非常大,所以在本工序里,采用环状、其内径边缘镶嵌有钻石颗粒的薄片锯片将晶棒切割成一片片薄片。 5 圆边(Edge Profiling) 由于刚切下来的晶片外边缘很锋利,硅单晶又是脆性材料,为避免边角崩裂影响晶片强度、破坏晶片表面光洁和对后工序带来污染颗粒,必须用专用的电脑控制设备自动修整晶片边缘形状和外径尺寸。 ? 6 研磨(Lapping) 研磨的目的在于去掉切割时在晶片表面产生的锯痕和破损,使晶片表面达到所要求的光洁度。 7 蚀刻(Etching) 1

1-3-半导体封装件的可靠性评价方法

半导体封装件的可靠性评价方法 Lunasus 科技公司,佐土原宽 Lunasus 科技公司细川丰 本章将依据半导体封装件可靠性评价的基本考虑方法,以故障机理为基础的实验条件介绍,并根据韦布图来解说可靠性试验下的(产品)寿命推导方法。 封装件开发及材料变化过程中的可靠性评价方法 为实现半导体封装件功能和电气特性的提高,在推动多引脚化的同时,也要发展高密度封装化下的小型、薄型化。最近,搭载多个芯片的SiP(System in Package,系统级封装)和芯片尺寸(与封装尺寸)非常相近的CSP(Chip Size Package,芯片级封装)已开始量产,封装件的构造多种多样。另外,为达成封装件低成本化和环保的要求,采用规格更高的封装件材料的开发正在活跃起来。但封装件构造的复杂化和新型材料的使用不能对制造品质和可靠性造成影响。这里将对新型封装件的开发和材料改变下的可靠性评价方法进行解说。 最近的半导体封装件多数属于树脂灌封型,对半导体单体的可靠性评价包括,高温保存(或动作)实验,耐湿性实验以及温度循环实验。另外,对于有可能要进行表面装配的高密度封装器型,需考虑焊接装配过程中的热应力情况,因此焊锡耐热性实验也是不可缺少的。这些可靠性试验,是对半导体封装件在实际使用过程中所预想发生的各种故障进行短时间评价的加速性实验方法。接下来需要先确定半导

体所发生的各种故障的主要加速原因是什么后才能进行实验。例如,对于树脂封装件来讲,湿度(水分)是造成硅芯片上金属线路受到腐蚀(图1)的主要原因之一,而温度可以加快水分浸入封装件内的速度,所以高温、高湿下的实验才有效果。与此同时,在电压也是故障主因的场合,有必要进行高温、高湿下的通电实验。 如上所述,对于封装件相关的各种故障,通过对机理的解析,找出加速实验的主要因子,设定合适的可靠性实验条件,这些就是可靠性评价的基础。 针对封装件构造的可靠性试验 正如开头所述,为实现封装件的高功能、高密度化,封装件的外观形状的主流是QFP(Quad Flat Package,四面扁平封装)和BGA

半导体制造基本概念 晶圆(Wafer) 晶圆(Wafer)的生产由砂即(二氧化硅)开始,经由电弧炉的提炼还原成冶炼级的硅,再经由盐酸氯化,产生三氯化硅,经蒸馏纯化后,透过慢速分解过程,制成棒状或粒状的「多晶硅」。一般晶圆制造厂,将多晶硅融解后,再利用硅晶种慢慢拉出单晶硅晶棒。一支85公分长,重76.6公斤的8?? 硅晶棒,约需2天半时间长成。经研磨、??光、切片后,即成半导体之原料晶圆片。 光学显影 光学显影是在光阻上经过曝光和显影的程序,把光罩上的图形转换到光阻 下面的薄膜层或硅晶上。光学显影主要包含了光阻涂布、烘烤、光罩对准、曝光和显影等程序。小尺寸之显像分辨率,更在IC 制程的进步上,扮演着最关键的角色。由于光学上的需要,此段制程之照明采用偏黄色的可见光。因此俗称此区为黄光区。 干式蚀刻技术 在半导体的制程中,蚀刻被用来将某种材质自晶圆表面上移除。干式蚀刻(又称为电浆蚀刻)是目前最常用的蚀刻方式,其以气体作为主要的蚀刻媒介,并藉由电浆能量来驱动反应。 电浆对蚀刻制程有物理性与化学性两方面的影响。首先,电浆会将蚀刻气体分子分解,产生能够快速蚀去材料的高活性分子。此外,电浆也会把这些化学成份离子化,使其带有电荷。 晶圆系置于带负电的阴极之上,因此当带正电荷的离子被阴极吸引并加速向阴极方向前进时,会以垂直角度撞击到晶圆表面。芯片制造商即是运用此特性来获得绝佳的垂直蚀刻,而后者也是干式蚀刻的重要角色。 基本上,随着所欲去除的材质与所使用的蚀刻化学物质之不同,蚀刻由下列两种模式单独或混会进行:

1. 电浆内部所产生的活性反应离子与自由基在撞击晶圆表面后,将与某特定成份之表面材质起化学反应而使之气化。如此即可将表面材质移出晶圆表面,并透过抽气动作将其排出。 2. 电浆离子可因加速而具有足够的动能来扯断薄膜的化学键,进而将晶圆表面材质分子一个个的打击或溅击(sputtering)出来。 化学气相沉积技术 化学气相沉积是制造微电子组件时,被用来沉积出某种薄膜(film)的技术,所沉积出的薄膜可能是介电材料(绝缘体)(dielectrics)、导体、或半导体。在进行化学气相沉积制程时,包含有被沉积材料之原子的气体,会被导入受到严密控制的制程反应室内。当这些原子在受热的昌圆表面上起化学反应时,会在晶圆表面产生一层固态薄膜。而此一化学反应通常必须使用单一或多种能量源(例如热能或无线电频率功率)。 CVD制程产生的薄膜厚度从低于0.5微米到数微米都有,不过最重要的是其厚度都必须足够均匀。较为常见的CVD薄膜包括有: ■二气化硅(通常直接称为氧化层) ■氮化硅 ■多晶硅 ■耐火金属与这类金属之其硅化物 可作为半导体组件绝缘体的二氧化硅薄膜与电浆氮化物介电层(plasmas nitride dielectrics)是目前CVD技术最广泛的应用。这类薄膜材料可以在芯片内部构成三种主要的介质薄膜:内层介电层(ILD)、内金属介电层(IMD)、以及保护层。此外、金层化学气相沉积(包括钨、铝、氮化钛、以及其它金属等)也是一种热门的CVD应用。 物理气相沉积技术 如其名称所示,物理气相沉积(Physical Vapor Deposition)主要是一种物理制程而非化学制程。此技术一般使用氩等钝气,藉由在高真空中将氩离子加速以撞击溅镀靶材后,可将靶材原子一个个溅击出来,并使被溅击出来的材质(通常为铝、钛或其合金)如雪片般沉积在晶圆表面。制程反应室内部的高温与高真空环境,可使这些金属原子结成晶粒,再透过微影图案化(patterned)与蚀刻,来得到半导体组件所要的导电电路。 解离金属电浆(IMP)物理气相沉积技术

晶圆级封装产业(WLP) 晶圆级封装产业(WLP),晶圆级封装产业(WLP)是什么意思 一、晶圆级封装(Wafer Level Packaging)简介晶圆级封装(WLP,Wafer Level Package) 的一般定义为直接在晶圆上进行大多数或是全部的封装测试程序,之后再进行切割(singulation)制成单颗组件。而重新分配(redistribution)与凸块(bumping)技术为其I/O绕线的一般选择。WLP 一、晶圆级封装(Wafer Level Packaging)简介 晶圆级封装(WLP,Wafer Level Package) 的一般定义为直接在晶圆上进行大多数或是全部的封装测试程序,之后再进行切割(singulation)制成单颗组件。而重新分配(redistribution)与凸块(bumping)技术为其I/O绕线的一般选择。WLP封装具有较小封装尺寸(CSP)与较佳电性表现的优势,目前多用于低脚数消费性IC的封装应用(轻薄短小)。 晶圆级封装(WLP)简介 常见的WLP封装绕线方式如下:1. Redistribution (Thin film), 2. Encapsulated Glass substrate, 3. Gold stud/Copper post, 4. Flex Tape等。此外,传统的WLP封装多采用Fan-in 型态,但是伴随IC信号输出pin 数目增加,对ball pitch的要求趋于严格,加上部分组件对于封装后尺寸以及信号输出脚位位置的调整需求,因此变化衍生出Fan-out 与Fan-in + Fan-out 等各式新型WLP封装型态,其制程概念甚至跳脱传统WLP 封装,目前德商英飞凌与台商育霈均已经发展相关技术。 二、WLP的主要应用领域 整体而言,WLP的主要应用范围为Analog IC(累比IC)、PA/RF(手机放大器与前端模块)与CIS(CMOS Ima ge Sensor)等各式半导体产品,其需求主要来自于可携式产品(iPod, iPhone)对轻薄短小的特性需求,而部分NOR Flash/SRAM也采用WLP封装。此外,基于电气性能考虑,DDR III考虑采用WLP或FC封装,惟目前JEDEC仍未制定最终规格(注:至目前为止,Hynix, Samsung与Elpida已发表DDR III产品仍采F BGA封装),至于SiP应用则属于长期发展目标。此外,采用塑料封装型态(如PBGA)因其molding compo und 会对MEMS组件的可动部份与光学传感器(optical sensors)造成损害,因此MEMS组件也多采用WLP

电子封装技术发展现状及趋势 摘要 电子封装技术是系统封装技术的重要内容,是系统封装技术的重要技术基础。它要求在最小影响电子芯片电气性能的同时对这些芯片提供保护、供电、冷却、并提供外部世界的电气与机械联系等。本文将从发展现状和未来发展趋势两个方面对当前电子封装技术加以阐述,使大家对封装技术的重要性及其意义有大致的了解。 引言 集成电路芯片一旦设计出来就包含了设计者所设计的一切功能,而不合适的封装会使其性能下降,除此之外,经过良好封装的集成电路芯片有许多好处,比如可对集成电路芯片加以保护、容易进行性能测试、容易传输、容易检修等。因此对各类集成电路芯片来说封装是必不可少的。现今集成电路晶圆的特征线宽进入微纳电子时代,芯片特征尺寸不断缩小,必然会促使集成电路的功能向着更高更强的方向发展,这就使得电子封装的设计和制造技术不断向前发展。近年来,封装技术已成为半导体行业关注的焦点之一,各种封装方法层出不穷,实现了更高层次的封装集成。本文正是要从封装角度来介绍当前电子技术发展现状及趋势。

正文 近年来,我国的封装产业在不断地发展。一方面,境外半导体制造商以及封装代工业纷纷将其封装产能转移至中国,拉动了封装产业规模的迅速扩大;另一方面,国内芯片制造规模的不断扩大,也极大地推动封装产业的高速成长。但虽然如此,IC的产业规模与市场规模之比始终未超过20%,依旧是主要依靠进口来满足国内需求。因此,只有掌握先进的技术,不断扩大产业规模,将国内IC产业国际化、品牌化,才能使我国的IC产业逐渐走到世界前列。 新型封装材料与技术推动封装发展,其重点直接放在削减生产供应链的成本方面,创新性封装设计和制作技术的研发倍受关注,WLP 设计与TSV技术以及多芯片和芯片堆叠领域的新技术、关键技术产业化开发呈井喷式增长态势,推动高密度封测产业以前所未有的速度向着更长远的目标发展。 大体上说,电子封装表现出以下几种发展趋势:(1)电子封装将由有封装向少封装和无封装方向发展;(2)芯片直接贴装(DAC)技术,特别是其中的倒装焊(FCB)技术将成为电子封装的主流形式;(3)三维(3D)封装技术将成为实现电子整机系统功能的有效途径;(4)无源元件将逐步走向集成化;(5)系统级封装(SOP或SIP)将成为新世纪重点发展的微电子封装技术。一种典型的SOP——单级集成模块(SLIM)正被大力研发;(6)圆片级封装(WLP)技术将高速发展;(7)微电子机械系统(MEMS)和微光机电系统(MOEMS)正方兴未艾,它们都是微电子技术的拓展与延伸,是集成电子技术与精密

半导体封装件的可靠性评价方法 Lunasus 科技公司,佐土原宽 Lunasus 科技公司细川丰 本章将依据半导体封装件可靠性评价的基本考虑方法,以故障机理为基础的实验条件介绍,并根据韦布图来解说可靠性试验下的(产品)寿命推导方法。 封装件开发及材料变化过程中的可靠性评价方法 为实现半导体封装件功能和电气特性的提高,在推动多引脚化的同时,也要发展高密度封装化下的小型、薄型化。最近,搭载多个芯片的SiP(System in Package,系统级封装)和芯片尺寸(与封装尺寸)非常相近的CSP(Chip Size Package,芯片级封装)已开始量产,封装件的构造多种多样。另外,为达成封装件低成本化和环保的要求,采用规格更高的封装件材料的开发正在活跃起来。但封装件构造的复杂化和新型材料的使用不能对制造品质和可靠性造成影响。这里将对新型封装件的开发和材料改变下的可靠性评价方法进行解说。 最近的半导体封装件多数属于树脂灌封型,对半导体单体的可靠性评价包括,高温保存(或动作)实验,耐湿性实验以及温度循环实验。另外,对于有可能要进行表面装配的高密度封装器型,需考虑焊接装配过程中的热应力情况,因此焊锡耐热性实验也是不可缺少的。这些可靠性试验,是对半导体封装件在实际使用过程中所预想发生的各种故障进行短时间评价的加速性实验方法。接下来需要先确定半导

体所发生的各种故障的主要加速原因是什么后才能进行实验。例如,对于树脂封装件来讲,湿度(水分)是造成硅芯片上金属线路受到腐蚀(图1)的主要原因之一,而温度可以加快水分浸入封装件内的速度,所以高温、高湿下的实验才有效果。与此同时,在电压也是故障主因的场合,有必要进行高温、高湿下的通电实验。 如上所述,对于封装件相关的各种故障,通过对机理的解析,找出加速实验的主要因子,设定合适的可靠性实验条件,这些就是可靠性评价的基础。 针对封装件构造的可靠性试验 正如开头所述,为实现封装件的高功能、高密度化,封装件的外观形状的主流是QFP(Quad Flat Package,四面扁平封装)和BGA(Ball

什么是晶圆级晶片尺寸封装(Wafer Level Chip Scale Packaging) 1. 晶圆级晶片尺寸封装(Wafer Level Chip Scale Packaging)是先在整片晶圆上进行封装和测试,然后经切割并将IC直接用机台以pick up & flip方式将其放置于Carrier tape中,并以Cover tape保护好后,提供后段SMT (Surface Mounting technology)直接以机台将该IC自Carrier tape取料后,置放于PCB上。 WLCSP选用较大的锡铅球来形成接点藉以进行电性导通,其目的是增加元件与基板底材之间的距离,进而降低并承受来自于基板与元件间因热膨胀差异产生的应力,增加元件的可靠性。利用重分布层技术则可以让锡球的间距作有效率的安排,设计成矩阵式排列(grid array)。采用晶圆制造的制程及电镀技术取代现有打金线及机械灌胶封模的制程,不需导线架或基板。晶圆级封装只有晶粒般尺寸,且有较好的电性效能,因系以每批或每片晶片来生产, 故能享有较低之生产成本。 2.特点:

WLCSP 少掉基材、铜箔等,使其以晶圆形态进行研磨、切割后完成的IC 厚度和一般QFP 、BGA……等等比较起来为最薄、最小、最轻,较符合未来产品轻、薄之需求;且因其不需再进行封装,即可进行后段SMT 制程,故其成本价格可以较一般传统封装为低。 ● 封装技术比较: 封装方式 优 点 缺 点 传统封装(QFP 、BGA ) 1. 技术成熟 2. 制程稳定 1. 无法达到未来细间距要求 2. 制程较复杂 3. 完成的IC 成本高 晶圆级晶片尺寸封装 1. 尺寸小 2. 成本低 3. 简化制程 4. 可达Fine Pitch 要求 1. I/O 数少(<100) 3.产品应用面: 3.1 Power supply (PMIC/PMU, DC/DC converters, MOSFET' s,...) 3.2 Optoelectronic device 3.3 Connectivity (Bluetooth, WLAN) 3.4 Other features (FM, GPS, Camera) 4.生产流程简介

目录 1.01晶圆 2.01制造过程 3.01著名晶圆厂商 4.01制造工艺 4.02表面清洗 4.03初次氧化 4.04热CVD 4.05热处理 4.06除氮化硅 4.07离子注入 4.08退火处理 4.09去除氮化硅层 4.10去除SIO2层 4.11干法氧化法 4.12湿法氧化 4.13氧化 4.14形成源漏极 4.15沉积 4.16沉积掺杂硼磷的氧化层 4.17深处理 5.01专业术语 1.01晶圆

晶圆(Wafer)是指硅半导体集成电路制作所用的硅芯片,由于其形状为圆形,故称为晶圆。晶圆是生产集成电路所用的载体,一般意义晶圆多指单晶硅圆片。 晶圆是最常用的半导体材料,按其直径分为4英寸、5英寸、6英寸、8英寸等规格,近来发展出12英寸甚至研发更大规格(14英吋、15英吋、16英吋、……20英吋以上等)。晶圆越大,同一圆片上可生产的IC就越多,可降低成本;但对材料技术和生产技术的要求更高,例如均匀度等等的问题。一般认为硅晶圆的直径越大,代表着这座晶圆厂有更好的技术,在生产晶圆的过程当中,良品率是很重要的条件。 2.01制造过程 二氧化硅矿石经由电弧炉提炼,盐酸氯化并经蒸馏后,制成了高纯度的多晶硅,其纯度高达99.999999999%,因在精密电子元件当中,硅晶圆需要有相当的纯度,不然会产生缺陷。晶圆制造厂再以柴可拉斯基法将此多晶硅熔解,再于溶液内掺入一小粒的硅晶体晶种,然后将其慢慢拉出,以形成圆柱状的单晶硅晶棒,由于硅晶棒是由一颗小晶粒在融熔态的硅原料中逐渐生成,此过程称为“长晶”。硅晶棒再经过切片、研磨、抛光后,即成为集成电路工厂的基本原料——硅晶圆片,这就是“晶圆”。 很简单的说,单晶硅圆片由普通硅砂拉制提炼,经过溶解、提纯、蒸馏一系列措施制成单晶硅棒,单晶硅棒经过切片、抛光之后,就成为了晶圆。 晶圆经多次光掩模处理,其中每一次的步骤包括感光剂涂布、曝光、显影、腐蚀、渗透、植入、刻蚀或蒸著等等,将其光掩模上的电路复制到层层晶圆上,制成具有多层线路与元件的IC晶圆,再交由后段的测试、切割、封装厂,以制成实体的集成电路成品,从晶圆要加工成为产品需要专业精细的分工。 3.01著名晶圆厂商 只制造硅晶圆基片的厂商 例如合晶(台湾股票代号:6182)、中美晶(台湾股票代号:5483)、信越化学等。 晶圆制造厂 著名晶圆代工厂有台积电、联华电子、格罗方德(Global Fundries)及中芯国际等。英特尔(Intel)等公司则自行设计并制造自己的IC晶圆直至完成并行销其产品。三星电子等则兼有晶圆代工及自制业务。南亚科技、瑞晶科技(现已并入美光科技,更名台湾美光内存)、Hynix、美光科技(Micron)等则专于内存产品。日月光半导体等则为晶圆产业后段的封装、测试厂商。 4.01制造工艺 4.02表面清洗 晶圆表面附着大约2um的Al2O3和甘晶圆,油混合液保护层,在制作前必须进行化学刻蚀和表面清洗。

集成电路封装的发展现 状及趋势 公司内部档案编码:[OPPTR-OPPT28-OPPTL98-OPPNN08]

序号:39 集成电路封装的发展现状及趋势 姓名:张荣辰 学号: 班级:电科本1303 科目:微电子学概论 二〇一五年 12 月13 日

集成电路封装的发展现状及趋势 摘要: 随着全球集成电路行业的不断发展,集成度越来越高,芯片的尺寸不断缩小,集成电路封装技术也在不断地向前发展,封装产业也在不断更新换代。 我国集成电路行业起步较晚,国家大力促进科学技术和人才培养,重点扶持科学技术改革和创新,集成电路行业发展迅猛。而集成电路芯片的封装作为集成电路制造的重要环节,集成电路芯片封装业同样发展迅猛。得益于我国的地缘和成本优势,依靠广大市场潜力和人才发展,集成电路封装在我国拥有得天独厚的发展条件,已成为我国集成电路行业重要的组成部分,我国优先发展的就是集成电路封装。近年来国外半导体公司也向中国转移封装测试产能,我国的集成电路封装发展具有巨大的潜力。下面就集成电路封装的发展现状及未来的发展趋势进行论述。 关键词:集成电路封装、封装产业发展现状、集成电路封装发展趋势。 一、引言 晶体管的问世和集成电路芯片的出现,改写了电子工程的历史。这些半导体元器件的性能高,并且多功能、多规格。但是这些元器件也有细小易碎的缺点。为了充分发挥半导体元器件的功能,需要对其进行密封、扩大,以实现与外电路可靠的电气连接并得到有效的机械、绝缘等

方面的保护,防止外力或环境因素导致的破坏。“封装”的概念正事在此基础上出现的。 二、集成电路封装的概述 集成电路芯片封装(Packaging,PKG)是指利用膜技术及微细加工技术,将芯片及其他要素在框架或基板上布置、粘贴固定及连线,引出接线端并通过可塑性绝缘介质灌封固定,构成整体立体结构的工艺。此概念称为狭义的封装。 集成电路封装的目的,在于保护芯片不受或少受外界环境的影响,并为之提供一个良好的工作条件,以使集成电路具有稳定、正常的功能。封装为芯片提供了一种保护,人们平时所看到的电子设备如计算机、家用电器、通信设备等中的集成电路芯片都是封装好的,没有封装的集成电路芯片一般是不能直接使用的。 集成电路封装的种类按照外形、尺寸、结构分类可分为引脚插入型、贴片型和高级封装。 引脚插入型有DIP、SIP、S-DIP、SK-DIP、PGA DIP:双列直插式封装;引脚在芯片两侧排列,引脚节距,有利于散热,电气性好。 SIP:单列直插式封装;引脚在芯片单侧排列,引脚节距等特征与DIP基本相同。

光刻和晶圆级键合技术在3D互连中的研究 作者:Margarete Zoberbier、Erwin Hell、Kathy Cook、Marc Hennemayer、Dr.-Ing. Barbara Neuber t,SUSS MicroTec 日益增长的消费类电子产品市场正在推动当今半导体技术的不断创新发展。各种应用对增加集成度、降低功耗和减小外形因数的要求不断提高,促使众多结合了不同技术的新结构应运而生,从而又催生出诸多不同的封装方法,因此可在最小的空间内封装最多的功能。正因如此,三维集成被认为是下一代的封装方案。 本文将探讨与三维互连技术相关的一些光刻挑战。还将讨论三维封装使用的晶圆键合技术、所面临的各种挑战、有效的解决方案及未来发展趋势。 多种多样的三维封装技术 为了适应更小引脚、更短互连和更高性能的要求,目前已开发出系统封装(SiP)、系统芯片(SoC)和封装系统(SoP)等许多不同的三维封装方案。SiP即“单封装系统”,它是在一个IC封装中装有多个引线键合或倒装芯片的多功能系统或子系统。无源元件、SAW/BA W滤波器、预封装IC、接头和微机械部件等其他元件都安装在母板上。这一技术造就了一种外形因数相对较小的堆叠式芯片封装方案。 SoC可以将所有不同的功能块,如处理器、嵌入式存储器、逻辑心和模拟电路等以单片集成的方式装在一起。在一块半导体芯片上集成系统设计需要这些功能块来实现。通常,So C设计与之所取代的多芯片系统相比,它的功耗更小,成本更低,可靠性更高。而且由于系统中需要的封装更少,因而组装成本也会有所降低。 SoP采用穿透通孔和高密度布线以实现更高的小型化。它是一种将整个系统安装在一个芯片尺寸封装上的新兴的微电子技术。过去,“系统”往往是一些容纳了数百个元件的笨重的盒子,而SoP可以将系统的计算、通信和消费电子功能全部在一块芯片上完成,从而节约了互连时间,减少了热量的产生。 最近穿透硅通孔(TSV)得到迅速发展,已成为三维集成和晶圆级封装(WLP)的关键技术之一。三维TSV已显现出有朝一日取代引线键合技术的潜力,因此它可以使封装尺寸进

Q/GSXH.Q. 质量管理体系第三层次文件1004.03-2001 可靠性试验规范

拟制:审核:批准: 海锝电子科技有限公司版次:C版 可靠性试验规范 1. 主题内容和适用范围 本档规定了可靠性试验所遵循的原则,规定了可靠性试验项目,条件和判据。 2. 可靠性试验规定 2.1 根据IEC国际标准,国家标准及美国军用标准,目前设立了14个试验项 目(见后目录〕。 2.2 根据本公司成品标准要求,用户要求,质量提高要求及新产品研制、工艺 改进等加以全部或部分采用上述试验项目。 2.3 常规产品规定每季度做一次周期试验,试验条件及判据采用或等效采用产 品标准;新产品、新工艺、用户特殊要求产品等按计划进行。 2.4 采用LTPD的抽样方法,在第一次试验不合格时,可采用追加样品抽样方 法或采用筛选方法重新抽样,但无论何种方法只能重新抽样或追加一次。 2.5 若LTPD=10%,则抽22只,0收1退,追加抽样为38只,1收2退。 抽样必须在OQC检验合格成品中抽取。 3.可靠性试验判定标准。

环境条件 (1)标准状态 标准状态是指预处理, 后续处理及试验中的环境条件。论述如下: 环境温度: 15~35℃ 相对湿度: 45~75% (2)判定状态 判定状态是指初测及终测时的环境条件。论述如下: 环境温度: 25±3℃ 相对湿度: 45~75% 4.试验项目。 目录 4.1 高温反向偏压试验------------------------------------ 第4页4.2 压力蒸煮试验------------------------------------ 第6页4.3 正向工作寿命试验------------------------------------ 第7页4.4 高温储存试验------------------------------------ 第8页4.5 低温储存试验------------------------------------ 第9页4.6 温度循环试验------------------------------------ 第10页4.7 温度冲击试验------------------------------------ 第11页4.8 耐焊接热试验------------------------------------ 第12页4.9 可焊性度试验------------------------------------ 第13页4.10 拉力试验------------------------------------ 第14页

晶圆处理制程 基本晶圆处理步骤通常是晶圆先经过适当的清洗(Cleaning)之后,送到热炉管(Furnace )内,在含氧的环境中,以加热氧化(Oxidation)的方式在晶圆的表面形成一层厚约数百个的二氧化硅层,紧接着厚约1000到2000的氮化硅层将以化学气相沈积Chemical Vapor Deposition;CVP)的方式沈积(Deposition)在刚刚长成的二氧化硅上,然后整个晶圆将进行微影(Lithography)的制程,先在晶圆上上一层光阻(Photoresist),再将光罩上的图案移转到光阻上面。接着利用蚀刻(Etching)技术,将部份未被光阻保护的氮化硅层加以除去,留下的就是所需要的线路图部份。接着以磷为离子源(Ion Source),对整片晶圆进行磷原子的植入(Ion Implantation),然后再把光阻剂去除(Photoresist Scrip)。制程进行至此,我们已将构成集成电路所需的晶体管及部份的字符线(Word Lines),依光罩所提供的设计图案,依次的在晶圆上建立完成,接着进行金属化制程(Metallization),制作金属导线,以便将各个晶体管与组件加以连接,而在每一道步骤加工完后都必须进行一些电性、或是物理特性量测,以检验加工结果是否在规格内(Inspection and Measurement);如此重复步骤制作第一层、第二层...的电路部份,以在硅晶圆上制造晶体管等其它电子组件;最后所加工完成的产品会被送到电性测试区作电性量测。 根据上述制程之需要,FAB厂内通常可分为四大区: 1)黄光本区的作用在于利用照相显微缩小的技术,定义出每一层次所需要的电路图,因为采用感光剂易曝光,得在黄色灯光照明区域内工作,所以叫做「黄光区」。 2)蚀刻经过黄光定义出我们所需要的电路图,把不要的部份去除掉,此去除的步骤就> 称之为蚀刻,因为它好像雕刻,一刀一刀的削去不必要不必要的木屑,完成作品,期间又利用酸液来腐蚀的,所 以叫做「蚀刻区」。 3)扩散本区的制造过程都在高温中进行,又称为「高温区」,利用高温给予物质能量而产生运动,因为本区的机台大都为一根根的炉管,所以也有人称为「炉管区」,每一根炉管都有不同的作用。 4)真空本区机器操作时,机器中都需要抽成真空,所以称之为真空区,真空区的机器多用来作沈积暨离子植入,也就是在Wafer上覆盖一层薄薄的薄膜,所以又称之为「薄膜区」。在真空区中有一站称为 晶圆允收区,可接受芯片的测试,针对我们所制造的芯片,其过程是否有缺陷,电性的流通上是否 有问题,由工程师根据其经验与电子学上知识做一全程的检测,由某一电性量测值的变异判断某一 道相关制程是否发生任何异常。此检测不同于测试区(Wafer Probe)的检测,前者是细部的电子 特性测试与物理特性测试,后者所做的测试是针对产品的电性功能作检测。

可靠性试验的常用术语 Biil of material:BOM 材料清单 可靠性试验常用术语 试验名称英文简称常用试验条件备注 温度循环TCT —65C ~150C, dwell15min, 100cycles 试验设备采用气冷的方式,此温度设置为设备的极限温度 高压蒸煮PCT 121 C,100RH., 2ATM,96hrs 此试验也称为高压蒸汽,英文也称为autoclave 热冲击TST —65 C ~150C, dwell15min, 50cycles 此试验原理与温度循环相同,但温度转换速率更快,所以比温度循环 更严酷。 稳态湿热THT 85C ,85%RH., 168hrs 此试验有时是需要加偏置电压的,一般为Vcb=~, 此时试验为THBT。易焊性solderability 235C,2 ±此试验为槽焊法,试验后为1 0~40倍的显微镜下看管脚的上锡面积。 耐焊接热SHT 260C ,10 ±1s 模拟焊接过程对产品的影响。 电耐久Burn in Vce=, Ic=P/Vce,168hrs 模拟产品的使用。(条件主要针对三极管) 高温反偏HTRB 125C, Vcb=~, 168hrs 主要对产品的PN结进行考核。 回流焊IR reflow Peak C 高温贮存超声波检测225C) HTST SAT 泡、裂缝。但产品表面一定要平整。 IC 产品的质量与可靠性测试 、使用寿命测试项目Life test items 只针对SME产品进行考核,且最多只能做三次。 150C ,168hrs 产品的高温寿命考核。 检测产品的内部离层、气):EFR, OLT (HTOL), LTOL

晶圆制备 硅是一种灰色、易碎、四价的非金属化学元素。地壳成分中27.8%是硅元素构成的,其次是氧元素,硅是自然界中最丰富的元素。在石英、玛瑙、燧石和普通的滩石中就可以发现硅元素。硅是建筑材料水泥、砖、和玻璃中的主要成分,也是大多数半导体和微电子芯片的主要原料。有意思的是,硅自身的导电性并不是很好。然而,可以通过添加适当的搀杂剂来精确控制它的电阻率。 半导体硅制备 半导体器件和电路在半导体材料晶圆的表层形成,半导体材料通常是硅。这些晶圆的杂质含量水平必须非常低,必须掺杂到指定的电阻率水平,必须是指定的晶体结构,必须是光学的平面,并达到许多机械及清洁度的规格要求。制造IC级的硅晶圆分四个阶段进行: 矿石到高纯气体的转变; 气体到多晶的转变; 多晶到单晶,掺杂晶棒的转变; 晶棒到晶圆的制备。 半导体制造的第一个阶段是从泥土里选取和提纯半导体材料的原料。提纯从化学反应开始。对于硅,化学反应是矿石到硅化物气体,例如四氯化硅或三氯硅烷。杂质,例如其他金属,留在矿石残渣里。硅化物再和氢反应生成半导体级的硅。这样的硅的纯度达99.9999999%,是地球上最纯的物质之一。它有一种称为多晶或多晶硅的晶体结构。 制造半导体前,必须将硅转换为晶圆片。这要从硅锭的生长开始。单晶硅是原子以三维空间模式周期形成的固体,这种模式贯穿整个材料。多晶硅是很多具有不同晶向的小单晶体单独形成的,不能用来做半导体电路。多晶硅必须融化成单晶体,才能加工成半导体应用中使用的晶圆片。 加工硅晶片 生成一个硅锭要花一周到一个月的时间,这取决于很多因素,包括大小、质量和终端用户要求。超过 75%的单晶硅晶圆片都是通过 Czochralski (CZ) 直拉法生长的。CZ 硅锭生长需要大块的纯净多晶硅将这些块状物连同少量的特殊III、V族元素放置在石英坩埚中,这称为搀杂。加入的搀杂剂使那些长大的硅锭表现出所需要的电特性。最普通的搀杂剂是硼、磷、砷和锑。因使用的搀杂剂不同,会成为一个 P 型或N型的硅锭(P 型 / 硼, N 型 / 磷、锑、砷),然后将这些物质加热到硅的熔点--摄氏1420度之上。一旦多晶硅和搀杂剂混合物熔解,便将单晶硅种子放在熔解物的上面,只接触表面。种子与要求的成品硅锭有相同的晶向。为了使搀杂均匀,子晶和用来熔化硅的坩埚要以相反的方向旋转。一旦达到晶体生长的条件,子晶就从熔化物中慢慢被提起。生长过程开始于快速提拉子晶,以便使生长过程初期中子晶内的晶缺陷降到最少。然后降低拖拉速度,使晶体的直径增大。当达到所要求的直径时,生长条件就稳定下来以保持该直径。因为种子是慢慢浮出熔化物的,种子和熔化物间的表面张力在子晶表面上形成一层薄的硅膜,然后冷却。冷却时,已熔化硅中的原子会按照子晶的晶体结构自我定向。

晶圆级封装W L P优势 The Standardization Office was revised on the afternoon of December 13, 2020

晶圆级封装(WLP)优势 晶圆级封装(WLP)以BGA技术为基础,是一种经过改进和提高的CSP(芯片级封装),充分体现了BGA、CSP的技术优势。它具有许多独特的优点。 晶圆级封装(Wafer Level Package,WLP)采用传统的IC工艺一次性完成后道几乎所有的步骤,包括装片、电连接、封装、测试、老化,所有过程均在晶圆加工过程中完成,之后再划片,划完的单个芯片即是已经封装好的成品;然后利用该芯片成品上的焊球阵列,倒装焊到PCB板上实现组装。WLP的封装面积与芯片面积比为1:1,而且标准工艺封装成本低,便于晶圆级测试和老化。 晶圆级封装以BGA技术为基础,是一种经过改进和提高的CSP,充分体现了BGA、CSP的技术优势。它具有许多独特的优点: (1)封装加工效率高,它以晶圆形式的批量生产工艺进行制造; (2)具有倒装芯片封装的优点,即轻、薄、短、小; 图5 WLP的尺寸优势 (3)晶圆级封装生产设施费用低,可充分利用晶圆的制造设备,无须投资另建封装生产线; (4)晶圆级封装的芯片设计和封装设计可以统一考虑、同时进行,这将提高设计效率,减少设计费用; (5)晶圆级封装从芯片制造、封装到产品发往用户的整个过程中,中间环节大大减少,周期缩短很多,这必将导致成本的降低;

(6)晶圆级封装的成本与每个晶圆上的芯片数量密切相关,晶圆上的芯片数越多,晶圆级封装的成本也越低。晶圆级封装是尺寸最小的低成本封装。晶圆级封装技术是真正意义上的批量生产芯片封装技术。 WLP的优势在于它是一种适用于更小型集成电路的芯片级封装(CSP)技术,由于在晶圆级采用并行封装和电子测试技术,在提高产量的同时显著减少芯片面积。由于在晶圆级采用并行操作进行芯片连接,因此可以大大降低每个I/O 的成本。此外,采用简化的晶圆级测试程序将会进一步降低成本。利用晶圆级封装可以在晶圆级实现芯片的封装与测试。

UESTC-Ning Ning 1 Chapter 2 Chip Level Interconnection 宁宁 芯片互连技术 集成电路封装测试与可靠性

UESTC-Ning Ning 2 Wafer In Wafer Grinding (WG 研磨)Wafer Saw (WS 切割)Die Attach (DA 黏晶)Epoxy Curing (EC 银胶烘烤)Wire Bond (WB 引线键合)Die Coating (DC 晶粒封胶/涂覆) Molding (MD 塑封)Post Mold Cure (PMC 模塑后烘烤)Dejunk/Trim (DT 去胶去纬) Solder Plating (SP 锡铅电镀)Top Mark (TM 正面印码)Forming/Singular (FS 去框/成型) Lead Scan (LS 检测)Packing (PK 包装) 典型的IC 封装工艺流程 集成电路封装测试与可靠性

UESTC-Ning Ning 3 ? 电子级硅所含的硅的纯度很高,可达99.9999 99999 % ? 中德电子材料公司制作的晶棒( 长度达一公尺,重量超过一百公斤 )

UESTC-Ning Ning 4 Wafer Back Grinding ?Purpose The wafer backgrind process reduces the thickness of the wafer produced by silicon fabrication (FAB) plant. The wash station integrated into the same machine is used to wash away debris left over from the grinding process. ?Process Methods: 1) Coarse grinding by mechanical.(粗磨)2) Fine polishing by mechanical or plasma etching. (细磨抛光 )

By Dianne Shi and Ilan Weisshas 本文介绍,先进圭寸装(advaneed packaging的后端工艺(back-end)之一: xx 圆切片(wafer dicing)。 在过去三十年期间,切片(dieing)系统与刀片(blade)已经不断地改进以对付工艺的挑战和接纳不同类型基板的要求。最新的、对生产率造成最大影响的设备进展包括: 采用两个切割(two cuts)同时进行的、将超程(overtravel)减到最小的双轴(dual-spindle)切片系统,代表性的有日本东精精密的AD3000T和AD2000T;自动心轴扭力监测和自动冷却剂流量调节能力。重大的切片刀片进步包括一些刀片,它们用于很窄条和/或较高芯片尺寸的晶圆、以铜金属化的晶圆、非常薄的晶圆、和在切片之后要求表面抛光的元件用的晶圆。许多今天要求高的应用都要求设备能力和刀片特性两方面都最优化的工艺,以尽可能最低的成本提供尽可能高的效率。 最近,日本东精精密又向市场推出了非接触式的激光切割设备ML200和 ML300 型 切片机制(The Dicing Mechanism) 硅晶圆切片工艺是在“后端”装配工艺中的第一步。该工艺将晶圆分成单个的芯片,用于随后的芯片接合(die bon di ng)、弓I线接合(wire bonding)和测试工序。 一个转动的研磨盘(刀片)完成切片(dicing)。一根心轴以高速, 30,000~60,000rpm (83~175m/sec的线性速度)转动刀片。该刀片由嵌入电镀镍矩 阵黏合剂中的研磨金刚石制成。 在芯片的分割期间,刀片碾碎基础材料(晶圆),同时去掉所产生的碎片。材料的去掉沿着晶方(dice)的有源区域之间的专用切割线(迹道)发生的。冷却剂(通常是去离子水)指到切割缝内,改善切割品质,和通过帮助去掉碎片而延长刀片寿命。每条迹道(street)的宽度(切口)与刀片的厚度成比例。 关键工艺参数 硅圆片切割应用的目的是将产量和合格率最大,同时资产拥有的成本最