第八次实验报告 实验六 数据选择器

一、实验目的要求

1、 熟悉中规模集成电路数据选择器的工作原理与逻辑功能

2、 掌握数据选择器的应用 二、实验仪器、设备

直流稳压电源、电子电路调试器、T4153、CC4011 三、实验线路、原理框图 (一)数据选择器的基本原理

数据选择器是常用的组合逻辑部件之一,它有若干个输入端,若干个控制输入端及一个输出端。

数据选择器的地址变量一般的选择方式是:

(1) 选用逻辑表达式各乘积项中出现次数最多的变量(包括原变量与反变量),以简

化数据输入端的附加电路。

(2) 选择一组具有一定物理意义的量。 (二)T4153的逻辑符号、逻辑功能及管脚排列图

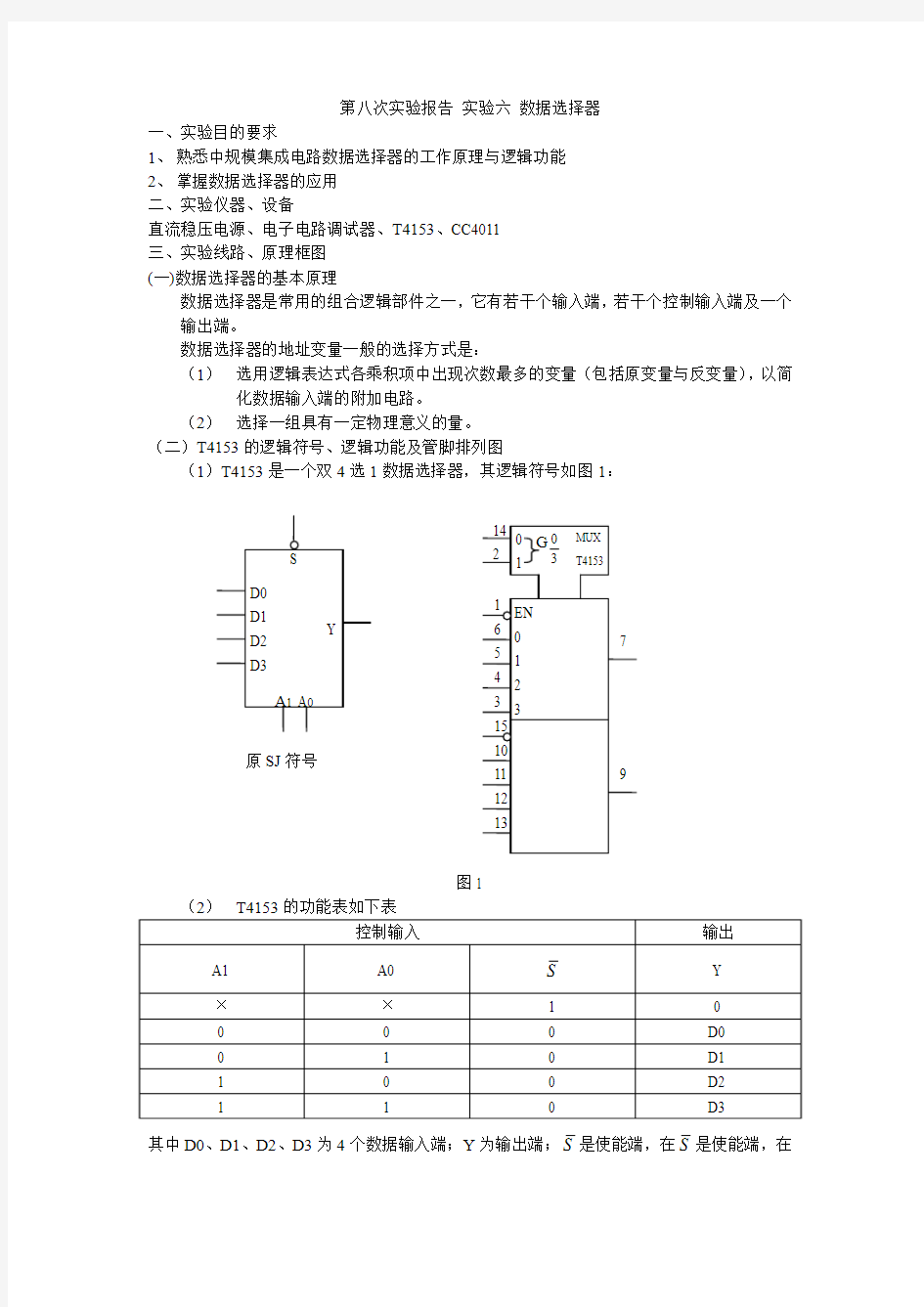

(1)T4153是一个双4选1数据选择器,其逻辑符号如图1:

图1

(2) T4153的功能表如下表

其中D0、D1、D2、D3为4个数据输入端;Y 为输出端;S 是使能端,在S 是使能端,在

原SJ 符号

S =0时使能,在S =1时Y=0;A1、A0是器件中两个选择器公用的地址输入端。该器件的

逻辑表达式为:

Y=S (1A 0A 0D +101D A A +201D A A +301A A A ) (3) T4153的管脚排列图如图2

图2

(三)利用T4153四选一数据选择器设计一个一位二进制全减器的实验原理和实验线路

(1)一位二进制全减器的逻辑功能表见下表:

n D =n A n B 1-n C +n A n B 1-n C +n A n B 1-n C +n A n B 1-n C n C =n A n B 1-n C +n A n B 1-n C +n A n B 1-n C +n A n B 1-n C

=n A n B 1-n C +n A n B +n A n B 1-n C

(3)根据全减器的逻辑功能表设计出的实验线路图为图3:

S 11D 3 1D 2 1D 1 1D 0 1Y

图3

(四)利用4选1数据选择器设计出一个表示血型遗传规律的的电路的实验原理和实验线路

O=D C B A +D C B A +D C B A +D C B A +D BC A +D C AB =D C B A +D B A +D B A +D C AB =D C B A +D B A +D B A +D C AB

A=D C B A +D C B A +D C B A +CD B A +D C AB +D C B A +D C B A

n

n

=D B A +B A +CD B A +D C AB

B=D C B A +D C B A +D BC A +CD B A +D C AB +D C B A +D C B A =D B A +D C B A +D C B A +D C AB AB=D C B A +D C AB +D C B A +D C B A =D C B A +D C B A +D C B A +D C AB (4) 其实验线路图为图4:

图4

四、实验方法步骤

(一) 测试T4153的逻辑功能

按图2接线,测试结果符合T4153功能表

(二) 利用T4153四选一数据选择器设计一个一位二进制全减器 按图3接线,测试结果符合一位二进制全减器功能表

(三) 利用4选1数据选择器设计出一个表示血型遗传规律的的电路 本实验只连接测试表示A 血型遗传规律的电路,其实验线路如下图所示:

图5

测试结果如下:

D C C

第八次实验报告 实验六 数据选择器 一、实验目的要求 1、 熟悉中规模集成电路数据选择器的工作原理与逻辑功能 2、 掌握数据选择器的应用 二、实验仪器、设备 直流稳压电源、电子电路调试器、T4153、CC4011 三、实验线路、原理框图 (一)数据选择器的基本原理 数据选择器是常用的组合逻辑部件之一,它有若干个输入端,若干个控制输入端及一个输出端。 数据选择器的地址变量一般的选择方式是: (1) 选用逻辑表达式各乘积项中出现次数最多的变量(包括原变量与反变量),以简 化数据输入端的附加电路。 (2) 选择一组具有一定物理意义的量。 (二)T4153的逻辑符号、逻辑功能及管脚排列图 (1)T4153是一个双4选1数据选择器,其逻辑符号如图1: 图1 (2) T4153的功能表如下表 其中D0、D1、D2、D3为4个数据输入端;Y 为输出端;S 是使能端,在S 是使能端,在 原SJ 符号

S =0时使能,在S =1时Y=0;A1、A0是器件中两个选择器公用的地址输入端。该器件的 逻辑表达式为: Y=S (1A 0A 0D +101D A A +201D A A +301A A A ) (3) T4153的管脚排列图如图2 图2 (三)利用T4153四选一数据选择器设计一个一位二进制全减器的实验原理和实验线路 (1)一位二进制全减器的逻辑功能表见下表: n D =n A n B 1-n C +n A n B 1-n C +n A n B 1-n C +n A n B 1-n C n C =n A n B 1-n C +n A n B 1-n C +n A n B 1-n C +n A n B 1-n C =n A n B 1-n C +n A n B +n A n B 1-n C (3)根据全减器的逻辑功能表设计出的实验线路图为图3: S 11D 3 1D 2 1D 1 1D 0 1Y

. 数字钟设计实验报告 专业:通信工程 :王婧 班级:111041B 学号:111041226 .

数字钟的设计 目录 一、前言 (3) 二、设计目的 (3) 三、设计任务 (3) 四、设计方案 (3) 五、数字钟电路设计原理 (4) (一)设计步骤 (4) (二)数字钟的构成 (4) (三)数字钟的工作原理 (5) 六、总结 (9) 1

一、前言 此次实验是第一次做EDA实验,在学习使用软硬件的过程中,自然遇到很多不懂的问题,在老师的指导和同学们的相互帮助下,我终于解决了实验过程遇到的很多难题,成功的完成了实验,实验结果和预期的结果也是一致的,在这次实验中,我学会了如何使用Quartus II软件,如何分层设计点路,如何对实验程序进行编译和仿真和对程序进行硬件测试。明白了一定要学会看开发板资料以清楚如何给程序的输入输出信号配置管脚。这次实验为我今后对 EDA的进一步学习奠定了更好的理论基础和应用基础。 通过本次实验对数电知识有了更深入的了解,将其运用到了实际中来,明白了学习电子技术基础的意义,也达到了其培养的目的。也明白了一个道理:成功就是在不断摸索中前进实现的,遇到问题我们不能灰心、烦躁,甚至放弃,而要静下心来仔细思考,分部检查,找出最终的原因进行改正,这样才会有进步,才会一步步向自己的目标靠近,才会取得自己所要追求的成功。 2

二、设计目的 1.掌握数字钟的设计方法。 2熟悉集成电路的使用方法。 3通过实训学会数字系统的设计方法; 4通过实训学习元器件的选择及集成电路手册查询方法; 5通过实训掌握电子电路调试及故障排除方法; 6熟悉数字实验箱的使用方法。 三、设计任务 设计一个可以显示星期、时、分、秒的数字钟。 要求: 1、24小时为一个计数周期; 2、具有整点报时功能; 3、定时闹铃(未完成) 四、设计方案 一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器和定时器组成。干电路系统由秒信号发生器、“时、 3

谢谢欣赏实验三数据选择器 实验人员:班号:学号: 一、实验目的 (1) 熟悉并掌握数据选择器的功能。 (2) 用双4选1数据选择器74LS153设计出一个16选1的数据选择器。 (3) 用双4选1数据选择器74LS153 设计出一个全加法器。 二、实验设备 数字电路实验箱,74LS00,74LS153。 三、实验内容 (1) 测试双4选1数据选择器74LS153的逻辑功能。 74LS153含有两个4选1数据选择器,其中A0和A1为芯片的公共地址输入端,Vcc 和GND分别为芯片的公共电源端和接地端。Figure1为其管脚图: Figure 1 1Q=A1A01D0+A1A0?1D1+A1A0?1D2+A1A0?1D3 2Q=A1A02D0+A1A0?2D1+A1A0?2D2+A1A0?2D3 按下图连接电路: Figure 2 (2) 设某一导弹发射控制机构有两名司令员A、B和两名操作员C、D,只有当两名司令员均同意发射导弹攻击目标且有操作员操作,则发射导弹F。利用所给的实验仪器设计出一个符合上述要求的16选1数据选择器,并用数字电路实验箱上的小灯和开关组合表达实验结果。 思路: 由于本实验需要有四个地址输入端来选中16个数据输入端的地址之中的一个,进而实现选择该数据输入端中的数据的功能,即16选1。而公共的A0、A1两个地址输入端和S使能端(用于片选,已达到分片工作的目的,进而扩展了一位输入)一共可以提供三个地址输入端,故需要采用降维的方法,将一个地址输入隐藏到一个数据输入端Dx 中。本实验可以降一维,也可以降两位。由于两位比较复杂,本实验选择使用降一维的方式。 做法: 画出如应用题中实现所需功能的卡诺图: 谢谢欣赏

北京邮电大学 数字电路与逻辑设计实验 实验报告 实验名称:QuartusII原理图输入 法设计与实现 学院:北京邮电大学 班级: 姓名: 学号:

一.实验名称和实验任务要求 实验名称:QuartusII原理图输入法设计与实现 实验目的:⑴熟悉用QuartusII原理图输入法进行电路设计和仿真。 ⑵掌握QuartusII图形模块单元的生成与调用; ⑶熟悉实验板的使用。 实验任务要求:⑴掌握QuartusII的基础上,利用QuartusII用逻辑 门设计实现一个半加器,生成新的半加器图像模 块。 ⑵用实验内容(1)中生成的半加器模块以及逻辑门 实现一个全加器,仿真验证其功能,并能下载到实 验板上进行测试,要求用拨码开关设定输入信号, 发光二级管显示输出信号。 ⑶用3线—8线译码器(74L138)和逻辑门实现要求 的函数:CBA F+ C + =,仿真验证其 + B C B A A A B C 功能,,并能下载到实验板上进行测试,要求用拨 码开关设定输入信号,发光二级管显示输出信号。二.设计思路和过程 半加器的设计实现过程:⑴半加器的应有两个输入值,两个输出值。 a表示加数,b表示被加数,s表示半加和, co表示向高位的进位。

⑵由数字电路与逻辑设计理论知识可知 b a s ⊕=;b a co ?= 选择两个逻辑门:异或门和与门。a,b 为异 或门和与门的输入,S 为异或门的输出,C 为与门的输出。 (3)利用QuartusII 仿真实现其逻辑功能, 并生成新的半加器图形模块单元。 (4)下载到电路板,并检验是否正确。 全加器的设计实现过程:⑴全加器可以由两个半加器和一个或门构 成。全加器有三个输入值a,b,ci ,两个输 出值s,co :a 为被加数,b 为加数,ci 为低 位向高位的进位。 ⑵全加器的逻辑表达式为: c b a s ⊕⊕= b a ci b a co ?+?⊕=)( ⑶利用全加器的逻辑表达式和半加器的逻 辑功能,实现全加器。 用3线—8线译码器(74L138)和逻辑门设计实现函数 CBA A B C A B C A B C F +++= 设计实现过程:⑴利用QuartusII 选择译码器(74L138)的图形模块

数字逻辑电路 实验报告 指导老师: 班级: 学号: 姓名: 时间: 第一次试验一、实验名称:组合逻辑电路设计

二、试验目的: 1、掌握组合逻辑电路的功能测试。 2、验证半加器和全加器的逻辑功能。 3、、学会二进制数的运算规律。 三、试验所用的器件和组件: 二输入四“与非”门组件3片,型号74LS00 四输入二“与非”门组件1片,型号74LS20 二输入四“异或”门组件1片,型号74LS86 四、实验设计方案及逻辑图: 1、设计一位全加/全减法器,如图所示: 电路做加法还是做减法是由M决定的,当M=0时做加法运算,当M=1时做减法运算。当作为全加法器时输入信号A、B和Cin分别为加数、被加数和低位来的进位,S 为和数,Co为向上的进位;当作为全减法时输入信号A、B和Cin分别为被减数,减数和低位来的借位,S为差,Co为向上位的借位。 (1)输入/输出观察表如下: (2)求逻辑函数的最简表达式 函数S的卡诺图如下:函数Co的卡诺如下: 化简后函数S的最简表达式为: Co的最简表达式为:

(3)逻辑电路图如下所示: 2、舍入与检测电路的设计: 用所给定的集成电路组件设计一个多输出逻辑电路,该电路的输入为8421码,F1为“四舍五入”输出信号,F2为奇偶检测输出信号。当电路检测到输入的代码大于或等于5是,电路的输出F1=1;其他情况F1=0。当输入代码中含1的个数为奇数时,电路的输出F2=1,其他情况F2=0。该电路的框图如图所示: (1)输入/输出观察表如下: B8 B4 B2 B1 F2 F1 0 0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 1 1 0 0 0 1 0 0 1 0 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 1 1 1 0 0 0 1 1 1 0 0 1 0 1 1 0 1 0 0 1 1 0 1 1 1 1 1 1 0 0 0 1 1 1 0 1 1 1

Verilog HDV 数字设计与综合 实验报告 微电子0901班 姓名:袁东明 _ 学号:_04094026 一、实验课题: 1.八选一数据选择器 2.四位数据比较器 二、八选一数据选择器Verilog程序: 2.1主程序 module option(a,b,c,d,e,f,g,h,s0,s1,s2,out); input [2:0] a,b,c,d,e,f,g,h; input s0,s1,s2; output [2:0] out; reg [2:0] out; always@(a or b or c or d or e or f or g or h or s0 or s1 or s2) begin case({s0,s1,s2}) 3'd0 : out=a;

3'd1 : out=b; 3'd2 : out=c; 3'd3 : out=d; 3'd4 : out=e; 3'd5 : out=f; 3'd6 : out=g; 3'd7 : out=h; endcase end endmodule 2.2激励程序 module sti; reg [2:0] A,B,C,D,E,F,G,H; reg S0,S1,S2; wire [2:0] OUT; option dtg(A,B,C,D,E,F,G,H,S0,S1,S2,OUT); initial begin A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=1;

数字电路实验报告 姓名:张珂 班级:10级8班 学号:2010302540224

实验一:组合逻辑电路分析一.实验用集成电路引脚图 1.74LS00集成电路 2.74LS20集成电路 二、实验内容 1、组合逻辑电路分析 逻辑原理图如下:

U1A 74LS00N U2B 74LS00N U3C 74LS00N X1 2.5 V J1 Key = Space J2 Key = Space J3 Key = Space J4 Key = Space VCC 5V GND 图1.1组合逻辑电路分析 电路图说明:ABCD 按逻辑开关“1”表示高电平,“0”表示低电平; 逻辑指示灯:灯亮表示“1”,灯不亮表示“0”。 真值表如下: A B C D Y 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1 表1.1 组合逻辑电路分析真值表 实验分析: 由实验逻辑电路图可知:输出X1=AB CD =AB+CD ,同样,由真值表也能推出此方程,说明此逻辑电路具有与或功能。 2、密码锁问题: 密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开;否则,报警信号为“1”,则接通警铃。

试分析下图中密码锁的密码ABCD 是什么? 密码锁逻辑原理图如下: U1A 74LS00N U2B 74LS00N U3C 74LS00N U4D 74LS00N U5D 74LS00N U6A 74LS00N U7A 74LS00N U8A 74LS20D GND VCC 5V J1 Key = Space J2 Key = Space J3 Key = Space J4 Key = Space VCC 5V X1 2.5 V X2 2.5 V 图 2 密码锁电路分析 实验真值表记录如下: 实验真值表 A B C D X1 X2 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 0 1 1 0 0 0 0 1 1 0 0 1 1 0 1 0 1 0 0 1 1 0 1 1 0 1 1 1 0 0 0 1 1 1 0 1 0 1 1 1 1 0 0 1 1 1 1 1 0 1 表1.2 密码锁电路分析真值表 实验分析: 由真值表(表1.2)可知:当ABCD 为1001时,灯X1亮,灯X2灭;其他情况下,灯X1灭,灯X2亮。由此可见,该密码锁的密码ABCD 为1001.因而,可以得到:X1=ABCD ,X2=1X 。

实验报告 一、实验目的 熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。 二、实验设备 GW48系列SOPC/EDA实验开发系统实验箱一台计算机一台 三、实验内容 1首先利用QuartusⅡ完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出下图所示的仿真波形。最后在实验系统上进行硬件测试,验证本项设计的功能。 源程序为: ENTITY mux21a IS PORT ( a, b, s: IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN PROCESS (a,b,s) BEGIN IF s = '0' THEN y <= a ; ELSE y <= b ; END IF; END PROCESS; END ARCHITECTURE one ;

图(1 ) 2选1多路选择器的编译图 、图(2) 功能仿真的波形图 图(3 ) 功能引脚图

图(4) 2选1多路选择器的RTL电路 2. 将此多路选择器看成是一个元件mux21a,利用元件例化语句描述图,并将此文件放在同一目录中。并对上例分别进行编译、综合、仿真,并对其仿真波形做出分析说明。以下是程序: 图(5) 双二选一多路选择器的编译图

图(6) 双路数据选择器功能仿真图 图(7) 双二选一多路选择器的引脚锁定图图 5 双2选1多路选择器 图(8) 双路数据选择器RTL电路图

图(9) 编程下载图 3.、引脚锁定以及硬件下载测试。若选择目标器件是EP1C3,建议选实验电路模式5,用键1(PIO0,引脚号为1)控制s0;用键2(PIO1,引脚号为2)控制s1;a3、a2 和a1 分别接clock5(引脚号为16)、clock0(引脚号为93)和clock2(引脚号为17);输出信号outy仍接扬声器spker(引脚号为129)。通过短路帽选择clock0接256Hz信号,clock5 接1024Hz,clock2 接8Hz 信号。最后进行编译、下载和硬件测试实验(通过选择键1、键2,控制s0、s1,可使扬声器输出不同音调)。 图(10) 实验电路模式5

本科实验报告实验名称:电路仿真

实验1 叠加定理的验证 1.原理图编辑: 分别调出接地符、电阻R1、R2、R3、R4,直流电压源、直流电流源,电流表电压表(Group:Indicators, Family:VOLTMETER 或AMMETER)注意电流表和电压表的参考方向),并按上图连接; 2. 设置电路参数: 电阻R1=R2=R3=R4=1Ω,直流电压源V1为12V,直流电流源I1为10A。 3.实验步骤: 1)、点击运行按钮记录电压表电流表的值U1和I1; 2)、点击停止按钮记录,将直流电压源的电压值设置为0V,再次点击运行按钮记录电压表电流表的值U2和I2; 3)、点击停止按钮记录,将直流电压源的电压值设置为12V,

将直流电流源的电流值设置为0A,再次点击运行按钮记录电压表电流表的值U3和I3; 4.根据叠加电路分析原理,每一元件的电流或电压可以看成是每一个独立源单独作用于电路时,在该元件上产生的电流或电压的代数和。 所以,正常情况下应有U1=U2+U3,I1=I2+I3; 经实验仿真: 当电压源和电流源共同作用时,U1=-1.6V I1=6.8A. 当电压源短路即设为0V,电流源作用时,U2=-4V I2=2A 当电压源作用,电流源断路即设为0A时,U3=2.4V I3=4.8A

所以有U1=U2+U3=-4+2.4=-1.6V I1=I2+I3=2+4.8=6.8A 验证了原理 实验2 并联谐振电路仿真 2.原理图编辑: 分别调出接地符、电阻R1、R2,电容C1,电感L1,信号源V1,按上图连接并修改按照例如修改电路的网络标号; 3.设置电路参数: 电阻R1=10Ω,电阻R2=2KΩ,电感L1=2.5mH,电容C1=40uF。信号源V1设置为AC=5v,Voff=0,Freqence=500Hz。 4.分析参数设置: AC分析:频率范围1HZ—100MHZ,纵坐标为10倍频程,扫描

第五次试验报告 实验五 译码器 一、实验目的要求 1、熟悉中规模集成电路T4138译码器的工作原理与逻辑功能 2、掌握译码器的应用 二、实验仪器、设备 直流稳压电源、电子电路调试器、万用表、两个T4138、74LS20 三、实验线路、原理框图 1、T4138的逻辑符号 T4138是一个3线—8线译码器,它是一种通用译码器,其逻辑符号如图1所示。 图1 其中,A 2、A 1、A 0是地址输入端,Y 0、Y 1、Y 2、Y 3、Y 4、Y 5、Y 6、Y 7是译码输出端,S 1、 S 2、S 3是使能端,当S 1=1, S 2+S 3=0时,器件使能。 2、T4138的管脚排列 T4138的管脚排列如图2所示: 图2 3、T4138的逻辑功能 T4138的功能表如下表所示: Y Y Y Y Y Y Y 32 (a )原SJ 符号 (b )GB 符号

3线—8线译码器实际上是一个负脉冲输出的脉冲分配器。若利用使能端中的一个输入端输入数据信息,器件就成为一个数据分配器。 4、用T4138实现一个逻辑函数 译码器的每一路输出,实际上是地址码的一个最小项的反变量,利用其中一部分输出端输出的与非关系,也就是它们相应最小项的或逻辑表达式,能方便地实现逻辑函数。 本试验要求实现以下逻辑函数: Y=AB C +A B C+A BC+ABC=ABC BC A C B A C AB ???=7356Y Y Y Y 用T4138和74LS20实现以上逻辑函数,实验线路见下图(图3): 图3 5,用两个3线—8线译码器组成一个4线—16线的译码器 4线—16线的真值表为: “0Y

. .. 数字逻辑电路设计 --多功能数字钟 学院:计算机科学与通信工程 专业: : 学号: 指导老师:

多功能数字钟 一、设计任务及要求 (1)拥有正常的时、分、秒计时功能。 (2)能利用实验板上的按键实现校时、校分及清零功能。 (3)能利用实验板上的扬声器做整点报时。 (4)闹钟功能 (5)在MAXPLUS II 中采用层次化设计方法进行设计。 (6)在完成全部电路设计后在实验板上下载,验证设计课题的正确性。 二、多功能数字钟的总体设计和顶层原理图 作为根据总体设计框图,可以将整个系统分为六个模块来实现,分别是计时模块、校时模块、整点报时模块、分频模块、动态显示模块及闹钟模块。

(1)计时模块 该模块使用74LS160构成的一个二十四进制和两个六十进制计数器级联,构成数字钟的基本框架。二十四进制计数器用于计时,六十进制计数器用于计分和秒。只要给秒计数器一个1HZ的时钟脉冲,则可以进行正常计时。分计数器以秒计数器的进位作为计数脉冲。 用两个74160连成24进制的计数器,原图及生成的器件如下: 生成的二十四进制计数器注: 利用使能端,时钟信号,清零以及预置数功能连成24进制。

用两个74160连成的60进制计数器,原图及生成的器件如下: 生成的六十进制计数器 (2)校时模块 校时模块设计要求实现校时,校分以及清零功能。 *按下校时键,小时计数器迅速递增以调至所需要的小时位。 *按下校分键,分计数器迅速递增以调至所需要的分位。 *按下清零键,将秒计数器清零。 注意事项:①在校分时,分计数器的计数不应对小时位产生影响,因而需要屏蔽此时分计数器的进位信号以防止小时计数器计数。 ②利用D触发器进行按键抖动的消除,因为D触发器是边沿触发,在除去时钟边沿到来前一瞬间之外的绝大部分时间都不接受输入,

《数字电子技术》实验报告 实验序号:01 实验项目名称:门电路逻辑功能及测试 学号姓名专业、班级 实验地点物联网实验室指导教师时间2016.9.19 一、实验目的 1. 熟悉门电路的逻辑功能、逻辑表达式、逻辑符号、等效逻辑图。 2. 掌握数字电路实验箱及示波器的使用方法。 3、学会检测基本门电路的方法。 二、实验仪器及材料 1、仪器设备:双踪示波器、数字万用表、数字电路实验箱 2. 器件: 74LS00 二输入端四与非门2片 74LS20 四输入端双与非门1片 74LS86 二输入端四异或门1片 三、预习要求 1. 预习门电路相应的逻辑表达式。 2. 熟悉所用集成电路的引脚排列及用途。 四、实验内容及步骤 实验前按数字电路实验箱使用说明书先检查电源是否正常,然后选择实验用的集成块芯片插入实验箱中对应的IC座,按自己设计的实验接线图接好连线。注意集成块芯片不能插反。线接好后经实验指导教师检查无误方可通电实验。实验中

1.与非门电路逻辑功能的测试 (1)选用双四输入与非门74LS20一片,插入数字电路实验箱中对应的IC座,按图1.1接线、输入端1、2、4、5、分别接到K1~K4的逻辑开关输出插口,输出端接电平显 图 1.1 示发光二极管D1~D4任意一个。 (2)将逻辑开关按表1.1的状态,分别测输出电压及逻辑状态。 表1.1 输入输出 1(k1) 2(k2) 4(k3) 5(k4) Y 电压值(v) H H H H 0 0 L H H H 1 1 L L H H 1 1 L L L H 1 1 L L L L 1 1 2. 异或门逻辑功能的测试

图 1.2 (1)选二输入四异或门电路74LS86,按图1.2接线,输入端1、2、4、5接逻辑开关(K1~K4),输出端A、B、Y接电平显示发光二极管。 (2)将逻辑开关按表1.2的状态,将结果填入表中。 表1.2 输入输出 1(K1) 2(K2) 4(K35(K4) A B Y 电压(V) L H H H H L L L H H H H L L L H H L L L L L H H 1 1 1 1 1 1 1 1

电气工程学院电工电子教学基地 数字电子技术实验 实验报告 仿真实验1 用数据选择器设计函数发生器 学号:18291035 姓名:陈涟漪 班级:电气1802 成绩: 指导教师:周晖 完成时间:2020年5 月15 日

数字电子技术实验 仿真实验1 用数据选择器设计函数发生器 1 实验任务 使用数据选择器74LS151和适当门电路设计一函数发生器,能够实现4位二进制码数据范围指示功能。要求该函数发生器能区别以下三种情况: (1)0≤X≤4; (2)5≤X≤9; (3)10≤X≤15。 2 实验电路

3 实验步骤 采用A、B、C、D取0或1依次表示这四位二进制码的从高到低位的取值(例如:A=0,B=1,C=0,D=0表示四位二进制码0100)。则对于第一组来说,共有5个四位二进制码包含在其中,用卡诺图表示如下: 化简即得: 同理,也有5个数包含在第二组中,卡诺图如下: 化简即得: 第三组包含了6个数,卡诺图如下:

化简即得: 对以上三个式子都去两次非并利用摩根定律可得: 这样就完成了该问题的逻辑转化。 根据前面对该实验分析所得到的逻辑表达式可以发现,输入变量为A、B、C、D,但是在后面的逻辑运算中它们的“非”都用到了,也就是第一步我们要得到这四个变量的非。然后再进行后面的与非运算。三个输出变量的状态也可以用三个灯泡来表示,这里采用了三个颜色不同的灯泡用以区分。到这里,逻辑图就可以很容易的用Multisim软件模拟出来。 其中,最上面的X1灯泡亮时,表示输入数字在0≤X≤4范围内,X2亮时表示输入数字在5≤X≤9范围内,X3亮时表示输入数字在10≤X≤15范围内。这里还是用了四个开关,每个开关“开”表示1,“关”表示0,四个开关以ABCD的顺序来表示四位二进制数。四位二进制数同上,也有16中情况,这里不做一一展示,只对每一类给出一种模拟结果。

实验一 逻辑门电路 一、与非门逻辑功能的测试 74LS20(双四输入与非门) 仿真结果 二、 或非门逻辑功能的测试 74LS02(四二输入或非门) 仿真结果: 三、与或非门逻辑功能的测试 74LS51(双二、三输入与或非门) 仿真结果: 四、异或门逻辑功能的测试 74LS86(四二输入异或 门)各一片 仿真结果: 二、思考题 1. 用一片74LS00实现Y = A+B 的逻辑功能 ; 2. 用一片74LS86设计 一个四位奇偶校验电路; 实验二 组合逻辑 电路 一、分析半加器的逻辑功能 二. 验证

的逻辑功能 4.思考题 (1)用两片74LS138 接成四线-十六线译码器 0000 0001 0111 1000 1111 (2)用一片74LS153接成两位四选一数据选择器; (3)用一片74LS153一片74LS00和接成一位全加器 (1)设计一个有A、B、C三位代码输入的密码锁(假设密码是011),当输入密码正确时,锁被打开(Y1=1),如果密码不符,电路发出报警信号(Y2=1)。 以上四个小设计任做一个,多做不限。 还可以用门电路搭建 实验三触发器及触发器之间的转换 1.D触发器逻辑功能的测试(上升沿) 仿真结果; 2.JK触发器功能测试(下降沿) Q=0 Q=0略

3.思考题: (1) (2) (3)略 实验四寄存器与计数器 1.右移寄存器(74ls74 为上升沿有效) 2.3位异步二进制加法,减法计数器(74LS112 下降沿有效) 也可以不加数码显示管 3.设计性试验 (1)74LS160设计7进制计数器(74LS160 是上升沿有效,且异步清零,同步置数)若采用异步清零: 若采用同步置数: (2)74LS160设计7进制计数器 略 (3)24进制 83进制 注意:用74LS160与74LS197、74LS191是完全不一样的 实验五555定时器及其应用 1.施密特触发器

数字电路组合逻辑电路设 计实验报告 The Standardization Office was revised on the afternoon of December 13, 2020

实验三组合逻辑电路设计(含门电路功能测试)

一、实验目的 1.掌握常用门电路的逻辑功能 2.掌握小规模集成电路设计组合逻辑电路的方法 3.掌握组合逻辑电路的功能测试方法 二、实验设备与器材 Multisim 、74LS00 四输入2与非门、示波器、导线 三、实验原理 TTL集成逻辑电路种类繁多,使用时应对选用的器件做简单逻辑功能检查,保证实验的顺利进行。 测试门电路逻辑功能有静态测试和动态测试两种方法。静态测试时,门电路输入端加固定的高(H)、低电平,用示波器、万用表、或发光二极管(LED)测

出门电路的输出响应。动态测试时,门电路的输入端加脉冲信号,用示波器观测输入波形与输出波形的同步关系。 下面以74LS00为例,简述集成逻辑门功能测试的方法。74LS00为四输入2与非门,电路图如3-1所示。74LS00是将四个二输入与非门封装在一个集成电路芯片中,共有14条外引线。使用时必须保证在第14脚上加+5V电压,第7脚与底线接好。 整个测试过程包括静态、动态和主要参数测试三部分。 表3-1 74LS00与非门真值表 1.门电路的静态逻辑功能测试 静态逻辑功能测试用来检查门电路的真值表,确认门电路的逻辑功能正确与否。实验时,可将74LS00中的一个与非门的输入端A、B分别作为输入逻辑变量,加高、低电平,观测输出电平是否符合74LS00的真值表(表3-1)描述功能。

实验三选数据选择器实 验报告 集团公司文件内部编码:(TTT-UUTT-MMYB-URTTY-ITTLTY-

实验三、八选一数据选择器 一、实验目的: 1.熟悉Quartus II6.0软件的使用和FPGA设计流程 2.用VHDL语言进行八选一数据选择器的设计 二、实验步骤: 一.建立文件夹:在D盘“xingming”的文件夹下建立一个名为“choice8”的文件夹。 二.建立新工程 1.双击桌面上Quartus II6.0 的图标,启动该软件。 2.通过File => New Project Wizard… 菜单命令启动新项目向导。在 随后弹出的对话框上点击Next按钮,在 What is the working directory for this project 栏目中设定新项目所使用的路径:D:\xingming\choice8;在 What is the name of this project 栏目中输入新项目的名字:choice8,点击 Next 按钮。在下一个出现的对话框中继续点击Next,跳过这步。 3.为本项目指定目标器件:选择器件系列为ACEX1K ,选择具体器件为 EP1K30TC144-3 1728 24576 ,再点击Next。在弹出的下一对话框中继续点击Next ,最后确认相关设置,点击Finish按钮,完成新项目创建。 三.设计输入 1.建立一个VHDL文件。通过 File => New 菜单命令,在随后弹出的对 话框中选择 VHDL File选项,点击 OK 按钮。通过 File => Save As 命令,将其保存,并加入到项目中。 2.在VHDL界面输入8选1数据选择器程序,然后通过File => Save

成都理工大学实验报告 课程名称:数字通信原理 姓名:__________________学号:______________ 成绩:____ ___ 实验三Matlab的数字调制系统仿真实验(参考) 1 数字调制系统的相关原理 数字调制可以分为二进制调制和多进制调制,多进制调制是二进制调制的推广,主要讨论二进制的调制与解调,简单讨论一下多进制调制中的差分相位键控调制(M-DPSK)。 最常见的二进制数字调制方式有二进制振幅键控(2-ASK)、移频键控(2-FSK)和移相键控(2-PSK 和2-DPSK)。下面是这几种调制方式的相关原理。 1.1 二进制幅度键控(2-ASK) 幅度键控可以通过乘法器和开关电路来实现。载波在数字信号1 或0 的控制下通或断,在信号为1 的状态载波接通,此时传输信道上有载波出现;在信号为0 的状态下,载波被关断,此时传输信道上无载波传送。那么在接收端我们就可以根据载波的有无还原出数字信号的1 和0。 幅移键控法(ASK)的载波幅度是随着调制信号而变化的,其最简单的形式是,载波在二进制调制信号控制下通断,此时又可称作开关键控法(OOK)。多电平MASK调制方式是一种比较高效的传输方式,但由于它的抗噪声能力较差,尤其是抗衰落的能力不强,因而一般只适宜在恒参信道下采用。 2-ASK 信号功率谱密度的特点如下: (1)由连续谱和离散谱两部分构成;连续谱由传号的波形g(t)经线性调制后决定,离散谱由载波分量决定; (2)已调信号的带宽是基带脉冲波形带宽的二倍。 1.2 二进制频移键控(2-FSK) 数字频率调制又称频移键控(FSK),二进制频移键控记作2FSK。数字频移键控是用载波的频率来传送数字消息,即用所传送的数字消息控制载波的频率。2FSK

实验三、八选一数据选择器 一、实验目的: 1.熟悉Quartus II6.0软件的使用和FPGA设计流程 2.用VHDL语言进行八选一数据选择器的设计 二、实验步骤: 一.建立文件夹:在D盘“xingming”的文件夹下建立一个名为“choice8” 的文件夹。 二.建立新工程 1.双击桌面上Quartus II6.0 的图标,启动该软件。 2.通过File => New Project Wizard… 菜单命令启动新项目向导。在随后弹 出的对话框上点击Next按钮,在 What is the working directory for this project 栏目中设定新项目所使用的路径:D:\xingming\choice8;在What is the name of this project 栏目中输入新项目的名字:choice8,点击 Next 按钮。在下一个出现的对话框中继续点击Next,跳过这步。 3.为本项目指定目标器件:选择器件系列为ACEX1K ,选择具体器件为 EP1K30TC144-3 1728 24576 ,再点击Next。在弹出的下一对话框中继续点击Next ,最后确认相关设置,点击Finish按钮,完成新项目创建。 三.设计输入 1.建立一个VHDL文件。通过 File => New 菜单命令,在随后弹出的对话框中 选择 VHDL File选项,点击 OK 按钮。通过 File => Save As 命令,将其保存,并加入到项目中。 2.在VHDL界面输入8选1数据选择器程序,然后通过File => Save As 命 令保存。

四.综合适配 1.选择Processing =>Start Compilation命令,检查发现无程序语法错误。 2.执行Tools =>Netlist Viewer =>RTL Viewe, 生成RTL图。 五.模拟仿真 1.在 File 菜单下,点击 New 命令。在随后弹出的对话框中,切换到 Other Files 页。选中 Vector Waveform File 选项,点击 OK 按钮。 2.选择命令 Edit=>End Time ,时间设置为30000ns , 进入到波形编辑界 面。在 Edit 菜单下,点击Insert Node or Bus… 命令,或在结点名字区连续双击鼠标左键两次,在新出现的框图中点击Node Finder出现结点查找器窗口搜索结点名, 在上一个框图中点击 Node Finder… 按钮后,打开Node Finder 对话框。点击 List 按钮,列出电路所有的端子。点击 >> 按钮,全部加入。点击 OK 按钮,确认。 3.回到 Insert Node or Bus 对话框,点击 OK 按钮,确认。 4.编辑输入激励信号波形.选中 a 信号,在 Edit 菜单下,选择 Value => Clock… 命令。在随后弹出的对话框的 Period 栏目中设定参数为10ns,点击 OK 按钮,重复前面的操作,设置输入信号b的参数为20ns ,c信号的参数为30ns,d信号的参数为40ns,e信号的参数为50ns,f信号的参数为60ns,g信号的参数为70ns,h信号的参数为80ns,输入激励信号波形编辑完毕。同样的,s[0]、s[1]、s[2]的参数分别设置为10ns、20ns、30ns。 5.功能仿真:(1)Processing=>Generate Functional Simulation Netlist

数字逻辑与CPU 仿真实验报告 姓名: 班级: 学号:

仿真实验 摘要:Multisim是Interactive Image Technologies公司推出的以Windows为基础的仿真工具,具有丰富的仿真分析能力。本次仿真实验便是基于Multisim软件平台对数字逻辑电路的深入研究,包括了对组合逻辑电路、时序逻辑电路中各集成元件的功能仿真与验证、对各电路的功能分析以及自行设计等等。 一、组合逻辑电路的分析与设计 1、实验目的 (1)掌握用逻辑转换器进行逻辑电路分析与设计的方法。 (2)熟悉数字逻辑功能的显示方法以及单刀双掷开关的应用。 (3)熟悉字信号发生器、逻辑分析仪的使用方法。 2、实验内容和步骤 (1)采用逻辑分析仪进行四舍五入电路的设计 ①运行Multisim,新建一个电路文件,保存为四舍五入电路设计。 ②在仪表工具栏中跳出逻辑变换器XLC1。 图1-1 逻辑变换器以及其面板 ③双击图标XLC1,其出现面板如图1-1所示 ④依次点击输入变量,并分别列出实现四舍五入功能所对应的输出状态(点击输出依 次得到0、1、x状态)。 ⑤点击右侧不同的按钮,得到输出变量与输入变量之间的函数关系式、简化的表达式、 电路图及非门实现的逻辑电路。 ⑥记录不同的转换结果。

(2)分析图1-2所示代码转换电路的逻辑功能 ①运行Multisim,新建一个电路文件,保存为代码转换电路。 ②从元器件库中选取所需元器件,放置在电路工作区。 ?从TTL工具栏选取74LS83D放置在电路图编辑窗口中。 ?从Source库取电源Vcc和数字地。 ?从Indictors库选取字符显示器。 ?从Basic库Switch按钮选取单刀双掷开关SPD1,双击开关,开关的键盘控制设 置改为A。后面同理,分别改为B、C、D。 图1-2 代码转换电路 ③将元件连接成图1-2所示的电路。 ④闭合仿真开关,分别按键盘A、B、C、D改变输入变量状态,将显示器件的结果填 入表1-1中。 ⑤说明该电路的逻辑功能。 表1-1 代码转换电路输入输出对应表

哈尔滨理工大学数字集成电路设计实验报告 学院:应用科学学院 专业班级:电科12 - 1班 学号:32 姓名:周龙 指导教师:刘倩 2015年5月20日

实验一、反相器版图设计 1.实验目的 1)、熟悉mos晶体管版图结构及绘制步骤; 2)、熟悉反相器版图结构及版图仿真; 2. 实验内容 1)绘制PMOS布局图; 2)绘制NMOS布局图; 3)绘制反相器布局图并仿真; 3. 实验步骤 1、绘制PMOS布局图: (1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层; (4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层; (7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察; 2、绘制NMOS布局图: (1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览; 3、绘制反相器布局图: (1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice 模拟; 4. 实验结果 nmos版图

译码器和数据选择器 12级电子信息工程20121060192 朱加熊 实验目的 1、熟悉集成译码器和数据选择器。 2、掌握集成译码器和数据选择器的应用。 3、学习组合逻辑电路的设计。 实验仪器及材料 1、双踪示波器 2、器件: 74LS00 二输入端四“与非”门1片 74LS20 四输入端双“与非”门1片 74LS139 双2-4先译码器1片 74LS153 双4选1数据选择器1片 实验内容 1、译码器逻辑功能测试 将74LS139译码器按图3.1接线,按表3.1分别置位输入电平,填输出状态表。

仿真结果Y0 Y1

Y2 Y3

2、译码器转换 将双2-4线译码器转换为3-8译码器。 (1)、画出转换电路图。 (2)、在试验箱上接线并验证设计是否正确。 (3)、设计并填写该3-8线译码器逻辑功能表,画出输入、输出波形。 电路图

逻辑功能表 注:表中Y=Yi 表示Yi=0,其余输 出值为1 3、数据选择器的测试及应 用 (1)、将双4选1数据选择器74LS153参照图3.2接线,测试其逻辑功能并填写功能表3.2. A B C Y 0 0 0 Y0 0 1 Y1 0 1 0 Y 2 0 1 1 Y 3 1 0 0 Y 4 1 0 1 Y 5 1 1 0 Y 6 1 1 1 Y7

(2)、将试验箱上4个不同频率的脉冲信号接到数据选择器4个输入端,将选择端置位,使输入端分别观察到4种不同频率的脉冲信号。 (3)、分析上述实验结果并总结数据选择器的作用。 逻辑功能表 输出控制选择端数据输入端输出 E A1 A2 D3 D2 D1 D0Y H X X X X X X L L L L X X X L L L L L X X X H H L L H X X L X L L L H X X H X H L H L X L X X L L H L X H X X H