5.1.6 SelectIO模块

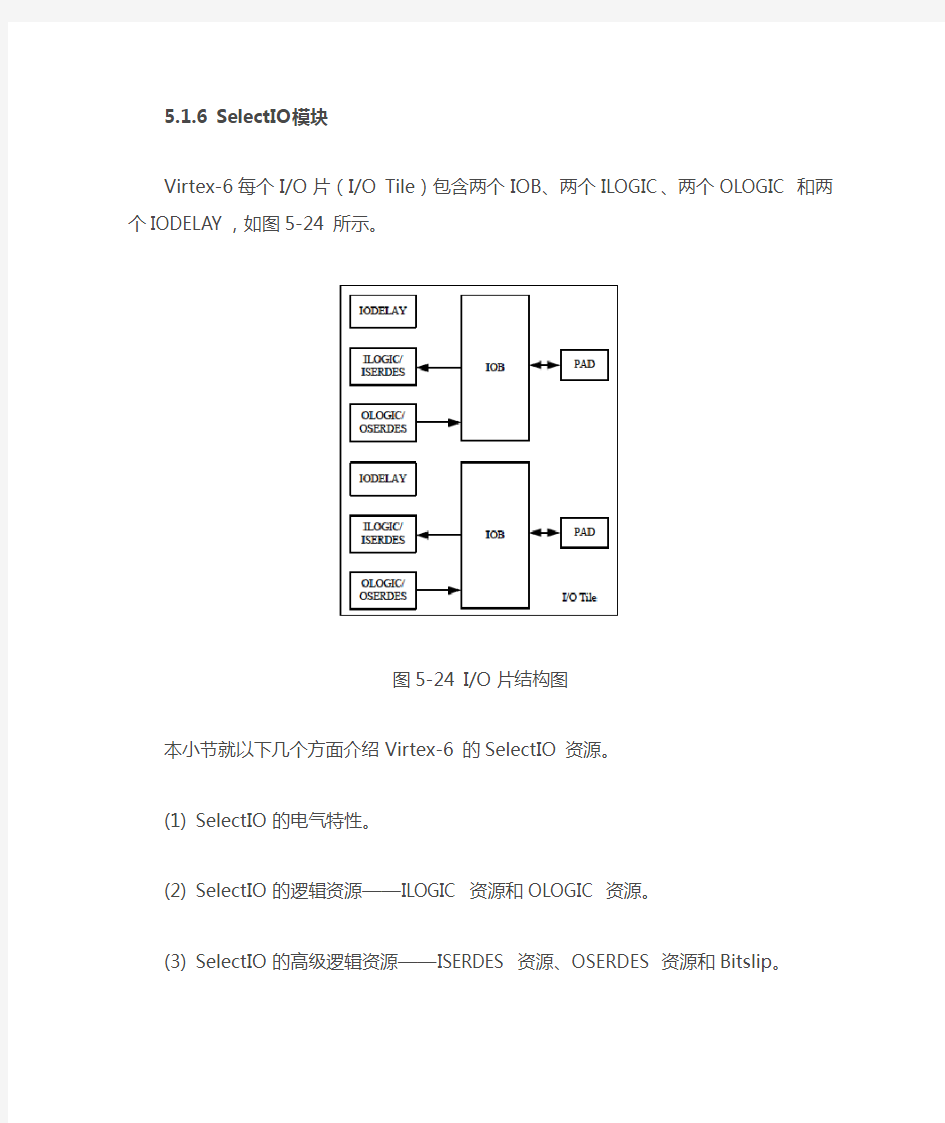

Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。

图5-24 I/O 片结构图

本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。

(1) SelectIO 的电气特性。

(2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。

(3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。

一、SelectIO IO 的电气特性

所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。支持单端I/O 标准(LVCMOS、

HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。

注意:差分输入和VREF 相关输入由VCCAUX 供电。

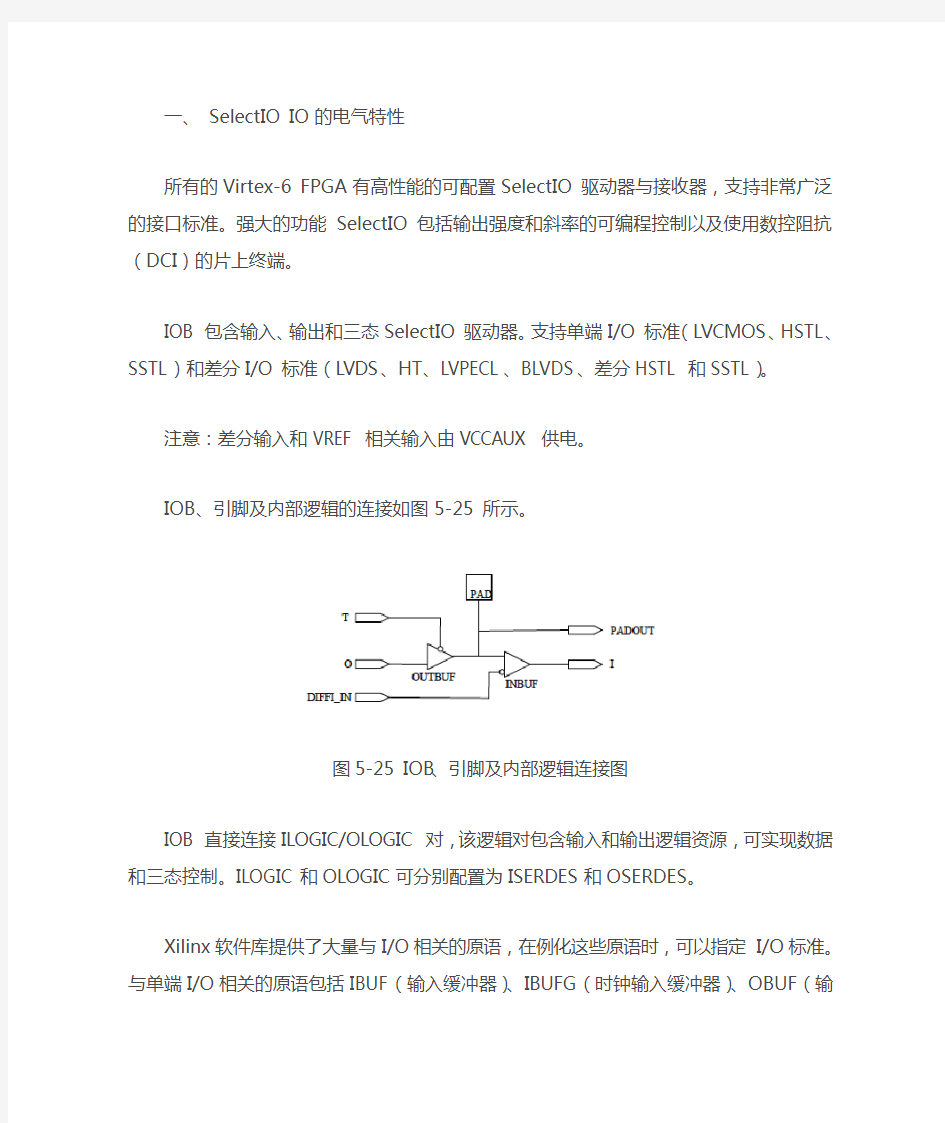

IOB、引脚及内部逻辑的连接如图5-25 所示。

图5-25 IOB、引脚及内部逻辑连接图

IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O

标准。与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。

二、SelectIO的逻辑资源

SelectIO的逻辑资源主要是指ILOGIC和OLOGIC资源,它们完成了FPGA引脚到内部逻辑的连接功能,包括组合输入/输出、三态输出控制、寄存器输入/输出、寄存器三态输出控制、DDR输入/输出、DDR输出三态控制、IODELAYE1高分辨率可调整延迟单元及其控制模块。

下面简要介绍ILOGIC和OLOGIC功能。

(1) ILOGIC。

图5-26 ILOGIC内部逻辑

ILOGIC的内部逻辑如图5-26所示,可以实现的操作包括:异步/组合逻辑、DDR 模式(OPPOSITE_EDGE、SAME_EDGE或SAME_EDGE_PIPELINED)、电平敏感型锁存器和边沿触发D型触发器。

?异步/组合逻辑。

用来创建输入驱动器与FPGA内部资源之间的直接连接。当输入数据与FPGA 内部逻辑之间存在直接(非寄存)连接,或者当“将I/O寄存器/锁存器合并到IOB 中”的设置为OFF时,此通路被自动使用。

?输入DDR(IDDR)。

Virtex-6器件的ILOGIC中有专用寄存器来实现输入双倍数据速率(DDR)。可以通过例化IDDR的原语来使用此功能。IDDR只有一个时钟输入,下降沿数据由输入时钟的反相版本(在ILOGIC内完成反相)进行时钟控制。所有输入I/O 模块的时钟均为完全多路复用,即ILOGIC或OLOGIC模块之间不共用时钟。IDDR支持以下三种操作模式:

OPPOSITE_EDGE模式、SAME_EDGE模式和SAME_EDGE_PIPELINED模式。

SAME_EDGE和SAME_EDGE_PIPELINED与Virtex-5一样。这些模式允许设计人员在ILOGIC模块内部将下降沿数据转移到上升沿时钟域,以节省CLB和时钟资源并提高性能。这些模式是用DDR_CLK_EDGE属性实现的。

各模式下时序图请参考图5-27、图5-28和图5-29。

图5-27 OPPOSITE_EDGE模式下的输入双倍数据速率

图5-28 SAME_EDGE模式下的输入双倍数据速率

图5-29 SAME_EDGE_PIPELINED模式下的输入双倍数据速率

可编程绝对延迟单元IODELAYE1。

每个I/O模块包含一个可编程绝对延迟单元,称为IODELAYE1。IODELAYE1可以连接到ILOGIC/ISERDES或OLOGIC/OSERDES模块,也可同时连接到这两个模块。

IODELAYE1是具有32个tap的环绕延迟单元,具有标定的tap分辨率。请参考附带光盘中的《Virtex-6 IO用户手册》。IODELAYE1可用于组合输入通路、寄存输入通路、组合输出通路或寄存输出通路,还可以在内部资源中直接使用。IODELAYE1允许各输入信号有独立的延迟。通过在《Virtex-6用户手册》中规定的范围内选择IDELAYCTRL参考时钟,可以改变tap延迟分辨率。IODELAYE1资源可用作IDELAY、ODELAY或组合延迟。

.IDELAYE1允许各输入信号有独立的延迟。延迟单元可以被校验到一个绝对延时固定值(TIDELAYRESOLUTION),这个值不随工艺,电压和温度的变化而改变。

IODELAYE1有四种操作模式:分别是零保持时间延迟模式

(IDELAY_TYPE=DEFAULT)、固定延迟模式(IDELAY_TYPE=FIXED)、可变延迟模式(IDELAY_TYPE=VARIABLE)和可装载的可变延时模式(IDELAY_TYPE=VAR_LOADABLE)。零保持时间延迟模式允许向后兼容,以使用Virtex-5器件中的零保持时间延迟功能的设计,在这种模式下使用时,不需要例化IDELAYCTRL的原语。在固定延迟模式,延迟值由属性

IDELAY_VALUE确定的tap数决定,此值配置后不可更改,此模式必须例化IDELAYCTRL的原语。在可变延迟模式,配置后通过控制信号CE和INC来改变延迟值,此模式必须例化IDELAYCTRL的原语。在可装载的可变延时模式下,IDELAY TAP可以通过FPGA逻辑相连的5位CNTVALUEIN<4:0>装载。当配置为此模式时,也必须例化IDELAYCTRL原语。

?IDELAYCTRL延时控制模块。

当IDELAYE1或ISERDES的原语中的IOBDELAY_TYPE属性设置为FIXED、VARIABLE或者VAR_LOADABLE时,都必须例化IDELAYCTRL。IDELAYCTRL模块连续校验IODELAYE1的延时环节,以减少工艺、电压和温度的影响。

(2) OLOGIC资源。

OLOGIC由两个主要模块组成,分别是输出数据通路和三态控制通路。这两个模块具有共同的时钟(CLK),但具有不同的使能信号OCE和TCE。

输出通路和三态通路可独立配置为边沿触发的D型触发器、电平敏感锁存器、异步/组合逻辑或者DDR模式。

?组合数据输出和三态控制路径。

组合输出通路用来实现从FPGA内部逻辑到输出驱动器或输出驱动器控制端的直接连接。当FPGA的内部逻辑与输出数据或三态控制之间存在直接(不寄存)连接,或者当“将I/O寄存器/锁存器合并到IOB中”的设置为OFF时,此路径被使用。

?输出DDR(ODDR)。

Virtex-6器件的OLOGIC中具有专用寄存器,用来实现DDR功能。要使用此功能,只需要例化ODDR。ODDR只有一个时钟输入,下降沿数据由输入时钟的反相时钟控制。ODDR支持两种操作模式:OPPOSITE_EDGE模式和

SAME_EDGE模式。SAME_EDGE模式允许在ODDR时钟的上升沿将两个数据送至ODDR,以节省CLB和时钟资源并提高性能。OPPOSITE_EDGE模式使用时钟的两个沿以两倍吞吐量从FPGA内部采集数据,两个输出都送至IOB 的数据输入或三态控制输入。图5-30所示为使用OPPPOSITE_EDGE模式时输出DDR的时序图。图5-31所示为使用SAME_EDGE模式时输出DDR的时序图。

图5-30 OPPPOSITE_EDGE模式时输出DDR

图5-31 SAME_EDGE模式时输出DDR

输出ODDR可以将时钟的一个副本传送到输出。将ODDR原语的D1固定为High,D2固定为Low,时钟与数据ODDR的时钟一样。这个方案可以确保输出数据与输出时钟延时的一致性。

三、SelectIO的高级特性

除了SelectIO的电器特性和专用于收发SDR或DDR数据的寄存器结构之外,Virtex-6还提供了更高级的逻辑特性。其中包含串并转换器ISERDES、并串转换器OSERDES和Bitslip。

(1) ISERDES。

Virtex-6 ISERDES是专用的串并转换器,具有专门实现高速源同步应用的时钟控制与逻辑功能。图5-32为ISERDES的结构图,其中包括串并转换器(ISERDES)、Bitslip子模块,以及对选通存储器接口的支持,如网络接口、DDR3接口和QDR接口。

图5-32 ISERDES结构图

输入串并转换器。

ISERDES解串器可以实现高速数据传输,不要求FPGA内部资源与输入数据频率匹配。此转换器支持SDR和DDR。在SDR模式下,串并转换器可以实现2、3、4、5、6、7或8bit宽的并行字。在DDR模式下,串并转换器可以实现4、6、8或10位宽的并行字。

ISERDES的原语ISERDES1如图5-33所示。

图5-33 ISERDES的原语ISERDES1

Bitslip模块。

Virtex-6器件中的所有ISERDES模块都包含一个Bitslip子模块。这个子模块可在源同步网络型应用中实现字对齐。Bitslip对ISERDES模块中的并行数据重新排序,以便将解串器所接收重复串行模式的每种组合都送至FPGA内部逻辑。这种重复串行模式通常称为培训模式(许多网络和电信标准都支持培训模式)。

Bitslip操作通过将ISERDES模块的Bitslip引脚置为有效,可以在并行侧对输入串行数据流重新排序。此操作重复进行,直到找到训练模型。图5-34 中所示为SDR 和DDR 模式下Bitslip 操作的效果。为了便于说明,采用了八位数据宽度。Bitslip 操作与CLKDIV 同步。在SDR 模式下,每次Bitslip 操作使输出模式左移一位。在DDR 模式下,每次Bitslip

操作使输出模式在右移一位和左移三位之间交替变化。在此示例中,输出模式在第八次Bitslip 操作时还原到初始模式。这里假定串行数据是八位重复模式。

图5-34 Bitslip 操作

使用Bitslip 子模块的指导原则如下。

只有在NETWORKING 模式下,Bitslip 才有效。其他模式下,不支持Bitslip。

要启动Bitslip 操作,BITSLIP 端口置为High 有效的时间必须持续在一个CLKDIV 周期。在SDR 模式下,Bitslip 的置位时间不能长达两个连续的CLKDIV 周期;在两次Bitslip有效置位之间,Bitslip 的无效时间至少有一个CLKDIV 周期。在SDR 和DDR 两种模式下,从ISERDES 采样到Bitslip 有效的宣称输入到“bit-slipped”ISERDES 的输出Q1-Q6 被

采样到FPGA 内部逻辑,总延迟是两个CLKDIV 周期。

?对选通存储器接口的支持。

ISERDES 包含专用电路(包括OCLK 输入引脚),可以完全在ISERDES 模块内部处理选通门到FPGA 跨时钟域的功能。该功能可以极大方便选通存储器的支持,如网络接口、DDR3 接口和QDR 接口。

(2) 输出并串转换器(OSERDES)。

Virtex-6 OSERDES 是专用的并串转换器,用来实现高速源同步接口设计。每个OSERDES 模块包括一个数据串行器和一个实现三态控制的串行器。此转换器支持SDR 和DDR。数据串行化可达6:1(如果使用“OSERDES 宽度扩展”可达10:1)。三态串行化可达4:1。OSERDES 的框图如图5-35 所示。

?数据并串转换器。

一个OSERDES 模块中的数据并串转换器接收来自内部逻辑的二到六位并行数据,将数据串行化,然后通过OQ 输出将数据送至IOB。并行数据串行化是按照从数据输入引脚的最低位到最高的顺序进行的(即D1 输入引脚上的数据传输到OQ 引脚的首位)。

OSERDES 使用CLK 和CLKDIV 两个时钟进行数据速率转换。CLK 是高速串行时钟;CLKDIV 是分频并行时钟。

图5-35 OSERDES的结构框图

三态并串转换。

除了数据的并串转换,OSERDES模块还包含一个三态并串转换器,三态并串转换器最多只能串行化四位并行三态信号。三态转换器不能级联。

OSERDES的原语如图5-36所示。

图5-36 OSERDES的原语

一、外文资料译文: Cyclone II器件系列简介 关键词:cyclone II器件;特点;简介; 在非常成功的第一代Cyclone器件系列之后,Altera的Cyclone II FPGA系列扩大低成本的FPGA的密度,最多达68,416个逻辑单元(LE),提供622个可用的输入/输出引脚和1.1M比特的嵌入式寄存器。Cyclone II器件的制造基于300毫米晶圆,采用台积电90nm、低K值电介质工艺,这种工艺技术是使用低绝缘体过程以确保了快速有效性和低成本。通过使硅片面积最小化,Cyclone II器件可以在单芯片上支持复杂的数字系统,而在成本上则可以和ASIC竞争。不像其他用电力功耗和性能来换取低成本的FPGA卖主,Altera 最新一代低价位的FPGA——cyclone II FPGA系列,和同类90nmFPGA器件相比,它提高了百分之六十的性能和降低了一半的功耗。低成本和优化特征使Cyclone II FPGA系列为各种各样的汽车、消费、通讯、视频处理、测试与测量、和其他最终市场提供理想的解决方案。在https://www.doczj.com/doc/0813547152.html,参考设计、系统图,和IP,使用cyclone II FPGA系列可以帮助你迅速实现最总市场方案开发。 低成本的嵌入式解决方案 Cyclone II 器件支持Nio s II 嵌入式处理器,能够自己完成自定义的嵌入式处理器。Cyclone II器件还能够扩展各种外部存储器和I/O口或者嵌入式处理器的性能。单个或多个NiosII嵌入式系统中嵌入式处理器也可以设计成cyclone II设备以提供一些额外的同时处理的能力或者甚至取代已经在你的系统中存在的嵌入式处理器。使用cyclone II和nios II 能够拥有成本低和高性能处理方案的共同特点,和普通的产品相比,这个特点能够延长你的产品的生命周期,提高产品进入市场的时间。 低成本DSP方案 单独使用cycloneII FPGA 系列或者或者作为数字信号处理(DSP)协处理器以提高数字信号处理(DSP)应用的性价比。,你用以下cyclone II的特点和设计支持可以实现高性能低成本DSP系统: ■150个18 × 18 乘法器 ■ 1.1 M比特的片内嵌入式存储器 ■高速的外部寄存器接口 ■数据处理的知识产权核

元器件封装及基本管脚定义说明 以下收录说明的元件为常规元件 A: 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。包括了实际元件的外型尺寸,所占空间位置,各管脚之间的间距等,是纯粹的空间概念。因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装. 普通的元件封装有针脚式封装(DIP与表面贴片式封装(SMD两大类. (像电阻,有传统的针脚式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD )这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD 元件放上,即可焊接在电路板上了。 元件按电气性能分类为:电阻, 电容(有极性, 无极性, 电感, 晶体管(二极管, 三极管, 集成电路IC, 端口(输入输出端口, 连接器, 插槽, 开关系列, 晶振,OTHER(显示器件, 蜂鸣器, 传感器, 扬声器, 受话器 1. 电阻: I.直插式 [1/20W 1/16W 1/10W 1/8W 1/4W] AXIAL0.3 0.4 II. 贴片式 [0201 0402 0603 0805 1206] 贴片电阻 0603表示的是封装尺寸与具体阻值没有关系 但封装尺寸与功率有关通常来说 0201 1/20W 0402 1/16W 0603 1/10W

0805 1/8W 1206 1/4W 电容电阻外形尺寸与封装的对应关系是: 0402=1.0x0.5 0603=1.6x0.8 0805=2.0x1.2 1206=3.2x1.6 1210=3.2x2.5 1812=4.5x3.2 2225=5.6x6.5 III. 整合式 [0402 0603 4合一或8合一排阻] IIII. 可调式[VR1~VR5] 2. 电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225] II. 有极性电容分两种: 电解电容 [一般为铝电解电容, 分为DIP 与SMD 两种] 钽电容 [为SMD 型: A TYPE (3216 10V B TYPE (3528 16V C TYPE (6032 25V D TYP E (7343 35V] 3. 电感: I.DIP型电感 II.SMD 型电感

XilinxFPGA引脚功能详细介绍 注:技术交流用,希望对大家有所帮助。 IO_LXXY_# 用户IO引脚 XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号 2.IO_LXXY_ZZZ_# 多功能引脚 ZZZ代表在用户IO的基本上添加一个或多个以下功能。 Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。配置完成后,这些引脚又作为普通用户引脚。 D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。 D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。 An:O,A[25:0]为BPI模式的地址位。配置完成后,变为用户I/O口。 AW AKE:O,电源保存挂起模式的状态输出引脚。SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。除非SUSPEND模式被使能,AWAKE被用作用户I/O。 MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。 FCS_B:O,BPI flash 的片选信号。 FOE_B:O,BPI flash的输出使能信号 FWE_B:O,BPI flash 的写使用信号 LDC:O,BPI模式配置期间为低电平 HDC:O,BPI模式配置期间为高电平 CSO_B:O,在并口模式下,工具链片选信号。在SPI模式下,为SPI flsah片选信号。 IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。 DOUT_BUSY:O,在SelectMAP模式下,BUSY表示设备状态;在位串口模式下,DOUT 提供配置数据流。 RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平有效的写使能信号;配置完成后,如果需要,RDWR_B可以在BANK2中做为Vref。 HSW APEN:I,在配置之后和配置过程中,低电平使用上拉。 INIT_B:双向,开漏,低电平表示配置内存已经被清理;保持低电平,配置被延迟;在配置过程中,低电平表示配置数据错误已经发生;配置完成后,可以用来指示POST_CRC 状态。 SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性。 CMPMOSI,CMPMISO,CMPCLK:N/A,保留。 M0,M1:I,配置模式选择。M0=并口(0)或者串口(1),M1=主机(0)或者从机(1)。 CCLK:I/O,配置时钟,主模式下输出,从模式下输入。 USERCCLK:I,主模式下,可行用户配置时钟。 GCLK:I,这些引脚连接到全局时钟缓存器,在不需要时钟的时候,这些引脚可以作为常规用户引脚。 VREF_#:N/A,这些是输入临界电压引脚。当外部的临界电压不必要时,他可以作为

Cyclone III 的配置 全文翻译自Altera公司Cyclone III的器件手册。 所有表格与图标标号与手册原文一致,以便于查对。 出于个人需要,仅翻译了AS与JTAG配置两部分,且仅都配置一片FPGA芯片。

可以通过压缩数据的方法以节约存储空间,并节省程序load时间(page 220); 9通过Remote System Upgrade方式可以减少新产品面市的时间(page 221); 9AS Configuration(Serial Configuration Devices) ?表10-6显示的是对各种配置电平来说,MSELx管脚的接法 ?单一器件配置 四个接口管脚包含了串口时钟(DCLK),串行数据输出(DATA),AS 数据输入(ASDI),以及低电平有效的片选信号(nCS)。 注: 1)上拉一个电阻,连接到该管脚所在的bank的VCCIO; 2)Cyclone III器件通过DATA[1]-to-ASDI路径控制配置芯片; 3)nCEO管脚浮空,或者当没有连接到另一个器件的nCE管脚时,可以当作通用IO使用; 4)MSEL管脚的设置,用于选择不同的电平标准和不同的POR时间;参考表10-6,选择

接法; 5)这些是复用管脚。FLASH_nCE管脚在AS配置电路图中当作nCSO功能使用,DATA[1] 管脚当作ASDO功能使用; 6)这些串接的电阻尽可能靠近配置芯片 当连接一个配置芯片到Cyclone III器件时,DATA[0]管脚必须串一个电阻,并应接近配置芯片。 配置器件和Cyclone III芯片间连线的长度应符合表10-8所推荐的值。 当选择AS配置方式的时候,BAMK 1的IO电压必须是3.3,3.0或2.5。 上电以后,CIII器件有一个POR时间的延迟,在此期间,nSTATUS和CONF_DONE 会一直为低,所有的IO也都是三态输出。 芯片配置的三个阶段分别是复位,配置和初始化。当nCONFIG或者nSTATUS为低,芯片处于复位状态,经过POR时间后,CIII释放nSTATUS,进入配置模式。(为开始配置,所有配置管脚和JTAG管脚所在的BANK的VCCINT,VCCA和VCCIO必须成功上电)。 CIII器件生成的串口时钟(DCLK)控制整个配置周期并为串口提供时序。CIII利用每步40MHz的晶振生成DCLK。 在AS配置模式下,配置芯片在DCLK的上升沿锁存输入和控制信号,并在下降沿送出数据;而CIII会在DCLK的下降沿发出控制信号并在DCLK的下降沿锁存配置数据。 CIII接收完所有的配置信息后,释放开环输出的CONF_DONE。只有当CONF_DONE 变成高电平时,CIII才开始初始化。 如果在配置期间出现了错误,CIII会将nSTATUS信号拉低,表示有一个数据帧错误,CONF_DONE信号保持为低。如果Auto-restart configuration after error 选项选中的话,CIII 会复位配置信号,通过向FLASH_NCE发一个脉冲,经过复位时间后释放nSTATUS的状态(最大230us)。

Cyclone? III Device Schematic Review Worksheet This document is intended to help you review your schematic and compare the pin usage against the Cyclone III Device Family Pin Connection Guidelines (PDF) version 1.1 and other referenced literature for this device family. The technical content is divided into focus areas such as FPGA power supplies, configuration, FPGA I/O, and external memory interfaces. Within each focus area, there is a table that contains the voltage or pin name for all of the dedicated and dual purpose pins for the device family. In some cases, the device density and package combination may not include some of the pins shown in this worksheet, you should cross reference with the pin-out file for your specific device. Links to the device pin-out files are provided at the top of each section. Before you begin using this worksheet to review your schematic and commit to board layout, Altera highly recommends: 1) Review the latest version of the Cyclone III Device Errata Sheet (PDF) and the Knowledge Database for Cyclone III Device Known Issues and Cyclone III Device Handbook Known Issues. 2) Compile your design in the Quartus? II software to completion. For example, there are many I/O related placement restrictions and VCCIO requirements for the I/O standards used in the device. If you do not have a complete project, then at a minimum a top level project should be used with all I/O pins defined, placed, and apply all of the configurable options that you plan to use. All I/O related megafunctions should also be included in the minimal project, including, but not limited to, external memory interfaces, PLLs, altlvds, and altddio. The I/O Analysis tool in the Pin Planner can then be used on the minimal project to validate the pinout in Quartus II software to assure there are no conflicts with the device rules and guidelines. When using the I/O Analysis tool you must ensure there are no errors with your pinout. Additionally, you should check all warning and critical warning messages to evaluate their impact on your design. You can right click your mouse over any warning or critical warning message and select “Help”. This will bring open a new H elp window with further information on the cause of the warning, and the action that is required.

A、常用芯片封装介绍 来源:互联网作者: 关键字:芯片封装 1、BGA 封装(ball grid array) 球形触点陈列,表面贴装型封装之一。在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配 LSI 芯片,然后用模压树脂或灌封方法进行密封。也称为凸点陈列载体(PAC)。引脚可超过200,是多引脚 LSI 用的一种封装。封装本体也可做得比 QFP(四侧引脚扁平封装)小。例如,引脚中心距为 1.5mm 的360 引脚 BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚 QFP 为 40mm 见方。而且 BGA 不用担心 QFP 那样的引脚变形问题。该封装是美国 Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。最初,BGA 的引脚(凸点)中心距为 1.5mm,引脚数为225。现在也有一些 LSI 厂家正在开发500 引脚的 BGA。 BGA 的问题是回流焊后的外观检查。 现在尚不清楚是否有效的外观检查方法。有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。美国 Motorola 公司把用模压树脂密封的封装称为 OMPAC,而把灌封方法密封的封装称为 GPAC(见 OMPAC 和 GPAC)。 2、BQFP 封装(quad flat package with bumper) 带缓冲垫的四侧引脚扁平封装。QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。美国半导体厂家主要在微处理器和 ASIC 等电路中采用此封装。引脚中心距0.635mm,引脚数从84 到196 左右(见 QFP)。

5.1.6 SelectIO模块 Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。 图5-24 I/O 片结构图 本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。 (1) SelectIO 的电气特性。 (2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。 (3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。 一、SelectIO IO 的电气特性 所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。支持单端I/O 标准(LVCMOS、 HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。 注意:差分输入和VREF 相关输入由VCCAUX 供电。 IOB、引脚及部逻辑的连接如图5-25 所示。 图5-25 IOB、引脚及部逻辑连接图 IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O 标准。与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。 二、SelectIO的逻辑资源 SelectIO的逻辑资源主要是指ILOGIC和OLOGIC资源,它们完成了FPGA引脚到部逻辑的连接功能,包括组合输入/输出、三态输出控制、寄存器输入/输出、寄存器三态输出控制、DDR输入/输出、DDR输出三态控制、IODELAYE1高分辨率可调整延迟单元及其控制模块。 下面简要介绍ILOGIC和OLOGIC功能。

Cyclone II 系列FPGA特殊引脚 (2009-07-26 12:17:20) 转载 分类:FPGA 标签: fpga管脚 杂谈 直接开始啦~~ 1/1.I/O, ASDO 在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。在AS 模式下,这个脚是CII 向串行配置芯片发送控制信号的脚。也是用来从配置芯片中读配置数据的脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。ASDO 脚直接接到配置芯片的ASDI 脚(第5 脚)。 2/2.I/O,nCSO 在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用.在AS 模式下,这个脚是CII 用来给外面的串行配置芯片发送的使能脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。这个脚是低电平有效的。直接接到配置芯片的/CS 脚(第1 脚)。 3/3.I/O,CRC_ERROR 当错误检测CRC 电路被选用时,这个脚就被作为CRC_ERROR 脚,如果不用默认就用来做I/O。但要注意,这个脚是不支持漏极开路和反向的。当它作为CRC_ERROR 时,高电平输出则表示出现了CRC 校验错误(在配置SRAM 各个比特时出现了错误)。CRC 电路

的支持可以在setting 中加上。这个脚一般与nCONFIG 脚配合起来用。即如果配置过程出错,重新配置. 4/4.I/O,CLKUSR 当在软件中打开Enable User-supplled start-up clock(CLKUSR)选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。在所有配置数据都已经被接收后,CONF_DONE 脚会变成高电平,CII 器件还需要299 个时钟周期来初始化寄存器,I/O 等等状态,FPGA 有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR 接进来的时钟(最大不能超过100MHz)。有这个功能,可以延缓FPGA 开始工作的时间,可以在需要和其它器件进行同步的特殊应用中用到。 7/13.I/O,VREF 用来给某些差分标准提供一个参考电平。没有用到的话,可以当成I/O 来用。 14/20. DATA0 专用输入脚。在AS 模式下,配置的过程是:CII 将nCSO 置低电平,配置芯片被使能。CII然后通过DCLK 和ASDO 配合操作,发送操作的命令,以及读的地址给配置芯片。配置芯片然后通过DATA 脚给CII 发送数据。DATA 脚就接到CII 的DATA0 脚上。CII 接收完所有的配置数据后,就会释放CONF_DONE 脚(即不强制使CONF_DONE 脚为低电平),CONF_DONE 脚是漏极开路(Open-Drain)的。这时候,因为CONF_DONE 在外部会接一个10K 的电阻,所以它会变成高电平。同时,CII 就停止DCLK 信号。在 CONF_DONE 变成高电平以后(这时它又相当于变成一个输入脚),初始化的过程就开始了。所以,CONF_DONE 这个脚外面一定要接一个10K 的电阻,以保证初始化过程可以正确开始。DATA0,DCLK,NCSO,ASDO 脚上都有微弱的上拉电阻,且一直有效。在配置完

LED 显示屏中常用的芯片说明及原理 Led中常见的芯片有:74HC595列驱动,74HC138译码驱动,74HC245信号放大,74HC4953行扫描等。 1、74HC595 74HC595是硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。 74HC595 是具有8位移位寄存器和一个存储器,三态输出功能。移位寄存器和存储器是分别的时钟。数据在SHcp(移位寄存器时钟输入)的上升沿输入到移位寄存器中,在STcp(存储器时钟输入)的上升沿输入到存储寄存器中去。如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。 8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。三态。 将串行输入的8位数字,转变为并行输出的8位数字,例如控制一个8位数码管,将不会有闪烁。 2特点 8位串行输入 /8位串行或并行输出存储状态寄存器,三种状态

输出寄存器(三态输出:就是具有高电平、低电平和高阻抗三种输出状态的门电路。)可以直接清除 100MHz的移位频率 特点8位串行输入 /8位串行或并行输出存储状态寄存器,三种状态 输出寄存器(三态输出:就是具有高电平、低电平和高阻抗三种输出状态的门电路。)可以直接清除 100MHz的移位频率 3输出能力并行输出,总线驱动;串行输出;标准中等规模集成电路 595移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。 参考数据 Cpd决定动态的能耗, Pd=Cpd×VCC×f1+∑(CL×VCC^2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压 4、引脚说明符号引脚描述 Q0…Q7 8位并行数据输出,其中Q0为第15脚 GND 第8脚地 Q7’第9脚串行数据输出 MR 第10脚主复位(低电平) SHCP 第11脚移位寄存器时钟输入 STCP 第12脚存储寄存器时钟输入 OE 第13脚输出有效(低电平) DS 第14脚串行数据输入 VCC 第16脚电源

Spartan-3E Starter Kit Board User Guide

Chapter 1: Introduction and Overview Chapter 2: Switches, Buttons, and Knob Chapter 3: Clock Sources Chapter 4: FPGA Configuration Options Chapter 5: Character LCD Screen Chapter 6: VGA Display Port Chapter 7: RS-232 Serial Ports Chapter 8: PS/2 Mouse/Keyboard Port Chapter 9: Digital to Analog Converter (DAC) Chapter 10: Analog Capture Circuit Chapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial Flash Chapter 13: DDR SDRAM Chapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion Connectors Chapter 16: XC2C64A CoolRunner-II CPLD Chapter 17: DS2432 1-Wire SHA-1 EEPROM

Chapter 1:Introduction and Overview Spartan-3E 入门实验板使设计人员能够即时利用Spartan-3E 系列的完整平台性能。 设备支持设备支持::Spartan-3E 、CoolRunner-II 关键特性关键特性::Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner?-II (XC2C64A-5VQ44C)与Platform Flash (XCF04S-VO20C) 时钟时钟::50 MHz 晶体时钟振荡器 存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM 连接器与接口: 以太网10/100 Phy, JTAG USB 下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED 输出, 四个瞬时接触按钮, 100管脚hirose 扩展连接端口与三个6管脚扩展连接器 显示器: VGA 显示端口,16 字符- 2 线式 LCD 电源电源::Linear Technologies 电源供电,TPS75003三路电源管理IC 市场: 消费类, 电信/数据通信, 服务器, 存储器 应用: 可支持32位的RISC 处理器,可以采用Xilinx 的MicroBlaze 以及PicoBlaze 嵌入式开发系统;支持DDR 接口的应用;支持基于Ethernet 网络的应用;支持大容量I/O 扩展的应用。 Choose the Starter Kit Board for Your Needs Spartan-3E FPGA Features and Embedded Processing Functions Spartan3-E FPGA 入门实验板具有Spartan3-E FPGA 系列突出独特的特点和为嵌入式处理发展与应用提供了很大的方便。该板的特点如下: Spartan3-E 特有的特征:并行NOR Flash 配置;通过并行NOR Flash PROM 实现FPGA 的多种配置方式 嵌入式系统:MicroBlaze? 32-bit 嵌入RISC 处理器;PicoBlaze? 8-bit 嵌入控制器;DDR 存储器接口 Learning Xilinx FPGA, CPLD, and ISE Development Software Basics Spartan3-E FPGA 入门实验板比其他的入门实验板先进、复杂。它是学习FPGA 或CPLD 设计和怎样运用ISE 软件的基础。 Advanced Spartan-3 Generation Development Boards 入门实验板示范了MicroBlaze? 32-bit 嵌入式处理器和EDK 的基本运用。其更先进的地方

EP2C5T144C8N/EP2C5Q208C8N 1/1. I/O, ASDO: 在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。在AS 模式下,这个脚是CII 向串行配置芯片发送控制信号的脚。也是用来从配置芯片中读配置数据的脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。ASDO 脚直接接到配置芯片的ASDI 脚(第5 脚)。 2/2. I/O,nCSO: 在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用.在AS 模式下,这个脚是CII 用来给外面的串行配置芯片发送的使能脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。这个脚是低电平有效的。直接接到配置芯片的/CS 脚(第1 脚)。 3/3. I/O,CRC_ERROR: 当错误检测CRC 电路被选用时,这个脚就被作为CRC_ERROR 脚,如果不用默认就用来做I/O。但要注意,这个脚是不支持漏极开路和反向的。当它作为CRC_ERROR 时,高电平输出则表示出现了CRC 校验错误(在配置SRAM 各个比特时出现了错误)。CRC 电路的支持可以在setting 中加上。这个脚一般与nCONFIG 脚配合起来用。即如果配置过程出错,重新配置。 4/4. I/O,CLKUSR: 当在软件中打开Enable User-supplled start-up clock(CLKUSR)选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。在所有配置数据都已经被接收后,CONF_DONE 脚会变成高电平,CII 器件还需要299 个时钟周期来初始化寄存器,I/O 等等状态,FPGA有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR 接进来的时钟(最大不能超过100MHz)。有这个功能,可以延缓FPGA 开始工作的时间,可以在需要和其它器件进行同步的特殊应用中用到。

Xilinx FPGA配置的一些细节 2010年07月03日星期六 14:26 0 参考资料 (1) Xilinx: Development System Reference Guide. dev.pdf, v10.1 在Xilinx的doc目录下有。 (2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005 在Xilinx网站上有,链接 (3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007 在Xilinx网站上有,链接 注:此外xapp139和xapp151也是和配置相关的。 (4)Xilinx: Virtex-4 Configuration Guide. UG071 (v1.5) January 12, 2007 (5) Tell me about the .BIT . 链接: 1 Xilinx配置过程 主要讲一下Startup Sequence。 Startup Sequence由8个状态组成. 除了7是固定的之外,其它几个的顺序是用户可设置的,而且Wait for DCM和DCI是可选的。 其中默认顺序如下: 这些在ISE生成bit文件时通过属性页设定。 这几个状态的具体含义如下: Release_DONE : DONE信号变高 GWE : 使能CLB和IOB,FPGA的RAMs和FFs可以改变状态 GTS : 激活用户IO,之前都是高阻。

ETL-002 Altera Cyclone III 系列FPGA开发板简介 概述 ETL-002 FPGA开发板是以Altera公司的最新系列Cyclone III中的3C10为主芯片,并提供了极为丰富的芯片外围接口资源以及下载线,数据线以及资料光盘等。除了这些硬件外,我们还提供了十多个接口实验,并公开了电路原理图和实验的Verilog源代码,以便于大家对照学习,并可以在该开发板上进行二次开发。

单板描述 主芯片EP3C10提供了10320个逻辑单元(LE),46块SRAM(每块9K bits), 23个18*18的乘法器。开发板自带USB供电电路:您只需将USB线插上您的USB端口,无需外接+5V直流电源,开发板即可工作。开发板同时支持AS模式下载和JTAG模式下载。程序固化既可通过JTAG口也可直接对板上的FLASH进行编程。 丰富的外围接口可满足常用的外设的人机交互,我们还将剩下未用的40个用户I/O引脚全部引出,使得您可以通过这些信号对本开发板进行电路扩展。这些接口主要包括: PS2鼠标接口:可以将PS2鼠标的任何移动的信息反应在数码管上 PS2键盘接口:可以将PS2键盘上的任意按键以16进制的信息反应在数码管上 VGA显示器接口:可以将FPGA产生的信息反映在VGA显示器上。开发板自带了动态彩条显示的功能 双串口接口:可以与任何的串口设备相接。开发板自带的演示程序是将PC上的超级终端中输入的任何信息返回PC 4位数码管:可以实时显示任何的数字信息。开发板自带的演示程序实时地显示分钟和秒钟的信息。 4位LED灯:用于指示状态。开发板自带了跑马灯实验。 4位按键开关:可用于复位等作用。 4位拨码开关:可用于电路的选择作用

. . 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

. . 74LS30 数据手册 74LS32数据手册 74LS33 数据手册 74LS37 数据手册 74LS38数据手册 74LS40 数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电平而试灯 输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。

cyclone3的配置方式 cyclone3器件使用SRAM单元保存配置信息。因为SRAM掉电易失的特性,fpga芯片上电的时候必须重新配置。根据期间密度和封装选择,它有如下5中配置方案(红色部分为常用配置方案,并不是所有FPGA芯片都能使用所有配置方案,具体可查看cyclone3的器件手册): 1.Active serial (AS)主动串行配置 2.Active parallel (AP)主动并行配置 3.Passive serial (PS)被动串行配置 4.Fast passive parallel (FPP)快速被动并行配置 5.Joint Test Action Group (JTAG) AS和AP配置方案需要外部FLASH存储器存储配置信息。其它3种配置方案需要外部的控制器或者下载电缆。主动配置方案以及JTAG方案常用于单芯片系统设计。下面重点介绍AS,AP和JTAG。以AS配置为例介绍。 Cyclone3器件的配置芯片通常选择EPCS64,EPCS16以及EPCS4或者flash.这些芯片能够提供廉价,方便(引脚少)的解决方案。因为FPGA芯片容量的限制,它对配置信息的大小也有所限制。EP3C80系列器件可提供21MBITS的配置信息流容量。 MSEL【3:0】为FPGA器件的输入,用于确定配置方式。AS模式下,它连接1101.AP模式下,它连接1011.注意要直接接 VCCA or GND,

更不能悬空,避免无效配置。查看手册可得到其它配置值。在JTAG 模式下,忽略MSEL配置,JTAG模式有优先权。 AS模式支持配置信息压缩,AP模式不支持。压缩信息可以节约空间以及配置时间。在 Device & Pin Options——Configuration中可以选择压缩与否。 选择好器件后,参考下图连接。 POR——上电复位.复位时间由MSEL【3:0】决定。复位结束后开始发送配置控制信号。 DCLK信号由fpga内部晶振产生。Cyclone3系列器件使用40Mhz时钟晶振。在此时钟上升沿,输入控制信号,下降沿输出配置信息。配置时间由配置信息流的大小和时钟频率决定。配置过程大概如下:复位

Cyclone III原型开发调试 转载:https://www.doczj.com/doc/0813547152.html,/ilove314/1819329/Message.aspx 最近设计的Cyclone III原型板是特权同学第一次接触Cyclone III的器件。原理图、PCB绘制、管脚分配上都碰到了一些问题,这些问题或多或少都是由于个人对新器件不熟悉、设计的时候有一些粗心大意造成的。主要针对板级的硬件设计,这里凌乱的罗列一下,做一点总结,今后要多吸取教训,低级的失误要尽量避免。 1. 首先要提一个没有解决的问题,EP3C5E144/EP3C10E144/ EP3C16E144/ EP3C 25E144(是管脚完全兼容的不同资源的器件,Altera在这一点上是非常值得称道的)器件的PIIN11和PIN12存在不可同时使用的问题,这个问题出现在架构了一个NIOS2系统里集成了EPCS控制器的时候,在Cyclone II中是不需要分配这个EPCS控制器的管脚的(内部自动映射),而Cyclone III则需要手动分配(事先需要到Setting里动动手脚)。EPCS的DCLK需要分配到PIN12上,工程中分配了一个SDRAM的D0脚给PIN11,编译到Fitting阶段就Error了。在handbook里海找没什么成效,求助于搜索引擎,最终看到有人遇到相同的问题,但是给出的却是不是办法的解决办法:不用PIN11或者不用PI N12。这个问题上特权同学也很是无可奈何,估计是Cyclone III器件的这两个脚做了一些信号耦合之类的检查,也不知道是否在工具选项里做一些设置可以取消此类检查。也很期待有相同遭遇的朋友现身说法,告诉特权如何解决问题。 2. 再说两个很低级的错误,错的很傻,没有什么技术含量,只能给自己敲个警钟:干活的时候脑子一定要清醒。两个错误分别和BOM表和网络标号有关。先说和BOM表有关的,这个错误源于原理图上两个三端稳压器-1.2和-2.5的标示刚好反过来了,因为管脚定义和封装都一样所以也没留意,好在最后只影响BOM表的标示,但这也导致了第一块样板焊接的时候出现了1.2V和2.5V互换位置的惨剧,结果可想而知,EP3C10E144C7就这样挂了,非常的心疼。另一个失误有点让人啼笑皆非,特权同学做板子一般都习惯加个LED灯到闲置端口,FPGA初始调试的第一件事就是让他闪起来,平时工作的时候也习惯让LED 闪烁着作为工作运行的指示。绘制原理图的时候直接copy了以前的一份图纸,没有注意网络标号,结果这个LED的GND和系统通用的DGND根本没有连上,最终调试的时候居然怀疑Cyclone III的输出电流太小以致连个灯都要罢工。 3. Cyclone III的几档电压也是和之前系列器件有所区别,VCCIO不提了,主要根据用户需求设计;VCCINT是1.2V,和Cyclone II是一样的;特别需要留意的是PLL的供电部分,即VCCA和VCCD,VCCD与核压一样供1.2V没有问题,VCCA通常需要加一些推荐的去耦电路,它不是1.2V,必须供2.5V,这里特权同学也犯错了,好在两个VCCA 的电源入口都通过磁珠了,因此在发现问题后及时飞了两条线出来算是临时应急。还有JT AG电路的电压也和以往有别,这个地方下面一个点谈。 4. Cyclone III的标准JTAG推荐接口电压是2.5V,当然貌似3.3V的时候也能够下载,不过大家还是按照官方推荐的电压来工作,以免出现一些不必要的麻烦。