时序逻辑电路51时序逻辑电路的基本概念1时序逻辑电路

第5章时序逻辑电路

5.1 时序逻辑电路的基本概念

1.时序逻辑电路的结构及特点

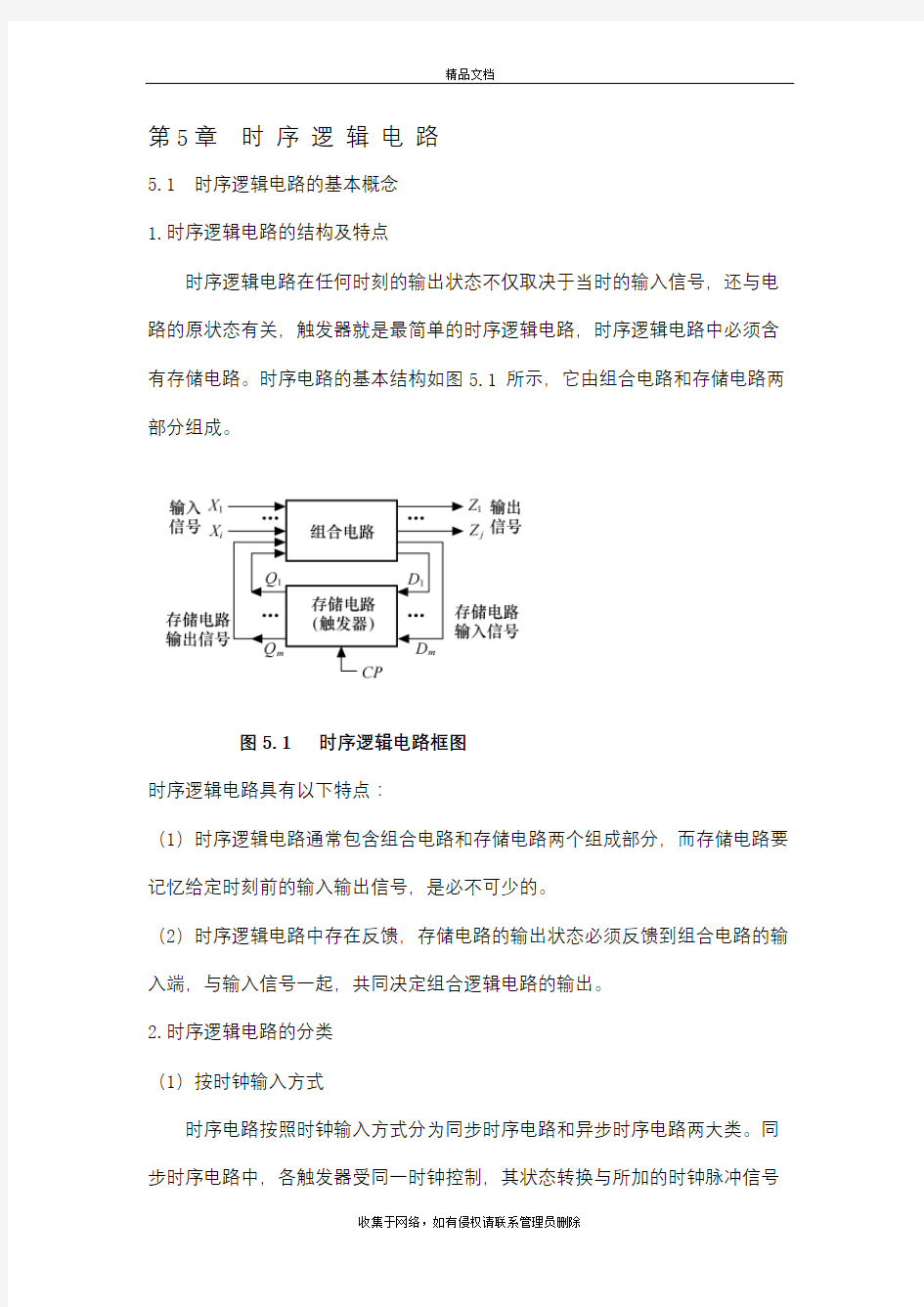

时序逻辑电路在任何时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关,触发器就是最简单的时序逻辑电路,时序逻辑电路中必须含有存储电路。时序电路的基本结构如图5.1 所示,它由组合电路和存储电路两部分组成。

图5.1 时序逻辑电路框图

时序逻辑电路具有以下特点:

(1)时序逻辑电路通常包含组合电路和存储电路两个组成部分,而存储电路要记忆给定时刻前的输入输出信号,是必不可少的。

(2)时序逻辑电路中存在反馈,存储电路的输出状态必须反馈到组合电路的输入端,与输入信号一起,共同决定组合逻辑电路的输出。

2.时序逻辑电路的分类

(1)按时钟输入方式

时序电路按照时钟输入方式分为同步时序电路和异步时序电路两大类。同步时序电路中,各触发器受同一时钟控制,其状态转换与所加的时钟脉冲信号

都是同步的;异步时序电路中,各触发器的时钟不同,电路状态的转换有先有后。同步时序电路较复杂,其速度高于异步时序电路。

(2)按输出信号的特点

根据输出信号的特点可将时序电路分为米里(Mealy)型和摩尔(Moore)型两类。米里型电路的外部输出Z既与触发器的状态Q n有关,又与外部输入X 有关。而摩尔型电路的外部输出Z仅与触发器的状态Q n有关,而与外部输入X 无关。

(3)按逻辑功能

时序逻辑电路按逻辑功能可划分为寄存器、锁存器、移位寄存器、计数器和节拍发生器等。

3.时序逻辑电路的逻辑功能描述方法

描述一个时序电路的逻辑功能可以采用逻辑方程组(驱动方程、输出方程、状态方程)、状态表、状态图、时序图等方法。这些方法可以相互转换,而且都是分析和设计时序电路的基本工具。

5.2 时序逻辑电路的分析方法和设计方法

1.时序逻辑电路的分析步骤

(1)首先确定是同步还是异步。若是异步,须写出各触发器的时钟方程。(2)写驱动方程。

(3)写状态方程(或次态方程)。

(4)写输出方程。若电路由外部输出,要写出这些输出的逻辑表达式,即输出方程。

(5)列状态表

(6)画状态图和时序图。

(7)检查电路能否自启动并说明其逻辑功能。

5.2.1 同步时序逻辑电路的设计方法

1.同步时序逻辑电路的设计步骤

设计同步时序电路的一般过程如图5.10所示。

图5.10 同步时序电路的设计过程

5.3 寄存器和锁存器

能够暂存数码(或指令代码)的数字部件称为寄存器。

寄存器根据功能可分为数码寄存器和移位寄存器两大类。

5.3.1 数码寄存器

寄存器要存放数码,必须要存得进、记得住、取得出。因此寄存器中除触发器外,通常还有一些控制作用的门电路相配合。

图5.17为由D触发器组成的4位数码寄存器。在存数指令(CP脉冲上升沿)的作用下,可将预先加在各D触发器输入端的数码,存入相应的触发器中,并可从各触发器的Q端同时输出,所以称其为并行输入、并行输出的寄存器。

图5.17 4位数码寄存器

数码寄存器的特点是:

(1)在存入新数码时能将寄存器中的原始数码自动清除,即只需要输入一个接收脉冲,就可将数码存入寄存器中——单拍接收方式的寄存器。

(2)在接收数码时,各位数码同时输入,而各位输出的数码也同时取出,即并行输入、并行输出的寄存器。

(3)在寄存数据之前,应在R D端输入负脉冲清零,使各触发器均清零。

5.3.2 移位寄存器

1.单向移位寄存器

由D触发器构成的4位右移寄存器如图5.18所示。CR为异步清零端。左边触发器的输出接至相邻右边触发器的输入端D,输入数据由最左边触发器FF0的输入端D0接入。

图5.18 D触发器组成的4位右移寄存器

除用D触发器外,也可用JK、RS触发器构成寄存器,只需将JK或RS触发器转换为D触发器功能即可。但T触发器不能用来构成移位寄存器。

图5.20 D触发器组成的4位双向左移寄存器

2.双向移位寄存器

双向移位寄存器电路结构如图5.20 所示,将右移寄存器和左移寄存器组合起来,并引入控制端S便构成既可左移又可右移的双向移位寄存器。

5.3.3 锁存器

1.锁存器原理

锁存器又称自锁电路,是用来暂存数码的逻辑部件,如图5.21 所示是一位锁存器逻辑电路图,它与触发器的区别是:当使能信号到来时,输出随输入数码变化(相当于输出直接接到输入端);当使能信号结束时,输出保持使能信号跳变时的状态不变。

图5.21 一位锁存器逻辑电路图

2.锁存器集成电路介绍

75 是4 位锁存器,它包括TTL系列中的54/7475 ,54/74LS75 和CMOS 系列中的54/74HC75、54/74HCT75 等。其外引脚排列图如图5.22 所示。

图5.22 4位锁存器75外引脚排列图

5.3.4 寄存器集成电路介绍

1.集成移位寄存器74194

集成移位寄存器74194如图5.23所示。

图5.23集成移位寄存器74194

2.集成移位寄存器的应用

移位寄存器除了具有寄存数码和将数码移位的功能外,还可以构成各种计数器和分频器。图5.24所示为4位右移寄存器构成的环形计数器。

图5.24 环形计数器

图5.25 环形计数器时序图

图5.26 用74194构成的环形计数器

图5.27 用74194构成的扭环形计数器

5.4 计数器

能累计输入脉冲个数的时序部件叫计数器。计数器不仅能用于计数,还可用于定时、分频和程序控制等。

计数器按计数进制可分为二进制计数器和非二进制计数器;按数字的增减趋势可分为加法计数器、减法计数器和可逆计数器;按计数器中各触发器翻转是否与计数脉冲同步可分为同步计数器和异步计数器。

5.4.1 二进制计数器

1.异步二进制计数器

以3 位二进制加法计数器为例,逻辑图如图5.28 所示。

图5.28 JK触发器构成的3位异步二进制加法计数器