模拟数字信号处理的相关性

Paul Hasler 和David V.Anderson

佐治亚州电子与计算机工程技术研究院, 亚特兰大市, GA30332 phasler@https://www.doczj.com/doc/0215276.html,, dva@https://www.doczj.com/doc/0215276.html,

摘要

我们介绍了模拟数字信号处理的相关性的定义和实时信号处理函数的含义.我们也讨论了模拟计算和数字计算电路中操作运算的平衡行问题,并且展示了模拟数字信号相关性处理系统的构架.该系统在模拟VLSI电路处理中的新特性使用采用可编程单元方法改进模拟信号处理系统成可能。

1.模拟数字信号处理相关性的定义

在最近和将来DSP的应用中, VLSI模拟电路的新特性得到了使用[1,2,3,4,5,6,7]。并且,模拟电路系统具有可编程性,可配置和良好的适应性,同时集成度可以和数学存储单元相比(例如,能将超过10万的加法器集成到单一芯片上)[8,9,10,11,5].通常,单一芯片不会同时具有模拟和可编程特性,模拟电路主要用在前置放大器中,而可编程器件专门用于数字处理域中。因此,我们必须清楚是否要具有数学和模拟信号处理两中特性,或者针对特殊用途选择专门的解决方案。本论文所关注的就是确定问题所在。本文章描述了一种创建模拟数字信号处理系统相关性方案。与简单将各部分拼接起来相对,该系统更能发挥各部分的优势。

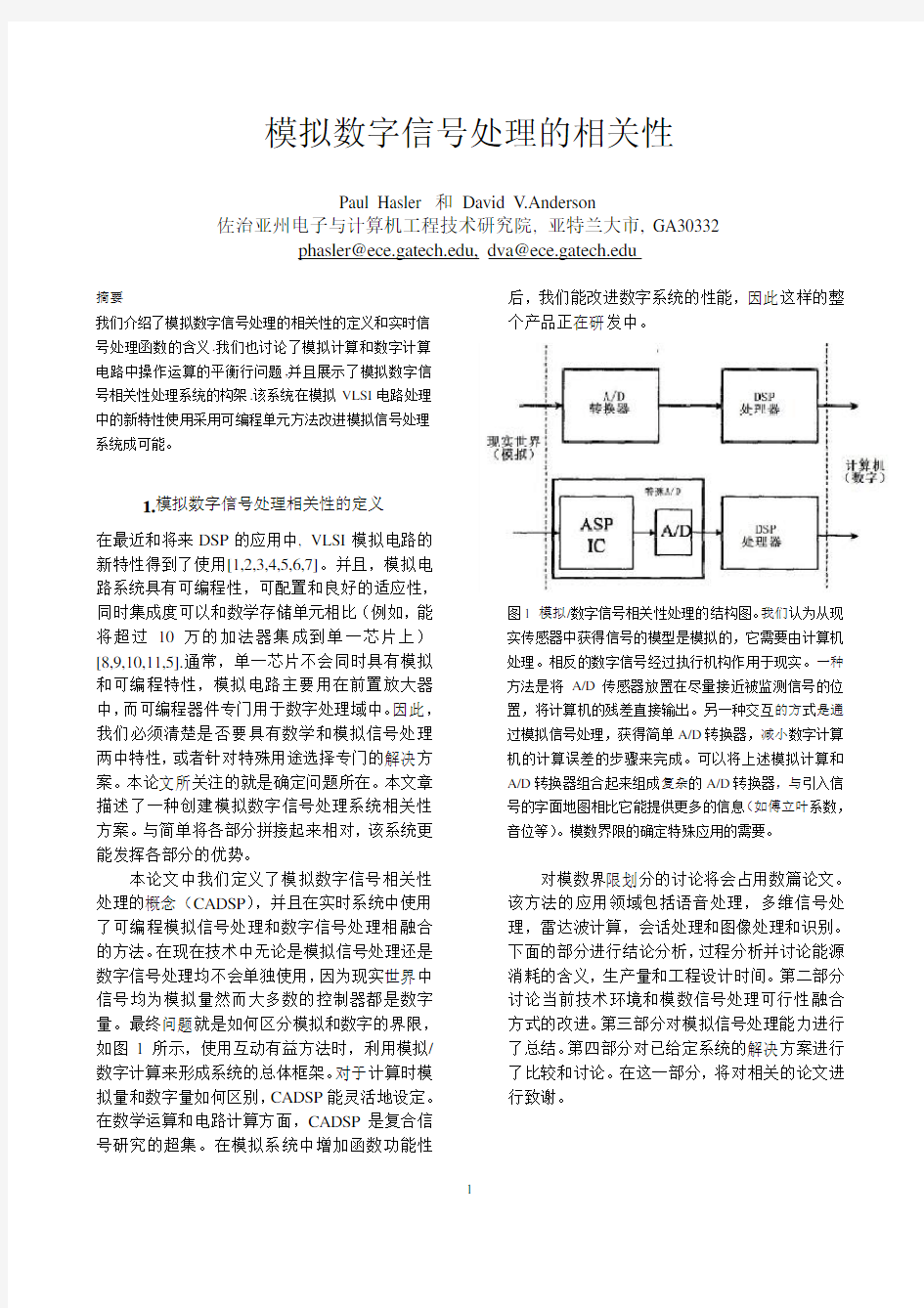

本论文中我们定义了模拟数字信号相关性处理的概念(CADSP),并且在实时系统中使用了可编程模拟信号处理和数字信号处理相融合的方法。在现在技术中无论是模拟信号处理还是数字信号处理均不会单独使用,因为现实世界中信号均为模拟量然而大多数的控制器都是数字量。最终问题就是如何区分模拟和数字的界限,如图1所示,使用互动有益方法时,利用模拟/数字计算来形成系统的总体框架。对于计算时模拟量和数字量如何区别,CADSP能灵活地设定。在数学运算和电路计算方面,CADSP是复合信号研究的超集。在模拟系统中增加函数功能性后,我们能改进数字系统的性能,因此这样的整个产品正在研发中。

图1 模拟/数字信号相关性处理的结构图。我们认为从现实传感器中获得信号的模型是模拟的,它需要由计算机处理。相反的数字信号经过执行机构作用于现实。一种方法是将A/D传感器放置在尽量接近被监测信号的位置,将计算机的残差直接输出。另一种交互的方式是通过模拟信号处理,获得简单A/D转换器,减小数字计算机的计算误差的步骤来完成。可以将上述模拟计算和A/D转换器组合起来组成复杂的A/D转换器,与引入信号的字面地图相比它能提供更多的信息(如傅立叶系数,音位等)。模数界限的确定特殊应用的需要。

对模数界限划分的讨论将会占用数篇论文。该方法的应用领域包括语音处理,多维信号处理,雷达波计算,会话处理和图像处理和识别。下面的部分进行结论分析,过程分析并讨论能源消耗的含义,生产量和工程设计时间。第二部分讨论当前技术环境和模数信号处理可行性融合方式的改进。第三部分对模拟信号处理能力进行了总结。第四部分对已给定系统的解决方案进行了比较和讨论。在这一部分,将对相关的论文进行致谢。

2.综合化模拟数字信号处理案例

可能有人会问为何要介绍模拟信号处理,因为图1的上半部分已经说明了实时信号处理的架构。它在实际中似乎运作得很好,首先经晶体管放大,然后由软件稳定。现在和以前的方法都是寻找一个新的策略来完成目的。另外,在DSP 上模拟VLSI能安静地使模拟信号处理完成。

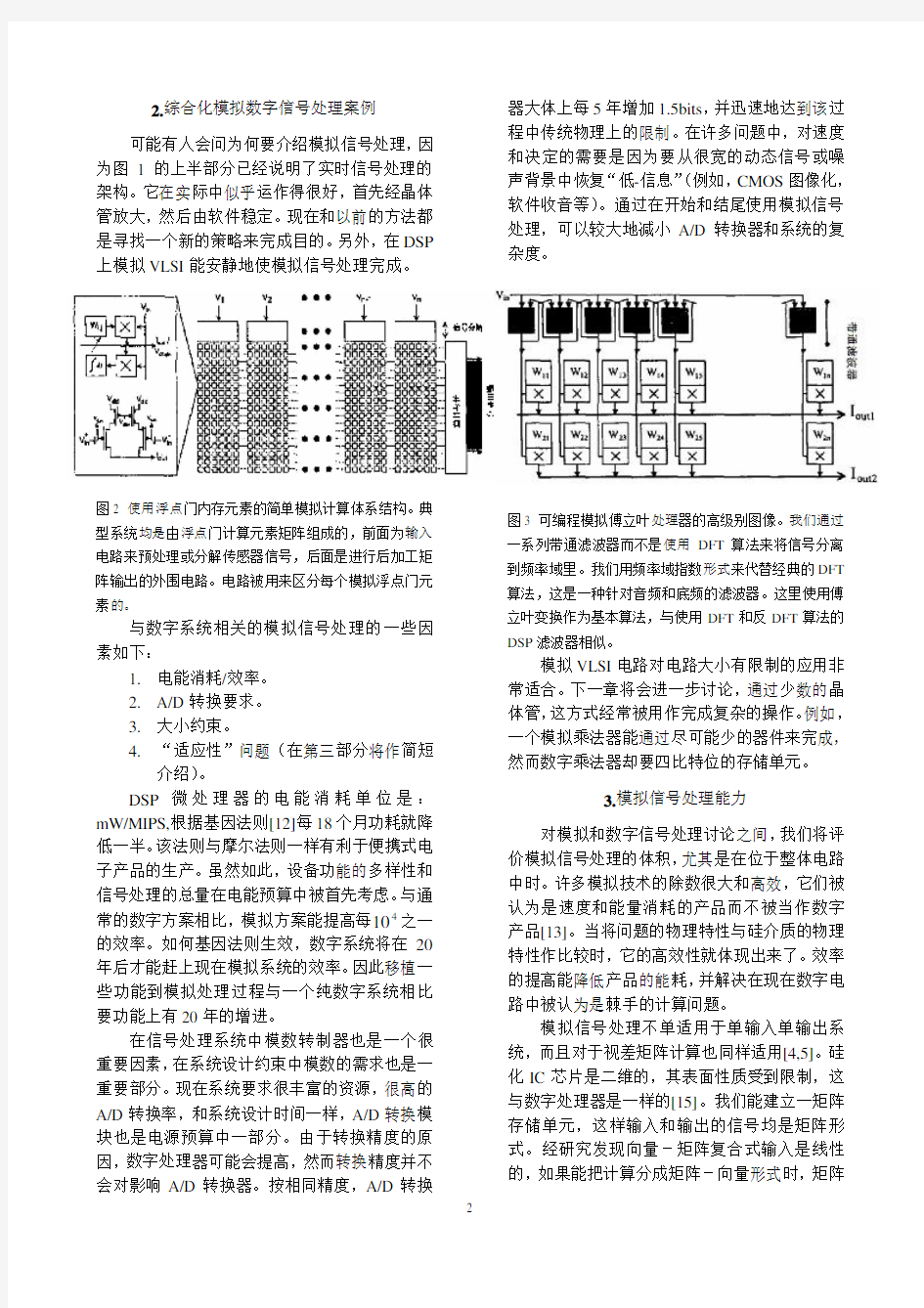

图2 使用浮点门内存元素的简单模拟计算体系结构。典型系统均是由浮点门计算元素矩阵组成的,前面为输入电路来预处理或分解传感器信号,后面是进行后加工矩阵输出的外围电路。电路被用来区分每个模拟浮点门元素的。

与数字系统相关的模拟信号处理的一些因素如下:

1.电能消耗/效率。

2.A/D转换要求。

3.大小约束。

4.“适应性”问题(在第三部分将作简短

介绍)。

DSP微处理器的电能消耗单位是:mW/MIPS,根据基因法则[12]每18个月功耗就降低一半。该法则与摩尔法则一样有利于便携式电子产品的生产。虽然如此,设备功能的多样性和信号处理的总量在电能预算中被首先考虑。与通常的数字方案相比,模拟方案能提高每4

10之一的效率。如何基因法则生效,数字系统将在20年后才能赶上现在模拟系统的效率。因此移植一些功能到模拟处理过程与一个纯数字系统相比要功能上有20年的增进。

在信号处理系统中模数转制器也是一个很重要因素,在系统设计约束中模数的需求也是一重要部分。现在系统要求很丰富的资源,很高的A/D转换率,和系统设计时间一样,A/D转换模块也是电源预算中一部分。由于转换精度的原因,数字处理器可能会提高,然而转换精度并不会对影响A/D转换器。按相同精度,A/D转换器大体上每5年增加1.5bits,并迅速地达到该过程中传统物理上的限制。在许多问题中,对速度和决定的需要是因为要从很宽的动态信号或噪声背景中恢复“低-信息”(例如,CMOS图像化,软件收音等)。通过在开始和结尾使用模拟信号处理,可以较大地减小A/D转换器和系统的复杂度。

图3 可编程模拟傅立叶处理器的高级别图像。我们通过一系列带通滤波器而不是使用DFT算法来将信号分离到频率域里。我们用频率域指数形式来代替经典的DFT 算法,这是一种针对音频和底频的滤波器。这里使用傅立叶变换作为基本算法,与使用DFT和反DFT算法的DSP滤波器相似。

模拟VLSI电路对电路大小有限制的应用非常适合。下一章将会进一步讨论,通过少数的晶体管,这方式经常被用作完成复杂的操作。例如,一个模拟乘法器能通过尽可能少的器件来完成,然而数字乘法器却要四比特位的存储单元。

3.模拟信号处理能力

对模拟和数字信号处理讨论之间,我们将评价模拟信号处理的体积,尤其是在位于整体电路中时。许多模拟技术的除数很大和高效,它们被认为是速度和能量消耗的产品而不被当作数字产品[13]。当将问题的物理特性与硅介质的物理特性作比较时,它的高效性就体现出来了。效率的提高能降低产品的能耗,并解决在现在数字电路中被认为是棘手的计算问题。

模拟信号处理不单适用于单输入单输出系统,而且对于视差矩阵计算也同样适用[4,5]。硅化IC芯片是二维的,其表面性质受到限制,这与数字处理器是一样的[15]。我们能建立一矩阵存储单元,这样输入和输出的信号均是矩阵形式。经研究发现向量-矩阵复合式输入是线性的,如果能把计算分成矩阵-向量形式时,矩阵

-矩阵的输入也是可行的。并且,我们发现矩阵的特征向量计算是很复杂的,但通过矩阵-向量复合计算方法,计算协方差矩阵的特征向量是较为容易的。

因为要处理的元素是信号内存元素的列向量方式,除了在单一列内存访问时,结果结构与数字内存结构相似,现在我们正对矩阵-向量乘法运算进行计算。与数字内存不同,第个单元均为乘法器,它能将存储于浮点门中的模拟量传递给另一个单元。通过在内存单元中自行地计算,可以突破大部分数字处理器中出现的输入输出瓶颈。通常地,这些内存计算单元允许私自访问(针对读出操作)或者在矩阵中使用全速差分访问(如矩阵乘法或适配器)。每个输入信号被获得时,每个内存就被访问,即当信号(最大频率输入)进入时系统就会运作;因此减少对整个系统的设计。

图4 针对不同方案(信号-噪声)的不同模拟数字信号处理方针。(a)在别的地方[16]数字计算的复杂程度与要解决方案的位数有关,同时,数字计算的成本与需解决问题的位数成指数关系。这是典型的8位与16位的区别,详细信息与实际应用有关。图(b)为针对SNR运算结果的实例和两个普通应用例子:第一个采用单纯的DSP解决方案,第二个采用了模数融合方案。最后每种方法都给出了每个输出通道下的信息结果。

系统结构确定以后,这些计算单元内存元素的体积和能耗标准将是很重要的,因为我们需要尽可能多的信息。该方法采用的技术是浮点门电路技术,此技术可对于单个或双个的EEPROM[9,17,18]单元进行调试、计算、和编程。图2所示为浮点门计算矩阵的框图。在标准数字CMOS处理器或者标准双CMOS处理器中该技术均适用。我们将其称为高密度模拟计算矩阵的计算内存行列(与计算矩阵有关)。该模拟计算矩阵对已存储或输入的信息均能处理。因为输入信号的相关性,每个单元均能处理,同时不会相互影响。因此,该矩阵在相同电路复杂度和电源能耗上提供了全差分计算,数字内存需要用4比特位精度来存储该矩阵(双转换器单元)。除此之外,这种方法还能将合并模拟信号处理模块加入到FPGA 和标准ASIC中去。

图3对片上可编程模拟滤波器概念作了大体上分析[5,19.,20]。每块均由两片组成,一片设计信号如何完成模拟功能,另一片负责对存储单元中数据作乘法运算。整个过程都是使用IFFT 通过FFT在每次采样,称重和输出结果时生成滤波器。输出是一个能产生普通相互关联的电流。电压带通滤波器将输入信号分割成时域上的基本函数。通过对滤波器中浮点门元素进行编程,拐角频率能划分到音频到MHz之内的任意域(例如线性或指数域)。通过单个处理器我们能输出原始信号的版本号。

4.信号到噪声的消耗

即使模拟信号处理能完成不同重要的功能,并且为可编程的,但问题是这些计算系统的效率如何。在特别的方案中相关能确定计算的成本。图4展示了典型信号到噪声方案的网状消耗[16]。当对区域计算,能源消耗,计算掩饰,设计和加工费用作研究时会得出相似结果。数字计算的费用与具体方案的位数有关,呈现非线性状态,而是与其位数呈指数关系。因此,需要较少

答案而不是瓶颈的模拟计算效率低,需要较少答案而不是瓶颈的方法不如数字计算方法。Sarpeskar[16]的详细研究表明,当系统信息阶数不是很高,低于10时,模拟计算有很强的优势。但在许多实时信号处理传感器或控制器方面,模拟执行器的定义还存在争议。数字格式的两种类型是,模拟计算电路表现动浮点系统尽管实际系统是定浮点系统。

无论是在模拟还是数字信号处理部分中,关键因素很大程序上依赖于信息总量和需要重现的量。图4b显示了一个应用该结果的例子。对后来传感器数据处理的关键步骤是使用FFT和傅立叶变换。对于DSP处理器,我们需要一个16位的模数转换器来得到10比特的输出。模拟系统设计有相同的复杂度,因为16位模数转换器比10位设计的复杂度是以指数级增长的。对于工程师来说算法的更新是透明的,因此可以保持平衡。模型模拟信号处理方案,尤其是在信号-噪声比率(SNR)分析时必须考虑电路的具体影响和连续信号处理的严格建立时间。使用有限注册结果将模拟元素当成定点算法时会低估SNR算法的实际效果。

5.结论:进入模拟-数字设计

由上可知,实际中我们设计系统是采用模拟信号处理或是数字信号处理,以及系统的复杂度如何均是未知?我们需设计处理器从传统IC工程开始,还是使用具有模拟FPGA,数字FPGA(s)加经典DSP处理器的开发板或片上系统,后者可以在需要时完全关闭其中任意部分的电源。我们从经典的DSP算法开始,因为数字方法经常是技术的开始和数字方法的分界线,也可能是某些灵感的来源(例如神经生物学)。我们一旦选择某种算法,就会在以下框架中思考。

l模拟信号处理是否使用于已选用的算法。

l对首个框架主要部分的估计:方案,电源预算,规范说明和推向市场的时间

表。

l模数信号处理的信号仿真级别(例如在MA TLAB中)对系统优化的效果。

对以上有些步骤反复思考是很必要的。

论文的后续的部分对处理过程中的某一方面或其它方面作了介绍。然后对某些实例和实验IC描述作了大体上说明,并指明了其中的某些问题。

参考文献

[1] Carver Mead,Analog VLSI and Neural Systems,Addison-Wesley,Reading,MA,1989.

[2] K.Boahen and A.Andreou,”A contrast-sensitive retina whit reciprocal synapses,”in Advances in Neural Information Processing Systems 4,J.E.Moddy,Ed.Morgan Kaufman Publisher,San Mateo,CA,1991.

[3] L.Watts,D.A.Kerns,and

R.F.Lyon,”Improved implementation of the silicon cochlea,”IEEE Journal of Solid-state Circuits,vol.27,no.5,pp.692-700,1992.

[4] https://www.doczj.com/doc/0215276.html,zzaro and C.A.Mead,”A winner-take-all circuit in o(n) complexity,”in Advances in Neural Information Processing Systems 1,Gerald Teasuro and David S.Touretzky,Eds,pp.817-824.MIT

Press,Cambridge,MA,1989.

[5] Matt Kucic,Paul Haslcr,Jeff Dugger,and David V.Adnerson,”Programmable and adaptive analog filers using arrays of floating-gate circuits,”in 2001 Conference on Advanced Research in VLSI,Erik Brunvand and Chris Myers,Dds,IEEE Computer Society,March 2001,pp.148-162.

[6] Asad A.Abidi G.Tyson Tuttle,Siavask Fallahi,”An 8b coms vector a/d converter,”in Proceedings of the IEEE International Solid State Circuits Conference,Monterey,CA,1993,pp.257- 259

[7] Jeremy Lubkin and Gert Cauwenberghs,”A micropower learning vector quantizer for parallel analog-to-digital data compression,”in Proceedings of the IEEE International Symposium on Circuits and System,Monterey,CA,1998,vol.Ⅲ,pp.191-196

[8] M.Holler,S.Tam,H.castro,and

R.Benson,”An electrically trainable artifical neural network with 10240 ‘floating ate’synapses,”in Proceedings of the International Joint Conference on Neural networks,Washington,D.C.,1989,vol.Ⅱ,pp.191-196

[9] P.Hasler,C.Diorio,B.A.Minch,and

C.A.Mead,’Single transistor learning synapses,’in Advances in Neural Information Processing Systems 7,Gerald Tesauro,David S.Touretzky,and Todd K.Leen,Eds.,pp.817-824.MIT Press,Cambridge,MA,1995.

[10] Paul Hasler,Bradley A.Minch,and Chris Diorio,”Floating-gate devices:They are not just for digital memories anymore,”in IEEE International Sympositum on Circuits and Systems,Orlando,Florida,1999,vol.Ⅱ,pp.399-391.

[11] P.Hasler and https://www.doczj.com/doc/0215276.html,nde,”Special issue on floating-gate devices,circuits,and systems,”IEEE Journal of Circuits and Systems,vol.48,no.1,Jan.2001

[12] Gene Franz,”Digital signal processor trends,”IEEE Micro,vol.20,no.6,pp.52-59,Nov-Dec 2000

[13] Carver A.Mead,”Neuromorphic electronic systems,”IEEE Proceedings,vol.78,no.10,pp.1629-1636,Oct.1990.

[14] Gert Cauwenbergs,Learning in Silicon,Kluwer Academic,1999.

[15] S.Y.Kung,VLSI array processors,Prentice Hall,Englewood Cliffs,N.J.,1988.

[16] Rahul Sarpeshkar,Efficient Precise computation with noisy components:extrapolating from an electronic cochlea to the brain,PhD thesis,California Institute of Technology,Pasadena,CA,1997.

[17] Paul Hasler,Bradley A.Minch,Jeff Dugger,and Chris Diorio,”Adaptive circuits and synapses using pfet floating-gate devices,”in Learning in Silicon,Gert Cauwenbergs,Ed.,pp,33-65.Kluwer Academic,1999

[18] Paul Hasler and Bradley

A.Minch,Floating-Gate Devices,Circuits,and Systems,IEEE Press,2002.

[19] P.Hasler,M.Kucic,and B.A.Minch,”A transistor-only circuit model of the autozeroing floating-gate amplifier,”in Midwest Conference on Circuits and Systems,Las Cruces,NM,1999

[20] Matt Kucic,AiChen Low,Paul Hasler,and Joe Neff,”A programmable continuus-time floating-gate fourier processor,”IEEE Transactions on Circuits and Systems Ⅱ,vol.48,no.1,pp.90-99,Jan.2001.

实验6 数字滤波器的网络结构 一、实验目的: 1、加深对数字滤波器分类与结构的了解。 2、明确数字滤波器的基本结构及其相互间的转换方法。 3、掌握用MA TLAB 语言进行数字滤波器结构间相互转换的子函数及程序编写方法。 二、实验原理: 1、数字滤波器的分类 离散LSI 系统对信号的响应过程实际上就是对信号进行滤波的过程。因此,离散LSI 系统又称为数字滤波器。 数字滤波器从滤波功能上可以分为低通、高通、带通、带阻以及全通滤波器;根据单位脉冲响应的特性,又可以分为有限长单位脉冲响应滤波器(FIR )和无限长单位脉冲响应滤波器(IIR )。 一个离散LSI 系统可以用系统函数来表示: M -m -1-2-m m m=0 012m N -1-2-k -k 12k k k=1 b z b +b z +b z ++b z Y(z)b(z)H(z)=== =X(z)a(z) 1+a z +a z ++a z 1+a z ∑∑ 也可以用差分方程来表示: N M k m k=1 m=0 y(n)+a y(n-k)=b x(n-m)∑∑ 以上两个公式中,当a k 至少有一个不为0时,则在有限Z 平面上存在极点,表达的是以一个IIR 数字滤波器;当a k 全都为0时,系统不存在极点,表达的是一个FIR 数字滤波器。FIR 数字滤波器可以看成是IIR 数字滤波器的a k 全都为0时的一个特例。 IIR 数字滤波器的基本结构分为直接Ⅰ型、直接Ⅱ型、直接Ⅲ型、级联型和并联型。 FIR 数字滤波器的基本结构分为横截型(又称直接型或卷积型)、级联型、线性相位型及频率采样型等。本实验对线性相位型及频率采样型不做讨论,见实验10、12。 另外,滤波器的一种新型结构——格型结构也逐步投入应用,有全零点FIR 系统格型结构、全极点IIR 系统格型结构以及全零极点IIR 系统格型结构。 2、IIR 数字滤波器的基本结构与实现 (1)直接型与级联型、并联型的转换 例6-1 已知一个系统的传递函数为 -1-2-3 -1-2-3 8-4z +11z -2z H(z)=1-1.25z +0.75z -0.125z 将其从直接型(其信号流图如图6-1所示)转换为级联型和并联型。

数字信号处理模拟试题一 一、单项选择题(本大题共10小题,每小题2分,共20分) 在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。错选、多选或未选均无分。 1.在对连续信号均匀采样时,要从离散采样值不失真恢复原信号,则采样角频率Ωs与信号最高截止频率Ωc应满足关系(A ) A.Ωs>2Ωc B.Ωs>Ωc C.Ωs<Ωc D.Ωs<2Ωc 2.下列系统(其中y(n)为输出序列,x(n)为输入序列)中哪个属于线性系统?(D) A.y(n)=y(n-1)x(n) B.y(n)=x(n)/x(n+1) C.y(n)=x(n)+1 D.y(n)=x(n)-x(n-1) 3.已知某序列Z变换的收敛域为5>|z|>3,则该序列为(D ) A.有限长序列 B.右边序列 C.左边序列 D.双边序列 4.实偶序列傅里叶变换是(A ) A.实偶序列 B.实奇序列 C.虚偶序列 D.虚奇序列 5.已知x(n)=δ(n),其N点的DFT[x(n)]=X(k),则X(N-1)=(B) A.N-1 B.1 C.0 D.-N+1 6.设两有限长序列的长度分别是M与N,欲通过计算两者的圆周卷积来得到两者的线性卷积,则圆周卷积的点数至少应取(B ) A.M+N B.M+N-1 C.M+N+1 D.2(M+N) 7.下面说法中正确的是(C) A.连续非周期信号的频谱为周期连续函数 B.连续周期信号的频谱为周期连续函数 C.离散非周期信号的频谱为周期连续函数 D.离散周期信号的频谱为周期连续函数 8.下列各种滤波器的结构中哪种不是IIR滤波器的基本结构?(C ) A.直接型 B.级联型 C.频率抽样型 D.并联型 9.下列关于FIR滤波器的说法中正确的是(C) A.FIR滤波器容易设计成线性相位特性

现代数字信号处理仿真作业 1.仿真题3.17 仿真结果及图形: 图 1 基于FFT的自相关函数计算

图 3 周期图法和BT 法估计信号的功率谱 图 2 基于式3.1.2的自相关函数的计算

图 4 利用LD迭代对16阶AR模型的功率谱估计16阶AR模型的系数为: a1=-0.402637623107952-0.919787323662670i; a2=-0.013530139693503+0.024214641171318i; a3=-0.074241889634714-0.088834852915013i; a4=0.027881022353997-0.040734794506749i; a5=0.042128517350786+0.068932699075038i; a6=-0.0042799971761507 + 0.028686095385146i; a7=-0.048427890183189 - 0.019713457742372i; a8=0.0028768633718672 - 0.047990801912420i a9=0.023971346213842+ 0.046436389191530i; a10=0.026025963987732 + 0.046882756497113i; a11= -0.033929397784767 - 0.0053437929619510i; a12=0.0082735406293574 - 0.016133618316269i; a13=0.031893903622978 - 0.013709547028453i ; a14=0.0099274520678052 + 0.022233240051564i; a15=-0.0064643069578642 + 0.014130696335881i; a16=-0.061704614407581- 0.077423818476583i. 仿真程序(3_17): clear all clc %% 产生噪声序列 N=32; %基于FFT的样本长度

一、 单 项选择题 1. 序列x(n)=Re(e jn π/12 )+I m (e jn π/18 ),周期为( )。 A. 18π B. 72 C. 18π D. 36 2. 设C 为Z 变换X(z)收敛域内的一条包围原点的闭曲线,F(z)=X(z)z n-1 ,用留数法求X(z)的反变换时( )。 A. 只能用F(z)在C 内的全部极点 B. 只能用F(z)在C 外的全部极点 C. 必须用收敛域内的全部极点 D. 用F(z)在C 内的全部极点或C 外的全部极点 3. 有限长序列h(n)(0≤n ≤N-1)关于τ= 2 1 -N 偶对称的条件是( )。 A. h(n)=h(N-n) B. h(n)=h(N-n-1) C. h(n)=h(-n) D. h(n)=h(N+n-1) 4. 对于x(n)= n )21(u(n)的Z 变换,( )。 A. 零点为z=21,极点为z=0 B. 零点为z=0,极点为z=21 C. 零点为z=21,极点为z=1 D. 零点为z=2 1 ,极点为z=2 5、)()(101n R n x =,)()(72n R n x =,用DFT 计算二者的线性卷积,为使计算量尽可能的少,应使DFT 的长度N 满足 。 A.16>N B.16=N C.16

数字信号处理作业

DFT 习题 1. 如果)(~n x 是一个周期为N 的周期序列,那么它也是周期为N 2的周期序列。把)(~ n x 看作周期为N 的周期序列,令)(~1k X 表示)(~n x 的离散傅里叶级数之系数,再把)(~ n x 看作周期为N 2的周期序列,再令)(~2k X 表示)(~n x 的离散傅里叶级数之系数。当然,)(~1k X 是周期性的,周期为N ,而)(~2k X 也是周期性的,周期为N 2。试利用)(~1k X 确定)(~2k X 。(76-4)

2. 研究两个周期序列)(~n x 和)(~n y 。)(~n x 具有周期N ,而)(~ n y 具有周期M 。序列)(~n w 定义为)()()(~ ~~n y n x n w +=。 a. 证明)(~n w 是周期性的,周期为MN 。 b. 由于)(~n x 的周期为N ,其离散傅里叶级数之系数)(~k X 的周期也是N 。类似地, 由于)(~n y 的周期为M ,其离散傅里叶级数之系数)(~k Y 的周期也是M 。)(~n w 的离散傅里叶级数之系数)(~k W 的周期为MN 。试利用)(~k X 和)(~k Y 求)(~k W 。(76-5)

数字信号处理期末试卷(含答案) 一、单项选择题(在每小题的四个备选答案中,选出一个正确答案,并将正确答案的序号填在括号内。 1.若一模拟信号为带限,且对其抽样满足奈奎斯特采样定理,则只要将抽样信号通过( )即可完全不失真恢复原信号。 A.理想低通滤波器 B.理想高通滤波器 C.理想带通滤波器 D.理想带阻滤波器 2.下列系统(其中y(n)为输出序列,x(n)为输入序列)中哪个属于线性系统?( ) A.y(n)=x 3(n) B.y(n)=x(n)x(n+2) C.y(n)=x(n)+2 D.y(n)=x(n 2) 3..设两有限长序列的长度分别是M 与N ,欲用圆周卷积计算两者的线性卷积,则圆周卷积的长度至少应取( )。 A .M+N B.M+N-1 C.M+N+1 D.2(M+N) 4.若序列的长度为M ,要能够由频域抽样信号X(k)恢复原序列,而不发生时域混 叠现象,则频域抽样点数N 需满足的条件是( )。 A.N ≥M B.N ≤M C.N ≤2M D.N ≥2M 5.直接计算N 点DFT 所需的复数乘法次数与( )成正比。 A.N B.N 2 C.N 3 D.Nlog 2N 6.下列各种滤波器的结构中哪种不是FIR 滤波器的基本结构( )。 A.直接型 B.级联型 C.并联型 D.频率抽样型 7.第二种类型线性FIR 滤波器的幅度响应H(w)特点( ): A 关于0=w 、π、π2偶对称 B 关于0=w 、π、π2奇对称 C 关于0=w 、π2偶对称 关于=w π奇对称 D 关于0=w 、π2奇对称 关于=w π偶对称 8.适合带阻滤波器设计的是: ( ) A )n N (h )n (h ---=1 N 为偶数 B )n N (h )n (h ---=1 N 为奇数 C )n N (h )n (h --=1 N 为偶数

数字信号处理试题及答案 一、填空题:(每空1分,共18分) 1、 数字频率ω是模拟频率Ω对采样频率s f 的归一化,其值是 连续 (连续还是离散?)。 2、 双边序列z 变换的收敛域形状为 圆环或空集 。 3、 某序列的 DFT 表达式为∑-==1 0)()(N n kn M W n x k X ,由此可以看出,该序列时域的长度为 N ,变换后数字频域上相邻两个频率样点之间的间隔是 M π 2 。 4、 线性时不变系统离散时间因果系统的系统函数为2 52) 1(8)(2 2++--=z z z z z H ,则系统的极点为 2,2 1 21-=-=z z ;系统的稳定性为 不稳定 。系统单位冲激响应)(n h 的初值 4)0(=h ;终值)(∞h 不存在 。 5、 如果序列)(n x 是一长度为64点的有限长序列)630(≤≤n ,序列)(n h 是一长度为128点 的有限长序列)1270(≤≤n ,记)()()(n h n x n y *=(线性卷积),则)(n y 为 64+128-1=191点 点的序列,如果采用基FFT 2算法以快速卷积的方式实现线性卷积,则FFT 的点数至少为 256 点。 6、 用冲激响应不变法将一模拟滤波器映射为数字滤波器时,模拟频率Ω与数字频率ω之间的 映射变换关系为T ω = Ω。用双线性变换法将一模拟滤波器映射为数字滤波器时,模拟频率Ω 与数字频率ω之间的映射变换关系为)2 tan(2ω T =Ω或)2arctan(2T Ω=ω。 7、当线性相位 FIR 数字滤波器满足偶对称条件时,其单位冲激响应)(n h 满足的条件为 )1()(n N h n h --= ,此时对应系统的频率响应)()()(ω?ω ωj j e H e H =,则其对应的相位函数 为ωω?2 1 )(-- =N 。 8、请写出三种常用低通原型模拟滤波器 巴特沃什滤波器 、 切比雪夫滤波器 、 椭圆滤波器 。 二、判断题(每题2分,共10分) 1、 模拟信号也可以与数字信号一样在计算机上进行数字信号处理,只要加一道采样的工序就可 以了。 (╳) 2、 已知某离散时间系统为)35()]([)(+==n x n x T n y ,则该系统为线性时不变系统。(╳)

实验5 抽样定理 一、实验目的: 1、了解用MA TLAB 语言进行时域、频域抽样及信号重建的方法。 2、进一步加深对时域、频域抽样定理的基本原理的理解。 3、观察信号抽样与恢复的图形,掌握采样频率的确定方法和插公式的编程方法。 二、实验原理: 1、时域抽样与信号的重建 (1)对连续信号进行采样 例5-1 已知一个连续时间信号sin sin(),1Hz 3 ππ=0001f(t)=(2f t)+6f t f ,取最高有限带宽频率f m =5f 0,分别显示原连续时间信号波形和F s >2f m 、F s =2f m 、F s <2f m 三情况下抽样信号的波形。 程序清单如下: %分别取Fs=fm ,Fs=2fm ,Fs=3fm 来研究问题 dt=0.1; f0=1; T0=1/f0; m=5*f0; Tm=1/fm; t=-2:dt:2; f=sin(2*pi*f0*t)+1/3*sin(6*pi*f0*t); subplot(4,1,1); plot(t,f); axis([min(t),max(t),1.1*min(f),1.1*max(f)]); title('原连续信号和抽样信号'); for i=1:3; fs=i*fm;Ts=1/fs; n=-2:Ts:2; f=sin(2*pi*f0*n)+1/3*sin(6*pi*f0*n); subplot(4,1,i+1);stem(n,f,'filled'); axis([min(n),max(n),1.1*min(f),1.1*max(f)]); end 程序运行结果如图5-1所示:

数字信号处理上机作业 学院:电子工程学院 班级:021215 组员:

实验一:信号、系统及系统响应 1、实验目的 (1) 熟悉连续信号经理想采样前后的频谱变化关系,加深对时域采样定理的理解。 (2) 熟悉时域离散系统的时域特性。 (3) 利用卷积方法观察分析系统的时域特性。 (4) 掌握序列傅里叶变换的计算机实现方法,利用序列的傅里叶变换对连续信号、离散信号及系统响应进行频域分析。 2、实验原理与方法 (1) 时域采样。 (2) LTI系统的输入输出关系。 3、实验内容及步骤 (1) 认真复习采样理论、离散信号与系统、线性卷积、序列的傅里叶变换及性质等有关内容,阅读本实验原理与方法。 (2) 编制实验用主程序及相应子程序。 ①信号产生子程序,用于产生实验中要用到的下列信号序列: a. xa(t)=A*e^-at *sin(Ω0t)u(t) b. 单位脉冲序列:xb(n)=δ(n) c. 矩形序列: xc(n)=RN(n), N=10 ②系统单位脉冲响应序列产生子程序。本实验要用到两种FIR系统。 a. ha(n)=R10(n); b. hb(n)=δ(n)+2.5δ(n-1)+2.5δ(n-2)+δ(n-3) ③有限长序列线性卷积子程序 用于完成两个给定长度的序列的卷积。可以直接调用MATLAB语言中的卷积函数conv。 conv 用于两个有限长度序列的卷积,它假定两个序列都从n=0 开始。调用格式如下: y=conv (x, h) 4、实验结果分析 ①分析采样序列的特性。 a. 取采样频率fs=1 kHz,,即T=1 ms。 b. 改变采样频率,fs=300 Hz,观察|X(e^jω)|的变化,并做记录(打印曲线);进一步降低采样频率,fs=200 Hz,观察频谱混叠是否明显存在,说明原因,并记录(打印)这时的|X(e^j ω)|曲线。 程序代码如下: close all;clear all;clc; A=50; a=50*sqrt(2)*pi; m=50*sqrt(2)*pi; fs1=1000; fs2=300; fs3=200; T1=1/fs1; T2=1/fs2; T3=1/fs3; N=100;

数字信号处理期末试题及答案汇总

数字信号处理卷一 一、填空题(每空1分, 共10分) 1.序列()sin(3/5)x n n π=的周期为 。 2.线性时不变系统的性质有 律、 律、 律。 3.对4 ()()x n R n =的Z 变换为 ,其收敛域为 。 4.抽样序列的Z 变换与离散傅里叶变换DFT 的关系为 。 5.序列x(n)=(1,-2,0,3;n=0,1,2,3), 圆周左移2位得到的序列为 。 6.设LTI 系统输入为x(n) ,系统单位序列响应为h(n),则系统零状态输出y(n)= 。 7.因果序列x(n),在Z →∞时,X(Z)= 。 二、单项选择题(每题2分, 共20分) 1.δ(n)的Z 变换是 ( )A.1 B.δ(ω) C.2πδ(ω) D.2π 2.序列x 1(n )的长度为4,序列x 2(n )的长度为3,则它们线性卷积的长度是 ( ) A. 3 B. 4 C. 6 D. 7 3.LTI 系统,输入x (n )时,输出y (n );输入 为3x (n-2),输出为 ( ) A. y (n-2) B.3y (n-2) C.3y (n ) D.y (n ) 4.下面描述中最适合离散傅立叶变换DFT 的是 ( ) A.时域为离散序列,频域为连续信号 B.时域为离散周期序列,频域也为离散周期序列

数字信号处理作业 哈尔滨工业大学 2006.10

DFT 习题 1. 如果)(~n x 是一个周期为N 的周期序列,那么它也是周期为N 2的周期序列。把)(~ n x 看作周期为N 的周期序列,令)(~ 1k X 表示)(~n x 的离散傅里叶级数之系数,再把)(~ n x 看作周期为N 2的周期序列,再令)(~ 2k X 表示)(~n x 的离散傅里叶级数之系数。当然,)(~ 1k X 是周期性的,周期为N ,而)(~ 2k X 也是周期性的,周期为N 2。试利用)(~ 1k X 确定)(~ 2k X 。(76-4)

2. 研究两个周期序列)(~ n x 和)(~ n y 。)(~ n x 具有周期N ,而)(~ n y 具有周期M 。序列 )(~n w 定义为)()()(~ ~~n y n x n w +=。 a. 证明)(~ n w 是周期性的,周期为MN 。 b. 由于)(~n x 的周期为N ,其离散傅里叶级数之系数)(~ k X 的周期也是N 。类似地, 由于)(~n y 的周期为M ,其离散傅里叶级数之系数)(~k Y 的周期也是M 。)(~ n w 的离散傅里叶级数之系数)(~ k W 的周期为MN 。试利用)(~ k X 和)(~ k Y 求)(~ k W 。(76-5)

A 一、 选择题(每题3分,共5题) 1、)6 3()(π-=n j e n x ,该序列是 。 A.非周期序列 B.周期6 π = N C.周期π6=N D. 周期π2=N 2、序列)1()(---=n u a n x n ,则)(Z X 的收敛域为 。 A.a Z < B.a Z ≤ C.a Z > D.a Z ≥ 3、对)70()(≤≤n n x 和)190()(≤≤n n y 分别作 20 点 DFT ,得)(k X 和)(k Y , 19,1,0),()()( =?=k k Y k X k F ,19,1,0)],([)( ==n k F IDFT n f , n 在 围时,)(n f 是)(n x 和)(n y 的线性卷积。 A.70≤≤n B.197≤≤n C.1912≤≤n D.190≤≤n 4、)()(101n R n x =,)()(72n R n x =,用DFT 计算二者的线性卷积,为使计算量尽可能的少,应使DFT 的长度N 满足 。 A.16>N B.16=N C.16 仿真作业 姓名:李亮 学号:S130101083 4.17程序 clc; clear; for i=1:500 sigma_v1=0.27; b(1)=-0.8458; b(2)=0.9458; a(1)=-(b(1)+b(2)); a(2)=b(1)*b(2); datlen=500; rand('state',sum(100*clock)); s=sqrt(sigma_v1)*randn(datlen,1); x=filter(1,[1,a],s); %% sigma_v2=0.1; u=x+sqrt(sigma_v2)*randn(datlen,1); d=filter(1,[1,-b(1)],s); %% w0=[1;0]; w=w0; M=length(w0); N=length(u); mu=0.005; for n=M:N ui=u(n:-1:n-M+1); y(n)=w'*ui; e(n)=d(n)-y(n); w=w+mu.*conj(e(n)).*ui; w1(n)=w(1); w2(n)=w(2); ee(:,i)=mean(e.^2,2); end end ep=mean(ee'); plot(ep); xlabel('迭代次数');ylabel('MSE');title('学习曲线'); plot(w1); hold; plot(w2); 仿真结果: 1. 两个有限长序列x1(n),0≤n ≤33和x2(n),0≤n ≤36,做线性卷积后结果的长度是 70 , 若对这两个序列做64点循环卷积,则圆周卷积结果中n= 6 至 64 为线性卷积结果。 2. 一线性时不变系统,输入为 x (n )时,输出为y (n ) ;则输入为2x (n )时,输出为 ; 输入为x (n-3)时,输出为 3. 若正弦序列x(n)=sin(30n π/120)是周期的,则周期是N= 8 4. 如果一台计算机的速度为平均每次复乘5μS ,每次复加0.5μS ,用它来计算512 点的DFT[x(n)],问直接计算需要多少时间,用FFT 运算需要多少时间。 1、 直接计算 复乘所需时间 62621510510512 1.31072T N s --=??=??= 复加所需时间()6610.51010.5105125110.130816T N N s --=???-=???= 所以12 1.441536T T T s =+= 2、用FFT 计算 复乘所需时间 66122512510log 510log 5120.0115222 N T N s --=?? =??= 复加所需时间662220.510log 0.510512log 5120.002304T N N s --=??=??= 所以120.013824T T T s =+=现代数字信号处理及应用仿真题答案

2017数字信号处理模拟题a答案