数字逻辑设计和应用-本科3-答案

- 格式:doc

- 大小:1.03 MB

- 文档页数:3

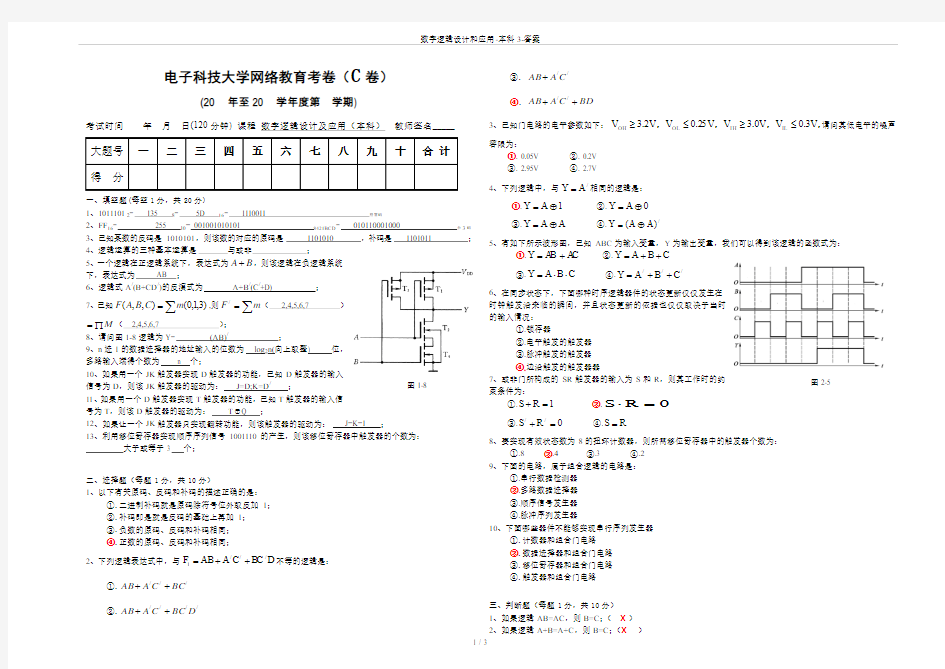

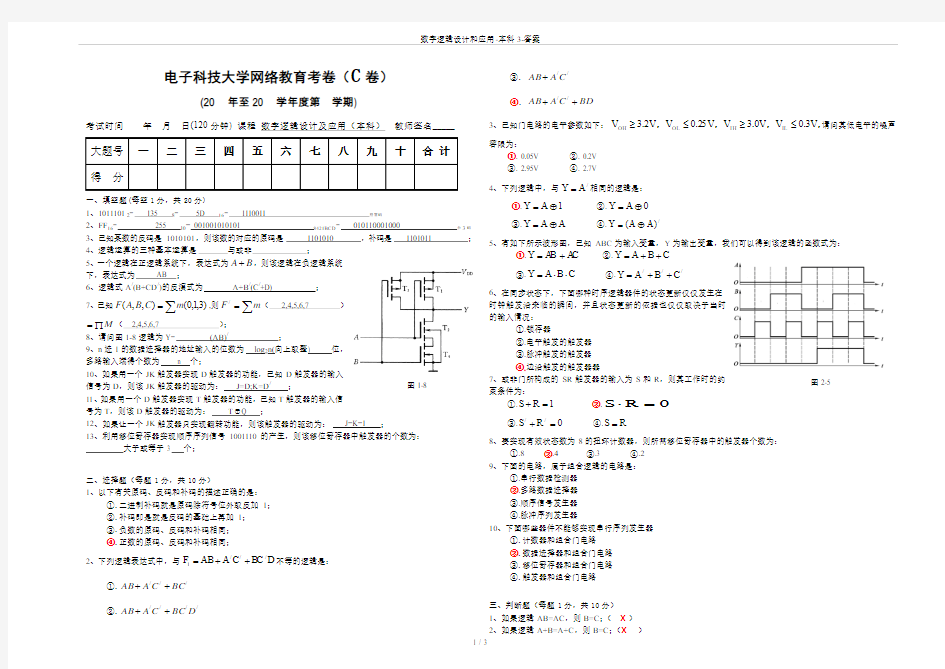

图1-8 图2-5

J=K=1 ;

的产生,则该移位寄存器中触发器的个数为:

2 / 3

3、如果逻辑AB+AC=1,则A=1;( √ )

4、如果逻辑AB+AC=0,则A=0;(Х )

5、若干个逻辑信号进行异或操作,如果这些信号中逻辑“1”的个数为奇数,则输出结果为1;(

√

) 6、A ⊕1=A /;( √ ) 7、A+A+A=A ·A ·A ;( √ )

8、对于CMOS 集成门电路而言,与门的结构比与非门的结构更为简单一些;(Х ) 9、TTL 逻辑比CMOS 逻辑的运行功耗更低,所以更利于集成;(Х ) 10、影响CMOS 集成门电路的运行速度主要是传输延迟和转换时间;( √ )

四、卡诺图化简(8分)

将逻辑F (A,B,C,D )=∑m(0,1,3,4,6,7,14,15)+d(8,9,10,11,12,13)化成最简或与函数式;

F=C /D /

+B /

D+BC

答案不唯一

五、组合逻辑分析,要求如下(8分)

完成图5所示电路的逻辑分析,并写出: 1、 逻辑Y 的函数式 2、 写出该逻辑的真值表 1、 函数式

2、 真值表

六、时序逻辑分析,要求如下:(14分)

请分析图6所示电路的逻辑,并写出: 1、 驱动方程和输出方程; 2、 状态方程;

3、 画出状态转换图或者状态转换表;

驱动方程:21'⋅=Q X EN ,

12Q J =,12=K

状态方程:121121111*1Q Q Q X Q Q X Q EN Q EN Q ⋅+⋅'+'⋅'⋅=⋅'+'⋅=

122222*2Q Q Q K Q J Q ⋅'=⋅'+'⋅=

输出方程:21'⋅+⋅'=Q X Q X Z 状态表:

或者状态图:

图5

图6

C

B A

C B A C

B A

C B A F /

/

/

///∙∙+∙∙+∙∙+∙∙=

3 / 3

七、组合逻辑设计,要求如下:(8分)

请利用一块8选1的数据选择器芯片74153来实现如下逻辑:BC AC AB Y ++=;可加一定的门电路来实现。

先对数据选择器进行扩展, 然后在赋值

八、时序逻辑设计,要求如下:(10分)

请利用移位寄存器74194和一定的门电路结构,设计一个3位的扭环计数器,要求该电路能够自行启动 1、画出能够自行启动的3位扭环计数器状态图

2、请在74194芯片上完成该逻辑,已知74194芯片的逻辑功能定义如下:

能够自行启动的3位扭环计数器,其状态图和反馈函数定义如下:

求反馈函数:

F=Q2/

+Q1/

Q0

选择右移方式,完成电路图如下:

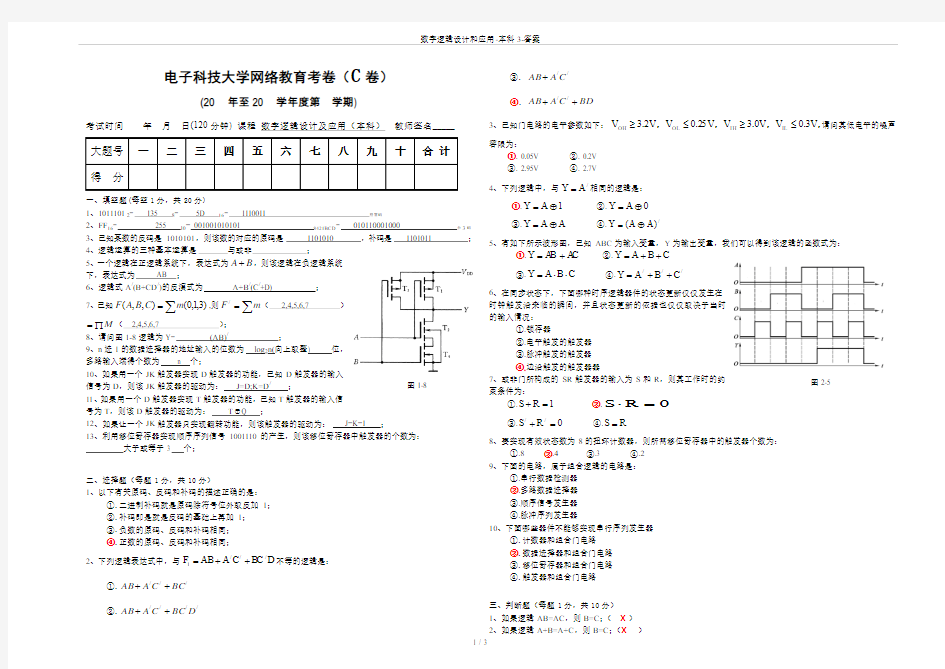

九、时序逻辑设计,要求如下:(12分)

已知一个时序逻辑的状态转换图如图9所示。请完成该逻辑电路的设计,无须考虑自启动问题。选择D 触发器来实现。要求写出:

1、 状态方程

2、 驱动方程和输出方程;

3、 画出逻辑图

(已知三个状态的编码分别为S0:Q1Q0=00;S1:Q1Q0=01;S2:Q1Q0=10; 状态表如下:

状态方程:

Q X 0Q 1XQ 0Q 1Q X 0XQ 1Q /

/

/

*

/*+=+=

驱动方程和输出方程:

1

XQ Y 0Q X 0Q 1XQ 0Q 0D 1Q X 0XQ 1Q 1D ///*/*=+==+== 电路图略;

图9

1/1