McBSP实时音频数据传输的EDMA3配置

- 格式:pdf

- 大小:743.25 KB

- 文档页数:3

DSP+ARM+FPGA三核实验箱硬件资源详解目录1 实验箱简介 (2)2 软硬件参数 (6)3 开发资料 (11)4 电气特性 (12)5 实验箱机械尺寸 (13)6 实验箱组件 (13)7 技术支持 (14)附录A 开发例程 (15)1实验箱简介基于TI OMAP-L138(定点/浮点DSP C674x+ARM9)+ Xilinx Spartan-6 FPGA处理器;OMAP-L138与FPGA通过uPP、EMIFA、I2C总线连接,通信速度可高达228MByte/s; OMAP-L138主频456MHz,高达3648MIPS和2746MFLOPS的运算能力,具备SATA、EMIFA、uPP、USB 2.0等高速数据传输接口;FPGA兼容Xilinx Spartan-6 XC6SLX9/16/25/45,平台升级能力强;通过高低温测试认证,适合各种恶劣的工作环境;66mm*38.6mm,全国最小DSP+ARM+FPGA三核核心板,采用工业级B2B连接器; 可充放电池电路,提供多种标准工业接口,可连多通道AD、DA等模块,拓展能力强; 支持裸机、SYS/BIOS操作系统、Linux操作系统。

图 1图2图3图4图5图6图7TL138F-TEB是广州创龙一款基于TI OMAP-L138(定点/浮点DSP C674x+ARM9)+ Xilinx Spartan-6 FPGA三核心可拆式新型嵌入式教学实验箱,提供了丰富的教学实验例程,并提供视频教程,十分适合高校以及研究所等实验机构。

可拆式实验箱TL138F-TEB可以用于师生项目开发,相对传统的实验箱来说,使用更加灵活,性价比更高。

2软硬件参数硬件参数图8 SOM-TL138F硬件框图图9 Xilinx Spartan-6 FPGA特性参数图10 实验箱主板图11实验箱主板图12实验箱拓展板图13实验箱拓展板表1 实验箱主板硬件参数CPUTI OMAP-L138,浮点/定点DSP C674x+ARM9处理器,双核主频456MHzXilinx Spartan-6 XC6SLX9/16/25/45 FPGAROMOMAP-L138端:128/256/512MByte NAND FLASHSpartan-6端:64Mbit SPI FLASHRAM OMAP-L138端:128/256MByte DDR2EEPROM 1x AT24C02,256Byte连接器2x 80pin公座B2B,2x 80pin母座B2B,间距0.5mm,共320pin拓展IO 2x 25pin IDC3简易牛角座,间距2.54mm,EMIFA拓展信号2x 25pin IDC3简易牛角座,间距2.54mm,FPGA GPIO拓展信号2x 12pin排针,间距2.54mm,含McASP、GPIO等拓展信号3x 12pin PMOD座,FPGA GPIO拓展信号2x 48pin欧式公座连接器,FPGA GPIO拓展信号LED 2x 供电指示灯(底板1个,核心板1个)5x 可编程指示灯(底板3个,核心板2个)5x 可编程指示灯(底板3个,核心板2个)按键1x 系统复位按键3x 可编程输入按键(含1个非屏蔽中断按键)3x 可编程输入按键仿真器接口1x 14pin TI Rev B JTAG接口,间距2.54mm1x 14pin FPGA JTAG接口,间距2.0mm 显示1x LCD触摸屏接口启动方式接口1x 5bit启动方式选择拨码开关SD卡1x Micro SD卡接口RTC 1x CR1620,3V可充电RTCSATA 1x 7pin SATA硬盘接口网络1x RJ45以太网口,10/100M自适应USB接口1x Micro USB 2.0 OTG接口4x USB 1.1 HOST接口串口2x RS232串口,1x RS485串口(RS485和UART1复用),其中UART2使用Micro USB 接口,UART1使用DB9接口1x RS232串口,使用DB9接口电源开关1x 电源拨码开关电源接口1x12V 2A直流输入DC417电源接口,外径4.4mm,内径1.65mm拓展电源接口2x 2pin白色端子座,间距2.54mm,提供3.3V和5V电源备注:广州创龙SOM-TL138F、SOM-TL1808F、SOM-TL6748F核心板在硬件上pin to pin兼容。

TMS320DM6437 DMP介绍TMS320DM6437 Digital Media Processor—一种高性能数字媒体处理器:VelociTI.2结构DSP内核,先进超长指令字(VLIW)C64x+指令集特性C64x+ L1/L2存储器结构口仅支持小端模式视频处理子系统(VPSS)外部存储器接口(EMIF)增强型直接存储器访问控制器(EDMA):64个独立通道1个64位看门狗定时器2个UART(带RTS和CTS流控信号)主/从I2C总线控制器两个多通道缓冲串行接口(McBSP)多通道音频串行接口(McASP0)高端CAN控制器(HECC)16位主机接口(HPI)32位、33MHz、3.3V PCI主从接口10/100Mb/s以太网MAC(EMAC)VL YNQ接口(FPGA 接口)VL YNQTM接口(FPGA 接口)片上ROM Bootloader独特的节电模式灵活的PLL时钟产生器IEEE-1149.1(JTAG)多达111个GPIO(与其他功能复用)引脚及封装3.3V/1.8V I/O;1.2V/1.05V内部一、DaVinci DM6437 概述TMS320C64x DSP内核:TMS320DM6437是专门为高性能、低成本视频应用开发的、32位定点DSP达芬奇(DaVinci(TM)) 技术的处理器。

该器件采用TI第2代超长指令字(VLIW)结构(VelociTI.2)的TMS320C64x+ DSP内核,主频可达700MHz,支持8个8位或4个16位并行MAC (multiply-accumulates)运算,峰值处理能力高达5600MIPS。

> C64x片内有2个数据通道、8个功能单元和2个通用寄存器文件(A和B)。

8个功能单元(2个乘法器和6个算术逻辑单元)用于提高影像和图像应用的性能。

每个通用寄存器文件包含32个32-bit寄存器。

这些通用寄存器可以用做数据指针或者数据地址指针。

基于DSP的PCI总线高速DMA数据传输闫改;郭晓光【摘要】针对数据采集系统中的高速数据传输需求,对TMS320C6416DSP的PCI 接口特性进行了简单介绍,以TMS320C6416DSP作为PCI主设备控制并启动直接存储器存取(DMA)数据传输,给出了数据传输系统的硬件及软件设计流程,实现了PCI总线的DMA数据传输.与其他PCI总线传输方式比较,TMS320C6416DSP开发成本低、集成度高、通用性好、功能拓展灵活,具有良好的PCI总线数据传输性能,使板卡与PC机之间通信速度得到很大提高,并在项目中证实了PCI总线数据传输方面的能力.【期刊名称】《无线电工程》【年(卷),期】2013(043)008【总页数】4页(P19-21,32)【关键词】PCI接口;数据传输;直接存储器存取;增强型直接存储器存取【作者】闫改;郭晓光【作者单位】中国电子科技集团公司第五十四研究所,河北石家庄050081;中国人民解放军驻北京地区军事代表室,北京100191【正文语种】中文【中图分类】TP330 引言高速数据采集建立在计算机对数据的传输和处理基础上,计算机系统一般通过总线(Bus)实现相互间信息或数据交换的,PCI总线广泛使用在计算机中,一方面是因为该总线的数据吞吐量大;另一方面是因为该总线与具体的处理器无关。

当前使用PCI总线进行数据传输有以下3种方法:① IP CORE,例如Altera的IP CORE,这种方法实现容易,但花费较大;② 使用内嵌PCI协议的专用芯片,例如AMCC的S5933,PLX的9054等,但前提是对此类芯片的用法非常熟悉;③利用高速FPGA 来实现PCI总线传输,由于需对PCI协议及时序精通,因此程序调试相对困难,功能很难得到全面完善。

由于高速数据采集系统的应用越来越广泛,本文采用基于TI公司TMS320C6416产品设计的高速数据传输平台,用户可以对芯片用法、PCI协议或时序等方面不需要特别熟悉,而且能够较大程度降低开发成本。

2014产品版本号:A2文档版本号:V1.0更多产品信息请浏览:广州创龙电子科技有限公司Revision History阅前须知版权声明广州创龙电子科技有限公司保留随时对其产品进行修改和完善的权利,同时也保留在不作任何通告的情况下,终止其任何一款产品的供应和服务的权利。

请用户在购买前向我司获取相关产品的最新信息,本文档一切解释权归广州创龙所有。

©2014-2018 Guangzhou Tronlong Electronic Technology Co.,Ltd. All rights reserved.公司简介广州创龙电子科技有限公司(简称“广州创龙”,英文简称“Tronlong”),是杰出的嵌入式方案商,专业提供嵌入式开发平台工具及嵌入式软硬件定制设计及技术支持等服务,专注于DSP+ARM+FPGA三核系统方案开发,和国内诸多著名企业、研究所和高校有密切的技术合作,如富士康、威胜集团、中国科学院、清华大学等国内龙头企业和院校。

TI 嵌入式处理业务拓展经理Zheng Xiaolong 指出:“Tronlong 是国内研究OMAP-L138最深入的企业之一,Tronlong 推出OMAP-L138+Spartan-6三核数据采集处理显示解决方案,我们深感振奋,它将加速客户新产品的上市进程,带来更高的投资回报率,使得新老客户大大受益。

”经过近几年的发展,创龙产品已占据相关市场主导地位,特别是在电力、通信、工控、音视频处理等数据采集处理行业广泛应用。

创龙致力于让客户的产品快速上市、缩短开发周期、降低研发成本。

选择创龙,您将得到强大的技术支持和完美的服务体验。

产品保修广州创龙所有产品保修期为一年,保修期内由于产品质量原因引起的,经鉴定系非人为因素造成的产品损坏问题,由广州创龙免费维修或者更换。

更多帮助目录1 核心板简介 (5)2 产品特点 (6)3 典型运用领域 (7)4 软硬件参数 (7)5 技术支持和开发资料 (8)6 电气特性 (12)7 机械尺寸图 (13)8 产品认证 (14)9 产品订购型号 (17)10 相关产品列表 (18)11 增值服务 (18)12 更多帮助 (19)1 核心板简介基于TI 浮点DSP TMS320C6748 CPU ,标配工业级,主频456MHz ,; 55mm*33mm ,全国最小DSP 核心板,采用精密工业级B2B 连接器; TI 主推的超低功耗C6000系列DSP 处理器,适用于便携式设备; 标配工业级NAND FLASH ,128/256/512MByte 可选; 标配工业级DDR2,128/256MByte 可选;标配裸机,支持DSP/BIOS 、SYS/BIOS 、TI-RTOS (SYS/BIOS ),提供40多个例程; 通过高低温、振动测试认证,满足工业环境应用;图2 SOM-TL6748背面由广州创龙自主研发的SOM-TL6748是全国最小的C6000系列浮点DSP C6748工业级核心板,55mm*33mm ,仅硬币大小,功耗小、成本低、性价比高。

DYEMB3.3 DY-EMB3.3配置与使用手册软件适用版本:DY-EMB 3.3.3.0文档版本:20110430系统网络产品部北京中科大洋科技发展股份有限公司2011.04目录DY-EMB3.3配置与使用手册 (3)1.数据库连接 (3)2.Config (4)2.1.数据库设置 (4)2.2.添加Actor (4)2.3.添加Manager (6)2.4.添加新用户 (7)2.5.参数说明与配置 (8)2.6.视音频模板配置 (10)2.7.存储空间管理 (11)2.7.1.访问路径控制 (12)2.7.2.路径切换 (12)2.7.3.存储配置 (12)3.Manager (16)3.1.Manager配置.................................................................................. 错误!未定义书签。

3.1.1.Config配置说明................................................................. 错误!未定义书签。

3.1.2.datasource数据库信息配置............................................... 错误!未定义书签。

3.2.Windows平台启动Manager .......................................................... 错误!未定义书签。

4.Actor (16)4.1.Actor配置 (20)4.2.Windows平台启动Actor (20)5.Monitor (22)5.1.查看EMB工作站 (22)5.2.查看EMB调度服务器 (24)5.3.查看任务 (24)5.4.表头配置 (25)5.5.任务检索 (26)5.6.任务树结构 (26)5.7.其它功能 (34)6.TaskEdit (34)6.1.添加转码任务 (34)6.2.添加拷贝任务 (39)文档更新记录 (42)EMB3.3配套文档 (42)DY-EMB3.3配置与使用手册1.数据库连接Config、Monitor、TaskEdit、转换桥与数据库连接。

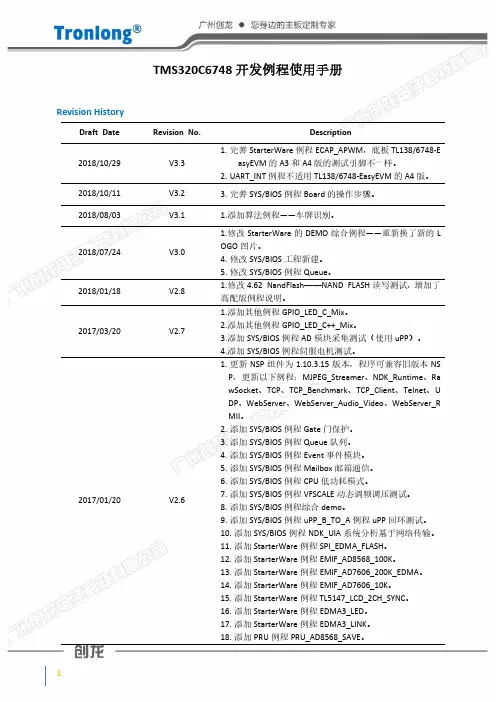

TMS320C6748开发例程使用手册Revision HistoryDraft Date Revision No. Description2018/10/29 V3.3 1.完善StarterWare例程ECAP_APWM,底板TL138/6748-EasyEVM的A3和A4版的测试引脚不一样。

2.UART_INT例程不适用TL138/6748-EasyEVM的A4版。

2018/10/11 V3.2 3.完善SYS/BIOS例程Board的操作步骤。

2018/08/03 V3.1 1.添加算法例程——车牌识别。

2014/05/05 V1.0 1.初始版本。

目录1 开发板准备 (16)1.1查看仿真器驱动是否正常安装 (17)2 程序加载和烧写 (19)2.1基于仿真器的程序加载和烧写 (19)2.1.1设置工程配置文件信息 (19)2.1.2测试仿真器是否正常连接 (20)2.1.3加载GEL文件 (21)2.1.4CCS连接开发板CPU (22)2.1.5查看CPU版本号 (23)2.1.6加载文件烧写程序 (24)2.1.7基于仿真器烧写程序到NAND FLASH (24)2.1.8NAND FLASH烧写格式镜像转换方法 (29)2.2基于串口的程序加载和烧写 (31)2.2.1串口加载和烧写格式镜像转换方法 (31)2.2.2程序加载和运行 (33)2.2.3基于串口烧写程序到NAND FLASH (39)2.2.4基于串口烧写程序到SPI FLASH (42)2.3基于SD卡运行程序 (44)2.3.1SD启动格式镜像转换方法 (44)2.3.2将程序烧写到SD卡 (46)2.3.3SD卡模式启动开发板 (49)2.4基于SD卡烧写程序到NAND FLASH (49)2.4.1格式化SD卡 (49)2.4.2准备烧写镜像 (53)2.5基于网络的程序烧写和启动 (55)3 CCS工程新建、编译和导入 (59)3.1裸机工程创建 (61)3.1.1新建工程 (61)3.1.2编写程序 (64)3.1.3编译和运行程序 (64)3.2SYS/BIOS工程创建 (66)3.2.1创建SYS/BIOS平台配置文件 (68)3.2.2新建SYS/BIOS工程 (74)3.2.3编译与运行程序 (79)3.3CCS工程导入和编译步骤 (79)3.4开启多线程编译 (86)3.5添加自动生成NAND FLASH烧写.ais文件 (88)4 基于StarterWare的Demo例程演示 (92)4.1DEMO——综合例程 (94)4.2GPIO_LED——GPIO输出(LED灯) (98)4.3GPIO_KEY——GPIO输入(按键中断) (98)4.4GPIO_KEY_EDMA——按键触发EDMA事件 (99)4.5GPIO_KEY_TIMER_EventCombine——按键及定时器中断 (101)4.6TIMER——定时器 (101)4.7TIMER_Dual_32-bit_Chained——关联32-bit模式定时器/计数器 (102)4.8TIMER_Dual_32-bit_UnChained——独立32-bit模式定时器/计数器 (104)4.9TIMER_Dual_32-bit_UnChained_4-bit_Prescaler——独立32-bit模式/额外4-bit分频定时器/计数器 (106)4.10UART0_INT——UART0串口中断收发 (108)4.11UART1_POLL——UART1串口查询收发 (110)4.12UART2_INT——UART2串口中断收发 (111)4.13UART2_EDMA——EDMA串口收发 (112)4.14RS485——RS485串口查询收发 (113)4.15TL_MULTUART_INT——多串口模块(查询方式) (114)4.16TL_MULTUART_POLL——多串口模块(中断方式) (116)4.17IIC_EEPROM——IICEEPROM读写 (117)4.18SPI_FLASH——SPI FLASH读写 (118)4.19SPI_EDMA_FLASH——SPI FLASH读写测试 (119)4.20SPI_DAC_AD5724——4通道DAC模块(模拟SPI总线) (120)4.21SPI_DAC_AD5724v2——4通道DAC模块(SPI总线) (124)4.22WatchDog——看门狗 (124)4.23NMI——不可屏蔽中断 (125)4.24PWM——高精度脉冲宽度调制器PWM输出 (125)4.25ECAP_APWM——增强型捕获模块ECAP辅助输出 (127)4.26PWM_ECAP——增强型捕获模块ECAP捕获 (130)4.27RTC——RTC时钟 (132)4.28LCD——LCD显示 (133)4.29VGA——VGA显示 (135)4.30LCD_TOUCH_4INCH3——4.3寸触摸屏 (136)4.31LCD_TOUCH——7寸触摸屏 (138)4.32LCD_TOUCH_5INCH6/10INCH4/12INCH/15INCH——多种尺寸触摸屏 (138)4.33GRLIB_DEMO——StarterWare图形库控件 (140)4.34MMCSD——SD卡读写 (140)4.35SATA——SATA枚举测试 (141)4.36USB_DEV_BULK——USB OTG从方式(USB BULK管道通信) (141)4.37USB_DEV_MSC——USB OTG从方式(虚拟存储设备) (150)4.38USB_DEV_SERIAL——USB OTG从方式(USB虚拟串口) (160)4.39USB_HOST_KEYBOARD——USB OTG主方式(USB键盘) (163)4.40USB_HOST_MOUSE——USB OTG主方式(USB鼠标) (163)4.41USB_HOST_MSC——USB OTG主方式(U盘内容查看) (165)4.42ENET_HTTPD——网络Web服务器 (166)4.43ENET_HTTPD_RMII——网络Web服务器(使用RMII接口) (169)4.44ENET_ECHO——网络Socket通信 (171)4.45AUDIO_LINE_OUT——Line Out音频输出(EMDA方式) (177)4.46AUDIO_LINE_OUT_INTR——Line Out音频输出(中断方式) (182)4.47AUDIO_LINE_OUT_POLL——Line Out音频输出(查询方式) (183)4.48AUDIO_LINE_OUT_WAV——Line Out音频输出(导入文件方式) (184)4.49AUDIO_MIC_IN——Mic In音频输入(EMDA方式) (187)4.50AUDIO_MIC_IN_INTR——Mic In音频输入(中断方式) (188)4.51AUDIO_MIC_IN_POLL——Mic In音频输入(查询方式) (189)4.52AUDIO_MIC_IN_SAVEMEM——Mic In音频输入(保存文件方式) (189)4.53AUDIO_MIC_IN_WAVE——Mic In音频输入(波形输入方式) (195)4.54AUDIO_LINE_IN——Line In音频输入(EMDA方式) (198)4.55AUDIO_LINE_INTR——Line In音频输入(中断方式) (199)4.56AUDIO_LINE_POLL——Line In音频输入(查询方式) (200)4.57AUDIO_LINE_IN_SAVEMEM——Line In音频输入(保存文件方式) (201)4.58AUDIO_LINE_IN_WAVE——Line In音频输入(波形输入方式) (206)4.59McBSP——McBSP总线数据收发 (209)4.60VPIF_OV2640——VPIF总线CMOS摄像头数据采集 (211)4.61Memory_Benchmark——内存读写速度测试 (213)4.62NandFlash——NAND FLASH读写测试 (213)4.63EMIF_AD7606——EMIFA总线8通道并口AD数据采集 (215)4.64EMIF_AD7606v2——EMIFA总线8通道并口AD数据采集 (219)4.65EMIF_AD7606_10K——使用CPU采集方式按10k速度采样 (222)4.66EMIF_AD7606_200K_EDMA——使用EDMA方式按200k采样率进行采样 (223)4.67EMIF_AD7656——EMIFA总线6通道并口AD数据采集 (224)4.68EMIF_AD7656v2——EMIFA总线6通道并口AD数据采集 (227)4.69EMIF_AD8568——EMIFA总线8通道并口AD数据采集 (229)4.70EMIF_AD8568v2——EMIFA总线8通道并口AD数据采集 (231)4.71EMIF_AD8568_100K——以100 KHz采样AD8568 8通道AD数据 (235)4.72EMIF_FPGA——EMIFA总线FPGA读写测试 (238)4.73EMIF_FPGA_DMA——EMIFA总线FPGA读写测试(经过EDMA优化) (240)4.74EDMA3——EDMA3一维数据传输 (242)4.75EDMA3_TRANSPOSE——EDMA3二维数据传输 (243)4.76uPP_B_TO_A——uPP总线FPGA读写测试 (244)4.77uPP_2CH——uPP板间双通信测试 (248)4.78TL2515_CAN——双CAN通信测试 (250)4.79TL5147_VGA——复合视频输入VGA显示测试 (252)4.80TL5147_LCD——复合视频输入LCD显示测试 (254)4.81TL5147_LCD_2CH——复合视频双通道输入LCD显示测试 (257)4.82H264Encoder——编码例程测试 (258)4.83NRF24L01——2.4G无线模块测试 (262)4.84HC-SR04——超声波测距测试 (265)4.85DHT11——温湿度传感器测试 (267)4.86WIFI_UART——串口WIFI模块测试 (269)4.87RFID——RFID射频识别测试 (273)4.88ECAP_REMOTE——红外遥控测试 (275)4.89BTUART——串口蓝牙模块测试 (277)4.90MPU6050——三轴加速陀螺仪测试 (279)4.91ZIGBEE——串口转Zigbee无线测试 (282)4.92ClockOut——时钟频率测试 (284)4.93DSPClockSpeed——CPU时钟测试 (287)4.94Fsfat——SD卡读写测试 (288)4.95SPI0——SPI0测试例程 (289)4.96UART2_INT_FIFO——UART2 FIFO中断模式 (291)4.97TL5147_LCD_3CH_Multi——TL5147摄像头实现3路图片采集 (292)4.98TL5147_LCD_2CH_SYNC——双路5147摄像头同时采集显示 (295)4.99EDMA3_LINK——EDMA链接工作方式 (296)4.100EDMA3_LED——EDMA方式让LED闪烁 (297)4.101EMIF_AD7606_PinBoard——EMIF拓展板测试 (297)5 基于SYS/BIOS的Demo例程演示 (300)5.1Board——综合例程 (300)5.2GPIO_LED——任务 (306)5.3GPIO_LED_MUTEX——抢占式多任务 (306)5.4GPIO_LED_STATIC——静态创建任务 (307)5.5Semaphore_Binary——二进制信号量 (311)5.6Semaphore_Counting——计数型信号量 (312)5.7Clock——时钟 (313)5.8Timestamp——SYS/BIOS时间戳(通用) (313)5.9Timestamp_C674x——SYS/BIOS时间戳(专用) (314)5.10Timer——定时器(通用) (314)5.11Timer_C674x——定时器(专用) (316)5.12Timer_C674x_Runtime——定时器(动态创建) (316)5.13Timer_C674x_Runtime_Reload——定时器(动态创建、更改定时周期) (317)5.14HWI_C674x——硬件中断(HWI设备专用组件) (317)5.15HWI_C674x_Hook——硬件中断(HWI挂钩函数) (318)5.16HWI_C674x_Nest——硬件中断(HWI中断嵌套) (319)5.17HWI_Runtime——硬件中断(HWI) (319)5.18HWI_Runtime_Post_SWI——硬件中断(HWI发布软件中断) (319)5.19HWI_Runtime_Post_Task——硬件中断(HWI触发任务) (320)5.20SWI——软件中断(静态配置) (320)5.21SWI_Runtime——软件中断(SWI) (322)5.22SWI_Runtime_Post_Conditionally_andn——软件中断(有条件触发ANDN)3225.23SWI_Runtime_Post_Conditionally_dec——软件中断(有条件触发DEC) (323)5.24SWI_Runtime_Post_Unconditionally_or——软件中断(无条件触发OR) (323)5.25MEMORY——内存分配 (324)5.26MMCSD——SD卡RAW模式 (325)5.27MMCSD_FatFs——SD卡FAT文件系统 (328)5.28UART1——UART1串口查询收发 (330)5.29UART2——UART2串口查询收发 (332)5.30UART2_INT——UART2串口中断接收 (333)5.31AudioLineInSave——Line In音频输入与保存 (334)5.32AudioMicInSave——MicIn音频输入与保存 (334)5.33AudioPlayMP3——MP3音频播放(SD卡) (335)5.34AudioPlayWAV——WAV音频播放(SD卡) (335)5.35LCD_TOUCH——触摸屏 (336)5.36TCP_Client——TCP客户端 (337)5.37TCP——TCP服务器 (344)5.38UDP——UDP通信 (348)5.39TCP_Benchmark——TCP发送/接收速度测试 (351)5.40Telnet——Telnet协议 (355)5.41Telnet——TFTP协议 (362)5.42WebServer——网络Web服务器 (368)5.43NDK_UIA——基于网络传输的系统分析 (376)5.44NDK_Runtime——网络Web服务器(支持串口输入IP) (384)5.45WebServer_RMII——网络Web服务器(使用RMII接口) (387)5.46WebServer_Audio_Video——Web服务器音视频实验 (395)5.47MJPEG_Streamer——IP Camera网络摄像头 (399)5.48RawSocket——以太网数据链路层通信 (402)5.49EDMA3——EDMA3一维数据传输 (413)5.50McBSP_LoopBack——McBSP内部回环测试 (414)5.51McBSP——McBSP外部回环测试 (415)5.52Gate——SYS/BIOS门保护 (416)5.53Queue——SYS/BIOS队列 (416)5.54Event——SYS/BIOS事件模块 (417)5.55Mailbox——SYS/BIOS邮箱通信 (418)5.56SLEEP——CPU低功耗模式 (418)5.57VFSCALE——动态调频调压测试 (419)5.58uPP_B_TO_A——uPP回环测试 (420)5.59ADS1278_uPP——AD模块采集测试(使用uPP) (423)5.60伺服电机测试——通过DSP与FPGA控制伺服电机运行 (424)6 算法Demo例程演示 (426)6.1FIR——有限长单位冲激响应滤波器 (426)6.2IIR——无限脉冲响应数字滤波器 (432)6.3Matrix——矩阵运算 (437)6.4FFT——快速傅里叶变换/逆变换 (439)6.5FFT_Benchmark——快速傅里叶变换/逆变换(打开/关闭缓存速度对比). 4426.6FFT_DIT2——基2时间抽取快速傅里叶变换/逆变换(原址计算) (465)6.8RGB2Gray——RGB24图像转灰度 (471)6.9HIST——灰度图像直方图 (475)6.10InteEqualize——直方图均衡化 (484)6.11ImageReverse——图像反色 (493)6.12Canny——边缘检测 (499)6.13Threshold——灰度图像二值化 (505)6.14LinerTrans——灰度图像线性变换 (512)6.15Zoom——图像缩放 (519)6.16Rotate——图像旋转 (525)6.17MATH——数学函数库 (532)6.18UniversalCopy——基于Codec Engine的数据复制算法 (533)6.19MP3Decode——MP3解码 (534)6.20MP3Decode_SD——MP3解码(使能缓存及通过SD存取) (535)6.21AACLCDecode——AACLCDecode AAC解码 (538)6.22AACHEv2Decode——AACHEv2Decode AAC解码 (539)6.23AACLCEncode——AACLCEncode AAC编码 (541)6.24G711ADecode——G711A率语音编码 (542)6.25G711ADecode——G711A率语音解码 (543)6.26ImageProcess——数字识别 (545)6.27FaceDetect——人脸识别跟踪 (548)6.28ImageProcessQR——二维码扫描 (549)6.29ImageProcessChar——文字识别 (553)6.30ImageProcessAlph——字母识别 (556)6.31Plate Recognition Demo——车牌识别 (559)7 基于TL-EasyBox实验板Demo例程演示 (569)7.1BUZZER——蜂鸣器 (570)7.2MATRIX_KEY——4x4键盘 (570)7.3DAC_TLC5615——DAC输出 (571)7.4EMIF_AD7606——EMIFA总线8通道并口AD数据采集 (573)7.6DCMOTOR——直流电机 (575)7.7STEPPERMOTOR——步进电机 (576)7.8EASYBOX_DEMO——实验板综合测试 (577)8 基于PRU的Demo例程演示 (579)8.1PRU_GPIO_LED——PRU控制GPIO输出 (583)8.2PRU_GPIO_KEY——PRU控制GPIO输入 (583)8.3PRU_TL5724_DAC——PRU驱动DAC输出测试 (583)8.4PRU_TL5724_DACv2——PRU控制AD5724输出连续波形 (585)8.5PRU_TL7606_ADC——PRU触发ADC采集模拟量 (588)8.6PRU_TL8568_ADC——PRU触发ADC采集模拟量 (590)8.7PRU_uPP_B_TO_A——PRU控制uPP传输数据 (591)8.8PRU_AD8568_SAVE——PRU控制AD8568采集数据存储SD卡 (595)8.9PRU_TIMER2_POLL——PRU控制定时器 (596)8.10PRU to DSP_Interrupt——PRU向DSP发送中断 (596)9 其它Demo例程演示 (597)9.1GPIO_LED_Assembly——GPIO输出(标准汇编) (597)9.2GPIO_LED_LinearAssembly——GPIO输出(线性汇编) (597)9.3GPIO_LED_C++——GPIO输出(C++) (597)9.4GPIO_KEYv2——不使用StarterWare函数库中断例程 (597)9.5GPIO_LED_C_Mix——C语言调用线性汇编、汇编语句及函数 (598)9.6GPIO_LED_C++_Mix——C++语言调用C语言、线性汇编、汇编语句及函数 598附录A (599)1TMS320C6748开发板准备测试开发板硬件将开发板的UART2连接到PC机。

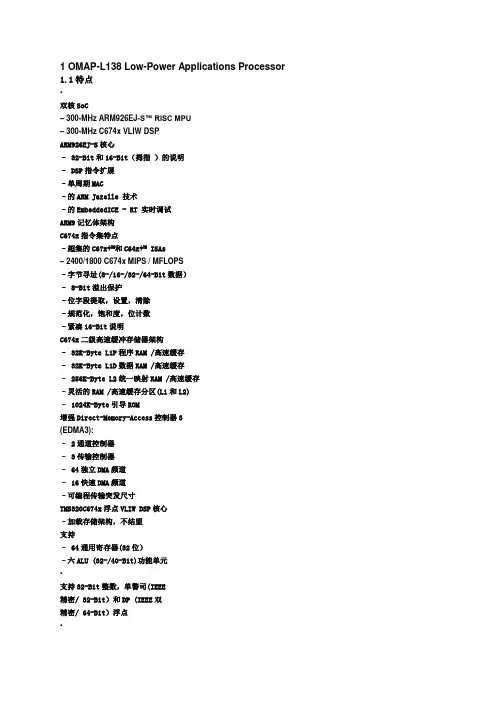

1 OMAP-L138 Low-Power Applications Processor 1.1特点•双核SoC– 300-MHz ARM926EJ-S™ RISC MPU– 300-MHz C674x VLIW DSPARM926EJ-S核心– 32-Bit和16-Bit(拇指)的说明– DSP指令扩展–单周期MAC–的ARM Jazelle 技术–的EmbeddedICE - RT 实时调试ARM9记忆体架构C674x指令集特点–超集的C67x+™和C64x+™ ISAs– 2400/1800 C674x MIPS / MFLOPS–字节寻址(8-/16-/32-/64-Bit数据)– 8-Bit溢出保护–位字段提取,设置,清除–规范化,饱和度,位计数–紧凑16-Bit说明C674x二级高速缓冲存储器架构– 32K-Byte L1P程序RAM /高速缓存– 32K-Byte L1D数据RAM /高速缓存– 256K-Byte L2统一映射RAM /高速缓存–灵活的RAM /高速缓存分区(L1和L2)– 1024K-Byte引导ROM增强Direct-Memory-Access控制器3(EDMA3):– 2通道控制器– 3传输控制器– 64独立DMA频道– 16快速DMA频道–可编程传输突发尺寸TMS320C674x浮点VLIW DSP核心–加载存储架构,不结盟支持– 64通用寄存器(32位)–六ALU (32-/40-Bit)功能单元•支持32-Bit整数,单警司(IEEE精密/ 32-Bit)和DP (IEEE双精密/ 64-Bit)浮点•最多支持四个SP的每添置时钟,每DP 2添置四时钟•最多支持两个浮动值(SP或DP)倒数逼近(RCPxP)和平方根倒数近似(RSQRxP)运营每个周期–两个乘法功能单位•混合浮点精度IEEE多点支撑高达:– 2 SP的x SP的SP的每个时钟->– 2 SP的x ->每两个时钟SP的DP– 2 SP的x DP每3个时钟-> DP– 2 DP x DP每4个时钟周期-> DP•不动点乘以支持两个32 x32-Bit相乘,四16 x 16-Bit相乘,或八8 x 8-Bit相乘每时钟周期的,复杂的倍数–指令包装减少了代码尺寸–所有条件指令–循环硬件支持的模操作–保护模式运行–支持异常错误检测和程序重定向软件支持–德州仪器DSP/BIOS™–芯片支持库和DSP图书馆128K-Byte内存共享内存1.8V或3.3V的LVCMOS IOs(除USB和DDR2接口)两个外部存储器接口:– EMIFA界面或非(8-/16-Bit-Wide数据)NAND (8-/16-Bit-Wide数据)16-Bit SDRAM的地址与128 MB空间– DDR2 /移动DDR内存控制器16-Bit随着DDR2 512 MB的SDRAM地址空间或•16-Bit随着mDDR 256 MB的SDRAM地址空间三个可配置16550类型UART模块:–带有调制解调器控制信号– 16-byte FIFO– 16x或13x过采样方案LCD控制器两个串行外设接口(SPI)每具有多个片选两个多媒体卡(MMC) /安全数字(SD)与安全数据卡接口的I / O(SDIO)接口两个主/从内部集成电路(I2CBus™)一个主机端口(HPI) Interface 16-Bit-Wide 复用地址/数据总线高带宽USB 1.1 OHCI(主机)和集成PHY(USB1)USB随着综合2.0 OTG PHY (USB0)港口– USB 2.0 High- /全速客户– USB 2.0 High- / Full- /低速主机–终点0(管制)–终点1,2,3,4(控制,批量,中断或ISOC) Rx和Tx一个多通道音频串行端口:–发送/接收时钟高达50 MHz–两个时钟区域和16 Pins串行数据–支持TDM, I2S,和类似格式–秩能够– FIFO用于接收和发送缓冲区两个多通道缓冲串行端口:–发送/接收时钟高达50 MHz–两个时钟区域和16 Pins串行数据–支持TDM, I2S,和类似格式– AC97音频编解码器接口–电信接口(ST段总线,H100)– 128-channel TDM– FIFO用于接收和发送缓冲区10/100 Mb / s以太网的MAC (EMAC):– IEEE 802.3标准– MII媒体独立接口– RMII简化媒体独立接口–管理数据I / O模块(MDIO)视频端口接口(VPIF):–两个8-bit SD (BT.656),或单16-bit单视频采集原料(8-/10-/12-bit)频道–两个8-bit SD (BT.656),单16-bit视频显示通道通用并行端口(uPP):–高速并行接口FPGA和数据转换器–数据对两个通道,每个通道宽度为8-到16-bit包容–单数据传输速率或双数据速率转移–支持多接口与START,ENABLE和wait控制串行ATA (SATA)控制器:–支持SATA I (1.5 Gbps)和SATA II (3.0 Gbps)–支持所有SATA电源管理特点–硬件辅助本地命令排队(NCQ)条目最多32–支持端口倍增器和基于命令的开关实时时钟32 kHz振荡器和独立电源导轨三64-Bit通用定时器(作为两个32-Bit定时器配置)一64-Bit通用定时器(观看狗)两个增强型脉宽调制器(eHRPWM):–专用16-Bit时基计数器周期和频率控制– 6单边,6偶棱边对称或3非对称双输出的边缘–死区产生– PWM经高频斩波载波–旅游区输入三32-Bit增强型捕捉模块(eCAP):–作为3捕捉输入或3配置辅助脉冲宽度调制(APWM)输出–多达四个单镜头捕捉事件时间标记361-Ball Pb-Free塑料球栅阵列(PBGA) [ZCE后缀],0.65-mm球间距361-Ball Pb-Free塑料球栅阵列(PBGA) [ZWT后缀],0.80-mm球间距商业或扩展温度1.3描述该器件是一种低功率应用处理器上ARM926EJ-S™和C674x DSP核心为基础.这提供了比对TMS320C6000™ DSPs.平台上的其他成员显着降低功耗该设备使OEMs和ODMs迅速向市场推出具有强大的经营设备系统支持,丰富的用户界面,高处理性能寿命通过最大灵活的完全集成的混合处理器解决方案.该装置的双核架构提供了两个DSP和精简指令集的好处计算机(RISC)技术,集成了高性能TMS320C674x DSP核心和一ARM926EJ-S核心.该ARM926EJ-S是32-bit RISC处理器核心执行32-bit或16-bit指示流程32-bit, 16-bit,或8-bit数据.核心uses流水线,使处理器的所有部件和内存系统可以连续工作制.ARM内核有一个协处理器15 (CP15),保护模块,数据和程序存储器管理单位(MMUs)与查表预留缓冲区.它有独立的指令和16K-byte16K-byte数据高速缓存.两者都是四路虚拟与虚拟索引标签关联(VIVT). ARM内核也有一个8KB内存(矢量表)和64KB ROM.该DSP两级缓存的架构设备uses核心.该级别1程序缓存(L1P)是32KB直接映射的缓存和数据缓存1水平(L1D)是32KB 2-way组相联高速缓存.该级别2程序缓存(L2P)一个256KB内存空间,包括在方案和共享数据空间. L2也有一个引导1024KB ROM.内存可以为映射内存,缓存配置L2,两个或组合.虽然DSP L2由ARM和访问系统中的其他主机,一额外128KB内存共享内存是供其他主机可使用不影响DSP性能.外设集包括:一10/100 Mb / S的一个管理数据输入以太网的MAC (EMAC) /输出(MDIO)模块;一USB2.0 OTG接口;一USB1.1 OHCI接口,两个内部集成电路(I2C)总线接口,一个多通道音频串行端口16串行FIFO缓冲区(McASP);二多通道缓冲串行端口(McBSP的)与FIFO缓冲器;二SPI多个芯片接口选择;四64-bit通用定时器每个配置(一配置为看门狗);一配置16-bit主机接口(HPI) ;高达9的16通用输入/输出pins银行(GPIO)可编程中断/事件生成与其他外设复用模式;三UART接口(与 RTS和CTS);二每种增强高解析度脉冲宽度调制器(eHRPWM)外设; 3 32-bit增强(eCAP)捕获外设模块可配置作为3捕捉输入或3辅助脉宽调制(APWM)产出; 2外部存储器接口:异步和SDRAM外部存储器接口速度较慢的记忆或(EMIFA界面)外设和更高的速度DDR2 /移动DDR控制器.以太网媒体访问控制器(EMAC)之间提供了一个有效的接口设备和网络.该EMAC支持10Base-T和100Base-TX,或10 Mbits /秒(Mbps)和100 Mbps 无论在哪一种半双工或全双工模式.另外一个管理数据输入/输出接口(MDIO)可用于PHY配置.该EMAC支持MII和RMII接口.该SATA控制器提供高速接口,海量数据存储设备.控制器的SATA同时支持SATA I (1.5 Gbps)和SATA II (3.0 Gbps).通用并行端口(uPP)提供高速数据转换器接口种类很多,FPGA或其它并行设备.该UPP支持在8-宽度上可编程数据16-bits每两个通道.单日的汇率和双倍数据率传输的支持以及启动,ENABLE和等待信号提供的数据转换器的各种控制.一个视频端口接口(VPIF)是包括提供一个灵活的视频输入/输出端口丰富的外设集提供了能够控制外围设备和沟通外部处理器.对每一个细节的外设,请相关部门在本文件稍后以及相关的外设参考指南.该装置有一个ARM和DSP.一套完整的开发工具,其中包括C编译器,DSP 汇编优化程序,简化规划和调度,和Windows 调试器接口为了深入源代码执行的知名度3.3设备兼容性该ARM926EJ-S RISC CPU与其他ARM9 CPUs从ARM控股plc.兼容该C674x DSP核心是代码与C6000™ DSP平台兼容,并支持这两种功能在C64x+和C67x+ DSP家庭.3.4的ARM子系统ARM的子系统包括以下功能:ARM926EJ-S RISC处理器ARMv5TEJ (32/16-bit)指令集小尾数系统控制协处理器15 (CP15)MMU16KB指令缓存16KB数据缓存写缓冲器嵌入式跟踪模块和嵌入式跟踪缓冲区(ETM/ETB)ARM的中断控制器3.4.1ARM926EJ-S RISC CPUARM的子系统集成的ARM926EJ-S处理器.该ARM926EJ-S处理器是会员ARM9 系列通用微处理器.该处理器是针对多任务应用程序在完整的记忆体管理,高性能,低电路小片尺寸,低功耗都是重要的.该ARM926EJ-S处理器支持ARM和32-bit 16位Thumb指令sets,使用户能够取舍之间的高性能和高代码密度.具体来说,ARM926EJ-S处理器支持ARMv5TEJ指令集,其中包括对Java字节代码执行效率的特点,提供Java性能相近的时(JIT) Java解释以获得公正,但没有相关的代码开销.该ARM926EJ-S处理器支持ARM调试架构,包括逻辑,以协助双方硬件和软件调试.该ARM926EJ-S处理器有一个哈佛架构,并提供一完整的高性能子系统,包括:ARM926EJ -S整数核心CP15系统控制协处理器存储器管理单元(MMU)独立指令和数据高速缓存写缓冲器独立指令和数据(内部RAM)接口独立指令和数据接口AHB 总线嵌入式跟踪模块和嵌入式跟踪缓冲区(ETM/ETB)有关ARM9,更完整的细节请参考ARM926EJ-S技术参考手册,可3.4.2CP15该系统控制协处理器ARM926EJ-S (CP15)是用来配置和控制指令和数据缓存,存储器管理单元(MMU),和其他ARM子系统功能.寄存器的CP15使用MRC的编程和MCR ARM指令,当在特权模式下,如ARM公司主管或系统模式.3.4.3MMU一二级页表存储在主存储器单套用于控制地址转换,权限检查和内存区域的属性数据和指令访问.该MMU uses一一个统一的翻译后备缓冲区(TLB)缓存在页表掌握的信息.该MMU特点是:标准的ARM架构v4和v5 MMU映射的大小,域和访问保护方案.测绘尺寸是:– 1MB(段)– 64KB(大页)– 4KB(小页)– 1KB(小页)大页面和小网页的访问权限可以单独指定每个季度该页面(子页面的权限)Hardware page table walks整个TLB,无效使用CP15 寄存器 8无效TLB项,由MVA,选择使用CP15 寄存器 8锁定的TLB项,使用CP15 寄存器 103.4.4高速缓存和写缓冲器该指令的高速缓存的大小是16KB,数据高速缓存16KB.此外,缓存有以下特点:虚拟索引,虚拟标记,并采用修正的解决虚拟地址(MVA)4路组相联,与一个八个字缓存行,每行,每行(32-bytes长度),并与两脏bits在DcacheDcache支持直写和回写(或复制回)缓存的操作,按内存选择地区使用在C转换表的B和bits MMU关键单词的第一个缓存加气站缓存锁定寄存器使控制哪些缓存ways是分配用于行填充,同时提供一个锁定机制,控制缓存腐败Dcache存储物理地址TAG(每年TAG)的对应每个条目在标记Dcache内存高速缓存行期间写的挫折,除了在存储到虚拟地址标签的使用标签RAM.这意味着MMU不Dcache写回行动的,删除可能错过的TLB相关的回写地址.缓存失效维修业务提供高效的,整个Dcache或Icache,地区在Dcache或Icache,和虚拟内存区域.写缓冲区用于所有写入noncachable bufferable地区,写,写通过区域门柱回写的地区.一个单独的缓冲区纳入Dcache举行写回高速缓存行驱逐或脏缓存行清洗.主要写缓冲区有16-word数据缓冲区和一四个地址的缓冲区.该Dcache回写数据字有八个项目和一个地址表项3.4.5先进的高性能总线 (AHB)ARM的子系统uses的AHB ARM926EJ-S端口连接到配置了ARM和总线外部存储器.仲裁者是聘请独立的仲裁获得了由D-AHB和I-AHB配置总线和总线外部存储器.3.4.6嵌入式跟踪宏单元(ETM)和嵌入式跟踪缓冲区(ETB)为了支持实时跟踪,ARM926EJ-S处理器提供了一个接口,使一个连接嵌入式跟踪宏单元(ETM).中ARM926ES-J OMAP-L138子系统还包括嵌入式跟踪缓冲区(ETB).的ETM由两部分组成:跟踪端口提供了实时跟踪能力的ARM9.触发器触发设施提供资源,其中包括地址和数据比较器,计数器,和音序器.跟踪端口的OMAP-L138不固定了,是不是只能连接到嵌入式跟踪缓冲区.该ETB有4KB缓冲存储器. ETB启用调试工具是必需的读/捕获的解释跟踪数据3.4.7ARM存储器映射默认情况下,ARM已经获得最上和片外存储器领域,包括内部的DSP回忆,EMIFA界面; DDR2,和额外128K字节片上共享SRAM.同样,几乎所有的片上外设的访问默认情况下,ARM的.见表3-3一个详细的顶级OMAP-L138内存映射,其中包括ARM存储器空间3.5 DSP子系统该DSP子系统包括以下功能:C674x DSP CPU32KB L1计划(L1P)32KB) /高速缓存(高达32KB L1资料(L1D)32KB) /高速缓存(高达256KB统一映射RAM /高速缓存(L2)1MB面膜可编程ROM小尾数3.5.1C674x DSP CPU描述中央处理单元的C674x (CPU)包括八个功能单元,两个寄存器文件和两个数据路径所示图3-2.这两个通用寄存器文件(A和B)每个包含32 32-bit登记册登记的64总计.在通用寄存器可用于数据或可数据地址指针.支持的数据类型包括包装8-bit数据,数据压缩16-bit,32-bit数据,40-bit数据和64-bit数据.值大于32 bits,如40-bit-long或64-bit-long值存储在寄存器对,随着放置在更寄存器数据32 LSBs,其余8或32 MSBs在未来上寄存器(总是奇数寄存器).八(.M1, .L1, .D1, .S1, .M2, .L2, .D2,和.S2)功能单位是每个有能力执行一每个时钟周期的指令.该.M职能单位执行所有乘法运算.单位的.S和.L执行算术,逻辑一般设置和分支功能.该.D单位主要负荷数据从内存到内存寄存器文件寄存器文件和存储结果.Each C674x .M单位可以执行下列其中一个每个时钟周期:一32 x 32位相乘,一16 x 32位相乘,二16 x 16位乘法,两个16 x 32位乘法,两个16 x 16位乘法和加/减功能,四8 x 8位乘法,四8 x 8位乘法与添加操作,四16 x 16乘与加/减功能(包括复杂的乘法).也有支持伽罗瓦的8-bit和32-bit数据域乘法.许多通信和算法,如FFTs调制解调器需要复杂的乘法.复杂的乘法(CMPY)需要输入指令16-bit并产生一种32-bit真实与虚构32-bit输出.也有复杂的乘法与四舍五入能力,产生一个32-bit包装输出,包含16-bit真实和16-bit虚值.该32 x 32位乘法指令扩展精度提供了高精确度的算法必要的一个符号和无符号32-bit各种数据类型.该.L或(算术逻辑单元)结合的能力,现在做并行加法/减法操作上对常见的输入.此指令的版本存在上班32-bit数据或对数据的16-bit执行双16-bit添加和并行减去.也有饱和这些指令形式.增强了核心的C674x于前几个.S内核的ways.单位,双16-bit MIN2和MAX2比较是只在.L单位.在C674x核心它们也可用在.S单位这增加了算法的性能做搜索和排序.最后,为了提高数据包装和拆包吞吐量,.S单元可以持续的高性能的四8-bit/16-bit和双16-bit指示.解压说明准备平行8-bit行动16-bit数据.包并行指令返回结果输出精度,包括饱和的支持.其他新功能包括:SPLOOP-中的一个小的CPU aids指令流水线的软件创建循环缓冲区在一个循环的多次迭代的并行执行.该SPLOOP缓冲降低了代码尺寸与软件流水.此外,在SPLOOP缓冲区循环是完全中断.紧凑型说明-为C6000设备的原生指令长度是32 bits.许多常见的如MPY,与,或,添加和SUB指令可以表示为16 bits如果C674x编译器可以限制代码以使用在寄存器文件的特定寄存器.这种压缩是执行的代码生成工具.指令集增强-如上所述,有新的指令,如32-bit乘法运算,复数乘法,包装,分拣,位操作,并32-bit伽罗瓦场乘法.异常处理-旨在帮助bugs.孤立的C674x CPU程序员能够异常检测和响应,无论是从国内检测来源(如非法操作码)和从系统事件(如看门狗时间到期).特权-定义用户和业务主管模式,让作业系统提供一个基层敏感资源的保护.本地内存被划分成多个页面,每个读,写和执行权限。

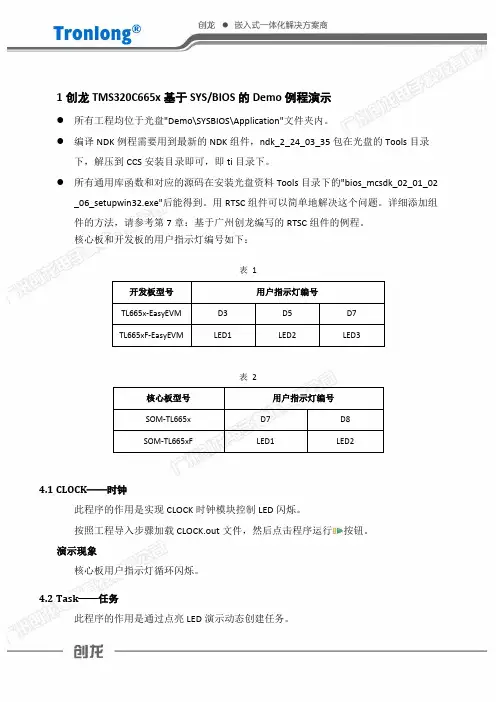

1创龙TMS320C665x基于SYS/BIOS的Demo例程演示●所有工程均位于光盘"Demo\SYSBIOS\Application"文件夹内。

●编译NDK例程需要用到最新的NDK组件,ndk_2_24_03_35包在光盘的Tools目录下,解压到CCS安装目录即可,即ti目录下。

●所有通用库函数和对应的源码在安装光盘资料Tools目录下的"bios_mcsdk_02_01_02_06_setupwin32.exe"后能得到。

用RTSC组件可以简单地解决这个问题。

详细添加组件的方法,请参考第7章:基于广州创龙编写的RTSC组件的例程。

核心板和开发板的用户指示灯编号如下:表 1开发板型号用户指示灯编号TL665x-EasyEVM D3 D5 D7TL665xF-EasyEVM LED1 LED2 LED3表 2核心板型号用户指示灯编号SOM-TL665x D7 D8SOM-TL665xF LED1 LED24.1CLOCK——时钟此程序的作用是实现CLOCK时钟模块控制LED闪烁。

按照工程导入步骤加载CLOCK.out文件,然后点击程序运行按钮。

演示现象核心板用户指示灯循环闪烁。

4.2Task——任务此程序的作用是通过点亮LED演示动态创建任务。

按照工程导入步骤加载Task.out文件,然后点击程序运行按钮。

演示现象底板用户指示灯循环点亮5次。

4.3Task_Mutex——抢占式多任务此程序的作用是通过点亮核心板板LED演示抢占式多任务线程。

按照工程导入步骤加载Task_Mutex.out文件,然后点击程序运行按钮。

演示现象核心板用户指示灯循环点亮,点亮循序如下:TL665x-EasyEVM:核心板D8先闪烁1次,然后D7再闪烁6次。

TL665xF-EasyEVM:核心板LED2先闪烁1次,然后LED1再闪烁6次。

先闪烁用户灯为高优先级,后闪烁用户灯为低优先级。

TMS320C6000DSP外设概览参考指南文献编号:ZHCU001H2005年3月内容目 (3)商 (5)1概述 (6)2引导模式和配置 (10)3增强直接存储器存取(EDMA)控制器 (10)4以太网媒体接入控制器(EMAC)/管理数据输入/输出(MDIO)模块 (10)5扩展总线(XBUS) (10)6外部存储器接口(EMIF) (11)7通用输入/输出(GPIO) (11)8主机端口接口(HPI) (12)9内部集成电路(I2C)模块 (12)10中断选择器 (13)11多通道音频串行端口(McASP) (13)12多通道缓冲串行端口(McBSP) (14)13外设组件互连(PCI) (14)14锁相环(PLL)控制器 (15)15程序和数据存储器控制器/直接存储器存取(DMA)控制器 (15)16计时器 (16)17Turbo解码器协处理器(TCP) (16)18两级内部存储器 (17)19ATM的通用测试和操作PHY接口(UTOPIA) (17)20视频端口/VCXO内插控制(VIC)端口 (17)21Viterbi解码器协处理器(VCP) (18)附录A修订历史记录 (19)附表目录1TMS320C62x DSP外设文档 (7)2TMS320C64x DSP外设文档 (8)3TMS320C67x DSP外设文档 (9)A-1文档修订历史记录 (19)商标TMS320C6000,C6000,VelociTI,TMS320C62x,TMS320C64x,TMS320C67x,TMS320C2000,TMS320C5000是德州仪器(TI)的商标参考指南ZHCU001H–2005年3月TMS320C6000DSP外设概览本文概述并简要描述了TMS320C6000™系列数字信号处理器(DSP)上可用的外设。

1概述C6000™器件平台由使用先进超长指令字(VLIW)的第一代现成DSP组成,通过增加指令级并行性获得高性能。

1McBSP简介1.1McBSP概述McBSP为多通道缓冲串口(Multichannel Buffered Serial Port)的简写,共有6个引脚,发送引脚MDX、接收引脚MDR、发送时钟信号引脚MCLKX、接收时钟信号引脚MCLKR、发送帧同步引脚MFSX和接收帧同步引脚MFSR。

28335有两个McBSP模块,对应引脚如下,1.2McBSP特点McBSP具有以下几个特点:1)全双工的通讯方式;2)通过两级缓冲发送和三级缓冲接收实现连续数据流的通信;3)独立的接收与发送的帧和时钟信号;4)可配置最多128个接收和发送通道;5)数据大小和范围可选,可配置为8、12、16、20、24、32位字长;6)数据传输时可选择高低位的发送顺序;7)可编程的内部时钟和帧发生器,可编程的帧同步和数据时钟极性;McBSP内部结构如下图所示:McBSP结构图1.3McBSP中断描述1.3.1接收中断1.3.2发送中断2DMA模块寄存器2.1.1控制寄存器1——SPCR1该寄存器设置McBSP串口的数字回环模式、接收字符拓展和校验模式、ClockStop模式、DX是否允许、A-bis模式、接收中断模式等,并给很粗接受同步错误、接收移位寄存器空、接收就绪等状态位,此外该可以接收复位。

2.1.2控制寄存器2——SPCR2SPCR2设置了McBSP自由运行模式、SOFT模式、发送中断模式,并给出发送同步错误、发送移位寄存器空、发送准备好等状态位,此外还可进行发送复位、采样率发生器复位、帧同步发生电路复位。

表FREE、SOFT设置2.1.3引脚控制寄存器PCRPCR设置McBSP传输帧同步模式、接收帧同步模式、发送时钟模式、接收时钟模式、发送帧同步信号的极性、接收帧同步信号的极性、发送时钟极性、接收时钟极性,并给出CLKS、DX、DR引脚的状态。

此外PCR还定义发送和接收部分在复位时相应引脚引脚是否配置为通用I/O;2.1.4接收控制寄存器RCR1RCR1设置McBSP接收时第一相的接收帧长度(从1个字到128个字、接收字长度(8、12、16、20、24、32bits)。

DM642中EDMA结构及优化DMA(Direct Memory Access)是DSP中至关重要的一个部分,DMA可以在不需要CPU的干预的情况下,在后台执行数据的高速传输,系统效率的高低很大程度上取决与DMA的使用好坏与否。

DM642是目前公司内使用最多的DSP,其运行效率的高低决定着大部分产品的性能。

下面就DM642上的DMA性能做一个简单的介绍和分析。

DM642中的DMA称为EDMA(Enhanced Direct Memory Access),其EDMA控制器支持64个相互独立的DMA通道,每个通道都可以接受系统外设事件的触发或者CPU的指令的触发,不同DMA传输之间还可以进行连接,构成各种复杂的DMA操作,在600MHz主频时可以提供2.4GB/秒的数据吞吐量。

具备的1维、2维传输模式,非常适合图像的处理。

要想用好EDMA,需要很好的理解EDMA的传输过程。

EDMA内部划分为4个优先级,分别是Q0(Urgent)、Q1(High)、Q2(Medium)和Q3(Low),顾名思义,从0-3由高至低,4个优先级分别对应4个队列,每个队列可容纳16个传输请求,每个队列都可以被CPU和外设使用,且每个部分占用的队列单元个数可以手动设置。

每个队列都是FIFO结构,先提交的传输先执行传输操作,队列后面的操作必须等待前面的操作完成后才能够被执行,但是各个队列之间的传输可以按照优先级并行操作,当某个操作处于阻塞、等待状态时,其它队列中的任务可以得到执行。

从这个基本操作模式可以看出合理的对EDMA资源进行分配很重要,目前DM642系统中的处理如下:1、高优先级的队列中执行传输数据少但时间要求最紧迫的任务,比如CACHE操作和CPU访问操作,因为这类操作如果得不到快速的响应,会造成CPU的阻塞,严重影响CPU的性能。

2、低优先级队列中执行紧迫性不高且数据量大的传输。

比如编解码的传输,预览、缩放的传输。

因为数据量的传输会很长时间的占用DMA操作和外部总线操作,如果将其放在高优先级队列中,会使那些数据量本来很少的操作因为优先级低而长时间得不到响应,造成浪费。