计算机系统结构实验报告

- 格式:doc

- 大小:341.00 KB

- 文档页数:12

计算机体系结构实验报告实验目的:1.掌握计算机体系结构的基本概念和组成部分2.学会使用模拟器对计算机性能进行测试和优化3.理解计算机指令的执行过程和流水线工作原理4.掌握计算机性能指标的测量方法和分析技巧实验材料和工具:1.一台个人电脑2.计算机体系结构模拟器3.实验指导书和实验报告模板实验步骤:1.搭建计算机系统:根据实验指导书提供的指导,我们搭建了一个简单的计算机系统,包括中央处理器(CPU)、内存和输入输出设备。

2.编写测试程序:我们编写了一段简单的测试程序,用于测试计算机系统的性能。

3.运行测试程序:我们使用模拟器运行测试程序,并记录测试结果。

模拟器可以模拟计算机的执行过程,并提供各种性能指标的测量功能。

4.分析和优化:根据测试结果,我们对计算机系统的性能进行分析,并尝试优化系统设计和测试程序,以提高性能。

实验结果:通过测试程序的运行和性能指标的测量,我们得到了如下结果:1.计算机的时钟频率:根据模拟器显示的结果,我们得知计算机的时钟频率为1000MHz。

2. 指令执行时间:我们计算了测试程序的平均执行时间,得到了结果为5ms。

4.流水线效率:我们通过模拟器提供的流水线分析功能,得到了计算机流水线的平均效率为80%。

实验分析:根据测试结果1.提高时钟频率:通过增加时钟频率可以加快计算机的运行速度。

我们可以尝试调整计算机硬件的设计和制造工艺,提高时钟频率。

2.优化指令执行过程:我们可以通过优化指令的执行过程,减少执行时间。

例如,并行执行多个指令、增加指令缓存等。

3.提高流水线效率:流水线是提高计算机性能的关键技术,我们可以通过增加流水线级数和优化流水线结构,提高流水线效率。

4.增加并行计算能力:并行计算是提高计算机性能的重要途径,我们可以尝试增加计算机的并行计算能力,例如增加处理器核心的数量。

实验总结:通过本次实验,我们深入了解了计算机体系结构的工作原理和性能指标。

通过模拟器的使用,我们学会了对计算机性能进行测试和进行性能优化的方法。

实验一流水线中的相关一、实验目的1. 熟练掌握WinDLX模拟器的操作和使用,熟悉DLX指令集结构及其特点;2. 加深对计算机流水线基本概念的理解;3. 进一步了解DLX基本流水线各段的功能以及基本操作;4. 加深对数据相关、结构相关的理解,了解这两类相关对CPU性能的影响;5. 了解解决数据相关的方法,掌握如何使用定向技术来减少数据相关带来的暂停二、实验平台WinDLX 模拟器三、实验内容和步骤1.用WinDLX模拟器执行下列三个程序:(分别以步进、连续、设置断点的方式运行程序,观察程序在流水线中的执行情况,观察CPU中寄存器和存储器的内容。

熟练掌握WinDLX的操作和使用。

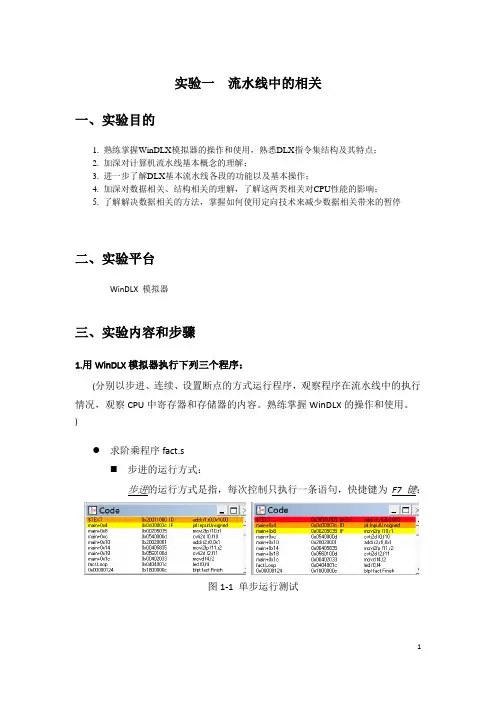

)●求阶乘程序fact.s⏹步进的运行方式:步进的运行方式是指,每次控制只执行一条语句,快捷键为F7键:图1-1 单步运行测试⏹设置断点的运行方式:鼠标点击某行,按下“Insert键”,设置断点:图1-2 设置断点图1-3 断点设置成功,按F5运行至断点⏹连续的运行方式:通过按下F5键,可直接运行至断点处;按下F8键,并在对话框内键入跳跃的步数,可以直接跳转指定的步数:图1-4 设置跳转步数●求最大公倍数程序gcm.s,观察程序在流水线中的执行情况:●求素数程序prim.s,观察CPU 中寄存器和存储器的内容2. 用WinDLX运行程序structure_d.s通过模拟找出存在资源相关的指令对以及导致资源相关的部件;记录由资源相关引起的暂停时钟周期数,计算暂停时钟周期数占总执行周期数的百分比;论述资源相关对CPU性能的影响,讨论解决资源相关的方法。

●存在资源相关的指令、导致资源相关的部件⏹两条指令同时访问寄存器f4,造成资源相关:⏹两条指令同时访问ALU,造成资源相关:●由资源相关引起的暂停时钟周期数、暂停时钟周期数占总执行周期数的百分比由资源相关引起的暂停时钟周期数:30;总执行周期数:139;暂停时钟周期数占总执行周期数的百分比:21.6%3. 在采用、以及不采用定向技术的情况下,分别用WinDLX 运行程序data_d.s(记录数据相关引起的暂停时钟周期数以及程序执行的总时钟周期数,计算暂停时钟周期数占总执行周期数的百分比;并计算采用定向技术后性能提高的倍数)●采用定向技术:(左下图)⏹计算暂停时钟周期数占总执行周期数的百分比:30/128=23.4%图3-1 采用定向技术图3-2 不采用定向技术●不采用定向技术:(右上图)⏹计算暂停时钟周期数占总执行周期数的百分比:104/202=51.5%●采用定向技术后性能提高的倍数:202/128=1.58倍四、实验总结●资源相关对CPU性能的影响、讨论解决资源相关的方法资源相关使相关指令在流水线上停滞,降低了执行效率;为解决这一问题,应在编写代码时尽量避免总是使用同一寄存器;并通过指令调度,使相关的代码执行距离拉开。

操作系统实验报告实验目的:随着操作系统应用领域的扩大,以及操作系统硬件平台的多样化,操作系统的体系结构和开发方式都在不断更新,目前通用机上常见操作系统的体系结构有如下几种:模块组合结构、层次结构、虚拟机结构和微内核结构。

为了更好的了解计算机操作系统体系结构,以及linux 的体系结构,特作此报告。

实验内容:计算机操作系统体系结构一、模块组合结构操作系统刚开始发展时是以建立一个简单的小系统为目标来实现的,但是为了满足其他需求又陆续加入一些新的功能,其结构渐渐变得复杂而无法掌握。

以前我们使用的MS-DOS 就是这种结构最典型的例子。

这种操作系统是一个有多种功能的系统程序,也可以看成是一个大的可执行体,即整个操作系统是一些过程的集合。

系统中的每一个过程模块根据它们要完成的功能进行划分,然后按照一定的结构方式组合起来,协同完成整个系统的功能。

如图1所示:在模块组合结构中,没有一致的系统调用界面,模块之间通过对外提供的接口传递信息,模块内部实现隐藏的程序单元,使其对其它过程模块来说是透明的。

但是,随着功能的增加,模块组合结构变得越来越复杂而难以控制,模块间不加控制地相互调用和转移,以及信息传递方式的随意性,使系统存在一定隐患。

二、层次结构为了弥补模块组合结构中模块间调用存在的固有不足之处,就必须减少模块间毫无规则的相互调用、相互依赖的关系,尤其要清除模块间的循环调用。

从这一点出发,层次结构的设计采用了高层建筑结构的理念,将操作系统或软件系统中的全部构成模块进行分类:将基础的模块放在基层(或称底层、一层),在此基础上,再将某些模块放在二层,二层的模块在基础模块提供的环境中工作;它只能调用基层的模块为其工作,反之不行。

严格的层次结构,第N+l层只能在N层模块提供的基础上建立,只能在N层提供的环境中工作,也只能向N 层的模块发调用请求。

在采用层次结构的操作系统中,各个模块都有相对固定的位置、相对固定的层次。

处在同一层次的各模块,其相对位置的概念可以不非常明确。

实验一流水线相关一.实验目的1. 熟练掌握WinDLX 模拟器的操作和使用,熟悉DLX 指令集结构及其特点;2. 加深对计算机流水线基本概念的理解;3. 进一步了解DLX 基本流水线各段的功能以及基本操作;4. 加深对数据相关、结构相关的理解,了解这两类相关对CPU 性能的影响;5. 了解解决数据相关的方法,掌握如何使用定向技术来减少数据相关带来的暂停。

二.实验内容1. 用WinDLX 模拟器执行下列三个程序(任选一个):求阶乘程序fact.s求最大公倍数程序gcm.s求素数程序prim.s分别以步进、连续、设置断点的方式运行程序,观察程序在流水线中的执行情况,观察CPU 中寄存器和存储器的内容。

熟练掌握WinDLX 的操作和使用。

注意:fact.s 中调用了input.s 中的输入子程序。

load 程序时,要两个程序一起装入(都select 后再点击load)。

gcm.s 也是如此。

2. 用WinDLX 运行程序structure_d.s,通过模拟:找出存在结构相关的指令对以及导致结构相关的部件;记录由结构相关引起的暂停时钟周期数,计算暂停时钟周期数占总执行周期数的百分比;论述结构相关对CPU 性能的影响,讨论解决结构相关的方法。

3. 在不采用定向技术的情况下(去掉Configuration 菜单中Enable Forwarding 选项前的勾选符),用WinDLX 运行程序data_d.s。

记录数据相关引起的暂停时钟周期数以及程序执行的总时钟周期数,计算暂停时钟周期数占总执行周期数的百分比。

4. 在采用定向技术的情况下(勾选Enable Forwarding),用WinDLX 再次运行程序data_d.s。

重复上述3 中的工作,并计算采用定向技术后性能提高的倍数。

三.实验过程和截图1.模拟执行fact.s和input.s流水线的状态如下:在执行求阶乘程序fact.s 之后,输入值5,查看寄存器的值为120,结果正确。

一、实验目的通过本次计算机系统实习,使学生了解计算机系统的基本组成和工作原理,掌握计算机系统调试和性能分析的基本方法,提高学生的实际操作能力和计算机系统维护能力。

二、实验内容1. 计算机系统组成及工作原理(1)计算机硬件系统:了解计算机硬件系统的基本组成,包括CPU、内存、硬盘、显卡、网卡等主要部件的功能和作用。

(2)计算机软件系统:了解计算机软件系统的基本组成,包括操作系统、应用程序、系统工具等。

(3)计算机工作原理:了解计算机的基本工作原理,包括数据输入、处理、存储和输出等过程。

2. 计算机系统调试(1)系统启动:了解计算机系统启动过程,包括BIOS自检、引导加载程序、操作系统启动等。

(2)系统故障排除:学习如何使用故障排除工具和技巧,对计算机系统进行故障诊断和修复。

(3)系统优化:了解如何对计算机系统进行优化,提高系统性能。

3. 计算机系统性能分析(1)性能指标:了解计算机系统性能的主要指标,如CPU、内存、硬盘、显卡等。

(2)性能分析工具:学习使用性能分析工具,如任务管理器、资源监视器等。

(3)性能优化:了解如何根据性能分析结果对计算机系统进行优化。

三、实验步骤1. 熟悉实验环境:了解实验计算机的硬件配置、操作系统版本等基本信息。

2. 熟悉实验工具:掌握实验过程中所需使用的软件和工具,如故障排除工具、性能分析工具等。

3. 实验一:计算机系统组成及工作原理(1)观察计算机硬件组成,了解各部件的功能和作用。

(2)查看计算机系统启动过程,了解BIOS自检、引导加载程序、操作系统启动等环节。

4. 实验二:计算机系统调试(1)使用故障排除工具,对计算机系统进行故障诊断和修复。

(2)根据系统启动日志,分析系统故障原因,并尝试修复。

5. 实验三:计算机系统性能分析(1)使用性能分析工具,对计算机系统进行性能分析。

(2)根据性能分析结果,对计算机系统进行优化。

四、实验结果与分析1. 实验一:通过观察计算机硬件组成和系统启动过程,掌握了计算机系统的基本组成和工作原理。

《计算机系统结构课内实验》实验报告第一次实验:记分牌算法和Tomasulo算法第二次实验:cache性能分析班级:物联网21姓名:李伟东学号:2120509011日期:2015.5.21第一次实验:记分牌算法和Tomasulo算法一、实验目的及要求1. 掌握DLXview模拟器的使用方法;2. 进一步理解指令动态调度的基本思想,了解指令动态调度的基本过程与方法;3. 理解记分牌算法和Tomasulo算法的基本思想,了解它们的基本结构、运行过程;4. 比较分析基本流水线与记分牌算法和Tomasulo算法的性能及优缺点。

二、实验环境DLXview模拟器三、实验内容1.用DLX汇编语言编写代码文件*.s(程序中应包括指令的数据相关、控制相关以及结构相关),以及相关的初始化寄存器文件*.i和数据文件*.d;2.观察程序中出现的数据相关、控制相关、结构相关,并指出三种相关的指令组合;四、实验步骤将自己编写的程序*.s、*.i、*.d装载到DLXview模拟器上,(1)分别用基本流水线、记分牌算法和Tomasulo算法模拟,针对每一种模拟做如下分析:①统计程序的执行周期数和流水线中的暂停时钟周期数;②改变功能部件数目重新模拟,观察并记录性能的改变;③改变功能部件延迟重新模拟,观察并记录性能的改变;论述功能部件数目、功能部件延迟对性能的影响。

(2)记录运行记分牌算法时的功能部件状态表和指令状态表;(3)记录运行Tomasulo算法时的指令状态表和保留站信息;五、实验结果1)基本流水线原始即加法延迟2,乘法延迟5,实验结果显示该段程序运行了11个时钟周期增加了一个除法器。

加法器延迟2,乘法器延迟5,除法器延迟19。

实验结果显示该段程序运行了11个时钟周期。

增加除法器对程序的执行无影响。

加法器延迟2,乘法器延迟6,无除法器。

实验结果显示该段程序运行了12个时钟周期乘法器的延迟对程序执行有有影响。

加法器延迟1,乘法器延迟5。

《计算机系统结构课内实验》实验报告班级:计算机15班姓名:高君宇学号:2110505112日期:2014.5.7动态分支预测实验一、实验目的及要求1. 了解掌握动态分支与推断执行技术对流水线性能的改进效果2. 了解动态分支预测的基本技术;3. 了解推断执行的基本过程;4. 比较各种分支预测技术的性能。

二、实验环境Linux、SimpleScalar Tool Set、SPEC 测试程序三、实验内容利用SimpleScalar仿真器中的分支预测仿真程序sim-pred运行所提供的三个benchmark程序,分别采用五种不同的分支预测方法,即bimod方式,two-level adaptive方式,always taken方式,always not taken方式,comb方式,并对前两种分别使用下表中两种参数配置;分析仿真器输出的关于分支预测的统计参数集,填写表格,并对各仿真器的能力给出相应说明。

命令格式为: ./sim-bpred {-option} executable_benchmark –argument 对于三种动态方法,分别说明如下:bimod是最普通的,即采用一个2bit宽的分支方向预测表,按分支地址查找,2bit分支预测器的判断和更新与课本上的一致。

这种方式只有一个参数,就是分支预测表的长度。

2-level要复杂一些,它采用两级表格式,第一级是分支历史表,存放各组分支历史寄存器的值,第二级是全局/局部分支模式表,(全局或局部应是由表长相对于分支历史寄存器的长决定),它存放各分支历史模式的2bit预测器。

在判断时用当前分支指令对应的历史寄存器值去索引二级表得到相应预测器值。

更新时,把当前分支的方向左移入历史寄存器,并对使用过的2bit预测器作更新。

它有四个参数,前三个是一级表长度,二级表长度,历史寄存器宽度,最后一个是异或标志。

如果为1,则将历史寄存器的值与当前分支指令地址异或,用其结果再去索引二级模式表。

计算机系统结构实验报告班级:xxxxxxxxxxxxxxxx 姓名:xxxxxx 学号:2xxxxxxxxxxxxxx 报告完成时间:20xxxxxxxx计算机系统结构实验报告班级xxxxxxx 实验日期xxxxxxxxx 实验成绩姓名xxxxxxxxxx 学号xxxxxxxxxxxx实验名称存储系统RAID 性能测试实验目的、要求及器材实验目的与要求:①掌握RAID0-5的基本组织方式和特点②RAID0,1,5配置与简单测试;③探究RAID的小写性能或参数敏感性实验器材:虚拟LINUX环境Ubuntu;d isksim-4.0;计算机一台。

实验内容、步骤及结果1.编译Disksim①通过邮件将disksim-4.0.tar.gz和ssd-add-on.zip传送至Ubuntu。

②Tar -vxzf disksim-4.0.tar.gz③在disksim-4.0中编译 make④Unzip ../ssd-add-on.zip⑤patch -p1 < ssdmodel/ssd-patch⑥在Ssdmodel中make⑦进入valid,chmod a+x runvalidOK now!在disksim-4.0中的valid或者ssdmodel/valid 中执行./runvalid即可得到所有文件的测试结果2.修改parv内logorg,模拟RAID0有效盘数设为5Raid0.parv中参数设置如下# component instantiationinstantiate [ statfoo ] as Statsinstantiate [ ctlr0 .. ctlr4 ] as CTLR0instantiate [ bus0 ] as BUS0instantiate [ disk0 .. disk4 ] as HP_C3323Ainstantiate [ driver0 ] as DRIVER0instantiate [ bus1 .. bus5 ] as BUS1# end of component instantiation# system topology[设为5个盘并行的拓扑结构]设置冗余模式、编址模式、分配策略等:disksim_logorg org0 {Addressing mode = Array,Distribution scheme = Striped,Redundancy scheme = Noredun,devices = [ disk0 .. disk4 ],Stripe unit = 64,……}设置随机概率Probability of sequential access = 0.2,Probability of local access = 0.4,Probability of read access = 0.66,Probability of time-critical request = 0.1,Probability of time-limited request = 0.3,存储器总容量为Storage capacity per device = 2056008*5 = 10280040,接下来便可进行虚拟测试../src/disksim raid0.parv raid0.txt ascii 0 1打开raid0.txt查看测试结果:Overall I/O System Total Requests handled: 10002Overall I/O System Requests per second: 100.928186Overall I/O System Completely idle time: 11953.034363 0.120616Overall I/O System Response time average: 24.486686Overall I/O System Response time std.dev.: 13.542895Overall I/O System Response time maximum: 137.672973Overall I/O System Response time distribution< 5 < 10 < 20 < 40 < 60 < 90 <120 <150 <200 200+ 196 332 3551 4960 690 220 44 9 0 0可见raid0 组织模式的I/O系统平均响应时间为24.486686 ms3.修改parv内logorg,模拟RAID1有效盘数设为4Raid1.parv中参数设置如下# component instantiationinstantiate [ statfoo ] as Statsinstantiate [ ctlr0 .. ctlr7 ] as CTLR0instantiate [ bus0 ] as BUS0instantiate [ disk0 .. disk7 ] as HP_C3323Ainstantiate [ driver0 ] as DRIVER0instantiate [ bus1 .. bus8 ] as BUS1# end of component instantiation# system topology[设为8个盘并行的拓扑结构]冗余模式设为Redundancy scheme = Shadowed,存储容量 Storage capacity per device = 8224032,其余设置同raid0接下来进行虚拟测试../src/disksim raid1.parv raid1.txt ascii 0 1打开raid1.txt查看测试结果:OVERALL I/O SYSTEM STATISTICS-----------------------------Overall I/O System Total Requests handled: 9999Overall I/O System Requests per second: 100.452735Overall I/O System Completely idle time: 12533.813298 0.125918Overall I/O System Response time average: 23.141863Overall I/O System Response time std.dev.: 11.234684Overall I/O System Response time maximum: 136.662648Overall I/O System Response time distribution< 5 < 10 < 20 < 40 < 60 < 90 <120 <150 <200 200+ 185 255 3912 4958 553 114 21 1 0 0可见raid1 组织模式的I/O系统平均响应时间为23.141863 ms4.修改parv内logorg,模拟RAID5有效盘数设为4Raid0.parv中参数设置如下# component instantiationinstantiate [ statfoo ] as Statsinstantiate [ ctlr0 .. ctlr4 ] as CTLR0instantiate [ bus0 ] as BUS0instantiate [ disk0 .. disk4 ] as HP_C3323Ainstantiate [ driver0 ] as DRIVER0instantiate [ bus1 .. bus5 ] as BUS1# end of component instantiation# system topology[设为5个盘并行的拓扑结构]冗余模式设为Redundancy scheme = Parity_rotated,存储容量 Storage capacity per device = 8224032,其余设置同raid0接下来进行虚拟测试../src/disksim raid5.parv raid5.txt ascii 0 1打开raid5.txt查看测试结果:OVERALL I/O SYSTEM STATISTICS-----------------------------Overall I/O System Total Requests handled: 10001Overall I/O System Requests per second: 100.494066Overall I/O System Completely idle time: 6.907489 0.000069Overall I/O System Response time average: 56.222291Overall I/O System Response time std.dev.: 49.033242Overall I/O System Response time maximum: 480.847859Overall I/O System Response time distribution< 5 < 10 < 20 < 40 < 60 < 90 <120 <150 <200 200+ 109 164 1496 3273 1722 1503 752 439 324 219可见raid5 组织模式的I/O系统平均响应时间为56.222291 ms5.探究性试验设计实验,任意选择其中一种RAID模式,分析验证其参数敏感性参数包括盘数,条带大小敏感性指,给定负载,其性能是否会随着参数变化而剧烈变化本实验采用ssdmodel执行,期间同时加载了<tracefile> 和<synthgen>发现得到的结果反而相差不大,所以后来只加载了ssd-postmark-aligned2.trace。

第1篇一、实验目的1. 理解计算机组成原理的基本概念和组成结构。

2. 掌握计算机各部件的功能和相互关系。

3. 通过实际操作,加深对计算机组成原理的理解和掌握。

4. 培养实验操作能力和问题解决能力。

二、实验环境1. 实验室:计算机组成原理实验室2. 硬件设备:计算机、示波器、逻辑分析仪、信号发生器等3. 软件:计算机组成原理实验软件三、实验内容1. 计算机基本组成原理实验(1)计算机系统结构实验(2)中央处理器(CPU)实验(3)存储器实验(4)输入/输出(I/O)接口实验2. 计算机组成原理综合实验(1)计算机系统结构综合实验(2)CPU组成与工作原理综合实验(3)存储器组成与工作原理综合实验(4)I/O接口组成与工作原理综合实验四、实验步骤1. 计算机基本组成原理实验(1)计算机系统结构实验1.1 打开计算机组成原理实验软件,查看计算机系统结构图。

1.2 根据实验指导书,理解计算机系统结构的组成和功能。

1.3 分析计算机系统结构中各部件之间的关系。

(2)中央处理器(CPU)实验2.1 查看CPU实验指导书,了解CPU的组成和功能。

2.2 使用示波器观察CPU的工作波形,分析CPU的工作原理。

2.3 通过实验软件,验证CPU的控制信号和时序。

(3)存储器实验3.1 查看存储器实验指导书,了解存储器的组成和功能。

3.2 使用逻辑分析仪观察存储器的读写过程,分析存储器的工作原理。

3.3 通过实验软件,验证存储器的读写操作。

(4)输入/输出(I/O)接口实验4.1 查看I/O接口实验指导书,了解I/O接口的组成和功能。

4.2 使用示波器观察I/O接口的信号波形,分析I/O接口的工作原理。

4.3 通过实验软件,验证I/O接口的通信过程。

2. 计算机组成原理综合实验(1)计算机系统结构综合实验5.1 分析计算机系统结构的组成和功能,总结各部件之间的关系。

5.2 使用实验软件,模拟计算机系统结构的工作过程。

计算机系统结构实验报告一.流水线中的相关实验目的:1. 熟练掌握WinDLX模拟器的操作和使用,熟悉DLX指令集结构及其特点;2. 加深对计算机流水线基本概念的理解;3. 进一步了解DLX基本流水线各段的功能以及基本操作;4. 加深对数据相关、结构相关的理解,了解这两类相关对CPU性能的影响;5. 了解解决数据相关的方法,掌握如何使用定向技术来减少数据相关带来的暂停。

实验平台:WinDLX模拟器实验容和步骤:1.用WinDLX模拟器执行下列三个程序:求阶乘程序fact.s求最大公倍数程序gcm.s求素数程序prim.s分别以步进、连续、设置断点的方式运行程序,观察程序在流水线中的执行情况,观察CPU中寄存器和存储器的容。

熟练掌握WinDLX的操作和使用。

2. 用WinDLX运行程序structure_d.s,通过模拟找出存在资源相关的指令对以及导致资源相关的部件;记录由资源相关引起的暂停时钟周期数,计算暂停时钟周期数占总执行周期数的百分比;论述资源相关对CPU性能的影响,讨论解决资源相关的方法。

3. 在不采用定向技术的情况下(去掉Configuration菜单中Enable Forwarding选项前的勾选符),用WinDLX运行程序data_d.s。

记录数据相关引起的暂停时钟周期数以及程序执行的总时钟周期数,计算暂停时钟周期数占总执行周期数的百分比。

在采用定向技术的情况下(勾选Enable Forwarding),用WinDLX再次运行程序data_d.s。

重复上述3中的工作,并计算采用定向技术后性能提高的倍数。

1. 求阶乘程序用WinDLX模拟器执行求阶乘程序fact.s。

这个程序说明浮点指令的使用。

该程序从标准输入读入一个整数,求其阶乘,然后将结果输出。

该程序中调用了input.s中的输入子程序,这个子程序用于读入正整数。

实验结果:在载入fact.s和input.s之后,不设置任何断点运行。

计算机系统结构实验报告实验一流水线的相关实验目的:1. 熟练掌握WinDLX模拟器的操作和使用,熟悉DLX指令集结构及其特点;2. 加深对计算机流水线基本概念的理解;3. 进一步了解DLX基本流水线各段的功能以及基本操作;4. 加深对数据相关、结构相关的理解,了解这两类相关对CPU性能的影响;5. 了解解决数据相关的方法,掌握如何使用定向技术来减少数据相关带来的暂停。

实验平台:WinDLX模拟器实验内容和步骤:一.用WinDLX模拟器执行下列三个程序:求阶乘程序fact.s求最大公倍数程序gcm.s求素数程序prim.s分别以步进、连续、设置断点的方式运行程序,观察程序在流水线中的执行情况,观察CPU中寄存器和存储器的内容。

熟练掌握WinDLX的操作和使用。

1、求阶乘程序fact.s(1)分别以步进、连续、设置断点的方式运行程序图1.1.1 求阶乘程序fact.s运行统计数据步进方式运行图1.1.2 求阶乘程序fact.s运行统计数据连续方式运行(2)数据统计图1.1.4 求阶乘程序fact.s运行统计数据图1.1.5 求阶乘程序fact.s流水线执行情况图1.1.6 求阶乘程序fact.s寄存器使用情况2、求最大公倍数程序gcm.s图1.2.1 求最大公倍数程序gcm.s运行统计数据图1.2.2 求最大公倍数程序gcm.s流水线执行情况图1.2.3 求最大公倍数程序gcm.s寄存器使用情况3、求素数程序prim.s图1.3.1 求素数程序prim.s运行统计数据图1.3.2 求素数程序prim.s流水线执行情况图1.3.3 求素数程序prim.s寄存器使用情况二、用WinDLX运行程序structure_d.s,通过模拟找出存在资源相关的指令对以及导致资源相关的部件;记录由资源相关引起的暂停时钟周期数,计算暂停时钟周期数占总执行周期数的百分比;论述资源相关对CPU性能的影响,讨论解决资源相关的方法。

《计算机系统结构》实验报告 专业班级 姓 名 学 号

实验一 熟悉模拟器WinDLX的使用 一、 实验目的 1. 熟练掌握WinDLX模拟器的操作和使用,熟悉DLX指令集结构及其特点。 2. 加深对计算机流水线基本概念的理解。 3.了解DLX基本流水线各段的功能以及基本操作。

二、 实验平台 WinDLX模拟器 三、 实验内容和步骤 1.WinDLX的安装 WinDLX模拟器是一个图形化、交互式的DLX流水线模拟器,能够演示DLX流水线是如何工作的。该模拟器可以装载DLX汇编语言程序(后缀为“.s”的文件),然后单步、设断点或是连续执行该程序。CPU的寄存器、流水线、I/O和存储器都可以用图形表示出来,以形象生动的方式描述DLX流水线的工作过程。模拟器还提供了对流水线操作的统计功能,便于对流水线进行性能分析。 WinDLX 包含windlx.exe和windlx.hlp文件。同时,还需要一些扩展名为.s的汇编代码文件。按以下步骤在Windows下安装WinDLX: (1)WinDLX创建目录,例如D:\WINDLX (2)解压WinDLX软件包或拷贝所有的WinDLX文件(至少包含 windlx.exe, windlx.hlp)到这个WinDLX 目录。 2.启动和配置WinDLX 双击WinDLX图标,将出现一个带有六个图标的主窗口,如图1-1。双击这些图标会弹出子窗口。 图1-1 WinDLX启动窗口 为了初始化模拟器, 点击File 菜单中的 Reset all 菜单项,弹出一个“Reset DLX”对话框。然后点击窗口中的“确认”按钮即可。WinDLX可以在多种配置下工作。可以改变流水线的结构和时间要求、存储器大小和其他几个控制模拟的参数。点击Configuration→Floating Point Stages(点击Configuration打开菜单,然后点击Floating Point Stages菜单项),选择如图1-2标准配置。如果需要, 可以通过点击相应区域来改变设置。然后, 点击OK 返回主窗口。点击Configuration→Memory Size ,可以设置模拟处理器的存储器大小。应设置为0x8000,然后,点击OK返回主窗口。 在Configuration 菜单中的其他三个配置也可以设置,它们是:Symbolic addresses(符号地址),absolute Cycle Count(周期)和Enable Forwarding。点击相应菜单项后,在它的旁边将显示一个小钩。

图1-2 配置Floating Point Stages菜单项 3.装载测试程序 在开始模拟之前,至少应装入一个程序到主存。我们选择fact.s作为例子,fact.s计算一个整型值的阶乘,它的运行还需要一个辅助文件input.s, input.s中包含一个子程序,它读标准输入(键盘)并将值存入DLX处理器的通用寄存器R1中。为此,选择File/Load Code or Data,窗口中会列出目录中所有汇编程序。按如下步骤操作,可将这两个文件装入主存。 点击fact.s 点击select 按钮 点击input.s 点击select按钮 点击load按钮 选择文件的顺序很关键,它决定了文件在存储器中出现的顺序。对话框中会显示信息“File(s)loaded successfully. Reset DLX?”,点击确认按钮。这样,文件就已被装入到主存储器中了。现在就可以开始模拟工作了。 4.模拟 在主窗口中,可以看见六个图标,它们分别为“Register”,“Code”,“Pipeline”,“Clock Cycle Diagram”,“Statistics” 和“Breakpoints”。点击其中任何一个将弹出一个新窗口(子窗口)。在模拟过程中将介绍每一个窗口的特性和用法。 (1) Pipeline 窗口 首先来看一下DLX处理器的内部结构。双击图标Pipeline,出现一个子窗口,窗口中以图表形式显示了DLX的五段流水线,包括取指段(IF)、译码段(ID)、执行段(EX)、访存段(MEM)和写回段(WB)。此图显示DLX处理器的五个流水段和浮点操作 (加/减, 乘和除)的单元,如图1-3。尽可能地扩大此窗口,以便处于不同流水段的指令都能够在图表中显示。

图1-3 Pipeline 窗口 不同指令在执行段的操作是不同的,而且不同操作在该段的延迟也是不同的。为此,DLX 流水线的执行段分为4 个单元,它们分别是:intEX 单元(整数操作),faddEX 单元(浮点加减),fmulEX(浮点乘法),fdivEX(浮点除法),每个单元设置的个数和其延迟时间已经在前面通过Configuration → Floating Point Stages 进行了设置,其中intEX 的延迟为1(IF 段,ID 段,MEM 段和WB 段的延迟均为1),faddEX、fmulEX和fdivEX 的延迟分别为2、5 和19。可以修改其设置,然后再观察程序的执行结果,从而得到你所需要的结论。 (2) Code 窗口 双击Code 窗口图标,将看到代表存储器内容的三栏信息,从左到右依次为:地址 (符号或数字)、命令的十六进制机器代码和汇编命令,如图1-4。

图1-4 Code 窗口中内容 现在,点击主窗口中的 Execution开始模拟。在出现的下拉式菜单中,点击Single Cycle或按 F7键。 这时,窗口中带有地址“$TEXT ”的第一行变成黄色。按下 F7 键,模拟就向前执行一步,第一行的颜色变成橘黄色,下一行变成黄色。这些不同颜色指明命令处于流水线的哪一段。如果Pipeline窗口已经关闭,请双击相应图标重新打开它。 如果窗口足够大,你能够看到命令“jal InputUnsigned”在 IF段,“addi r1, r0, 0x1000 ”在第二段ID。其他方框中带有一个“X”标志,表明没有处理有效信息。 (3) Clock Cycle Diagram 窗口 它显示流水线的时空图,使所有子窗口图标化,双击打开Clock Cycle Diagram 窗口。 图1-5 流水线的时空图 在窗口中,将看到模拟正在第四时钟周期,第一条命令正在MEM段,第二条命令在intEX段,第四条命令在IF段。而第三条命令指示为"aborted"。其原因是:第二条命令(jal)是无条件分支指令, 但只有在第三个时钟周期, jal 指令被译码后才知道,这时,下一条命令movi2fp已经取出,但需执行的下一条命令在另一个地址处,因而,movi2fp的执行应被取消,在流水线中留下气泡。 jal 的分支地址命名为"InputUnsigned"。为找到此符号地址的实际值,点击主窗口中的Memory → Symbols,出现的子窗口中显示相应的符号和对应的实际值。在 "Sort:"区域选定"name",使它们按名称排序,而不是按数值排序。数字后的"G"代表全局符号, "L"代表局部符号。"input"中的"Input Unsigned" 是一个全局符号,它的实际值为0x144 ,用作地址。点击OK 按纽关闭窗口。 再一次点击 F7 ,第一条命令(addi)到达流水线的最后一段。如果想了解某条命令执行后处理器内部会发生什么?只要对准Clock cycle diagram窗口中相应命令所在行,然后双击它,弹出一个新窗口。窗口中会详细显示每一个流水段处理器内部的执行动作。观察完后,点击OK按钮关闭窗口。双击第三行(movi2fp),你会看到它只执行了第一段(IF), 这是因为出现跳转而被取消。 双击Code窗口中的某一行或者Pipeline 窗口中的某一段,可以出现Information 窗口。 (4) Breakpoint 窗口 按F7键以单步方式运行程序,可以清楚的看到每条指令在流水线各个段的具体操作情况,除此之外,DLX模拟器还提供了其他几种运行程序的方式。 单击主窗口中Execute子菜单,可以看到DLX模拟器共提供了4种运行程序的方式。这些运行方式为我们了解DLX流水线或调试程序提供了非常方便的环境。 Single Cycle(或按F7键)就是单步执行方式; Multiple Cycles(或按F8键)是多步执行方式,选择该方式,会在屏幕上出现一个窗口,询问周期个数,它表示流水线从当前位置继续向前执行的周期个数,输入你需要的值,然后按OK键,流水线就会向前执行相应的周期个数; Run(或按F5键)是运行方式,选择该方式,流水线就会从当前位置一直运行到程序结束; Run to(或按F4键)是断点方式,选择该方式,会在屏幕上出现一个窗口,要求指定某条指令的地址和流水线的某个段,表示让流水线运行到该条指令在流水线该段的时候暂停,输入你需要的指令,然后按OK键,流水线就会运行到指定的位置后停下来。 激活Breakpoints子窗口,里面什么都没有。现在,请指向Code窗口中包含指令trap 0x5的0x0000013c行,该指令是写屏幕的系统调用。单击指令行,然后点击主窗口菜单Code,单击Set Breakpoint (确保指令行仍被标记),将弹出一个 “Set Breakpoint”窗口。通过此窗口,你可以选择指令运行到流水线的哪一阶段时,程序停止执行。 注意,在Address栏里标记的是trap 0x5指令的地址,而且是相对寻址方式。该子窗口缺省设置选择的指令在流水线的ID段时停止程序。点击OK关闭窗口。在Code 窗口中,我们看到指令trap 0x5行上出现了“BID”字样,它表示当本指令在译码段时,程序中止执行。 再次激活Breakpoints子窗口,就可以看到里面标记了断点设置的详细情况:在什么地址,在什么段,是什么指令。根据需要,你可以设置多个断点,Reakpoints子窗口将记录所有断点的设置情况。删除断点时,首先在Code子窗口中选中需要删除断点的指令行,然后点击主窗口中的Code选项,再点击Delete Breakpoint选项,即可删除断点。 点击Execution→Run或按F5键,程序就会连续向前运行,直到碰到我们设置的断点后停下来,,按OK按钮关闭。现在你可以激活任何一个子窗口,观察你希望看到的结果,然后按F5键继续运行,屏幕上会出现DLX-Standard–I/O对话框,要求你输入一个整型值。输入20后按回车键,程序会继续模拟运行,直至出现提示框“Trap #0 occurred”表明最后一条指令trap 0已经执行,Trap指令中编号“0”没有定义,只是用来终止程序。点击主窗口中Execute菜单下“Display DLX-I/O...”选项,你会看到输出结果(20的阶乘)为2.4329e+18。点击OK关闭窗口。 (5) Register 窗口 双击Register子窗口,可以看到DLX的全部寄存器及其内容,观察左上角的PC寄存器,其值为0x00000100,也就是说程序会从内存0x00000100处开始执行。 在程序执行过程中,随时可以点击Register子窗口来观察各个寄存器内容的变化。看一下R1到 R5的值。按F5使模拟继续运行到下一个断点处,有些值将发生改变,指令lw从主存中取数到寄存器中。 (6) Statistics 窗口 双击子窗口Statistics,可以看到该窗口提供了各个方面的信息:模拟中硬件配置情况、暂停及原因、条件分支、Load/Store指令、浮点指令和traps。窗口中给出事件发生的次数和百分比。利用这些数据,我们可以定量的比较各种改善流水线性能的技术对程序运行