改进的抽取滤波器设计

- 格式:pdf

- 大小:283.99 KB

- 文档页数:4

改进型CIC抽取滤波器的FPGA实现谢海霞;赵欣【摘要】In order to reduce the data rate and power consumption of the previously-designed CIC decimation filter,the FPGA-based realization process of the improved CIC decimation filter is studied,the hardware implementation structure of the CIC decimation filter is optimized,and FPGA is used to design the decimation filter.The hardware implementation structure and bit wide of CIC decimation filter are analyzed.The filter structure is decimated through Hogenauer to get the CIC hardware implementation structure whose decimation rate is 16 and decimation degree is 6.The structure is transformed into four cascaded CIC decimation filters implemented with FPGA,which can reduce the data rate and improve the data bit wide.In the implementation process of CIC decimation filter with FPGA,the highest bit wide required by the register while it is operating is analyzed to avoid the data overflow problem.The experimental result shows that the modified CIC decimation filter is effective,and can reduce the data rate and system power consumption.%为了解决以往设计的CIC抽取滤波器存在的数据速率高以及功耗高的问题,研究了改进型CIC抽取滤波器的FPGA实现过程,优化CIC抽取滤波器硬件实现结构,采用FPGA实现抽取滤波器的设计.分析CIC抽取滤波器的硬件实现结构和位宽,通过Hogenauer抽取滤波器结构,得到6级16抽取的CIC硬件实现结构,将该结构变换成4个CIC抽取滤波器的级联式FPGA实现,逐级降低数据速率,提升数据位宽.以FPGA实现CIC抽取滤波器过程中,分析了其运算时寄存器所需的最高位宽,避免产生数据溢出问题.实验结果表明,所设计的改进型CIC抽取滤波器是有效的,可降低数据速率和系统功耗.【期刊名称】《现代电子技术》【年(卷),期】2017(040)016【总页数】3页(P148-150)【关键词】Hogenauer;CIC抽取滤波器;数据速率;FPGA【作者】谢海霞;赵欣【作者单位】海南热带海洋学院,海南三亚572022;海南热带海洋学院,海南三亚572022【正文语种】中文【中图分类】TN713-34;TP368.1地震检波器是地震数据采集系统的核心部件,其可检测到微弱信号,具有较高的探测性能。

改进型CIC抽取滤波器设计与FPGA实现摘要:为了改善级联积分梳状(CIC)滤波器通带不平和阻带衰减不足的缺点,给出一种改进型CIC 滤波器。

该滤波器在采用COSINE 滤波器提高阻带特性的基础上,级联了一个SINE 滤波器,补偿了其通带衰减。

硬件实现时,采用新的多相分解方法结合非递归结构,不仅大大减少了存储单元数量,还使电路结构更加规则。

经仿真和FPGA 验证,改进型CIC 滤波器使用较少硬件,实现了阻带衰减100.3 dB,通带衰减仅为O.000 1 dB 。

关键词:CIC 抽取滤波器;COSINE 滤波器;SINE 滤波器;设计优化;FPGA抽取滤波器是∑-△模/数转换器中的重要组成部分,积分梳状滤波器经常作为第一级滤波器,用以实现抽取和低通滤波。

其优点是实现时不需要乘法器电路,且系数为整数,不需要电路来存储系数,同时通过置换抽取可以使部分电路工作在较低频率,与相同滤波性能的其他FIR 滤波器相比,节约了硬件开销。

经过仿真,抽取率为32 的一阶积分梳状滤波器第一旁瓣相对于主瓣的衰减最大约为15 dB,这样的阻带衰减根本达不到实用滤波器的设计要求。

为了改变滤波性能,一般采用级联积分梳状滤波器(CIC)。

但经过CIC 降频滤波系统降频后会产生信号混叠现象,并且主瓣曲线不平,需要用新的算法或新结构来修正改善这些特性。

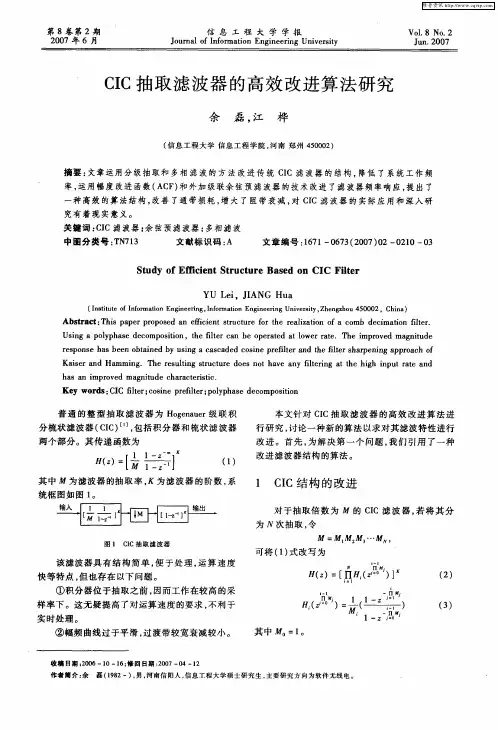

1 CIC 抽取滤波器原理经典的抽取滤波器为Hogenauer CIC 滤波器,其传输函数表达式为:式中:参数M 为降频因子,决定了CIC 的通带大小;K 为滤波器的阶数,对阻带衰减起到加深作用。

频率响应为:滤波电路由积分模块与差分模块组成,根据置换原则将抽取因子提到差分模块之前,使其工作在较低频率,并节省了M-1 个存储单元,框图如图1 所示。

改进的抽取滤波器设计潘桃莉;谢光忠;周云;蒋亚东【期刊名称】《微处理机》【年(卷),期】2011(32)1【摘要】在Sigma-Delta ADC芯片中,数字抽取滤波器电路占据了大部分面积.所设计的改进型Hogenauer CIC滤波器,将梳状部分进行优化,采用控制单元、加法器和寄存器代替传统Hogenauer CIC滤波器中的差分器,从而减小数字电路的面积.一个采用这种结构的4阶32倍降采样数字滤波器在Stratix Ⅱ系列2S30 FPGA芯片中实现.经过测试,耗费的硬件资源比传统Hogenauer结构滤波器减少11%.%Digital circuit of decimation filter occupies most of chip area in Sigma - Delta ADC. In this paper, an improved Hogenauer CIC filter is designed. A control unit, an adder and some registers are used to replace multiple of adders in traditional Hogenauer CIC filter, in order to optimize the comb part of decimation filter and reduce digital circuit area. A fourth order digital filter employing such method with downsampling rate of 32 is designed and realized in S tratix Ⅱ set 2S30 FPCA chip. As a result of practice, it costs chip resources 11 percent less than that using traditional Hogenauer structure.【总页数】4页(P7-10)【作者】潘桃莉;谢光忠;周云;蒋亚东【作者单位】电子科技大学光电信息学院,电子薄膜与集成器件国家重点实验室,成都,610054;电子科技大学光电信息学院,电子薄膜与集成器件国家重点实验室,成都,610054;电子科技大学光电信息学院,电子薄膜与集成器件国家重点实验室,成都,610054;电子科技大学光电信息学院,电子薄膜与集成器件国家重点实验室,成都,610054【正文语种】中文【中图分类】TN713.7【相关文献】1.改进型CIC抽取滤波器设计与FPGA实现 [J], 张杰;戴宇杰;张小兴;吕英杰2.一种改进的CIC抽取滤波器设计 [J], 窦建华;梁红松;胡敏;汪荣贵3.Sigma-Delta模数转换器的三级数字抽取滤波器设计 [J], 胥珂铭;高博;龚敏4.低成本的∑△ADC数字抽取滤波器设计 [J], 钟燕清;田易;李继秀;刘谋;张兴成;孟真;陈华;阎跃鹏5.适用于Sigma-Delta ADC的多抽取率数字滤波器设计 [J], 王尧;卜刚因版权原因,仅展示原文概要,查看原文内容请购买。

改进型CIC抽取滤波器的研究与设计张茂磊;栾晓明;徐向斌【摘要】由于CIC(级联积分梳状)滤波器不需要乘法运算和存储系数,因此实现非常简单,在采样率变换过程中经常使用CIC滤波器进行数字滤波.在CIC滤波器概念的基础上,提出了基于正弦函数的补偿滤波器与基于锐化技术的改进型CIC滤波器,补偿滤波器与锐化技术二者用来改善CIC滤波器的通带与阻带特性.通过对CIC滤波器及其改进型的综合性能进行对比体现出所设计滤波器的优点.【期刊名称】《应用科技》【年(卷),期】2011(038)002【总页数】4页(P18-21)【关键词】采样率变换;CIC抽取滤波器;补偿滤波器;锐化技术【作者】张茂磊;栾晓明;徐向斌【作者单位】哈尔滨工程大学,信息与通信工程学院,黑龙江,哈尔滨,150001;哈尔滨工程大学,信息与通信工程学院,黑龙江,哈尔滨,150001;哈尔滨工程大学,信息与通信工程学院,黑龙江,哈尔滨,150001【正文语种】中文【中图分类】TN911.23在现代通信系统中,随着采样速率的提高,采样后的数据流速率会很高,这会导致后续环节的信号处理速率跟不上,因此采样率变换(抽取和内插)技术已经成为数字信号处理过程中不可缺少的一部分,并且成为无线通信领域里最常用,也是最有用的技术之一.多速率信号处理技术可以实现采样率的变换,对A/D变换后的数据进行降速处理,以适应在不同的情形下对不同采样速率的需求.多速率信号处理技术包含二次采样或称重采样过程,在这一过程中会产生频谱混叠和镜像效应,为了抑制这2种基本特性产生的不利影响,在抽取前或内插后需要进行预滤波处理,该数字滤波器性能的好坏对采样率变换后信号的实时处理能力有着决定性的作用.因此设计满足抗混叠、抗镜像效应要求的数字滤波器无论在抽取或内插变换过程中都极其重要.在这方面,积分级联梳状(CIC)滤波器具有较好的性能[1].由于CIC抽取滤波器与CIC内插滤波器的原理相似,因此主要讨论CIC抽取滤波器的优化设计.1 CIC滤波器概述式中D为CIC滤波器的抽取因子,也是其阶数.对其冲激响应函数进行Z变换得积分梳状滤波器的冲激响应形式为由式(2)可见,CIC滤波器是由积分器H1(z)与梳状滤波器H2(z)级联构成的,其单级实现框图如图1(a)所示.可见CIC滤波器无需一般的FIR滤波器所需的乘法运算,这对简化硬件、提高实时性都有极其重要的意义.根据Noble原理:对序列先进行抽取或者插值,再进行线性滤波与先进行线性滤波,再进行抽取或者插值,这二者等价.可以得到高效CIC滤波器实现结构如图1(b)所示,即在梳状滤波器之前完成抽取,此时只有积分器工作在输入的高采样率上,而梳状滤波器工作在抽取后的低采样率上,这样就大大降低了系统的计算量,这种系统结构称为Hogenauer抽取滤波器[2],其占用资源少,易于实现.图1 CIC实现框图式中加入了归一化因子1/D,目的是使该滤波器的直流增益为1.其幅频响应为此时,整个系统的传输函数为图2 单级CIC滤波器的幅频特性图2所示为D=8时单级CIC滤波器的幅频特性图.由图2可见,随着频率的增大,旁瓣电平逐渐减小,当D1时第一旁瓣电平为2/(3π),则单级CIC滤波器的旁瓣抑制比为由此可以看出单级CIC滤波器的旁瓣抑制比较小,阻带衰减较差.采用多级CIC滤波器级联的办法可以降低旁瓣电平.设有N级CIC滤波器级联,则旁瓣抑制比为虽然随着级联级数的增大;旁瓣抑制比增大;但是滤波器的通带特性变差了,因此一般情况下级联的级数不超过5级[3].当N=5时,CIC滤波器的阻带衰减约为67 dB,基本能满足实际使用的需求.图3为D=2时单级与5级CIC滤波器的通带特性对比图,可见5级CIC滤波器的通带特性变差了.图3 单级CIC与5级CIC滤波器的通带特性2 SCIC滤波器的设计多级CIC滤波器级联的方法虽然能使旁瓣抑制比增大,但这是以通带特性变差来换取的,而在滤波器的设计中两方面都很重要,不能只考虑其中一方面,而忽略另外一方面.传统CIC滤波器的设计方法通常只是改进CIC滤波器一种特性,而另外一种特性得不到改善.为了解决这一问题,许多学者提出了一系列的解决方案.其中最常用的就是基于幅度变换函数的锐化技术[4].锐化技术既能改善CIC滤波器的通带特性,又能改善其阻带特性.利用该技术所得的滤波器通常称为SCIC(Sharpened CIC)滤波器[5].设H为原CIC滤波器的传递函数,则SCIC滤波器的传递函数为式中C(t+n,t)是二项式的系数.对于一些给定的m和n的典型值,幅度变换函数的表达式如表1所示.表1 m和n取典型值时幅度变换函数表达式m n H0 1 0 2H-H2 1 1 3H2-2H32 0 H3-3H2+3H3 0 -H4+4H3-6H2+4H 3 1 -4H5+15H4-20H3+10H23 2 -10H6+36H5-45H4+20H3 3 3 -20H7+70H6-84H5+35H4不失一般性,文中只讨论m=n=1时的情况,此时H0=3H2-2H3.图4为D=8时单级 CIC与单级SCIC滤波器幅频特性对比图;图5为D=2时单级CIC与单级SCIC滤波器通带衰减特性对比图.图4 单级CIC与SCIC滤波器的幅频特性图5 单级CIC与SCIC滤波器的通带特性由图4、5可以看出,与CIC滤波器相比,SCIC滤波器的性能有很大改善,其旁瓣抑制比有较大提高,约为38 dB.虽然SCIC滤波器的特性优良,但这是以增加滤波器的复杂度换取的,显然这种以增加复杂度换取性能的改进在一些对实时性要求不是很高的场合是很适用的.3 基于正弦函数的补偿滤波器为了进一步改善CIC滤波器的性能,可以利用基于正弦函数的补偿滤波器对其性能进行优化.设滤波器的幅频特性为由公式sin2α=(1-cos2α)/2 ,可得到式中:A= -2-(b+2);B= -(2b+2+2),参数 b是[0,2]之间的整数,b 的选取不依赖于抽取因子D,而是由滤波器的级联级数N决定的.其关系如表2所示.其中参数N决定阻带衰减特性,b补偿相应的通带特性[6].表2 N与b的取值关系N 1 2 3 4 5 6 7 b 2 1 0 0 0 1 -2把具有式(7)所示传递函数的滤波器用于补偿作用时,称为基于正弦函数的补偿滤波器(Sine-Based),可以利用此补偿滤波器对CIC滤波器的幅频特性进行优化[7].设级联上基于正弦函数补偿的CIC(BSCIC)滤波器的系统的传递函数为Hc(z),则图6 单级CIC与BSCIC滤波器的幅频特性式中H(z)与G(zD)分别由式(3)与式(7)给出.图6所示为N=1,b=2,D=8时单级CIC与单级BSCIC滤波器的幅频特性对比图.由图6可以看出,BSCIC 滤波器的通带特性得到了改善,旁瓣抑制比在11 dB左右,若采用5级BSCIC滤波器级联的办法,则旁瓣抑制比也可以满足实际使用的需求.4 BSSCIC滤波器的设计与分析4.1 BSSCIC滤波器的设计从以上分析可以看出,具有式(7)所示的滤波器确实能改善CIC滤波器的通带特性,可以考虑将其用于改善阻带特性优良的SCIC滤波器,称该滤波器为BSSCIC 滤波器,下面考虑其幅频特性.设SCIC滤波器的传递函数为H0=3H2-2H3,则BSSCIC滤波器的传递函数H BSSCIC=3H2c,其中 Hc由式(8)给出.4.2 BSSCIC滤波器的性能分析图7分别给出了当N=1,b=2,D=8时单级CIC,SCIC,BSCIC与BSSCIC滤波器的幅频特性对比图.从图7中可以看出,相比之下CIC滤波器结构最简单、最容易实现;BSCIC滤波器通带特性最好,SCIC滤波器阻带特性最好,而BSSCIC滤波器的通带特性及阻带特性较折中,但复杂度最大.图7 单级CIC,SCIC,BSCIC与BSSCIC的幅频特性单级CIC,SCIC,BSCIC与BSSCIC滤波器的性能对比如表3所示.表3 单级CIC,SCIC,BSCIC与BSSCIC的性能对比特性CIC SCIC BSCIC BSSCIC复杂度最简单复杂简单最复杂通带较好最差最好一般阻带一般最好最差较好从以上的比较分析中可以看出BSSCIC滤波器的优点突出,下面从实用的角度予以分析.1)BSSCIC滤波器的旁瓣抑制比约为27 dB,若采用2级级联的办法其旁瓣抑制比即可以满足实际使用的需求.2)实际使用中若采用2级BSSCIC滤波器级联,此时的复杂度与5级CIC滤波器级联时的复杂度相当.3)在采用2级BSSCIC滤波器级联满足旁瓣抑制比要求的情况下,虽然其通带特性也变差,但从图7中可以推论出其比2级SCIC滤波器级联时的通带特性要好. 另外,为了降低BSSCIC滤波器的复杂度,在设计SCIC滤波器时可以取表1中的m=1,n=0,这样BSSCIC滤波器的复杂度可大大降低.由于其原理相似,仿真也更简单一些,因此这里就不再赘述了.5 结束语讨论了几种改进型的CIC滤波器,对它们的性能进行了仿真与比较分析.在此基础上提出了基于正弦函数的补偿滤波器的改进型SCIC滤波器,通过与传统CIC滤波器的比较可以得出结论,BSSCIC滤波器具有较好的性能,在适当增大系统复杂度的前提下获得了较好的通带特性及阻带特性.改进方法使CIC滤波器具有更好的实用价值,对CIC滤波器的进一步研究与使用有着现实意义.参考文献:[1]DOLECEK G J,MITRA S K.A new two-stage sharpened comb decimator[J].IEEE Trans On Circuits and Systems-I,2005,2(7):1416-1420.[2]HOGENAUER EB.An economical class of digital filters for decimation and interpolation[J].IEEE Trans Acoustic,Speech,Signal Processing,1981,29(2):155-162.[3]GOODMAN D J,CAREY M J.Nine digital filters for decimation and interpolation[J].IEEE Trans Acoustic,Speech,Signal Processing,1997(4):325-329.[4]KAISER J,HAMMING R.Sharpening the response of a symmetric non-recursive filter by multiple use of the same filter[J].IEEE Trans Acoustic,Speech,Signal Processing,1977,25:415-422.[5]DOLECEK G J,HARRISF.Design of CIC compensator filter in a digital IF receiver[C]//2008 IEEE International Symposium on Communications and Information Technologies.Vientiane,USA,2008:638-643.[6]DOLECEK G J,MITRA SK.On design of CIC decimation filter with improved response[C]//.IEEE International Symposium on Communications,Control& Signal Processing.St.Julians,Malta,2008:1072-1076.[7]DOLCEK G J,TORRES F J pensated CIC-Cosine decimation filter[C]//2007 IEEE International Symposium on Communications and Information Technologies.Sydney ,Australia,2007:256-259.。

24位Σ-△A/D转换器中抽取滤波器的设计和实现的开题报告1.选题背景与研究意义Σ-△模数转换器广泛应用于音频数字信号处理、网络音频播放等领域。

其中,24位Σ-△A/D转换器是一种比较常见的Σ-△模数转换器。

在这种转换器中,抽取滤波器是非常重要的一部分,其负责去除高频噪声,保证信号的精度和清晰度。

因此,对24位Σ-△A/D转换器中抽取滤波器的设计和实现进行研究,具有很高的实用价值和理论意义。

2.研究内容与研究方法研究内容:本研究主要对24位Σ-△A/D转换器中抽取滤波器进行设计和实现。

具体包括以下方面:(1)研究抽取滤波器的基本原理和设计方法。

(2)对24位Σ-△A/D转换器的系统要求进行分析,确定抽取滤波器的参数。

(3)根据设计要求,选择合适的滤波器类型,并进行滤波器的设计和仿真。

(4)在FPGA开发板上搭建实验平台,对设计好的抽取滤波器进行硬件实现,并验证实验结果的正确性。

研究方法:本研究采用以下方法进行研究:(1)文献研究法:对相关文献进行综合分析和归纳,掌握抽取滤波器的基本原理和设计方法。

(2)仿真研究法:通过Matlab等软件进行滤波器的设计和仿真,验证设计方案的可行性和效果。

(3)实验研究法:在FPGA开发板上进行硬件实现,进行实验验证,分析实验结果,并对实验结果进行优化。

3.预期研究结果与研究意义预期研究结果:(1)设计出合适的抽取滤波器,可以有效去除24位Σ -△ A/D转换器中的高频噪声,提高信号精度和清晰度。

(2)在FPGA开发板上搭建实验平台,将抽取滤波器硬件实现,并验证实验结果的正确性,为后续的优化提供数据支持。

研究意义:(1)对于研究、开发和改进现代音频处理技术,具有建设性意义。

(2)为音频数字信号处理和网络音频播放等领域的产品开发提供技术支持。

(3)提供了设计和仿真方法,为类似系统的设计提供了一些实践经验。

数字下变频中抽取滤波器的设计及FPGA实现摘要:针对软件无线电接收机数字下变频中高速数字信号的降采样需求,利用半带滤波器及级联积分梳状滤波器,设计了一种半带滤波器前置的多级抽取滤波器架构。

通过Simulink搭建系统模型验证之后,利用Xilinx ISE 12.3在Xilinx xc5vsx95t-2ff1136 FPGA上实现了一种下采样率为64的抽取滤波器。

Modelsim仿真结果表明,该抽取滤波器设计是有效的,达到了设计指标。

0 引言数字下变频是软件无线电接收机的关键模块,高速数字信号进行变频、降采样、滤波,将高速中频信号变为低速基带信号[1-2],便于后级处理。

其中,降采样和滤波是下变频的关键模块,由抽取滤波器来完成[3]。

由于多级结构可以大大降低滤波器的阶数[4],允许每一级归一化过渡带宽比较宽[5],抽取滤波器一般采用多级结构实现,常用结构如图1所示,wdz4-t1.gif级联积分梳状(Cascaded integrator-com,CIC)滤波器通常作为第一级抽取滤波器[1-6]。

为缩短关键路径,从而提高采样速度,滤波器常采用并行处理及流水线技术[6]。

CIC滤波器中有反馈回路,加入流水线寄存器则会导致反馈回路不同步,从而无法采用流水线技术;FIR滤波器则可以采用并行处理及流水线技术。

对于半带滤波器(Half-band Filter, HBF)而言,采用分布式算法则可以很好地兼容并行处理与流水线技术,且无需速率受限的乘法器资源。

本设计对流水线式全并行分布式算法进行改进用以实现HBF,而并行处理提高采样率是采用复制硬件的方法[7],wdz4-t2.gif全并行结构的HBF则是复制使用LUT,在满足处理速度的要求下,本文将HBF置于数据位宽最小的输入级(如图2)。

1 抽取滤波器整体设计及Simulink建模仿真本文将64倍抽取的总抽取率分为3级实现:2倍抽取的前置HBF、16倍抽取的CIC抽取滤波器以及2倍抽取的FIR补偿滤波器,如图2所示。

微 处 理 机M I CROPROCE SSORS改进的抽取滤波器设计潘桃莉,谢光忠,周 云,蒋亚东(电子科技大学光电信息学院电子薄膜与集成器件国家重点实验室,成都610054)摘 要:在S i g m a-Delta ADC 芯片中,数字抽取滤波器电路占据了大部分面积。

所设计的改进型H ogenauer C I C 滤波器,将梳状部分进行优化,采用控制单元、加法器和寄存器代替传统H ogenauer CI C 滤波器中的差分器,从而减小数字电路的面积。

一个采用这种结构的4阶32倍降采样数字滤波器在Stratix II 系列2S30FPGA 芯片中实现。

经过测试,耗费的硬件资源比传统H ogenauer 结构滤波器减少11%。

关键词:H ogenauer 滤波器;抽取滤波器;现场可编程门阵列DO I 编码:10.3969/.j issn .1002-2279.2011.01.003中图分类号:TN 713.7文献标识码:A文章编号:1002-2279(2011)01-0007-04D esign of Improved D ecim ati on FilterPAN Tao-l,i X I E Guang-zhong ,Z HOU Yun ,JIANG Y a-dong(School of Op toelectron ic Infor m ation ,Uni ver sity of Electronic Science and T ec hno logy of China ,S tate K ey Labora t ory of E lectronic Th i n F il m s and Integrated D evices,Chengdu 620054,China )Abst ract :D ig ita l circu it of dec i m ation filter occup i e s m ost of chip area in S i g m a -Delta ADC .I n th is paper ,an i m proved H ogenauer C I C filter is designed .A contro l un i,t an adder and so m e registers are used to replace m u ltiple o f adders in trad itionalH ogenauer C I C filter ,in order to opti m ize the co m b part o f deci m ati o n filter and reduce d i g ital circuit area .A fourth o r der dig ita l filter e m ploy i n g such m eth od w ith do wnsa mp li n g rate o f 32i s designed and rea lized in Stratix II set 2S30FPGA ch i p .As a result o f practice ,it costs ch i p resources 11percent less t h an that usi n g trad iti o na lH ogenauer str ucture .K ey w ords :H ogenauer F ilter ;Dec i m ation Filter ;FPGA1 引 言随着信号处理理论日趋完善,基于通信编码与数字信号处理的S i g m a-Delta ADC 以其在高精度方面显著的优势成为了研究的热点[1]。