简易数字钟设计实验报告东北大学

- 格式:docx

- 大小:161.75 KB

- 文档页数:4

实验十:简易数字钟设计实验

1、实验目的 1)学习掌握数字系统综合设计方法。

2)学习掌握层次设计方法。

3)学习掌握设计下载方法。

4)学习掌握实验系统使用方法。

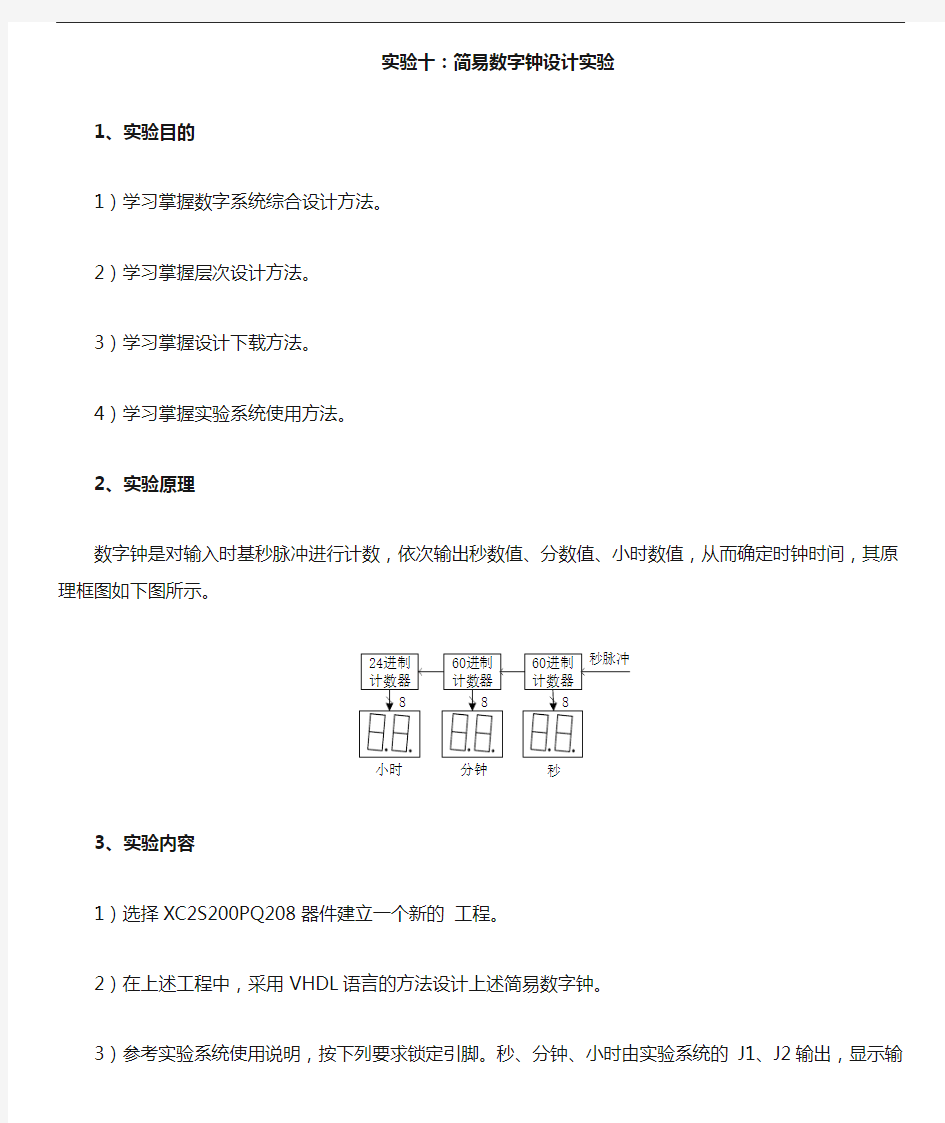

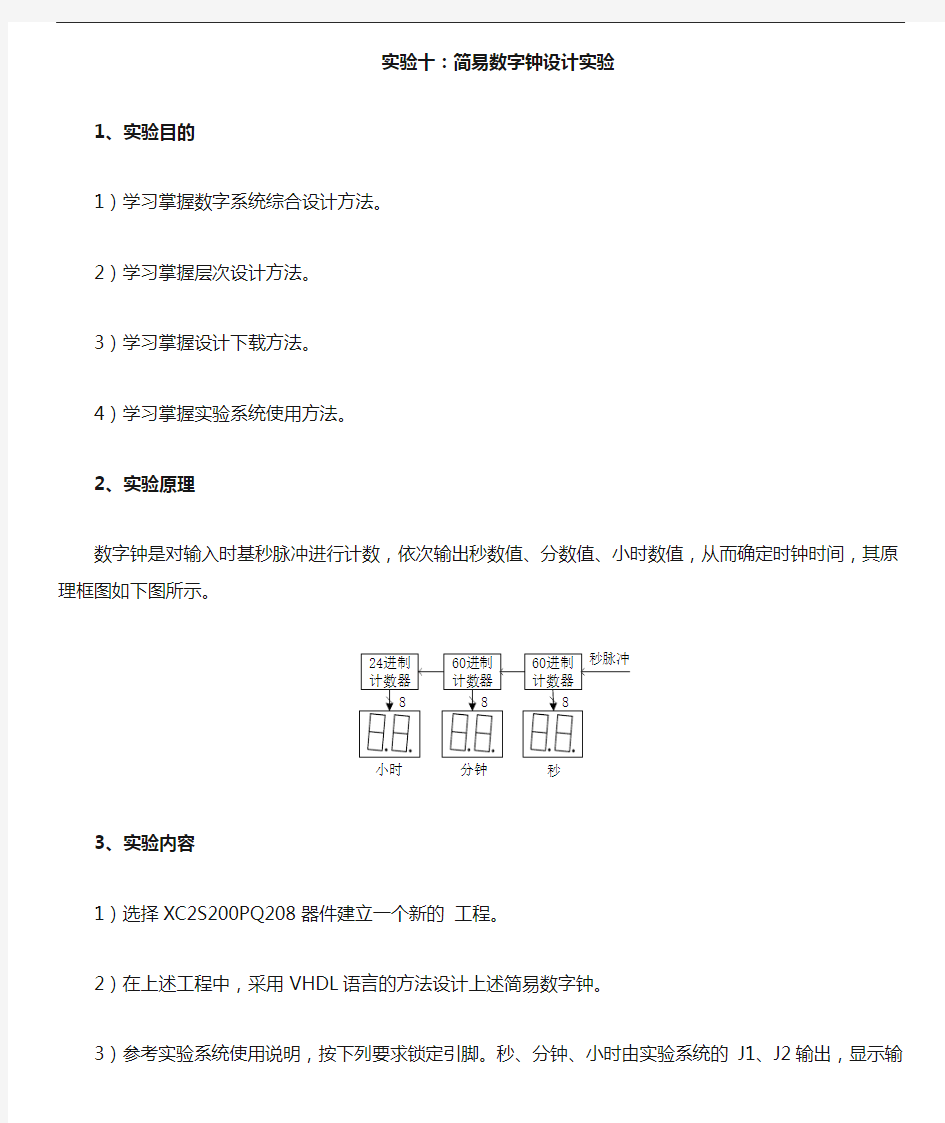

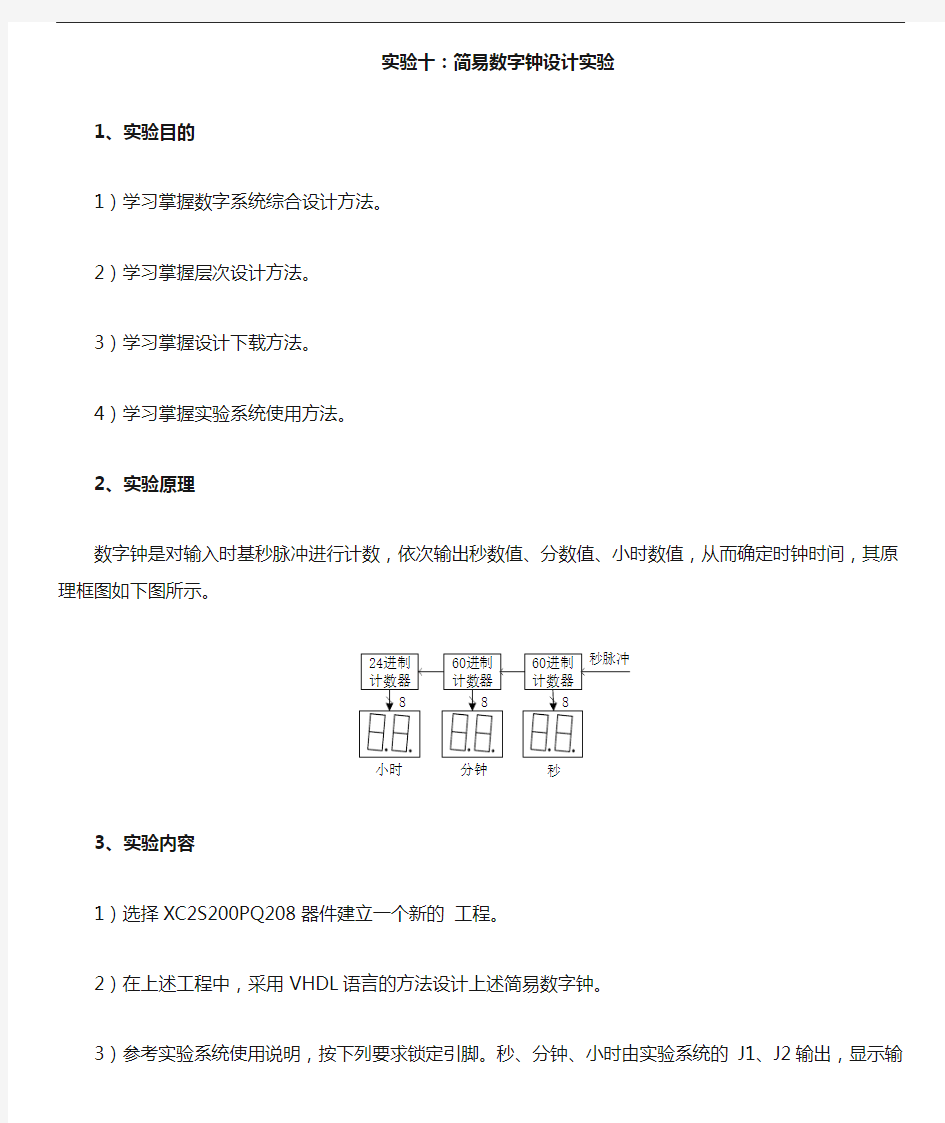

2、实验原理 数字钟是对输入时基秒脉冲进行计数,依次输出秒数值、分数值、小时数值,从而确定时钟时间,其原理框图如下图所示。

秒分钟

小时

3、实验内容

1)选择XC2S200PQ208器件建立一个新的 工程。

2)在上述工程中,采用VHDL 语言的方法设计上述简易数字钟。

3)参考实验系统使用说明,按下列要求锁定引脚。秒、分钟、小时由实验系统的J1、J2输出,显示输出的时分秒间隔一位数码管。时钟输入由J7的1脚输入。

4)下载编程并验证设计结果。

4、实验代码

module ZLT(clock,s1,s2,m1,m2,h1,h2 );

input clock;

output s1,s2,m1,m2,h1,h2;

reg [5:0] sec,min,hou;

reg mj,nj;

reg [3:0] s1,s2,m1,m2,h1,h2;

wire mt,nt;

initial

begin

mj=1;

nj=1;

min=58;

hou=23;

sec=58;

s1=0;

s2=0;

m1=0;

m2=0;

h1=0;

h2=0;

end

always@(posedge clock) begin

if(sec==59)

begin

sec<=0;

mj<=1;

end

else

begin

sec<=sec+1;

mj<=0;

end

end

assign mt=mj;

always@(posedge mt) begin

if(min==59)

begin

min<=0;

nj<=1;

end

else

begin

min<=min+1;

nj<=0;

end

end

assign nt=nj;

always@(posedge nt) begin

if(hou==23)

hou<=0;

else

hou<=hou+1; end

always@(sec)

begin

s1=sec%10;

s2=sec/10;

end

always@(min) begin

m1=min%10;

m2=min/10; end

always@(hou) begin

h1=hou%10;

h2=hou/10; end

endmodule

5、程序仿真