基于FPGA的数字相敏检波算法实现

- 格式:pdf

- 大小:297.07 KB

- 文档页数:4

FPGA实现数字相敏检波(DPSD)

原理是从⽹上论⽂找到的,⼤家⾃⼰找⼀下。

相敏检波利⽤互相关原理,能够⼗分有效地从噪声中提取出与参考信号具有相关性的待测信号的幅度和相位信息,同时忽略不相关的背景噪声的⼲扰。

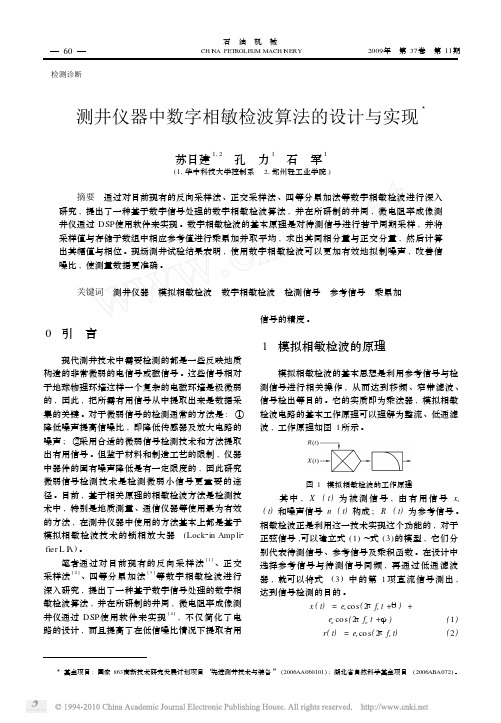

⼀、数字相敏检波原理

待测信号:x(t)为待测信号s(t)与系统噪声n(t)的叠加,表达式为: x(t) = s(t) + n(t) = A cos(wt +θ)+n(t)

r(t)为与待测信号s(t)同频率的参考信号,在r(t)与s(t)的相位关系不明确的情况下,欲测得s(t)的幅度A与相位差Θ,需要采⽤两组正交的参考信号r1(t)和r2(t)同时完成相敏检波流程。

假设参考信号幅值为1,相位为0,既:

r1(t)=cos(wt), r2(t)=sin(wt),

经过运算:

若认为噪声为随机噪声,与参考信号⽆关,则要积分时间⾜够长,n(t)的影响可以被消除得

显然,结合R1和R2即可求得待测信号的幅度A与相位θ。

⼆、DPSD算法实现

DPSD是上述模拟相敏检波的数字实现⽅式,⽤数学⽅式⾯熟互相关算法的表达式为:

从公式中,可以看出,DPSD算法需要对待测信号进⾏AD转换后再完成两者的乘法和累加操作,在这个过程中,诸多因素都可能对DPSD算法的精度照成影响。

算法输出信噪⽐与测量时间成正⽐,且在满⾜奈奎斯特采样率的前提下,采⽤频率对信噪⽐⽆直接影响。

但若考虑到电路中带通滤波器性能和采样率不⾜可能带来频率混叠,对⾼采样率对抑制ADC量化误差的积极作⽤,适当提⾼采样率对DPSD算法精度多少有些好处。

FPGA逻辑功能框图如下:。

基于FPGA的数字相敏检波算法实现

梁世盛;乔凤斌;张燕

【期刊名称】《自动化仪表》

【年(卷),期】2013(034)011

【摘要】数字相敏检波(DPSD)算法是一种有效的信号检测方法.针对某些高速采样系统采用现有DSP芯片控制模数转换和进行DPSD算法运算所出现的控制精度不高和运算速度慢等问题,详细分析了DPSD算法,设计了基于FPGA的数字相敏检波算法.该算法解决了控制信号精度不高等问题,满足高速采样系统对运算速度的要求.试验结果表明,基于FPGA的数字相敏检测算法在测试系统中能有较好的检测效果.【总页数】4页(P13-16)

【作者】梁世盛;乔凤斌;张燕

【作者单位】上海航天设备制造总厂,上海200245;上海航天设备制造总厂,上海200245;上海航天设备制造总厂,上海200245

【正文语种】中文

【中图分类】TP316+.2

【相关文献】

1.基于FPGA的FIR数字滤波器算法实现 [J], 蒋垒;王昌林;刘鎏;许冲

2.基于FPGA的高频全数字低电平系统算法实现 [J], 文良华;王贤武;李庆

3.基于FPGA的数字多波束算法实现 [J], 廉丹;

4.基于DSP和FPGA的短波功放数字预失真算法实现 [J], 郭雅琴;叶焱;刘太君;李

先印;程琪榕

5.基于SoC FPGA的数字荧光算法实现 [J], 张晋;严建桥;黄光明

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的多通道同步数字锁相放大器王晓娜;陈珂;陶鹏程;张莹莹【摘要】针对多通道弱信号检测的需求,提出了基于FPGA的多通道数字锁相同步检测技术方案.锁相放大器的相敏检波和低通滤波功能采用数字互相关算法实现.通过理论分析,优化了系统设计参数,减少了离散化效应和量化误差对锁相高次谐波抑制能力和动态储备的影响,并用仿真程序对互相关算法和选定的参数进行了验证.所研制的基于FPGA的四通道同步数字锁相放大器具有体积小和成本低等特点,其动态储备达100 dB,极限检测灵敏度达到10 nV,输入噪声密度为7.4 nV/Hz,通道隔离度大于80 dB.【期刊名称】《大学物理实验》【年(卷),期】2019(032)003【总页数】5页(P5-9)【关键词】数字锁相放大器;多通道检测;同步检测;互相关;FPGA【作者】王晓娜;陈珂;陶鹏程;张莹莹【作者单位】大连理工大学物理学院,辽宁大连 116024;大连理工大学光电工程与仪器科学学院,辽宁大连 116024;大连理工大学光电工程与仪器科学学院,辽宁大连 116024;大连理工大学物理学院,辽宁大连 116024【正文语种】中文【中图分类】TP216+.1锁相放大器技术从诞生至今,经历了不间断的发展,特别是DSP(digital signal processor)和FPGA(field programmable gate array)的出现,数字化逐渐成为锁相放大器的主要发展方向 [1-2]。

此外,数字化硬件平台成本较低,易于被模块化并方便地移植到其他系统中,且在不改变硬件平台的情况下,也可以利用升级软件算法的方法来提升系统整体的性能,因此,近年来数字锁相放大器获得了大规模的应用[3]。

FPGA技术近年来发展迅速,在对信号进行并行处理等方面与DSP和单片机等处理器相比,具有无可比拟的优势,因此,FPGA技术在多通道信号处理领域应用广泛[4-6]。

在相敏检波方面,FPGA技术对信号处理速度较快并且可以对兆赫兹频率段的信号进行检测。

1引言关于低频数字相位测量系统的设计与实现方法,提出了以单片机最小系统和复杂可编程逻辑芯片为核心的电路设计模型。

相位的数字测量方法基本分为硬件电路测量与A/D采样后利用软件计算两种。

硬件法测量由于电路结构比较复杂,易受外界干扰影响以及准确度较差的缺点,限制了其作用进一步发挥。

近年来,随着计算机硬件及其外围设备的日益发展,以数字信号处理为核心的软件法测量技术在相位差的测量中得到了越来越多关注,并且得到了较快发展。

同频率正弦信号间的相位差测量在电工技术、工业自动化、智能控制及通讯、电子等许多领域都有广泛的应用,如电工领域中的电机功角测试,介质材料的损耗角的确定等。

因此相位差测量有着广泛的实用价值。

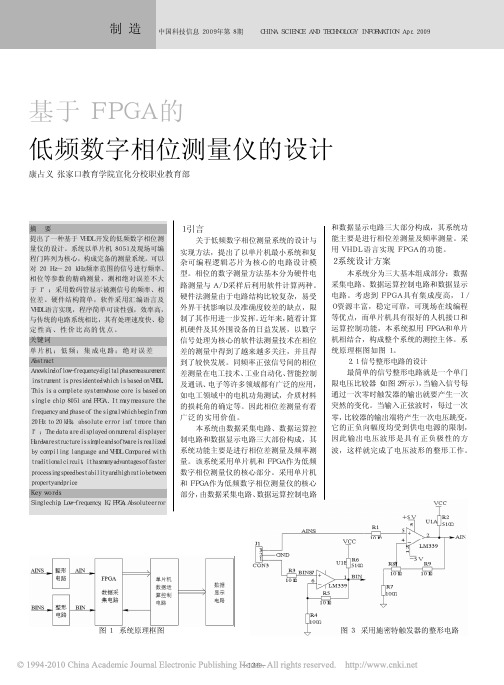

本系统由数据采集电路、数据运算控制电路和数据显示电路三大部份构成,其系统功能主要是进行相位差测量及频率测量。

该系统采用单片机和FPGA作为低频数字相位测量仪的核心部分。

采用单片机和FPGA作为低频数字相位测量仪的核心部分,由数据采集电路、数据运算控制电路基于FPGA的低频数字相位测量仪的设计康占义 张家口教育学院宣化分校职业教育部图1 系统原理框图图3 采用施密特触发器的整形电路和数据显示电路三大部分构成,其系统功能主要是进行相位差测量及频率测量。

采用VHDL语言实现FPGA的功能。

2系统设计方案本系统分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

考虑到FPGA具有集成度高,I/O资源丰富,稳定可靠,可现场在线编程等优点,而单片机具有很好的人机接口和运算控制功能,本系统拟用FPGA和单片机相结合,构成整个系统的测控主体。

系统原理框图如图1。

2.1 信号整形电路的设计最简单的信号整形电路就是一个单门限电压比较器(如图2所示),当输入信号每通过一次零时触发器的输出就要产生一次突然的变化。

当输入正弦波时,每过一次零,比较器的输出端将产生一次电压跳变,它的正负向幅度均受到供电电源的限制,因此输出电压波形是具有正负极性的方波,这样就完成了电压波形的整形工作。

电子技术• Electronic Technology86 •电子技术与软件工程 Electronic Technology & Software Engineering【关键词】带通采样 高频数字鉴相 多相低通滤波1 引言宽带探测系统可以很好的利用大带宽信号提供的更加丰富的目标信息和高分辨率,一般用与SAR/ISAR 成像等应用,是实现成像雷达的关键技术。

但是由于大带宽的影响,整个接收通道的设计十分困难,采用射频直采可有效简化接收通道的设计难度,灵活性更大,是实现数字接收机的关键技术。

同时鉴相质量直接决定了后续算法的结果质量,对系统指标十分关键。

基于FPGA 的高频数字鉴相技术文/张绘 王艳涛本文提出了一种基于FPGA 的通用高频数字鉴相技术,采用数字信号处理的方法进行鉴相,提高处理精度。

该技术将射频信号直接经过AD 采样后得到高频的数字信号,然后通过FPGA 进行高频数字鉴相得到用于后端信号处理的I/Q 信号,相对于传统的鉴相方法,减轻了前端模拟处理对性能的影响,并且更符合软件无线电技术的发展趋势。

2 高频数字鉴相如图1所示,高频数字鉴相的处理流程如下:将AD 采样得到的数字信号传送到FPGA 中,在此过程中,对数据进行了扩位降速处理;通过Matlab 设计生成用于在FPGA 中实现滤波器的系数进行滤波,由于数据量过大,进行带通滤波时采用了多路并行处理的方法;将Matlab 中设计的正余弦信号存入到FPGA 的块RAM 中,运用读取出的本振信号与带通滤波后的信号相乘实现变频;在多相低通滤波的过程中选择对固定的相位进行滤波处理来达到数据降速的目的,滤波之后的结果就是I/Q 路数字信号。

2.1 高频AD采样根据带通采样得知采样频率应满足以下两个关系式F s ≥2B (1) (2F c +B)/(m+1) ≤Fs ≤(2F c -B)/m (2)其中B 为被采样带通信号的带宽,本文中为130MHz ;F c 为被采样带通信号的中心频率,本文中为1.29GHz ;m 为满足(公式1)和(公式2)的任意正整数;F s 为采样频率,根据(公式1)和(公式2),本文中采用960MHz 。

基于FPGA的数字式相位测量仪的设计与制作基于FPGA的数字式相位测量仪的设计与制作摘要:本设计给出了基于FPGA核心的数字式相位测量的基本原理与实现方案,实现的是对两列信号的相位差的精确测量并数字显示测量结果。

该系统利用可编程逻辑器件为主系统芯片,用VHDL对其进行设计开发,系统由相位测量仪、数字式移相信号发生器和移相网络三个模块构成,整个装置具有原理简单,测量精度高,测量结果显示直观的特点。

本次设计在EDA软件开发平台MAX+PLUSⅡ上利用硬件描述语言VHDL进行设计编程。

关键词:FPGA/CPLD、VHDL、测相仪FPGA-based digital phase-measuring instrument design and production Abstract: The design is based on the FPGA core of the digital phase measurement and realization of the basic principles of the programme, the realization of the two signals in the phase of precision measurement and statistics show that the measurement results. The system of programmable logic devices based system chips, with their VHDL design and development, the system by the phase-measuring instrument, the digital shift believe that the phase-shifting, generator and a network of three modules, the device has a simple theory, measurement High-precision measurement results show that the visual characteristics. The design of the EDA software development platform MAX + PLUS Ⅱon the use of hardware description language VHDL design programming.Key words: FPGA / CPLD;VHDL;measurement of the instrument第1章绪论1.1 EDA技术概述1.1.1 引言20世纪末,电子技术获得飞速发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力推动社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

基于fpga的数字相敏检波算法实现fpga(Field Programmable Gate Array)是一种非易失可配置逻辑器件,成为当今技术发展的关键产品之一。

近年来,由于其高速处理能力、低功耗、低成本等特点,fpga在数字信号处理领域得到了越来越多的应用。

一种常见的应用就是基于fpga的数字相敏检波算法实现。

在基于fpga的数字相敏检波算法中,首先要实现的是数字滤波器的设计。

这里的滤波器必须能够满足信号处理的时序要求,保证信号有较低的噪声水平。

基于此,一般采用离散傅立叶变换(DFT)进行信号滤波,使用折线拟合技术对滤波系数进行优化,从而获得高质量的滤波结果。

接下来,应该实现的是数字相敏检波的算法。

首先,通过数字滤波器进行数据采样,并将数据转换为频域数据。

然后,为了解决检波问题,把信号进行振幅处理,使噪声的振幅大小小于某一特定阈值,以判断其检波结果。

最后,以系统仿真结果为准,基于fpga实现数字相敏检波算法。

数字相敏检波算法是fpga应用中常用的一种有效方法,它可以将信号进行调制和解调,从而控制信号的振幅。

此外,基于fpga的数字相敏检波算法具有较强的容错性和可靠性,可以提供调制解调以及精确测量等功能,在许多领域得到了广泛的应用。

综上所述,基于fpga的数字相敏检波算法是一种有效的信号处理技术,由于其低功耗、低成本特点,被广泛应用于许多领域。

它可以利用数字滤波器进行数据采样和频域数据转换;利用折线拟合技术优化系统性能;利用振幅处理和判断阈值实现信号检波;利用fpga实现算法,最终达到调制解调以及精确测量等功能。