用单片机低频数字式相位测量仪430

- 格式:doc

- 大小:2.15 MB

- 文档页数:14

105相位是交流信号的重要参数之一,相位差的测量是电子和电力测量中经常遇到的问题,如何获得准确的相位差已经越来越重要。

例如在电力系统中,当电网合闸时,要求两电网信号的相位必须相同,如果信号相位不同,就会在电网中产生很大的冲击电流,造成严重事故。

因此,相位测量在信号提取、检测、处理等方面有重要的应用意义。

随着数字电子技术在实际生产应用中的发展,由数字逻辑电路组成的控制系统已经逐渐成为现代测量、检测技术中的主要方法。

本文介绍了一种基于单片机和FPGA的低频数字相位测量仪,该设计具有测量精度高、反应速度快、稳定性好、读数方便等明显特点。

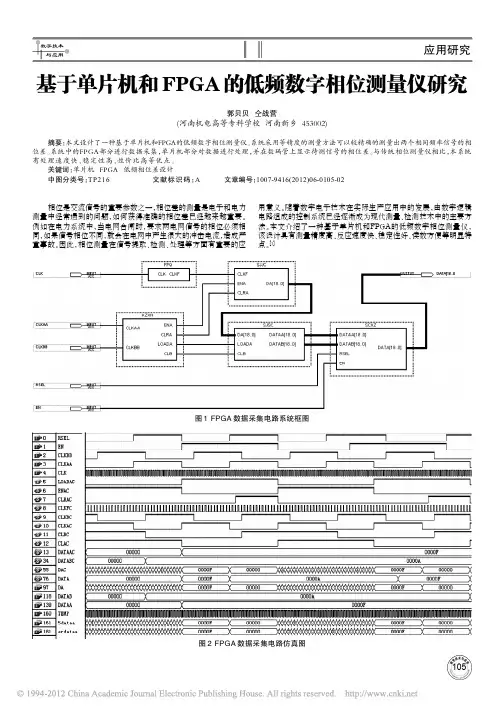

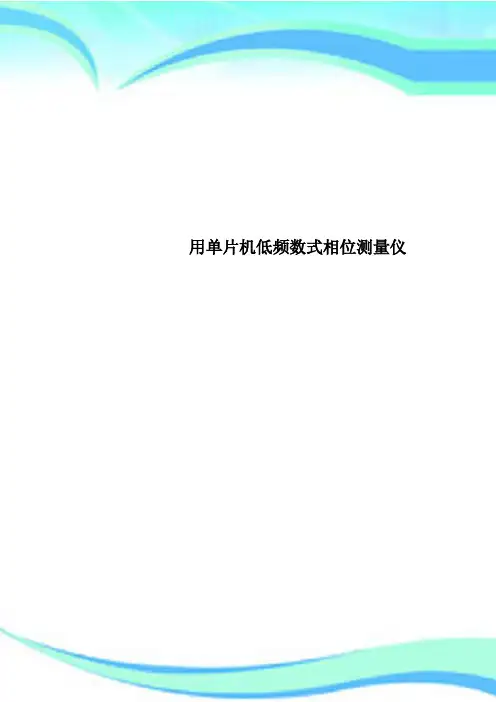

[1]图1 FPGA 数据采集电路系统框图图2 FPGA 数据采集电路仿真图基于单片机和FPGA 的低频数字相位测量仪研究郭贝贝 仝战营(河南机电高等专科学校 河南新乡 453002)摘要:本文设计了一种基于单片机和FPGA的低频数字相位测量仪。

系统采用等精度的测量方法可以较精确的测量出两个相同频率信号的相位差。

系统中的FPGA部分进行数据采集,单片机部分对数据进行处理,并在数码管上显示待测信号的相位差。

与传统相位测量仪相比,本系统有处理速度快、稳定性高、性价比高等优点。

关键词:单片机 FPGA 低频相位差设计中图分类号:TP216文献标识码:A文章编号:1007-9416(2012)06-0105-02106取相应的数据,最后再将模板文件转换为html网页文件呈现给用户,供浏览器端查阅。

4、实现功能定制报表提供了能源成本管理、能源平衡管理、能源台账管理、能源介质结算管理、能源介质综合管理等方面的管理、呈现和分析,提供了对各个工序、厂区在每天、每月、每年产品和副产品产出、原料消耗、能源生产与消耗的成本情况和能源折标情况;对能源管理过程中的重要能源介质进行深入的分析和管理;提供了公司各个主要能源介质在结算时的采购情况和外售情况并对公司内的各系统在公司各个主体工序、重要耗能设备的消耗量、单耗情况进行了统一综合的统计和分析。

用单片机低频数式相位测量仪————————————————————————————————作者:————————————————————————————————日期:低频数字式相位测量仪c65作者:吕锦柏 刘勇 冯科(山东理工大学) 赛前及文稿整理辅导教师: 姜吉顺 卢恒炜摘 要该数字式相位测量仪以单片机(89c52)为核心,通过高速计数器CD4040为计数器计算脉冲个数从,而达到计算相位的要求,通过8279驱动数码管显示正弦波的频率,不采用一般的模拟的振动器产生,而是采用单片机产生,从而实现了产生到显示的数字化.具有产生的频率精确,稳定的特点.相移部分采用一般的RC 移相电路,节省了成本。

一 方案论证与比较:1 常见正弦信号的测量方法:方案一:采用模拟分离元件 如二极管,三极管等非线性元件,实现频率的测量,检相的功能,使用起来方便,价格便宜,但采用分离元件由于分散性太大,不便于集成及数字化,而且测量误差大。

方案二:采用集成的检相器,检频器实现频率及相位的测量。

这种方法的实现框图如下:这种方法虽然可实现比较精确的测量,但由于模拟信号易受外界的干扰,不易调节,无法实现智能化,数字化的缺点,一般在要求较低的情况下使用。

方案三:此方案采用高速信号发生器产生20MHz 的高频信号,其主要特点是采用CD4040高频计数器结合单片机,利用计数脉冲实现测量相位与频率的目标。

这种方法克服了模拟电路的缺点,实现了数字化与集成化。

本设计采用了这种方法。

这种方案的组成框图:检相器相位及频率显检频器正弦波\二 系统总体设计按照题目要求,我们设计的相位测量系统包括三部分:正弦波产生系统(包括频率调整电路),移相电路和相位显视系统,其总体框图如下:三 各部分硬件电路设计及参数计算1、正弦波产生电路(一)方案一:利用8038芯片或MAX038可以实现压控的函数发生器通过改变少量的外围元件,可实现正弦波,方波,三角波,并可实现频率调节,但采用模拟器件由于元件分散性太大,即使使用单片函数发生器,参数也与外部元件有关,外接的电阻,电容对参数影响很大,因而产生的频率稳定度差,精度低,抗干扰能力差,调节困难,成本也高。

1 引言由于频率信号具有抗干扰性强、易于传输、测量准确度较高等优点,因此许多非频率量的传感信号都转换为频率量来进行测量和处理。

因此频率测量方法愈来愈引起关注和研究。

频率测量是测量和控制系统领域的最基本测量之一。

当今用的最多的测量信号频率的仪器是频率计,由于频率计在测量过程中需要一个时基信号作为测量信号频率的时基。

时基信号一般是由本机振荡电路发生的,尽管现在多用石英晶体振荡器,但是仍然不能保证时基信号的精度,因此频率计的测量精度也就成了问题。

传统的频率测量方法有两种[1]:一种是测频法,在一定时间间隔T内测出待测信号重复变化次数N,频率即为;另一种方法是测周法,在被测信号的一个周期内测出标准高频信号f的个数N,则被测频率。

本文介绍了一种测宽法[2],借助光电耦合原理,将交流信号转变成周期脉冲信号,通过捕获脉冲信号的下降沿,由定时器计数,通过二次计数的差值便能得到脉冲信号的周期,进而可以计算出所测交流信号的频率。

2 硬件电路设计硬件电路完成的任务是:(1)模拟电路部分的设计,其功能是进行信号的转化。

交流信号通过整流桥、光电耦合器等模拟器件便能得到周期脉冲信号。

(2)数字电路部分的设计,其功能是进行信号的检测。

MSP430单片机内部的16位定时器A具有脉冲捕获功能,能将脉冲信号的占空比检测出来。

图1为它的基本结构图。

图1 系统的基本结构2.1 模拟电路部分的设计图2为模拟部分原理。

下面主要阐述该电路的工作原理:图2模拟部分原理图考虑到交流信号中可能含有一定的直流信号,而直流信号会引起交流波形的上移或下移,这可能会导致原有交流信号没有零点,这就谈不上过零检测、周期脉冲了,因此要根据交流信号的实际情况,在交流信号的出口处用设个适当的电容,起到隔直的作用。

R1和R2是限流电阻,保护后面的稳压管、二极管、光电耦合器在额定功耗范围内。

由于这里的交流信号源选取的是220V市电正弦信号,所以R1和R2的阻值要比较大而且功率要比较大,该系统使用的是、1W的电阻。

低频相位测量仪硬件电路设计本设计提出了一种基于AT89C51单片机开发的低频数字相位测量仪的方案。

主要包括相位测量模块、单片机最小系统、显示模块、电源模块的设计。

可以对低频率范围的信号进行相位等参数的精确测量,测相绝对误差不大于1°。

相位测量模块采用对输入的两路信号(同频率、不同相位)通过比较器整形、鉴相器异或之后得到的相位差,输入到单片机的中断口进行数据采集处理;采用数码管显示被测信号的相位差。

硬件结构简单,软件采用汇编语言实现,程序简单可读写性强、效率高。

与传统的电路系统相比,其有处理速度快、稳定性高、性价比高的优点。

关键词相位差单片机低频误差(2.11.1 课题研究内容我们设计的数字式相位测量系统电路, 主要是由MCU 芯片和小规模的集成电路 构成。

两路待测信号(同频率、不同相位的两路信号)通过整形电路,变成矩形波信号, 再通过鉴相器,得到两路波形的正脉冲宽度,也就是所要测量的两路信号的相位差所 对应的时间差。

以上部分构成了相位测量系统的相位测量电路 ⑻。

将其送到MCU 外部中断口,再通过MCU 处理数据(数字滤波、计算、送数据、 键盘处理等),最后得到我们所要的相位值,并将其通过数码管显示出来。

2 方案选择2.1 设计方案论证从功能角度来看,相位测量仪要完成信号相位差的测量。

相位测量仪有两路输入 信号,也是被测信号,他们是两个同频率的正弦信号,频率范围为 20Hz~20KHz (正 好是音频范围),幅度为U PP =1~5V (可以扩展到0.3~5V ),但两者幅度不一定相等。

相位和相位差的概念⑷:令正弦信号为:A t ]= AmSi n — I 2.1式中Am 称为幅值(最大值),且Am 7;2A ,A 称为有效值;二t -‘t •称为相位,称为初相位,「称为角频率。

Am 、「、;:0称为正弦量的三要素 只有两个同频率的(正弦)信号才有相位差的概念。

不妨令两个同频率的正弦信号为: Ai (t )=A m Sin (豹t *%i ) ( 22)A 2 t A A zm Sin t02 则相位差:71 - t 0^ ^'t ' ' 0^ ~ 01 i 02(2.3) 由2.3式中可看出,相位差在数值上等于初相位之差,二是一个角度 不妨令二二T ,其中匚是相位差二对应的时间差,且令T 为信号周期,则有比例关系:「360 丁:二(2.4) 可以推导得到:n - TJT 3 6 0(2.5)式子2.5中可以说明,相位差二与一一对应,可以通过测量时间差及信号周期T,计算得到相位差v,这就是相位差的基本测量原理。

低频数字式相位测量仪c11石油大学(华东)尚海燕曹善甫梁锴摘要本系统由两片独立的CPU组成。

用MSP430实现基本要求中的相位、频率、电压测量及其数字和图形显示功能;用AVRmega8515实现扩展要求中的数字式移相信号发生器及其设置频率和相位的功能。

本设计充分利用了MSP430的高速硬件捕获功能来实现频率和相位的测量,并利用AD转换器对数据进行进一步处理,在高低频段分别采用多次测量、滤波算法、矢量分解、偏移修正等算法消除干扰提高精度,采用了大屏幕液晶显示测量的详细信息。

利用AVRmega8515配合16.384MHz的高速晶振,采用软件DDFS实现双路数字式移相信号发生器,由于使用优化算法,实现了高达每秒655.36K次的双路相位计算,输出频率为20Hz-40.48KHz,可实现20Hz的步进,系统硬件结构简单,频率、相位稳定度高;采用数码管显示和按键设置频率及相位差。

移相网络安题目要求由常规的模拟器件组成。

本系统主要由相位测量、移相网络和数字式移相信号发生器三大模块组成。

一、方案比较与论证1 、相位测量部分方案一:传统的模拟法。

该方案采用倍频、计数、门控等电路。

此方法难以实现大频率范围的相位测量,精度低、稳定性差。

方案二:采用双通道高速A/D对输入的信号进行采集,然后FFT和基波的矢量分解的方法计算出这两个信号的基频和相位。

该方案精度高,算法简单,对畸变波形有一定的处理能力。

但要求在AD采集前作频率测量,在信号频率较高时,需要使用超高速AD转换器并且需要较高的计算能力,一般需要使用DSP进行信号处理。

硬件复杂,难度较高。

方案三:整形鉴相法。

将输入的两相位不同的正弦波通过比较器进行整形,变成方波。

然后将两方波进行异或比较输出,从而得到两输入信号的过零时间差和两信号的周期,通过计算获得信号的频率和相位。

该方案较简单,但普通单片机需要通过扩展外部电路,增强计时、计数能力才能达到满足题目要求的精度。

低频数字式相位测量仪制作报告摘要本系统由低频数字相位频率测量仪,输入移相网络和数字式移相信号发生器组成。

利用CPLD,单片机控制模块实现了高精度的频率相位测量。

数字式移相信号发生器采用直接数字频率合成(DDFS)技术,输出频率范围宽,控制精度高。

由于在DDFS系统中采用了双D/A输出形式,信号幅度采用数字调节方式,输出信号幅度稳定。

移相网络的输入采用了自动增益控制(AGC),实现了高达48dB的宽范围输入,实现信号的自动稳幅输出。

此外,本系统友好的人机界面,合理实用的功能扩展,使整个系统更利于实际使用。

一.方案设计与论证1.相位频率测量部分方案一:对输入的两路正弦信号分别进行过零比较,并对生成的两路方波信号进行异或运算,得到占空比与相位差成正比的脉冲信号。

将该正弦送入单片机系统,对信号的脉宽进行测量,经计算得到输入的两路正弦信号的相位差。

单片机系统直接对过零比较后的方波信号计数,得到输入信号频率。

经单片机系统处理后,显示测量结果。

此方案电路相对简单,容易实现,但是受到单片机工作速度的限制,精度不高。

方案二:对输入的两路正弦信号分别进行过零比较,并对生成的两路方波信号进行异或运算,得到占空比与相位差成正比的脉冲信号。

由CPLD对相位差脉冲信号和频率信号进行计数,将计数结果送入单片机,单片机经过简单计算后显示测量结果。

此方案可以提高系统的测量精度,单片机要实现的功能相对简单,可以实现友好的人机界面。

缺点是电路相对复杂,成本较高。

系统框图详见图2-1。

综合考虑,这里采用了方案二。

2.移相网络部分方案一:直接采用题目中提供的参考电路。

此电路实现简单,但对于不同幅度的输入信号,不能做到自动稳幅输出。

对于小信号输入,无法满足题目输出峰-峰值0.3~5V的要求,除非采用可变增益放大器,在没有单片机控制的情况下,显然带来诸多不便。

方案二:以题目中提供的参考电路为基础,在信号输入前端加入自动增益控制电路(AGC),以适应各种幅度的信号输入。

测控技术与仪器专业课程设计报告班级:040852 :姬树明学号:04085144起始时间:2012-02-27 --- 2012-03-11课程设计题目:基于51单片机频率计的设计〔0—10MHz〕一、对题目的认识和理解1 引言本设计综合考虑了频率测量精度和测量反应时间的要求。

例如当要求频率测量结果为3位有效数字,这时如果待测信号的频率为1 Hz,则计数闸门宽度必须大于1 000 s。

为了兼顾频率测量精度和测量反应时间的要求,把测量工作分为两种方法:〔1〕当待测信号的频率>100 Hz时,定时/计数器构成为计数器,以机器周期为基准,由软件产生计数闸门,计数闸门宽度>1 s时,即可满足频率测量结果为3位有效数字;〔2〕当待测信号的频率<100 Hz时,定时/计数器构成为定时器,由频率计的予处理电路把待测信号变成方波,方波宽度等于待测信号的周期。

这时用方波作计数闸门,当待测信号的频率=100 Hz,使用12 MHz时钟时的最小计数值为10000,完全满足测量精度的要求。

二、本频率计的设计以AT89C51单片机为核心,利用他内部的定时/计数器完成待测信号周期/频率的测量。

单片机AT89C51内部具有2个16位定时/计数器,定时/计数器的工作可以由编程来实现定时、计数和产生计数溢出时中断要求的功能。

在定时器工作方式下,在被测时间间隔内,每来一个机器周期,计数器自动加1〔使用12 MHz时钟时,每1μs加1〕,这样以机器周期为基准可以用来测量时间间隔。

在计数器工作方式下,加至外部引脚的待测信号发生从1到0的跳变时计数器加1,这样在计数闸门的控制下可以用来测量待测信号的频率。

外部输入在每个机器周期被采样一次,这样检测一次从1到0的跳变至少需要2个机器周期〔24个振荡周期〕,所以最大计数速率为时钟频率的1/24〔使用12 MHz时钟时,最大计数速率为500 kHz〕。

定时/计数器的工作由运行控制位TR控制,当TR置1,定时/计数器开始计数;当TR清0,停止计数。

基于CPLD与MSP430的多功能数字相位频率测量系统基于CPLD与MSP430的多功能数字相位频率测量系统张世雄,祁玉林,边红昌,王应吉吉林大学电子科学与工程学院 130026Email:******************************摘要:本文介绍了一种基于CPLD与MSP430实现的全数字式控制、具有移相信号发生功能的相位频率测量系统。

本系统主要包括两大模块。

其相位频率测量模块设计了0°~360°相位差脉冲变换电路、脉冲同步多周期变换电路和周期法测频电路,可实现10Hz~20KHz两路正弦信号的高精度测相测频;其数字式移相信号发生模块利用DDS 原理设计了数控移项信号发生器,可数控产生0°~359.99°相位差、1Hz ~10MHz的两路正弦信号。

关键词:CPLD DDS 相位测量频率测量数控移相1.引言本设计源于2003年全国大学生电子设计竞赛C题——低频数字式相位测量仪。

在题目要求的功能指标基础上设计了此多功能数字相位测量系统。

本系统主要包括两大模块:相位频率测量模块,数字式移相信号发生器模块。

目前常见的相位测量方法有:①模拟差脉积分法②传统单周期计数法③正弦信号数值采样法④多周期脉冲计数法。

模拟差脉积分法电路复杂且对元器件要求较高;传统的单周期计数法对高频信号精度较低;本设计采取多周期脉冲计数法提高测量相位精度。

对于常见的正弦信号产生方法有:①锁相环式频率合成器法②专用的DDS芯片法③利用DDS原理CPLD 实现法。

锁相环式频率合成器法难以实现数控移相功能;采用专用的DDS芯片价格较高;综合考虑,我们利用DDS 原理设计了数控移相发生器,实现数控移相、信号产生功能。

3. 相位测量模块设计:本模块主要包括输入信号变换,测频,测相三大部分。

3.1 输入信号变换部分:输入信号变换电路部分包括放大、整形两级电路(具体电路见图9)。

前级输入采用开环放大,以增加信号的上升沿陡度,尽可能减小后级过零比较时出现的附加相移误差,器件选择低噪、高精度、高速运放OP37。

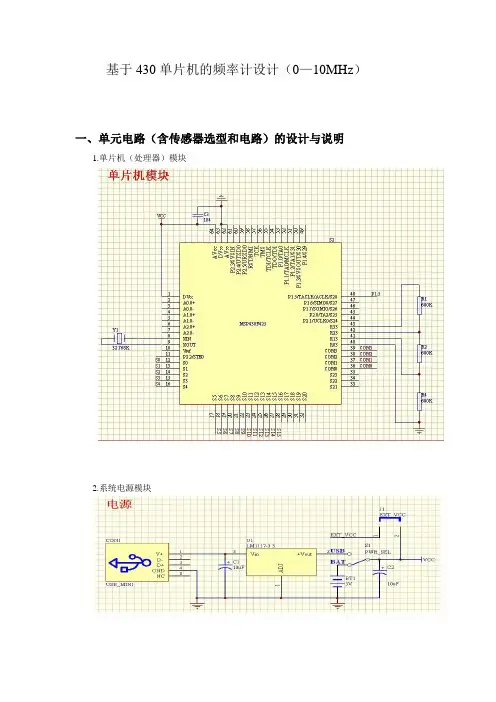

基于430单片机的频率计设计(0—10MHz)一、单元电路(含传感器选型和电路)的设计与说明1.单片机(处理器)模块2.系统电源模块3.JTAG在线调试接口4.LCD显示器模块5.频率信号入口二、监控软件设计与说明(1)程序流程图(2)主程序/************基于430单片机频率计程序**************************************** 说明:本程序实现了超低功耗的频率测量,测量范围:0~429MHz,分辨率:0.1Hz,完全满足0~10MHz的范围要求,10s产生一次定时中断,并检测在此时间内的脉冲个数Freq=TA_OverflowerCnt*65536 + TAR******************************************************************************/ #include "msp430x42x.h"#include "LCD_Display.h"unsigned long int Freq; //频率测量结果存放变量unsigned int TA_OverflowerCnt;//TA溢出次数存放变量unsigned char Timer5=0;//BT定时时基计时用全局变量,实现倍数次定时时基void main( void ){WDTCTL = WDTPW + WDTHOLD;//停止看门狗FLL_CTL0 |=XCAP18PF; //配置晶振电容P1DIR &=~BIT5; //P1.5(TACLK)作为输入引脚P1SEL |=BIT5; //允许其第二功能,作为TACLK输入BTCTL =BTDIV+BT_fCLK2_DIV256; //BasicTimer设为2s一次中断IE2 |=BTIE; //允许BasicTimer中断_EINT(); //允许总中断LCD_Init(); //初始化LCDfor(;;){LPM3; //休眠,等待被BasicTimer中断唤醒,10s唤醒一次/****************以下代码每10秒运行一次********************************/ Freq=TA_OverflowerCnt*65536 + TAR; //读取上次TA计数值及溢出次数,计算频率TA_OverflowerCnt=0; //溢出次数清零TACTL=TASSEL_0 + MC_2 +TAIE + TACLR; //TA清零并重新开始计数if(Freq>=10000000)//MHz级别的显示(7个0),1S周期内对应6个0才是MHz,故10s//对应7个{Freq=Freq/1000000;//省略了先除以10,再乘以10的算术操作,故此处只除以6个0 LCD_DisplayDecimal(Freq,1);LCD_InsertChar(mm);LCD_InsertChar(HH);LCD_InsertChar(ZZ);}else if(Freq>=10000) //KHz级别显示(4个0),1S周期内对应3个0才是KHz,故10s//对应4个{Freq=Freq/1000;//省略了先除以10,再乘以10的算术操作,故此处只除以3个0LCD_DisplayDecimal(Freq,1);LCD_InsertChar(KK);LCD_InsertChar(HH);LCD_InsertChar(ZZ);}else //Hz级别显示{Freq=Freq*10;//显示一位小数之前需对该值扩大10倍LCD_DisplayDecimal(Freq,1);LCD_InsertChar(HH);LCD_InsertChar(ZZ);}}}#pragma vector = BASICTIMER_VECTOR__interrupt void BT_ISR(void) //2s中断一次(由BasicTimer产生),每10s唤醒一次CPU {Timer5++;if(Timer5>=5) Timer5=0;if(Timer5==0)__low_power_mode_off_on_exit();//唤醒CPU}#pragma vector = TIMERA1_VECTOR__interrupt void TA_ISR(void) //为测量大于65536Hz的频率,计数溢出中断个数{switch(TAIV){case 2: break;case 4: break;case 10: TA_OverflowerCnt++;//TA每次溢出,溢出次数变量+1break;}}(3)LCD显示模块函数/***********MSP430F4XX系列LCD显示通用驱动程序**************************** 说明:该驱动程序库包含了常用的LCD显示功能,如显示数字、字母等可以作为各种程序的底层驱动使用。

现代电子学实验报告实验题目:低频数字相位测量仪姓名:年级:2012级指导教师:完成日期:2015年10月14日原创性声明本人声明本实验报告涉及的电路图、程序代码均为自己设计,没有抄袭他人的成果。

特此声明!声明人:目录摘要 (1)一、系统设计要求与技术指标 (2)二、方案选择与可行性论证 (2)2.1总体框架 (2)2.2频率测量 (2)2.3相位测量 (3)三、系统模块设计 (3)3.1信号整形电路的设计 (3)3.2 FPGA数据采集电路的设计 (5)3.2.1硬件部分 (5)3.2.2精度分析 (5)3.2.3软件部分 (5)3.3、单片机数据运算控制电路的设计 (6)3.3.1硬件部分 (6)3.3.2软件部分 (7)3.4、数据显示电路的设计 (10)3.4.1显示部分设计方案 (10)3.4.2数据显示电路 (10)四、参考资料 (12)附录 (13)主要器件介绍 (13)FPGA数据采集程序 (15)硬件电路图 (21)低频数字式相位测量仪的设计摘要:基于过零检测法原理,以单片机89C51和可编程逻辑器件CPLD为核心,从数据采集﹑数据运算控制、显示等电路功能电路设计,实现了一个低频数字式相位测量仪系统。

在此过程中,采用MCU与FPGA相结合的方案,将软件部分为数据采集、运算、控制和单片机控制显示两部分,充分发挥单片机具有的控制、运算能力强,FPGA数据采集速度快的特点来对实现各个模块功能进行程序设计,同时还对相关程序进行调试和仿真,验证了其可行性,使其性能接近最优。

而对硬件电路设计包括采用施密特触发器组成的整形电路、显示电路、FPGA 芯片及单片机外围电路等,实现了对频率信号频率、相位差的显示,同时配合系统完成数据采集、运算、控制等功能。

在上述基础上,本文还对有关频率信号的频率、相位测量技术及理论进行了研究和分析,对FPGA可编程芯片、单片机控制等的运用进行了学习,从而为课题研究奠定了理论基础。

mp430定时器转的一些文章:--------------------------MSP430的定时器中有比较捕获的概念,刚刚接触非常生疏。

看了半天终于清楚:比较模式:这是定时器的默认模式,当在比较模式下的时候,与捕获模式相关的硬件停止工作,如果这个时候开启定时器中断,然后设置定时器终值(将终值写入TACCRx),开启定时器,当TAR的值增到TACCRx的时候,中断标志位CCIFGx 置一,同时产生中断。

若中断允许未开启则只将中断标志位CCIFGx置一。

例子:比较模式就像51单片机一样,要能够软件设置定时间隔来产生中断处理一些事情,如键盘扫描,也可以结合信号输出产生时序脉冲发生器,PWM信号发生器。

如:不断装载TACCRx,启动定时器,TAR和TACCRx比较产生中断处理。

捕获模式:利用外部信号的上升沿、下降沿或上升下降沿触发来测量外部或内部事件,也可以由软件停止。

捕获源可以由CCISx选择CCIxA,CCIxB,GND,VCC。

完成捕获后相应的捕获标志位CCIFGx置一捕获模式的应用:利用捕获源的来触发捕获TAR的值,并将每次捕获的值都保存到TACCRx 中,可以随时读取TACCRx的值,TACCRx是个16位的寄存器,捕获模式用于事件的精确定位。

如测量时间、频率、速度等例子:利用两次捕获的值来测量脉冲的宽度。

或捕获选择任意沿,CCISx=”11“(输入选择VCC),这样即当VCC与GND发生切换时产生捕获条件结合利用:异步通讯同时应用比较模式和捕获模式来实现UART异步通信。

即利用定时器的比较模式来模拟通讯时序的波特率来发送数据,同时采用捕获模式来接收数据,并及时转换比较模式来选定调整通信的接受波特率,达到几首一个字节的目的----------------------------------------利用MSP430单片机定时器A和捕获/比较功能模块结合使用,实现脉冲宽度的测量。

本例程用到了定时器A的CCI1A端口(例如MSP430F14X的P1.2引脚)作捕获外部输入的脉冲电平跳变,同时结合简单的软件算法就能实现脉冲宽度的测量。

低频数字式相位测量仪作者:余蜜 刘勇 尹佳喜(华中科技大学) 获奖队编号:1-32赛前辅导教师:刘志强 文稿整理辅导教师:熊蕊摘要:本设计以凌阳16位单片机S PCE061A 和Lattice 公司的CPLD ispLSI 1032E 为核心,由相位测量、移相网络和数字式移相信号发生器三个子系统组成。

采用CPLD 与单片机相结合的方法,充分利用单片机丰富的资源以及CPLD 的高速特性,大大地拓宽了系统的工作频带,提高了系统的灵敏度和精确度,使系统运行稳定。

利用红外键盘使系统可以远距离无线控制。

关键词:相位测量,移相,CPLD ,DDS一 方案论证与设计1 相位测量仪方案方案一:单周波计数法。

将有相位差的两路方波信号进行”异或”后作为闸门,在高电平时,利用外部高频信号进行计数,在下降沿将数据读出,低电平时对计数器清零。

设晶振频率为f c ,测得信号的频率为f r ,计数值为N ,则相位差phase 为o crN f f phase 180⨯⨯=方案二:定时间计数。

将高频时钟信号和两路信号异或得到的信号进行“与”,在设定时间s 内利用其上跳变沿计数,设高频时钟频率为f c ,计数值为N ,则o csf Nphase 180⨯=方案三:多周期同步计数法。

设被测信号的频率为f ,则将一被测信号进行f 1倍(f 取整)分频,则在f 1周期内(保证测量时间在1s 左右),被测信号异或与参考高频信号相与的信号singal1的计数为N 1,同时期参考高频信号的计数为N ,则o NN phase 1801⨯=以上三种方案都可以采用一个D 触发器将相位测量的相位扩展到o 0-o 360。

方案一需高速时钟,按题目要求,在20kHz 信号时的相位差分辨率为0.1o ,则要求时钟最少为72MHz ,实现困难。

而方案二测量时间段一定,存在遗漏0~1个周波的情况,从而引入较大的误差。

方案三的读数与异或得到的信号同步,不存在遗漏问题,误差很小,故采用此方案。

基于单片机的低频数字相位测量仪的设计

史国清;倪晋平;刘文军

【期刊名称】《现代电子技术》

【年(卷),期】2005(28)8

【摘要】提出了一种基于AT89C52单片机开发的低频数字相位测量仪的设计.系统以单片机AT89C52及可编程逻辑器件为核心,构成完备的测量系统.可以对

10Hz~20 kHz频率范围的信号进行频率、相位等参数的精确测量,测相绝对误差不大于1°;采用数码管显示被测信号的频率、相位差.硬件结构简单,软件采用汇编语言实现,程序简单可读写性强,效率高.与传统的电路系统相比,其有处理速度快、稳定性高、性价比高的优点.

【总页数】2页(P80-81)

【作者】史国清;倪晋平;刘文军

【作者单位】西安工业学院,陕西,西安,710032;西安工业学院,陕西,西安,710032;西安工业学院,陕西,西安,710032

【正文语种】中文

【中图分类】TP398.1

【相关文献】

1.基于AVR单片机与FPGA的低频数字式相位测量仪 [J], 井新宇

2.基于单片机和FPGA的低频数字相位测量仪研究 [J], 郭贝贝;仝战营

3.基于单片机和FPGA的低频数字相位测量仪研究 [J], 郭贝贝;仝战营

4.基于FPGA的低频数字相位测量仪的设计 [J], 康占义

5.基于AT89S52的低频数字式相位测量仪的设计 [J], 贾雅琼; 俞斌

因版权原因,仅展示原文概要,查看原文内容请购买。

低频数字式相位测量仪摘要:本系统设计了一个基于现场可编程门阵列(FPGA)的低频数字式相位测量仪。

该测量仪包括数字式移相信号发生器和相位测量仪两部分,分别完成移相信号的发生及其频率、相位差的预置及数字显示、信号的移相以及移相后信号相位差和频率的测量与显示等功能。

其中数字式移相信号发生器可以产生预置频率的正弦信号,也可产生预置相位差的两路同频正弦信号,并能显示预置频率或相位差值;相位测量仪能对移相信号的频率、相位差的测量和显示。

两个部分均采用基于FPGA的数字技术实现,使得该系统具有抗干扰能力强, 可靠性好等优点。

关键词:现场可编程门阵列(FPGA),数字式移相信号发生器,相位测量仪1.总体方案设计根据系统的设计要求,本系统可分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

考虑到FPGA/CPLD具有集成度高,I/O资源丰富,稳定可靠,可现场在线编程等优点,而单片机具有很好的人机接口和运算控制功能,本系统拟用FPGA/CPLD 和单片机相结合,构成整个系统的测控主体。

如图1.1。

图1.1 系统原理框图1.1整形电路方案一:最简单的信号整形电路就是一个单门限电压比较器(如图1.2所示),当输入信号每通过一次零时触发器的输出就要产生一次突然的变化。

当输入正弦波时,每过一次零,比较器的输出端将产生一次电压跳变,它的正负向幅度均受到供电电源的限制,因此输出电压波形是具有正负极性的方波,这样就完成了电压波形的整形工作。

图1.2 采用单门限触发器的整形电路方案二:为了避免过零点多次触发的现象,我们使用施密特触发器组成的整形电路。

施密特触发器在单门限电压比较器的基础上引入了正反馈网络。

由于正反馈的作用,它的门限电压随着输出电压Uo 的变化而改变,因此提高了抗干扰能力。

本系统中我们使用两个施密特触发器对两路信号进行整形,电路图如图1.3所示。

图1.3 采用施密特触发器的整形电路1.2 相位测量方案方案一:采用脉冲填充计数法。

基于单片机和FPGA的低频数字相位测量仪研究随着电子技术的不断发展,数字相位测量技术也越来越成熟。

而基于单片机和FPGA的低频数字相位测量仪是目前应用最为广泛的一种数字相位测量设备。

本文将针对这一设备进行研究。

一、低频数字相位测量仪的研究背景低频数字相位测量仪是一种主要应用于电力系统中的高精度相位测量设备,可以用来测量电网中的电压、电流、功率等参数。

然而,由于电网的复杂性以及电气设备的特性,传统的模拟相位测量技术难以满足要求,因此数字相位测量技术逐渐成为了主流。

二、基于单片机和FPGA的低频数字相位测量仪研究1. 基本原理基于单片机和FPGA的低频数字相位测量仪,其基本原理是通过对输入信号进行数字化处理,计算出信号的相位差。

具体实现方式包括对输入信号进行取样、滤波、快速傅里叶变换等步骤,最终得到精准的相位测量结果。

2. 设计方案在设计方案中,单片机和FPGA分别负责不同的任务。

单片机主要用于控制信号的获取和预处理,而FPGA则负责完成数字信号的处理和相位计算。

具体实现过程中,单片机通过AD转换器将输入信号转换为数字信号,然后通过串口将数据传输到FPGA。

FPGA进行数字信号处理并通过输出端口返回结果。

3. 技术难点在实现过程中,主要涉及到数模转换、数字信号处理、相位计算等技术。

其中,相位计算是整个设计的核心。

在相位计算中,需要考虑到噪声、时钟漂移等因素对计算结果的影响。

因此,需要对数据进行滤波、校准和数据清零等处理。

三、总结基于单片机和FPGA的低频数字相位测量仪具有精度高、抗干扰能力强等优点,被广泛应用于电力系统中的相位测量。

在设计方案中,应该注意解决相位计算的难点问题,并加强对设备的监测和维护工作,确保设备的长期稳定运行。

低频数字式相位测量仪c11石油大学(华东)尚海燕曹善甫梁锴摘要本系统由两片独立的CPU组成。

用MSP430实现基本要求中的相位、频率、电压测量及其数字和图形显示功能;用AVRmega8515实现扩展要求中的数字式移相信号发生器及其设置频率和相位的功能。

本设计充分利用了MSP430的高速硬件捕获功能来实现频率和相位的测量,并利用AD转换器对数据进行进一步处理,在高低频段分别采用多次测量、滤波算法、矢量分解、偏移修正等算法消除干扰提高精度,采用了大屏幕液晶显示测量的详细信息。

利用AVRmega8515配合16.384MHz的高速晶振,采用软件DDFS实现双路数字式移相信号发生器,由于使用优化算法,实现了高达每秒655.36K次的双路相位计算,输出频率为20Hz-40.48KHz,可实现20Hz的步进,系统硬件结构简单,频率、相位稳定度高;采用数码管显示和按键设置频率及相位差。

移相网络安题目要求由常规的模拟器件组成。

本系统主要由相位测量、移相网络和数字式移相信号发生器三大模块组成。

一、方案比较与论证1 、相位测量部分方案一:传统的模拟法。

该方案采用倍频、计数、门控等电路。

此方法难以实现大频率范围的相位测量,精度低、稳定性差。

方案二:采用双通道高速A/D对输入的信号进行采集,然后FFT和基波的矢量分解的方法计算出这两个信号的基频和相位。

该方案精度高,算法简单,对畸变波形有一定的处理能力。

但要求在AD采集前作频率测量,在信号频率较高时,需要使用超高速AD转换器并且需要较高的计算能力,一般需要使用DSP进行信号处理。

硬件复杂,难度较高。

方案三:整形鉴相法。

将输入的两相位不同的正弦波通过比较器进行整形,变成方波。

然后将两方波进行异或比较输出,从而得到两输入信号的过零时间差和两信号的周期,通过计算获得信号的频率和相位。

该方案较简单,但普通单片机需要通过扩展外部电路,增强计时、计数能力才能达到满足题目要求的精度。

方案四:采用较高性能的混合信号处理器MSP430,采用方案三和方案二相结合的方式对输入信号进行处理,在高低频段混合采用矢量分解和两相比较器输出方波信号跳变时间的分析,准确计算出频率和相位差。

此方法由于使用了混合信号处理器MSP430,集成度高,片内包含多路高速且有缓冲存储能力的俘获单元,可以准确记录方波信号跳变时间,片内包括速度高达200k sps且有连续操作和缓冲存储能力的12位ADC,为扩展各项功能提供了支持。

软件部分实现了自动频率测量、相位测量、信号源电压测量、信号波形显示,用软件采用平均、矢量等算法进行多次复合测量消除噪声干扰、接触不良等引起的误差,并能在输入信号异常(如直流分量高、信号严重畸变、信号太小、输入信号超量称等)状态下自动报警,给出提示。

此方案硬件比方案二和方案三都简单,而且测量精度高,功耗低,体积小。

2、数字式移相信号的产生部分方案一:采用单片机的定时器产生数字信号,通过滤波或锁相等环节输出正弦信号。

该方案对单片机要求低,但产生的信号频率低,频率步进大,模拟部分产生较大相移,难以保证输出的相位精度,很难达到设计要求。

方案二:采用硬件直接数字频率合成(DDFS)技术产生数字信号。

直接频率合成方法具有频率转换时间短、近载频相位噪声性能好、精度高,产生的信号频率范围宽等优点,但由于需要采用地址,相位计算,访问存储器操作等环节,导致直接频率合成器结构复杂、体积庞大、成本高,功耗大。

而且即使使用大规模的PLD,也需要单片机来实现键盘、显示的控制等工作。

方案三:采用软件DDFS方法产生数字信号。

该方案硬件实现简单,产生的信号精度高,频率范围宽。

采用高速的AVR单片机,使用16.384MHz的晶体振荡器可实现软件DDFS算法,可以以655.36K的速度刷新双D/A,可实现20Hz的频率步进和从20Hz到40.96KHz的可移相的0~360度的信号输出。

完全可以满足题目的要求。

此方案由于使用了较高性能的单片机和充分优化的软件结构,在不降低系统性能的条件下,硬件简单、成本低、功耗低、可靠性高,具有较高的实用性。

3、模拟移相部分采用常见的模拟器件电阻,电位器,电容和运放的组合电路实现移相。

直接对模拟信号进行移相,如阻容移相,变压器移相等,早期的移相通常采用这种方式。

采用这种方式制造的移相器有许多不足之处,如:输出波形受输入波形的影响,移相操作不方便,移相角度随所接负载和时间等因素的影响而产生漂移等。

该方案由于使用模拟器件,因此精度不是很高,硬件系统比较复杂。

此类方案形式较多,但都难以消除作为模拟系统的弱点,在此不作详细讨论。

题目的基本要求部分既是采用此方案,我们按要求完成了这部分电路。

二、系统设计与计算1、数字式相位测量仪的设计总体设计:数字式相位测量仪的设计框图如图2-1所示。

使用高性能单片机MSP430F149为核心,前端的两路信号分别通过跟随器,直流耦合电路,提高了系统输入阻抗。

然后使用LM339比较器进行整形,输入到单片机的捕获端。

再令引一路信号,送给单片机的内部AD转换器。

通过单片机判断两通道的输入信号的上升沿和下降沿,对来自AD的数据进行处理,从而计算出两信号的相位差。

软件实现流程图:数字式相位测量仪的软件流程图如图2-2所示:图2-2 数字式相位测量仪的软件流程图器件的选择与计算:要使LM339比较器输出稳定,则要求其输入阻抗小于20K,而本题目要求系统输入阻抗大于100K,因此,在输入端我们选择使用一片LM324作为信号的输入缓冲,从而提高了系统的输入阻抗。

为了减少噪声的影响,在输入端我们使用200K的电阻接地。

如图2-3所示:图2-3 缓冲电路图LM339比较器比较容易受干扰,因此,在电源部分使用鉭电容,将未用输入端接固定电平,以保证LM339的稳定性。

LM339的输出为OC结构,使用时要接上拉电阻和分压电阻,使输出电平符合单片机要求。

如图2-4所示:如果使用施密特触发器可以是比较信号更稳定。

但这样影响相位的测量,因此本方案采用直接比较法,在软件中消除零点及噪声的干扰。

通过捕获处理后的两通道的方波,就可计算出频率和相位。

原理如图2-5所示:图2-5 相位计算示意图 计算公式为:tt∆=∆φ根据题目要求在20KHz 时,应保证2度的精度。

可计算出单片机的计时分辨精度为:6310*6.32360*10*20=Hz 当单片机的计时分辨精度优于3.6MHz 时,才能保证题目要求的精度。

我们使用的430F149使用8MHz 的晶振,足可以保证精度的要求。

以上是本方案的基本原理,实际使用中采用噪声消除和零点平移修正来减少系统误差。

本方案采用24位计时器,可以保证在被测信号周期为2秒时不会溢出。

可以满足对被测信号的最低频率要求。

误差分析:此方案中采用计时和鉴相处理。

其中计时部分使用单片机系统时钟。

此时钟来自于晶振,其误差很小可以忽略。

鉴相部分精度取决于从信号输入端到单片机捕获端通过的跟随器、电压比较器所产生的相位差和时间滞后。

本方案使用了直流耦合,使得由跟随器产生的相移误差几乎为零。

而两通道的电压比较器的时间滞后相同,为130ns 。

此外,本设计中使用单片集成的运放和比较器,一致性好,不会对测量结果产生影响。

由于输入信号和运放、比较器固有特性都可能产生零点偏移,使比较器的输出不平衡。

如果单边沿检测,显然影响精度。

本方案使用上下边沿都检测,然后通过计算来修正由零点漂移引起的误差。

2、数字式移相信号发生器的设计实现的基本原理:DDFS原理:DDFS的基本原理框图如图2-6所示。

图2-6 DDFS 的基本原理图DDFS包括信号幅值计算单元、存储正弦数据表的ROM存储器、DAC和输出滤波器组成。

正弦波的信号幅值以数据表的形式存储在ROM存储器中,由信号幅值计算单元以恒定的速度进行相位累加计算,计算出当前时刻的输出正弦信号的相位,然后用此相位在ROM种查得应送往DAC的数值。

通常使用的相位累加器由N位加法器与N位累加寄存器级联构成。

每来1个时钟脉冲,加法器将频率控制数据与累加寄存器输出的累积相位数据相加,把相加后的结果送至累加寄存器的数据输入端。

累加寄存器将加法器在上1个时钟作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下1个时钟的作用下继续与频率控制数据相加。

这样,相位累加器在参考时钟的作用下,进行线性相位累加,当相位累加器累积满量时就会产生1次溢出,完成1个周期性的动作,这个周期就是DDS合成信号的1个频率周期,累加器的溢出频率就是DDS输出的信号频率。

用相位累加器输出的数据作为取样地址,对正弦波波形存储器进行相位-幅值转换,即可在给定的时间上确定输出的波形幅值。

数模转换及低通滤波器:DAC将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号,低通滤波器用于滤除不需要的取样分量,以便输出特定频率段及平滑的正弦波信号。

按照Nyquist准则,最高输出频率可达0.5fc。

但考虑到实际低通滤波器性能的限制,实际最高输出频率一般取为40%fc。

通过对DDFS原理的分析,我们发现DDFS核心的是相位累加器、相位计算和ROM查表算发,通过CPU和软件完全可以完成同样的工作,本题需要输出移相信号,需要使用两路同频DDFS。

经过理论计算和软件测试,我们选用了A VRmega8515单片机,使用优化算法实现了图2-6的算法,实现了高达每秒655.36K次的双路相位计算。

软件DDFS与硬件DDFS的基本原理是相同的,同样输出频率下效果完全相同。

但软件DDFS用高性能的单片机来代替过去用PLD、ROM和单片机才能实现的功能。

从而使得操作更灵活、硬件电路更简单。

总体设计:数字式移相信号发生器的总体设计框图如图2-8所示:图2-8 数字式移相信号发生器的设计框图器件选择及相关的计算:题目要求频率范围在20Hz-20KHz,步进20Hz可得:频控字K从最低输出频率到最高输出频率变化至少20KHz/20Hz=1000,因此至少使用10位计数器。

从单片机的存储能力和计算能力考虑,使用16位无符号整形表示K,使用范围1-2048,即实际使用11位。

根据要求,为了在最高频率20KHz时输出平滑波形,使用32点输出,因此选择了具有665.36KHz的DA输出速度的DA0800器件。

在此频率下,在输出20.48KHz信号时保持32点输出,波形相当平滑。

最高可以输出40.96KHz信号。

在软件DDFS计算过程中,移位和计算ROM表的地址比较耗时,为了提高计算速度,使用了空间换时间的方法,在ROM表中连续构造每周波2048点的正弦表3个。

通过这种方法,减少了计算地址移位的时间和避免了B相相位叠加后溢出的问题。

通过优化,AVR CPU可以在25机器周期内完成两通道DDFS计算并送DA输出。