数电期末模拟题及答案

- 格式:docx

- 大小:75.62 KB

- 文档页数:13

数电期末考试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑运算是()。

A. 与运算B. 或运算C. 非运算D. 异或运算答案:C2. 一个触发器可以存储()位二进制信息。

A. 1B. 2C. 3D. 4答案:A3. 以下哪个不是组合逻辑电路的特点?()A. 输出只依赖于当前输入B. 输出与输入之间存在时延C. 没有记忆功能D. 任何时刻输出仅由该时刻的输入决定答案:B4. 一个4位二进制计数器可以计数到()。

A. 8B. 16C. 15D. 14答案:B5. 一个D触发器的特点是()。

A. 有两个稳定状态B. 只有一个稳定状态C. 没有稳定状态D. 以上都不是答案:A6. 在数字电路中,以下哪个不是基本的门电路?()。

A. 与门B. 或门C. 非门D. 异或门答案:D7. 一个3线-8线译码器可以译码()种不同的输入。

A. 3B. 8C. 6D. 7答案:B8. 一个8位寄存器可以存储()位二进制数。

A. 8B. 16C. 32D. 64答案:A9. 以下哪个是同步时序电路的特点?()A. 电路的输出仅依赖于当前的输入B. 电路的输出依赖于当前的输入和电路的历史状态C. 电路的输出不依赖于输入D. 电路的输出仅依赖于电路的历史状态答案:B10. 一个JK触发器可以表示()种不同的状态。

A. 1B. 2C. 3D. 4答案:B二、填空题(每题2分,共20分)1. 在数字电路中,一个基本的与门电路有_____个输入端和一个输出端。

答案:22. 一个4位二进制计数器的计数范围是从0到_____。

答案:153. 一个D触发器在时钟信号的上升沿到来时,其输出Q将与输入D保持_____。

答案:一致4. 在数字电路中,一个3线-8线译码器的输出是_____进制的。

答案:二5. 一个8位寄存器可以存储的最大十进制数是_____。

答案:2556. 一个JK触发器在J=0,K=0时,其状态将保持_____。

数字电子期末考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系有几种?A. 2种B. 3种C. 4种D. 5种答案:B2. 以下哪个不是基本的逻辑门?A. AND门B. OR门C. NOT门D. XOR门答案:D3. 一个触发器可以存储多少位二进制信息?A. 1位B. 2位C. 3位D. 4位答案:A4. 以下哪个是组合逻辑电路的特点?A. 输出状态与输入状态有关B. 输出状态与输入状态无关C. 输出状态只与当前输入状态有关D. 输出状态只与过去输入状态有关答案:A5. 以下哪个是时序逻辑电路的特点?A. 输出状态与输入状态有关B. 输出状态与输入状态无关C. 输出状态只与当前输入状态有关D. 输出状态与当前输入状态和过去输入状态都有关答案:D二、填空题(每空2分,共20分)6. 数字电路中,最基本的信号类型是______和______。

答案:数字信号;模拟信号7. 一个完整的数字系统通常由______和______两部分组成。

答案:硬件;软件8. 在数字电路中,常用的计数器类型有二进制计数器、______计数器等。

答案:十进制9. 一个8位的寄存器可以存储______个二进制位。

答案:810. 在数字电路中,信号的频率越高,其传输的______也越高。

答案:数据量三、简答题(每题10分,共30分)11. 简述数字电路与模拟电路的主要区别。

答案:数字电路处理的是离散的数字信号,而模拟电路处理的是连续的模拟信号。

数字电路具有更高的抗干扰能力,且易于实现大规模集成。

模拟电路则在信号处理的精度和连续性上有优势。

12. 解释什么是触发器,并简述其在数字电路中的作用。

答案:触发器是一种具有记忆功能的电路元件,可以存储一位二进制信息。

在数字电路中,触发器常用于存储中间结果,实现寄存器、计数器等功能。

13. 描述数字电路中同步计数器和异步计数器的区别。

答案:同步计数器的时钟信号同时控制所有触发器的时钟输入,而异步计数器的触发器时钟输入是独立控制的。

数电期末考试题库及答案 一、单项选择题(每题2分,共20分) 1. 在数字电路中,最基本的逻辑运算是( )。 A. 与运算 B. 或运算 C. 非运算 D. 异或运算

答案:C 2. 一个触发器可以存储( )位二进制信息。 A. 1 B. 2 C. 3 D. 4 答案:A 3. 以下哪个不是组合逻辑电路的特点?( ) A. 输出只依赖于当前输入 B. 输出与输入之间存在时间延迟 C. 没有记忆功能 D. 输出与输入之间不存在时间延迟

答案:B 4. 一个完整的二进制计数器至少需要( )个触发器。 A. 1 B. 2 C. 3 D. 4

答案:B 5. 一个D触发器的输出Q与输入D的关系是( )。 A. Q=D B. Q=非D C. Q=D的延迟 D. Q=非D的延迟

答案:A 6. 一个4位二进制计数器的状态数是( )。 A. 2 B. 4 C. 8 D. 16

答案:D 7. 在数字电路中,以下哪个不是基本的门电路?( ) A. 与门 B. 或门 C. 非门 D. 异或门

答案:D 8. 一个3线-8线译码器可以译码( )种不同的输入。 A. 3 B. 7 C. 8 D. 64

答案:C 9. 一个4位二进制数最大可以表示的十进制数是( )。 A. 15 B. 255 C. 1023 D. 4095 答案:B 10. 在数字电路中,以下哪个不是触发器的类型?( ) A. SR触发器 B. JK触发器 C. D触发器 D. T触发器

答案:D 二、填空题(每题2分,共20分) 1. 在数字电路中,使用最广泛的逻辑门是______门。 答案:与

2. 一个3位二进制计数器的状态数是______。 答案:8 3. 一个4线-16线译码器的输出线数是______。 答案:16

4. 在数字电路中,一个JK触发器的输出Q与输入J和K的关系是Q=______。

答案:J⊕K

5. 一个二进制数1011转换为十进制数是______。 答案:11

数电期末考试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑运算是()。

A. 与运算B. 或运算C. 非运算D. 异或运算2. 一个D触发器具有()个稳定状态。

A. 1B. 2C. 3D. 43. 一个四进制计数器有()个状态。

A. 4B. 8C. 16D. 324. 一个3线到8线译码器可以译出()种不同的二进制信号。

A. 3B. 4C. 8D. 275. 一个4位二进制计数器的计数范围是()。

A. 0到7B. 0到15C. 0到31D. 0到2556. 在数字电路中,若要实现逻辑“与”运算,应该使用()门。

A. 与门B. 或门C. 非门D. 异或门7. 触发器的输出状态取决于()。

A. 当前输入B. 上一状态C. 输入与上一个状态D. 外部控制信号8. 一个8位寄存器可以存储()位二进制数。

A. 1B. 4C. 8D. 169. 一个2进制计数器在计数过程中,其输出状态的变化规律是()。

A. 01, 10, 11, 00B. 00, 01, 11, 10C. 00, 01, 10, 11D. 00, 10, 01, 1110. 在数字电路中,若要实现逻辑“或”运算,应该使用()门。

A. 与门B. 或门C. 非门D. 异或门二、填空题(每题2分,共20分)1. 在数字电路中,逻辑“0”通常用电压______伏特表示,逻辑“1”通常用电压______伏特表示。

2. 一个3线到8线译码器的输入端有______个信号线,输出端有______个信号线。

3. 一个4位二进制计数器的进位链是______进制的。

4. 一个D触发器的输出Q与输入D的关系是______。

5. 在数字电路中,逻辑“非”运算的符号是______。

6. 一个4位二进制计数器的计数范围是______到______。

7. 一个3线到8线译码器可以译出______种不同的二进制信号。

8. 一个8位寄存器可以存储______位二进制数。

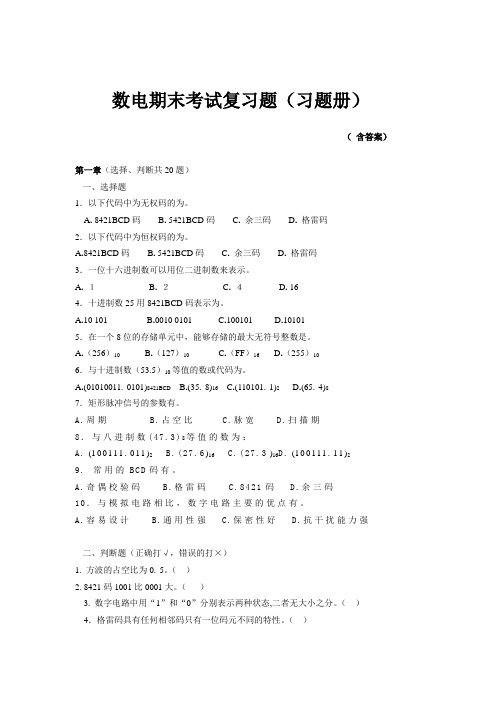

数电期末考试复习题(习题册)(含答案)第一章(选择、判断共20题)一、选择题1.以下代码中为无权码的为。

A. 8421BCD码B. 5421BCD码C.余三码D.格雷码2.以下代码中为恒权码的为。

A.8421BCD码B. 5421BCD码C.余三码D.格雷码3.一位十六进制数可以用位二进制数来表示。

A.1B.2C.4D. 164.十进制数25用8421BCD码表示为。

A.10 101B.0010 0101C.100101D.101015.在一个8位的存储单元中,能够存储的最大无符号整数是。

A.(256)10B.(127)10C.(FF)16D.(255)106.与十进制数(53.5)10等值的数或代码为。

A.(01010011.0101)8421BCDB.(35.8)16C.(110101.1)2D.(65.4)87.矩形脉冲信号的参数有。

A.周期B.占空比C.脉宽D.扫描期8.与八进制数(47.3)8等值的数为:A. (100111.011)2B.(27.6)16C.(27.3 )16D. (100111.11)29.常用的B C D码有。

A.奇偶校验码B.格雷码C.8421码D.余三码10.与模拟电路相比,数字电路主要的优点有。

A.容易设计B.通用性强C.保密性好D.抗干扰能力强二、判断题(正确打√,错误的打×)1. 方波的占空比为0.5。

()2. 8421码1001比0001大。

()3. 数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

()4.格雷码具有任何相邻码只有一位码元不同的特性。

()5.八进制数(18)8比十进制数(18)10小。

()6.当传送十进制数5时,在8421奇校验码的校验位上值应为1。

()7.在时间和幅度上都断续变化的信号是数字信号,语音信号不是数字信号。

()8.占空比的公式为:q = t w / T,则周期T越大占空比q越小。

()9.十进制数(9)10比十六进制数(9)16小。

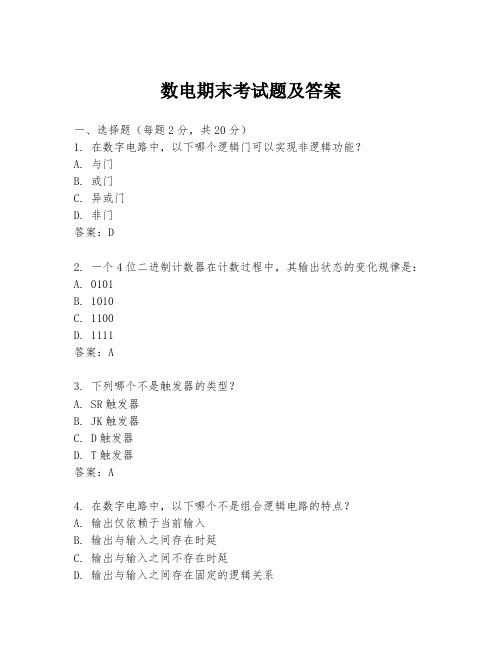

数电期末考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,以下哪个逻辑门可以实现非逻辑功能?A. 与门B. 或门C. 异或门D. 非门答案:D2. 一个4位二进制计数器在计数过程中,其输出状态的变化规律是:A. 0101B. 1010C. 1100D. 1111答案:A3. 下列哪个不是触发器的类型?A. SR触发器B. JK触发器C. D触发器D. T触发器答案:A4. 在数字电路中,以下哪个不是组合逻辑电路的特点?A. 输出仅依赖于当前输入B. 输出与输入之间存在时延C. 输出与输入之间不存在时延D. 输出与输入之间存在固定的逻辑关系答案:B5. 一个8位二进制数,其最大值是多少?A. 255B. 256C. 511D. 512答案:A6. 在数字电路中,以下哪个不是时序逻辑电路的特点?A. 输出不仅依赖于当前输入,还依赖于电路的过去状态B. 输出仅依赖于当前输入C. 输出与输入之间存在时延D. 输出与输入之间存在固定的逻辑关系答案:B7. 以下哪个逻辑门可以实现与非逻辑功能?A. 与门B. 或门C. 异或门D. 非门答案:A8. 一个3位二进制计数器在计数过程中,其输出状态的变化规律是:A. 000B. 001C. 010D. 100答案:A9. 在数字电路中,以下哪个不是触发器的类型?A. SR触发器B. JK触发器C. D触发器D. F触发器答案:D10. 一个16位二进制数,其最大值是多少?A. 65535B. 65536C. 131071D. 131072答案:A二、填空题(每题2分,共20分)1. 在数字电路中,一个2位二进制计数器可以表示______种不同的状态。

答案:42. 一个D触发器的输出状态取决于其______的状态。

答案:输入3. 在数字电路中,一个3-8译码器可以产生______个输出信号。

答案:84. 一个4位二进制计数器在计数过程中,其输出状态的变化规律是______。

数电期末考试题及答案 一、单项选择题(每题2分,共20分) 1. 在数字电路中,以下哪个逻辑门可以实现非功能? A. 与门 B. 或门 C. 异或门 D. 非门 答案:D

2. 二进制数1011转换为十进制数是多少? A. 8 B. 9 C. 10 D. 11 答案:D

3. 下列哪个触发器是边沿触发的? A. SR触发器 B. JK触发器 C. D触发器 D. T触发器 答案:C

4. 一个4位二进制计数器最多能表示多少个不同的状态? A. 8 B. 16 C. 32 D. 64 答案:B 5. 以下哪个不是组合逻辑电路的特点? A. 输出仅取决于当前输入 B. 输出与输入之间存在时延 C. 输出与输入之间不存在时延 D. 输出状态随输入状态变化而变化 答案:B

6. 一个3线-8线译码器能译码多少个输入? A. 1 B. 2 C. 3 D. 4 答案:C

7. 在数字电路中,以下哪个元件不是基本的逻辑门? A. 与非门 B. 或非门 C. 异或门 D. 放大器 答案:D

8. 一个8位二进制数能表示的最大十进制数是多少? A. 255 B. 256 C. 511 D. 512 答案:A

9. 以下哪个不是时序逻辑电路的特点? A. 输出不仅取决于当前输入,还取决于过去输入 B. 输出仅取决于当前输入 C. 输出状态随输入状态变化而变化 D. 输出状态随时间变化而变化 答案:B

10. 在数字电路中,以下哪个元件可以实现数据存储功能? A. 电阻 B. 电容 C. 二极管 D. 触发器 答案:D

二、填空题(每题2分,共20分) 1. 在数字电路中,逻辑0通常表示为电压______伏特。 答案:0

2. 一个D触发器的输出状态仅取决于时钟信号的______边沿。 答案:上升

3. 二进制数1101转换为十进制数是______。 答案:13

4. 一个3位二进制计数器最多能表示______个不同的状态。 答案:8

《数字电子技术》模拟题一一、单项选择题(2×10分)1.下列等式成立的是()A、A⊕1=AB、A⊙0=AC、A+AB=AD、A+AB=B2.函数F=(A+B+C+D)(A+B+C+D)(A+C+D)的标准与或表达式是()A、F=∑m(1,3,4,7,12)B、F=∑m(0,4,7,12)C、F=∑m(0,4,7,5,6,8,9,10,12,13,14,15)D、F=∑m(1,2,3,5,6,8,9,10,11,13,14,15)的RAM。

、、C、D、.函数F=A C+AB+,无冒险的组合为()。

B=C=1B、C=0D、B=C=OA、多谐振荡器B、施密特触发器C、双稳态触发器D、单稳态触发器二、判断题(1×10分)()1、在二进制与十六进制的转换中,有下列关系:()B=(9DF1)H()2、8421码和8421BCD码都是四位二进制代码。

()3、二进制数1001和二进制代码1001都表示十进制数9。

()4、TTL与非门输入采用多发射极三极管,其目的是提高电路的开关速度。

()5、OC与非门的输出端可以并联运行,实现“线与”关系,即L=L1+L2()6、CMOS门电路中输入端悬空作逻辑0使用。

()7、数字电路中最基本的运算电路是加法器。

()8、要改变触发器的状态,必须有CP脉冲的配合。

()9、容量为256×4的存储器,每字4位,共计256字,1024个存储单元。

()10、自激多谐振荡器不需外加触发信号,就能自动的输出矩形脉冲。

是否、C,CP,试四→4,试用8选1数据选择器74151和四位同步二进制加法计数器74LS161芯片设计序列信号发生器,序列信号为(左位在先),画出电路连线图。

附74LS161四位同步二进制加法计数器芯片功能表。

《数字电子技术》模拟题二一、单项选择题(2×10分)1.在下列数据中,数值最小的是()A 、59HB 、130OC 、1010111B8421BCD2.函数的标准与或表达式是()4D 触发器7,计9.用容量为16K ×8位存储芯片构成容量为64K ×8位的存储系统,需()片16K ×8位存储芯片,需()根地址线,( )根数据线。

A 、4,16,8B 、4,14,8 C 、2,16,8D 、2,14,16 10.集成单稳态触发器的暂稳态维持时间取决于()。

A 、 R 、C 元件参数B 、 所用门电路的传输延迟时间 C 、 触发脉冲持续的时间D 、 器件本身的参数二、判断题(1×10分)()1、8421码和8421BCD 码都是四位二进制代码。

()2、二进制数代码1000和二进制代码1001都可以表示十进制数8。

()3、保险库有一把锁,A、B两名经理各有一把钥匙,必须两名经理同时在才能开锁。

用F表示打开保险库锁的状态,F的逻辑表达式为:B=F+A()4、TSL门输出有三种状态。

()5、TG门只用于数字信号的传输。

()6、CMOS门电路中输入端悬空作逻辑0使用。

()7、要改变触发器的状态,必须有CP脉冲的配合。

()次()()2和JK4要求BC⊕,试用符号“×”对该电路矩阵进行恰当的编程。

AY(A)+=CB6、由集成四位比较器74LS85和集成计数器74LS161构成一个定时电路如图所示,Z是信号输出端。

比较器A3A2A1A0预置为1001,计数器的数据输入端DCBA预置为0010,试问:(1)当Z接在LD端时(R D置1),一个Z脉冲周期内包含多少个时钟脉冲CP?(2)当Z接在R D端时(LD置1),一个Z脉冲周期内又包含多少个时钟脉冲CP?简单写出分析过程四、设计题(10×2分)2、试用正边沿JK触发器和门器件设计一个模可变同步减计数器。

当X=0时M=3;当X=1时,M=4。

检查电路的自启动能力。

2、用两片74LS290(异步二-五-十进制加计数器)芯片设计一个54进制加计数器,画出电路连接图。

1234、欲使一路数据分配到多路装置应选用带使能端的:()a、编码器b、译码器c、选择器d、比较器5、JK触发器在CP脉冲作用下,欲使Q n+1=1,则必须使:()a、J=1,K=0b、J=0,K=0c、J=0,K=1d、J=1,K=16、触发器的状态转换图如下,则它是:()a、RS触发器b、D触发器c、JK触发器d、T触发器7、将三角波变换为矩形波,需选用:()a、施密特触发器b、多谐振荡器R()4、TTL与非门输入采用多发射极三极管,其目的是提高电路的抗干扰能力。

()5、OC与非门的输出端可以并联运行,实现“线与”关系,即L=L1+L2 ()6、在具有三组与输入端的与或非门中,当只使用其中的两组与输入端时,余下的一组与输入端应接高电平。

()7、数字电路中最基本的运算电路是加法器。

()8、要改变触发器的状态,必须有CP 脉冲的配合。

()9、容量为256×4的存储器,每字4位,共计256字,1024个存储单元。

()10、自激多谐振荡器不需外加触发信号,就能自动的输出矩形脉冲。

三、化简逻辑函数(12分)1、(6分)用公式法:C AB C B BC A AC L +++= 2、 (6分)用卡诺图法:D AB C B A ABD D C B B A L ++++=1、,B ,C 与输达式;3)2C ,输出1.2、(方程,3.求出Q 0,Q 1的设Q 0,Q 1的六、《数字电子技术》模拟题一解答及评分标准 一、单项选择题(2×10分)1、C2、D3、A4、B5、D6、B7、D8、C9、A 10、B评分标准:每题2分,做对一个2分,错误不给分。

二、判断题(1×10分) 1、√ 2、× 3、× 4、√ 5、×6、×7、√8、×9、√ 10、√评分标准:每题1分,做对一个1分,错误不给分。

三、分析计算题(7×6分) 1、∑=)9,8,6,4,3,2(),,,(m D C B A F ,∑=++=)15,14,13,12,11,10,9,8,6,4,3,2(1m C B D B A F ,(3分)要使,1F F =则F 中含有无关项(1分),无关项为:∑)15,14,13,12,11,10(d (3分)。

2、解答如下:F C B A C B A C B A F 21345发器就翻为才会改变(分钟脉状态6四、1、解:设计步骤如下:(1)确定触发器个数K 。

K =3,因为状态数N =5,符合2K -1<N <2K。

电路状态用Q 3Q 2Q 1表示。

(1分)(2)列状态转换真值表。

根据D 触发器的次态方程DQ n =+1,列状态转换真值表,如下表表示。

(3分),各个量填对计0.5分。

状态转换真值表D3、D2、、D2、D1的所示。

(3(5代入激励知所有的001;111(62CP B接对各个模8计数器使用。

(1分)当74LS161芯片的输入端P、T、T C、D L都接高电平“1”时,芯片就是一个模16计数器,Q D Q C Q B Q A的状态号从0、1、2直至15。

如果不使用输出端Q D,则Q C Q B Q A的状态号从0、1、2直至7。

在这种情况下,芯片就可当作模8计数器使用。

(2分)设8选1数据选择器的地址信号输入端从高到低为C、B、A,而74LS161芯片的4个数据输出端从高到低为Q D、Q C、Q B、Q A。

只需将Q A接A,Q B接B,Q C接C,(2分)数据选择器的8个数据输入端X0至X7分别接1、1、0、0、1、1、0、1就可以实现设计目的。

(2分)电路图如下图所示,图中F为序列信号输出端。

(图中D、C、B、A 接地,是为了避免干扰信号进入。

)(1分)序列信号发生器电路图《数字电子技术》模拟题二参考答案及评分标准一、单项选择题(2×10分)1.11、((2(3(42、8(1若方法不同,按结论酌情给分。

3、8分(1)状态真植表:(4分) (2)特性方程:(1分) (3)JK 触发器的特性方程:PH K HP J =⊕=∴(1分)(4)D 触发器的特性方程:D Qn =+1∴4、8JK 若K 5、86、(1(2) 一个Z 脉冲周期内又包含9个时钟脉冲CP 。

5分若方法不同,按结论酌情给分。

四、设计题(10×2分)1、 设计题(10分)(1)状态表:6分110=n时,810、b10、?。

下降沿状态表波形图功能:4位二进制异步加法计数器六、(10分)1.R D为清零端,异步清零;L D为置数控制端,同步置数;A、B、C、D为置数输入端,A为低位,D为高位;Q A、Q B、Q C、Q D为输出端,Q A为低位、Q D为高位;RCO为输出使能控制端。

2、。