卷积码编码器的设计 (1)汇总

- 格式:doc

- 大小:791.50 KB

- 文档页数:13

湖南文理学院课程设计报告学生姓名: 指导教师:完成时间:2014-11-18报告成绩:课程名称: 通信系统课程设计 专业班级:通信工程11102班09朱涛 侯清莲、设计要求 二、设计作用与目的 三、所用设备及软件 四、卷积码编码的概念五、EDA 设计方法及工具软件QUARTUB7.1 VHDL 设计的优点与设计方法八、心得体会 九、参考文献目录4.1卷积码的编码描述方法4.3 4.44.2 卷积编码 卷积码的树状图 卷积码的网格图六、 改变卷积编码器的参数仿真以及结论6.1 不同回溯长度对卷积编码器性能的影响 6.2 不同码率对卷积编码器误码性能的影响 6.3不同约束长度对卷积编码器的误码性能影响七、 卷积码编码器的VHDL 设计与仿真7.2卷积码编码器的VHDL 实现10 10 11卷积编码器的设计三、所用设备及软件(1) QUARTUS ⑵PC 机四、卷积码编码的概念4.1卷积码的编码描述方法编码描述方法有5种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述法和网格图描述法。

卷积码的纠错能力随着N 的增加而增大,而差错率随着 N 的增加而指数下降。

在编码器复杂性相同的情况下,卷积码的性能优于分组码。

分组码有严格 的代数结构,但卷积码至今尚未找到如此严密的数学手段。

分组码的译码算法可以由其代 数特性得到。

卷积码虽然可以采用适用于分组码的门限译码(即大数逻辑译码),但性能 不如维特比译码和序列译码[2]。

以二兀码为例,输入信息序列为 u = ( U 0,U 1,…),其多项式表示为u(x) = U 0+U 1X +…+…。

编码器的连接可用多项式表示为 g 1,1)(x) = 1+X+X 2和g (1,2)(x) = 1+x 2,称为码的子生 成多项式。

它们的系数矢量g (1,1)=(111)和g (1,2)=(101)称作码的子生成元。

以子生成多项式 为阵元构成的多项式矩阵 G(x) =[ g (1,1)(x), g (1,2)(x)],称为码的生成多项式矩阵。

长沙理工大学《通信电路EDA》课程项目报告系别计通系专业通信工程班级通信1203班指导教师单树民项目组组长历洋学号201254080312 项目组成员刘鼎新学号201254080330 项目组成员陈士怡学号201254080324 项目组成员侯耀文学号201254080323完成日期2014年11月5日目录1 引言 (3)1.1项目背景 (3)2 卷积码编解码器的结构概述 (4)2.1 卷积码编码器的结构 (4)2.2 卷积译码器的结构 (4)3 卷积码编解码器的VHDL设计 (5)3.1 VHDL设计的优点与设计方法 (5)3.2 卷积码编解码器的VHDL实现 (6)3.2.1 卷积编解码器顶层建模的VHDL描述 (7)3.2.2 用MAX+PLUSⅡ编译后生成的编解码器图形符号错误!未定义书签。

3.2.3 卷积编解码器VHDL仿真波形 (9)4 后记 (11)基于VHDL的卷积码编解码器的设计1 引言1.1项目背景现代数字通信有两个基本的理论基础,即信息论和纠错编码理论,它们几乎是同时在第二次世界大战结束后不久诞生的。

前者首先由Shannon以他的不朽名著“通信的数学理论”为标志建立起来的,而后者则以Hamming的经典著作“纠错和检错编码”为代表。

Shannon信息论主要讨论信息的度量,以及对于信息表示和信息传输的基本限制。

信道编码定理告诉我们,只要信息传输速率小于信道容量,则信息传输可以以任何小的错误概率进行。

但是,Shannon信息论并没有告诉我们如何去实现这一点。

Hanmming提出的纠错编码理论正是为了解决这个问题。

科学技术的发展使人类跨入了高度发展的信息化时代。

在政治、军事、经济等各个领域,信息的重要性不言而喻,有关信息理论的研究正越来越受到重视。

20世纪50年代信息论在学术界引起了巨大的反响。

20世纪60年代信道编码技术有了较大进展,成为信息论的又一重要分支。

信道编码技术把代数方法引入到纠错码的研究,使分组码技术的发展到了高峰,找到了大量可纠正多个错误的码,而且提出了可实现的译码方法。

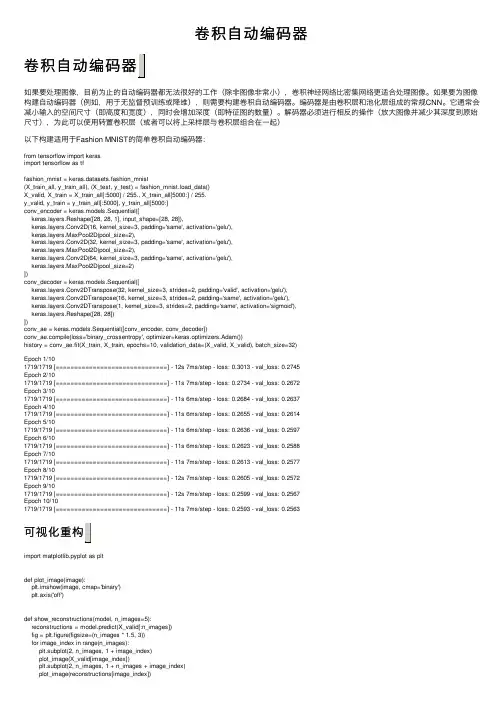

卷积⾃动编码器卷积⾃动编码器如果要处理图像,⽬前为⽌的⾃动编码器都⽆法很好的⼯作(除⾮图像⾮常⼩),卷积神经⽹络⽐密集⽹络更适合处理图像。

如果要为图像构建⾃动编码器(例如,⽤于⽆监督预训练或降维),则需要构建卷积⾃动编码器。

编码器是由卷积层和池化层组成的常规CNN。

它通常会减⼩输⼊的空间尺⼨(即⾼度和宽度),同时会增加深度(即特征图的数量)。

解码器必须进⾏相反的操作(放⼤图像并减少其深度到原始尺⼨),为此可以使⽤转置卷积层(或者可以将上采样层与卷积层组合在⼀起)以下构建适⽤于Fashion MNIST的简单卷积⾃动编码器:from tensorflow import kerasimport tensorflow as tffashion_mnist = keras.datasets.fashion_mnist(X_train_all, y_train_all), (X_test, y_test) = fashion_mnist.load_data()X_valid, X_train = X_train_all[:5000] / 255., X_train_all[5000:] / 255.y_valid, y_train = y_train_all[:5000], y_train_all[5000:]conv_encoder = keras.models.Sequential([yers.Reshape([28, 28, 1], input_shape=[28, 28]),yers.Conv2D(16, kernel_size=3, padding='same', activation='gelu'),yers.MaxPool2D(pool_size=2),yers.Conv2D(32, kernel_size=3, padding='same', activation='gelu'),yers.MaxPool2D(pool_size=2),yers.Conv2D(64, kernel_size=3, padding='same', activation='gelu'),yers.MaxPool2D(pool_size=2)])conv_decoder = keras.models.Sequential([yers.Conv2DTranspose(32, kernel_size=3, strides=2, padding='valid', activation='gelu'),yers.Conv2DTranspose(16, kernel_size=3, strides=2, padding='same', activation='gelu'),yers.Conv2DTranspose(1, kernel_size=3, strides=2, padding='same', activation='sigmoid'),yers.Reshape([28, 28])])conv_ae = keras.models.Sequential([conv_encoder, conv_decoder])conv_pile(loss='binary_crossentropy', optimizer=keras.optimizers.Adam())history = conv_ae.fit(X_train, X_train, epochs=10, validation_data=(X_valid, X_valid), batch_size=32)Epoch 1/101719/1719 [==============================] - 12s 7ms/step - loss: 0.3013 - val_loss: 0.2745Epoch 2/101719/1719 [==============================] - 11s 7ms/step - loss: 0.2734 - val_loss: 0.2672Epoch 3/101719/1719 [==============================] - 11s 6ms/step - loss: 0.2684 - val_loss: 0.2637Epoch 4/101719/1719 [==============================] - 11s 6ms/step - loss: 0.2655 - val_loss: 0.2614Epoch 5/101719/1719 [==============================] - 11s 6ms/step - loss: 0.2636 - val_loss: 0.2597Epoch 6/101719/1719 [==============================] - 11s 6ms/step - loss: 0.2623 - val_loss: 0.2588Epoch 7/101719/1719 [==============================] - 11s 7ms/step - loss: 0.2613 - val_loss: 0.2577Epoch 8/101719/1719 [==============================] - 12s 7ms/step - loss: 0.2605 - val_loss: 0.2572Epoch 9/101719/1719 [==============================] - 12s 7ms/step - loss: 0.2599 - val_loss: 0.2567Epoch 10/101719/1719 [==============================] - 11s 7ms/step - loss: 0.2593 - val_loss: 0.2563可视化重构import matplotlib.pyplot as pltdef plot_image(image):plt.imshow(image, cmap='binary')plt.axis('off')def show_reconstructions(model, n_images=5):reconstructions = model.predict(X_valid[:n_images])fig = plt.figure(figsize=(n_images * 1.5, 3))for image_index in range(n_images):plt.subplot(2, n_images, 1 + image_index)plot_image(X_valid[image_index])plt.subplot(2, n_images, 1 + n_images + image_index)plot_image(reconstructions[image_index])show_reconstructions(conv_ae)。

卷积编码作者:韩丽君来源:《卷宗》2013年第11期摘要:空时格型码是建立在卷积码的基础上设计出来的,文中通过三种方法来说明卷积码的编码过程,为我们设计出高性能的空时码字提供理论依据。

关键词:空时格型码;卷积码;多输入多输出系统1 引言卷积码是把信源输出的信息序列,以k0个码元分为一段,通过编码器输出长为n0(≥k0)一段的码段。

该码段的n0﹣k0个校验元不仅与本组的信息元有关,而且也与其前m 段的信息元有关,称m为编码存贮,表示为,码率。

卷积码是一种重要的差错控制编码,由于其性能优且编码运算较简单,因此在mimo系统中获得了广泛的采用。

卷积编码过程的描述方法有很多,为了更容易理解卷积码的编码原理,下面就分别通过状态图方法、树图方法、网格图方法这三种方法来详细说明卷积码的编码过程。

2 状态图表示方法状态图可以清晰的反映卷积编码器的状态转移过程。

例如图1,(2,1,2)卷积码编码器:图1 (2,1,2)卷积编码器由于k0=1且码器由m=2级移位寄存器组成,所以移位寄存器中的存数只有四种可能:00,10,01,11。

相应于编码器有四个状态:。

随着信息序列的不断送入,编码器就不断地从一个状态转移到另一状态,并输出相应的码序列。

由编码器电路图可得到编码器状态图,如图2:图2 (2,1,2)卷积编码器状态图图2中,实线表示0输入,虚线表示1输入时的状态转移。

虽然状态图能表示卷积编码器在不同输入的信息序列下,编码器各状态之间的转移关系,但并不能表示出编码器状态转移随时间的关系。

因此我们可以用码树图和网格图来表示。

3 树图表示方法卷积码的生成矩阵和生成多项式表示方法可以使人深入了解卷积编码原理,而树图表示方法很形象,此外,卷积码的各种距离度量,也往往与树图发生密切关系,因此卷积码的树图表示是一种非常重要的描述卷积码的方法。

对一般的二进制编码器来说,每次输入的是k0个信息元,有个可能的信息组,这相应于从码树每一节点上分出的分支数有条,相应于种不同信息组的输入,并且每条都有n0个码元作为与此相应的输出子码。

卷积码的设计与实现卷积码是一种线性编码技术,广泛应用于通信和数据传输领域。

它通过将输入数据编码为卷积码的形式,提高了数据的纠错能力和传输效率。

本文将介绍卷积码的设计与实现。

一、卷积码的设计1、编码器设计卷积码的编码器由多个移位寄存器和模2加法器组成。

编码器的设计取决于两个参数:约束长度和生成多项式。

约束长度是指编码器中移位寄存器的数量,它决定了卷积码的纠错能力。

生成多项式则决定了编码器的结构。

在设计编码器时,需要选择合适的约束长度和生成多项式,以实现所需的纠错能力和编码效率。

常用的生成多项式有G(D) = (1+D+D^2)和G(D) = (1+D^2),其中D表示延迟。

2、解码器设计卷积码的解码器通常采用最大似然解码算法,如维特比算法或概率解码算法。

这些算法通过搜索所有可能的路径,找到最可能的路径作为解码结果。

在设计解码器时,需要选择合适的算法,并优化算法的复杂度和性能。

常用的优化方法包括剪枝、动态规划、并行计算等。

二、卷积码的实现1、硬件实现卷积码的硬件实现通常采用数字电路和集成电路技术。

通过将编码器和解码器设计成硬件电路,可以实现高速、低功耗的卷积码编码和解码。

在硬件实现中,需要考虑电路的功耗、面积、速度等因素,以优化硬件性能。

常用的硬件实现方法包括ASIC、FPGA和DSP等。

2、软件实现卷积码的软件实现通常采用编程语言和算法库。

通过编写代码实现编码器和解码器的功能,可以实现灵活、可扩展的卷积码编码和解码。

在软件实现中,需要考虑代码的效率、可读性和可维护性等因素,以优化软件性能。

常用的软件实现方法包括C/C++、Python等编程语言和相应的算法库。

三、总结卷积码是一种有效的线性编码技术,具有纠错能力强、传输效率高等优点。

本文介绍了卷积码的设计和实现方法,包括编码器和解码器的设计、硬件和软件实现等方面。

在实际应用中,需要根据具体需求选择合适的卷积码参数和实现方法,以实现高效的通信和数据传输。

摘要在数字通信系统中,通常采用差错控制编码来提高系统的可靠性。

自P.Elias 首次提出卷积码编码以来,这一编码技术至今仍显示出强大的生命力。

目前,卷积码已广泛应用在无线通信标准中,如GSM,CDMA2000和IS-95等无线通信标准中。

针对N-CDMA数据传输过程中的误码问题,本文论述了旨在提高数据传输质量的维特比译码器的设计。

虽然Viterbi译码复杂度较大,实现较为困难,但效率高,速度快。

因此本文着重分析和讨论了1/2速率的(2,1,9)卷积码编码和其Viterbi译码算法。

深入研究卷积码编码原理和Viterbi算法原理后,提出了(2,1,9)卷积码编码以及Viterbi算法的初始化、加—比—选和回溯设计方案,运用查表的方法,避免了大量繁琐计算,使得译码简洁迅速,译码器的实时性能良好。

并充分利用TMS320C54X系列DSP芯片,用汇编语言完成了(2,1,9)卷积码编码和Viterbi 译码的程序。

关键词:差错控制编码、卷积码、Viterbi译码、TMS320C54X、DSPAbstractIn digital communication systems, error control coding is usually used to improve system reliability. Since P.Elias put forward the convolutional coding the first time, the coding is still showing strong vitality.,has become widely used in satellite communications, wireless communications and many other communication systemsas a kind of channel coding method. such as GSM, CDMA2000 and has been a wireless communication standards of IS-95.In view of the error problem in the process of N-CDMA data transmission, this paper discusses the aims to improve the quality of data transmission of victor design than the decoder.Although Viterbi decoding complexity is bigger, more difficult to achieve, but high efficiency and fast speed. So this article emphatically analyzed and discussed the 1/2 rate (2,1,9) convolution code coding and its Viterbi decoding algorithm. In-depth study on principle of convolution code coding and Viterbi algorithm, proposed the convolution code coding and Viterbi algorithm (2,1,9) initialization, add - than - choose and back design, using look-up table method, to avoid a large amount of tedious calculation, the decoding and quick, good real-time performance of the decoder. Make full use of the series of TMS320C54X DSP chip, using assembly language to complete the(2,1,9)convolution code coding and Viterbi decoding process.Keywords: error control coding, convolutional code, Viterbi decoding, TMS320C54X目录摘要 (1)Abstract (2)目录 (3)1.绪论 (1)1.1 移动通信及N-CDMA背景 (1)1.2 数字通信概述 (1)1.3 卷积编码与译码的发展 (3)1.4 主要研究工作 (3)2.DSP与CCS简介 (5)2.1 DSP概述 (5)2.1.1 DSP的主要特点 (5)2.1.2 CSSU单元概述 (7)2.2 CCS概述 (8)2.3 本章小结 (8)3.卷积码的理论基础 (9)3.1 卷积码的概述 (9)3.1.1 卷积码基本原理 (9)3.1.2 卷积码的纠错能力 (9)3.1.3 卷积码的表示方法 (10)3.2 Viterbi译码的概述 (11)3.3 本章小结 (14)4.卷积编码的实现 (15)4.1 (2,1,9)卷积码编码 (15)4.1.1 (2,1,9)卷积码编码设计方案 (15)4.1.2 (2,1,9)卷积码编码流程图 (16)4.1.3 (2,1,9)卷积编码程序实现 (16)4.1.4 (2,1,9)的程序仿真 (17)4.2 (2,1,9)卷积码状态转换表 (17)4.2.1 (2,1,9)卷积码状态转换表的设计算法 (18)4.2.2 (2,1,9)卷积码状态转换表的流程图 (18)4.2.3 (2,1,9)卷积码状态表 (18)4.2.4 (2,1,9)卷积码状态表的蝶形结构 (21)4.3 本章小结 (22)5. Viterbi译码的实现 (23)5.1 Viterbi译码基础 (23)5.2 Viterbi译码算法 (23)5.3 变量定义情况 (25)5.4 初始化 (26)5.4.1 初始化流程图 (27)5.4.2 初始化程序仿真 (27)5.5 加-比-选 (28)5.5.1加-比-选流程图 (29)5.5.2加-比-选程序仿真 (30)5.6 回溯 (31)5.6.1 回溯流程图 (32)5.6.2 回溯仿真图 (33)5.7 Viterbi纠错测试 (34)5.8 本章小结 (34)总结 (36)致谢 ............................................................................ 错误!未定义书签。

前言卷积码是由伊莱亚斯(Elias)于1954 年首先提出来的。

它充分利用了各组之间的相关性,本组的信息元不但决定本组的监督元,而且也参与决定以后若干组的监督元。

同时在译码过程中,不但从该时刻所收到的码组中提取译码信息,而且还利用以后若干时刻内所收到的码组来提取有关信息。

无论从理论上还是实际上均已证明其性能优于线性分组码。

近年来众多有关卷积码研究结果表明,卷积码最有希望实现香农信道编码定理。

但卷积码在译码理论及实际应用较为复杂,这些缺点限制了其进一步发展和应用。

维特比译码算法由维特比(Viterbi)1964年提出,算法实质是最大似然译码,但它利用了编码网格图的特殊结构,在网格图中选择一条路径,使相应的译码序列与接收到的序列之间的汉明距(即量度)最小的一种最大似然译码方法,从而大大降低了计算的复杂性。

目前,第三代移动通信系统(3G) 在我国已经开始紧锣密鼓地实施,它带来的高速度、高品质的无线通信服务,将使我们领略到信息技术的无穷魅力。

信道纠错编码技术作为保证信息可靠传输的技术,在3G各系统中广泛采用,并且我们现在所使用的第二代移动通信系统,如GSM、 CDMA 通信系统,还有卫星与空间通信系统广泛采用了卷积码信道编、译码技术。

本次设计将以(2,1,2)卷积码为例,通过单片机,实现卷积码的译码,借助RS232完成单片机与单片机、单片机与计算机的串口通信,借助7279完成键盘扫描和数码管显示。

第一章系统组成及工作原理本次设计的(2,1,2)卷积码的译码由89C52单片机为工具,接收来自另一单片机或计算机的编码信息,通过7279的键盘扫描和数码管显示功能可以方便地观察到单片机接收的信息和译码结果。

其系统框图如下图1-1所示。

MAX232芯片能实现EIA-RS-232C的正负电压与TTL的高低电平之间的转换,通过它能够方便实现单片机与单片机、单片机与计算机间的串口通信。

HD7279是一片具有串行接口的, 可同时驱动8位共阴极数码管的智能显示驱动芯片, 该芯片同时还可连接多达64键的键盘矩阵, 单片即可独立完成显示、键盘接口的全部功能。

实验名称:___ 卷积编码_______1、使用MATLAB进行卷积编码的代码编写、运行、仿真等操作;2、熟练掌握MATLAB软件语句;3、理解并掌握卷积编码的原理知识。

二、实验原理卷积码是由Elias于1955 年提出的,是一种非分组码,通常它更适用于前向纠错法,因为其性能对于许多实际情况常优于分组码,而且设备较简单。

卷积码的结构与分组码的结构有很大的不同。

具体地说,卷积码并不是将信息序列分成不同的分组后进行编码,而是将连续的信息比特序列映射为连续的编码器输出符号。

卷积码在编码过程中,将一个码组中r 个监督码与信息码元的相关性从本码组扩展到以前若干段时刻的码组,在译码时不仅从此时刻收到的码组中提取译码信息,而且还可从与监督码相关的各码组中提取有用的译码信息。

这种映射是高度结构化的,使得卷积码的译码方法与分组译码所采用的方法完全不同。

可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。

对于某个特定的应用,采用分组码还是卷积码哪一种更好则取决于这一应用的具体情况和进行比较时可用的技术。

(一)卷积编码的图形表示卷积码的编码器是由一个有k 个输人位,n 个输出位,且有m 个移位寄存器构成的有限状态的有记忆系统,其原理如图1所示。

图1 卷积码编码器的原理图描述这类时序网络的方法很多,它大致可分为两大类型:解析表示法与图形表示法。

在解析法中又可分为离散卷积法、生成矩阵法、码多项式法等;在图形表示法中也可分为状态图法、树图法和网络图法等。

图2给出的是一个生成编码速率为1/2 卷积码的移位寄存器电路。

输人比特在时钟触发下从左边移人到电路中,每输入一位,分别去两个模2加法器的输出值并复用就得到编码器的输出。

对这一编码,每输入一比特就产生两个输出符号,故编码效率为1/2。

可以看出,每个特定的输入比特不仅影响本时间间隔内的编码器输出,同时还影响紧接着的下两个输入比特时间间隔的编码器输出。

卷积编码由移位寄存器的阶数、输出的数量(即模2加法器的个数)和移位寄存器与模2 加法器间的连接所决定。

卷积码译码器设计1 完成(2,1,4)卷积码编码器设计2 完成相应的维特比译码器设计卷积码编译码基本原理(n,k,m)卷积码中编码后的n个码元不仅与当前段的k个信息有关,而且也与前面段的信息有关,编码过程中相互关联的码元为n(m+1)个。

因此,这N时间内的码元数目n(m+1)通常被称为这种码的约束长度。

卷积码的纠错能力随着m的增加而增大。

因为任何一个发送序列对应于编码器网格图中的一条路径。

似然函数可以用接收序列与编码器网格图中的路径对应输出序列之间的距离来度量,译码的过程即是在网格图中寻找一条与接收序列距离最小的路径。

2个状态,若输入的信息序列的长度是(L+m)K 一般情况下,(n,k,m)卷积码编码器共有km(后mk个码元全为0),则进入和离开每一状态各有k2条分支在网格图上共有kl2条不同的路径,相应于编码器输出的kl2个码序列。

具体理论见各种书籍介绍。

(2,1,4)卷积器结构及其性质本实验中所涉及的(2,1,4)卷积码编码器结构如图1所示:图1其对应的编码规则为:C[1]=input+D2+D3;C[0]=input+D0+D2+D3;该编码器的viterbi译码的篱笆图如图2所示:0 1 2 3 4 5……图2注:a) 0走实线,1走虚线;b) 在16个状态全部达到之后,状态图中间状态开始循环出现;viterbi卷积器的verilog实现一.设计和测试的总结构设计如图3所示:…图3Test_decode //to test the basic function of this project…….encode //to encode the original 01 code, and output the convoluted codes …….decode //input the codes which are generated by encoder and interfered by //random noise//to compute the length of the two paths linked to node x andx)//generated when a new code comes in (}15'1,0{,...,……..acs0……..acs1……..acs23……..acs_4_7……..acs_8_15……..mod2 //to computer the distance between this inputted code and 00//01 10 or 11, and the result is inputted into acs0,acs1 and//the like.//get the result of acs0, acs1 and the like, compare the//distance of the two paths linked to a single nod and choose//the shorter paths as the path value as the basic value of//the nod when a new code comes in……..path01……..path23……..path_4_7……..path_8_15Notation:1. 因为初始截断树的存在,各结点有着不同的特点,故分成acs0,acs1,acs23,acs_4_7,acs_8_15 5个不同的模块,其实他们功用相同;同样,path01,path23,path_4_7,path_8_15也由此原因得出;二.编码器设计利用上述(2,1,4)卷积编码器的结构生成相应的编码,见encode.v文件用R[3:0]寄存器寄存已输入的码,最多寄存之前输入的4位,所以为4位。

卷积码编码维特比译码实验设计报告SUN一、实验目的掌握卷积码编码和维特比译码的基本原理,利用了卷积码的特性, 运用网格图和回溯以得到译码输出。

二、实验原理1.卷积码是由连续输入的信息序列得到连续输出的已编码序列。

其编码器将k个信息码元编为n个码元时,这n个码元不仅与当前段的k个信息有关,而且与前面的(m-1)段信息有关(m为编码的约束长度)。

2.一般地,最小距离d表明了卷积码在连续m段以内的距离特性,该码可以在m个连续码流内纠正(d-1)/2个错误。

卷积码的纠错能力不仅与约束长度有关,还与采用的译码方式有关。

3. 维特比译码算法基本原理是将接收到的信号序列和所有可能的发送信号序列比较,选择其中汉明距离最小的序列认为是当前发送序列。

卷积码的Viterbi 译码是根据接收码字序列寻找编码时通过网格图最佳路径的过程,找到最佳路径即完成了译码过程,并可以纠正接收码字中的错误比特。

4.所谓“最佳”, 是指最大后验条件概率:P( C/ R) = max [ P ( Cj/ R) ] , 一般来说, 信道模型并不使用后验条件概率,因此利用Beyes 公式、根据信道特性出结论:max[ P ( Cj/ R) ]与max[ P ( R/ Cj) ]等价。

考虑到在系统实现中往往采用对数形式的运算,以求降低运算量,并且为求运算值为整数加入了修正因子a1 、a2 。

令M ( R/ Cj) = log[ P ( R/ Cj) ] =Σa1 (log[ P( Rm/ Cmj ) ] + a2) 。

其中, M 是组成序列的码字的个数。

因此寻找最佳路径, 就变成寻找最大M( R/ Cj) , M( R/ Cj) 称为Cj 的分支路径量度,含义为发送Cj 而接收码元为R的似然度。

5.卷积码的viterbi译码是根据接收码字序列寻找编码时通过网格图最佳路径的过程,找到最佳路径即完成了译码过程并可以纠正接收码字中的错误比特。

三、实验代码#include<stdio.h>#include "Conio.h"#define N 7#include "math.h"#include <stdlib.h>#include<time.h>#define randomize() srand((unsigned)time(NULL))encode(unsigned int *symbols, /*编码输出*/unsigned int *data, /*编码输入*/unsigned int nbytes, /*nbytes=n/16,n为实际输入码字的数目*/unsigned int startstate /*定义初始化状态*/)////////////////////////////////////////////////////////////////////////////卷积码编码///////////////////////////////////////////////////////////////////////////////{unsigned int j;unsigned int input,a1=0,a2=0,a3=0,a4=0,a5=0,a6=0;for(j=0;j<nbytes;j++){input=*data;data++;*symbols = input^a1^a2^a3^a6; //c1(171)symbols++;*symbols = input^a2^a3^a5^a6; //c2(133)symbols++;a2=a1;a1=input;}return 0;}int trandistance(int m, int state1, int state2)/*符号m与从state1到state2时输出符号的汉明距离,如果state1无法到state2则输出度量值为100*/{int c;int sym,sym1,sym2;sym1=((state2>>1)&1)^(state2&1)^(state1&1);sym2=((state2>>1)&1)^(state1&1);sym=(sym1<<1) | sym2;if ( ((state1&2)>>1)==(state2&1))c=((m&1)^(sym&1))+(((m>> 1)&1)^((sym >> 1)&1));elsec=10000;return(c);}int traninput(int a,int b) /*状态从a到b时输入卷积码的符号*/{int c;c=((b&2)>>1);return(c);}int tranoutput(int a,int b) /*状态从a到b时卷积码输出的符号*/{int c,s1,s2;s1=(a&1)^((a&2)>>1)^((b&2)>>1);s2=(a&1)^((b&2)>>1);c=(s1<<1)|s2;return(c);}////////////////////////////////////////////////////////////////////////////维特比译码///////////////////////////////////////////////////////////////////////////////void viterbi(int initialstate, /*定义解码器初始状态*/int *viterbiinput, /*解码器输入码字序列*/int *viterbioutput /*解码器输出码字序列*/){struct sta /*定义网格图中每一点为一个结构体,其元素包括*/ {int met; /*转移到此状态累计的度量值*/int value; /*输入符号*/struct sta *last; /*及指向前一个状态的指针*/};struct sta state[4][N];struct sta *g,*head;int i,j,p,q,t,r,u,l;for(i=0;i<4;i++) /* 初始化每个状态的度量值*/for(j=0;j<N;j++)state[i][j].met=0;for(l=0;l<4;l++){state[l][0].met=trandistance(*viterbiinput,initialstate,l);state[l][0].value=traninput(initialstate,l);state[l][0].last=NULL;}viterbiinput++; /*扩展第一步幸存路径*/for(t=1;t<N;t++){for(p=0;p<4;p++){state[p][t].met=state[0][t-1].met+trandistance(*viterbiinput,0,p);state[p][t].value=traninput(0,p);state[p][t].last=&state[0][t-1];for(q=0;q<4;q++){if(state[q][t-1].met+trandistance(*viterbiinput,q,p)<state[p][t].met){state[p][t].met=state[q][t-1].met+trandistance(*viterbiinput,q,p);state[p][t].value=traninput(q,p);state[p][t].last=&state[q][t-1];}}}viterbiinput++;} /*计算出剩余的幸存路径*/r=state[0][N-1].met; /*找出n步后度量值最小的状态准备回溯路由*/g=&state[0][N-1];for(u=N;u>0;u--) /*向前递归的找出最大似然路径*/{*(viterbioutput+(u-1))=g->value;g=g->last;}/* for(u=0;u<8;u++)*(viterbioutput+u)=state[u][2].met; */ /*此行程序可用于检测第n列的度量值*/}void decode(unsigned int *input, int *output,int n){int viterbiinput[100];int j;for(j=0;j<n+2;j++){viterbiinput[j]=(input[j*2]<<1)|input[j*2+1];}viterbi(0,viterbiinput,output);}void main(){unsigned intencodeinput[100],wrong[10]={0,0,0,0,0,0,0,0,0,0},encodeoutput[100];int n=5,i,m,j=0,decodeinput[100],decodeoutput[100];randomize();for(i=0; i<n; i++)encodeinput[i]=rand()%2;encodeinput[n]= encodeinput[n+1]=0;encode(encodeoutput,encodeinput,n+2,0);printf("the input of encoder is :\n"); //信息源输入的信息码(随机产生)for(i=0;i<n; i++)printf("%2d",encodeinput[i]);printf("\n");printf("the output of encoder is :\n"); //编码之后产生的卷积码for(i=0;i<(n+2)*2;i++){printf("%2d",encodeoutput[i]);if(i%20==19)printf("\n");}printf("\n");printf("please input the number of the wrong bit\n"); //信道传输收到干扰而产生的错误码scanf("%d",&m);printf("please input the positions of the wrong bit(0-9)\n");for(i=0;i<m;i++){scanf("%d",&wrong[m]);if(encodeoutput[wrong[m]]==0)encodeoutput[wrong[m]]=1;elseencodeoutput[wrong[m]]=0;}printf("the input of decoder is :\n");for(i=0;i<(n+2)*2;i++){printf("%2d",encodeoutput[i]);if(i%20==19)printf("\n");}printf("\n");decode(encodeoutput,decodeoutput,n+2);printf("the output of decoder is :\n");for(i=0;i<n;i++)printf("%2d",decodeoutput[i]);printf("\n");for(i=0;i<n;i++){if(encodeinput[i]!=decodeoutput[i])j++;}printf("the number of incorrect bit is:%d\n",j);}四、实验总结(1)了解实验原理,分析实验所占数组变量很重要,也是相对考虑较多的;(2)对于读写文件,通过本实验更加熟悉;(3)记录实验程序最佳路径是本实验的难点;。

3/4 卷积码编码原理解析与建模拟真一、大纲卷积码是一种性能优越的信道编码。

它的编码器和译码器都比较简单实现,同时它拥有较强的纠错能力。

随着纠错编码理论研究的不断深入,卷积码的实质应用越来越广泛。

本文简短地介绍了卷积码的编码原理和 Viterbi 译码原理。

并在 SIMULINK模块设计中,达成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。

最后,经过在仿真过程中解析了卷积码误比特率与信噪比之间的关系,及卷积码与非卷积码的对照。

经过仿真和实测,并对测试结果作了解析。

要点词:卷积码编码建模SIMULINK 仿真目录一、大纲 .................................................................................................................................................................- 1 -二、设计目的和意义 .............................................................................................................................................- 2 -三、设计原理 .........................................................................................................................................................- 3 -卷积码根本看法 ......................................................................................................................................- 3 -卷积码的结构 ..........................................................................................................................................- 3 -卷积码的解析表示 ..................................................................................................................................- 4 -卷积码的译码 ..........................................................................................................................................- 4 -卷积码译码的方式 ........................................................................................................................- 4 -卷积码的 Viterbi 译码 ..................................................................................................................- 5 -四、详细设计步骤 .................................................................................................................................................- 6 -卷积码的仿真 ..........................................................................................................................................- 6 -SIMULINK 仿真模块的参数设置及意义.................................................................................- 6 -五、设计结果及解析 . (11)不相同信噪比对卷积码的影响 (11)卷积码的对照 (12)六、总结 (14)七、领悟 (14)八、参照文件 (14)二、设计目的和意义由于信道中信号不可以防范会碰到搅乱而出错。

《数字集成电路设计》课程设计题目:交织器解交织器学院:电子与信息学院专业:学号:姓名:一、设计要求1. 请设计一个交织器和解交织器,完成二进制比特流的交织/ 解交织功能。

2. 设计测试文件,验证设计的功能是否正确。

二、设计卷积交织器目的在数字传输系统中,因为存在噪声,信道衰落等干扰因素,会使传输的信号发生错误,产生误码。

虽然数字信号的传输为了防止误码而会进行信道编码,增加传输码的冗余,例如增加监督位等来克服信号在信道传输过程中的错误,但这种检错纠错能力是有限的。

例如当出现突发错误,出现大片误码时,这时信道的纠错是无能为力的。

而卷积交织器可以将原来的信息码打乱,这时尽管出现大面积突发性错误,这些可以通过解交织器来进行分散,从而将大面积的错误较为平均地分散到不同的码段,利于信道纠错的实现。

三、卷积码编码器原理卷积码拥有良好的纠错性能,是一种被广泛应用于移动通信的信道编码系统。

一个(n,k,m)卷积码编码器由k个输入,具有m阶存储的n个输出的线形时序电路实现。

通常,n和k是较小的整数,且k<n,但m比较大。

当k=1时,信息序列不再分成小块,以便可以连续处理。

卷积码(n,k,m)表示码率R=k/n,编码器级数m=s-1,其中s是码约束长度。

反向CDMA信道使用(3,1,8)卷积码,码率R=1/3,约束长度为9,由于k=1,n=3,m=8,则该卷积编码器包含单个输入端,一个8级移位寄存器,三个模2加法器和一个3向编码器输出的连续转向器。

编码器每输入一位信息比特将产生三位编码输出。

这些编码符号中,第一个输出符号G0是生成序列g1⑴编码产生的符号,第二个输出符号G1是由生成序列g1⑵编码产生的符号,最后一个输出符号G2是由生成序列g1⑶编码产生的符号,如下图所示。

该电路由一个八位寄存器、三个码生成逻辑、一个时隙发生器和一个四选一复用器构成。

mux的输入为G0、G1和G2,码选择信号C[1:0]和clk1由时隙发生器产生,输出信号即为整个电路的输出Yout。

图11-8 卷积码编码器一般原理方框图例: (n, k, N) = (3, 1, 3)卷积码编码器每当输入1比特时,此编码器输出3比特c 1c 2 c 31. 卷积码的代数表述 (1) 监督矩阵H一般说来,卷积码的截短监督矩阵具有如下形式:I n-k — (n – k)阶单位方阵; P i — k ⨯ (n – k)阶矩阵; O n-k — (n – k)阶全零方阵k1……Nk k 2k 3k ……………Nk n 级移存器个模2加法器M 输入b iM 2`12i ii i i i i i i c b d b b e b b b ---==⊕=⊕⊕1211321121n k n k n k n k n k n kNn k N n k N n kn k P I P O P I H P O P O P I P O P O P O P I ------------⎡⎤⎢⎥⎢⎥⎢⎥=⎢⎥⎢⎥⎢⎥⎣⎦有时还将H 1的末行称为基本监督矩阵hh = [P N O n-k P N-1 O n-k P N-2 O n-k ⋅ ⋅ ⋅ P 1 I n-k ]从给定的h 不难构造出H 1 (2) 生成矩阵G一般说来,截短生成矩阵具有如下形式:I k - k 阶单位方阵; Q i - (n – k)⨯k 阶矩阵;O k - k 阶全零方阵。

并将上式中矩阵第一行称为基本生成矩阵g = [I k Q 1 O k Q 2 O k Q 3⋯O k Q N ]如果基本生成矩阵g 已经给定,则可以从已知的信息位得到整个编码序列 2. 卷积码的解码(1) 代数解码:利用编码本身的代数结构进行解码,不考虑信道的统计特性。

大数逻辑解码,又称门限解码,是卷积码代数解码的最主要一种方法,它也可以应用于循环码的解码。

大数逻辑解码对于约束长度较短的卷积码最为有效,而且设备较简单。

(2) 概率解码:又称最大似然解码。

它基于信道的统计特性和卷积码的特点进行计算。

题目:信道编码中卷积编码器的设计第1章卷积编码器的原理与设计1.1 引言卷积码是1955年由Elias等人提出的,是一种非常有前途的编码方法。

我们在一些资料上可以找到关于分组码的一些介绍,分组码的实现是将编码信息分组单独进行编码,因此无论是在编码还是译码的过程中不同码组之间的码元无关。

卷积码和分组码的根本区别在于,它不是把信息序列分组后再进行单独编码,而是由连续输入的信息序列得到连续输出的已编码序列。

即进行分组编码时,其本组中的n-k个校验元仅与本组的k 个信息元有关,而与其它各组信息无关;但在卷积码中,其编码器将k个信息码元编为n个码元时,这n个码元不仅与当前段的k个信息有关,而且与前面的段信息有关。

同样,在卷积码译码过程中,不仅从此时刻收到的码组中提取译码信息,而且还要利用以前或以后各时刻收到的码组中提取有关信息。

而且卷积码的纠错能力随约束长度的增加而增强,差错率则随着约束长度增加而呈指数下降。

卷积码(n,k,m)主要用来纠随机错误,它的码元与前后码元有一定的约束关系,编码复杂度可用编码约束长度mn来表示。

一般地,最小距离d表明了卷积码在连续m段以内的距离特性,该码可以在m个连续码流内纠正(d-1)/2个错误。

卷积码的纠错能力不仅与约束长度有关,还与采用的译码方式有关。

总之,由于n,k较小,且利用了各组之间的相关性,在同样的码率和设备的复杂性条件下,无论理论上还是实践上都证实:卷积码的性能至少不比分组码差。

1.2 卷积编码原理卷积码在一个二进制分组码(n,k)当中,包含k个信息位,码组长度为n,每个码组的(n-k)个校验位仅与本码组的k个信息位有关,而与其它码组无关。

为了达到一定的纠错能力和编码效率(=k/n),分组码的码组长度n通常都比较大。

编译码时必须把整个信息码组存储起来,由此产生的延时随着n的增加而线性增加。

为了减少这个延迟,人们提出了各种解决方案,其中卷积码就是一种较好的信道编码方式。

湖南文理学院课程设计报告课程名称:通信系统课程设计专业班级:通信工程11102班09 学生姓名:朱涛指导教师:侯清莲完成时间:2014-11-18报告成绩:目录一、设计要求 (1)二、设计作用与目的 (1)三、所用设备及软件 (1)四、卷积码编码的概念 (1)4.1卷积码的编码描述方法 (1)4.2 卷积编码 (2)4.3 卷积码的树状图 (3)4.4 卷积码的网格图 (3)五、 EDA设计方法及工具软件QUARTUSⅡ (4)六、改变卷积编码器的参数仿真以及结论 (4)6.1 不同回溯长度对卷积编码器性能的影响 (4)6.2 不同码率对卷积编码器误码性能的影响 (5)6.3 不同约束长度对卷积编码器的误码性能影响 (6)七、卷积码编码器的VHDL设计与仿真 (8)7.1 VHDL设计的优点与设计方法 (8)7.2 卷积码编码器的VHDL实现 (10)八、心得体会 (10)九、参考文献 (11)卷积编码器的设计一、设计要求(1)画出卷积码的原理框图,说明系统中各主要组成部分的功能。

(2)使用EDA技术及VHDL语言对卷积编码器进行设计与仿真并对结果分析。

二、设计作用与目的(1)巩固加深对通信基本知识分析以及卷积码的掌握,提高综合运用通信知识的能力。

(2)掌握采用仿真软件对系统进行仿真分析。

(3)培养学生查阅参考文献,独立思考,设计,钻研电子技术相关问题的能力。

(4)掌握相关电子线路工程技术规范以及常规电子元器件的性能技术指标。

(5)培养严肃认真的工作作风与科学态度,建立严谨的工程技术观念。

(6)了解电气图国家标准,并利用电子CAD等正确绘制电路图。

(7)培养工程实践能力,创新能力与综合设计能力。

三、所用设备及软件(1)QUARTUSⅡ(2)PC机四、卷积码编码的概念4.1卷积码的编码描述方法编码描述方法有5种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述法和网格图描述法。

卷积码的纠错能力随着N的增加而增大,而差错率随着N的增加而指数下降。

在编码器复杂性相同的情况下,卷积码的性能优于分组码。

分组码有严格的代数结构,但卷积码至今尚未找到如此严密的数学手段。

分组码的译码算法可以由其代数特性得到。

卷积码虽然可以采用适用于分组码的门限译码(即大数逻辑译码),但性能不如维特比译码和序列译码[2]。

以二元码为例,输入信息序列为u=(u0,u1,…),其多项式表示为u(x)=u0+u1x+…+…。

编码器的连接可用多项式表示为g(1,1)(x)=1+x+x2和g(1,2)(x)=1+x2,称为码的子生成多项式。

它们的系数矢量g(1,1)=(111)和g(1,2)=(101)称作码的子生成元。

以子生成多项式为阵元构成的多项式矩阵G(x)=[g(1,1)(x),g(1,2)(x)],称为码的生成多项式矩阵。

由生成元构成的半无限矩阵。

4.2 卷积编码卷积码的编码器一般都比较简单。

图4.1 卷积码编码器图4.1是一般情况下的卷积码编码器框图。

它包括NK级的输入移位器,一组n个模2和加法器和n级的输出移位寄存器。

对应于每段k比特的输入序列,输出n个比特。

由图可知,n个输出比特不但与当前的k个输入比特有关,而且与以前的(N-1)k个输入信息比特有关。

整个编码过程可以看成是输入信息序列与由移位寄存器和模2加法器的连接方式所决定的另一个序列的卷积,卷积码由此得名。

本文采用的是冲击响应描述法编码思想。

图4.2(2,1,3)卷积编码器如图4.2是卷积码(2,1,3)卷积编码器的一个框图。

左边是信息的输入。

下面分别是系统位输出和校验位输出。

其中间是3个移位寄存器和一个模2加法器。

简单的说就是信息位经过移位寄存器和一个模2加法器产生一个系统位和校验位加在一起输出。

可以看出:每输入一个比特,移位寄存器中就向右移动一个位子。

原来的第三个寄存器就被移出。

可见卷积编码不只与现在的输入比特有关还与前面的3-1个比特有关。

所以约束长度是3。

在这里,其中K=1,n=2所以码率R=K/n=1/2[3]。

4.3 卷积码的树状图对于图4.2所示的(2,1,3)卷积码编码电路,其树状图如下图4.3所示,这里,分别用a ,b ,c 和d 表示寄存器的4种状态:00,01,10和11,作为树状图中每条支路的节点。

以全零状态a 为起点,当输入位信息位为0时,输出码元c1c2=00,寄存器保持状态a 不变,对应图中从起点出发的上支路;当输入位为1时,输出码元c1c2=11,寄存器则转移到状态b ,对应图中的下支路;然后再分别以这两条支路的终结点a 和b 作为处理下一位输入信息的起点,从而得到4条支路,以此类推,可以得到整个树状图。

如下图4.3图4.3(2,1,3)树状图4.4 卷积码的网格图状态图可以完整的描述编码器的工作过程,但是其只能显示状态转移的过程而不能显示状态转移发生的时刻,由此引出用来表示卷积码的另一种常用方法——网格图。

网格图就是时 间与对应状态的转移图,在网格图中每一个点表示该时刻的状态,状态之间的连线表示状态转移。

通过观察网格图可以发现在网格图中输入信息x (n )并没有标出,但如观察到转移后的状态表示(x (n ),x (n -1))就可以发现输入信息已经隐含在转移后的状态中[4]。

如下图4.4是(2,1,3)卷积编码的网格图。

0000 状态 A 00 B 01 C 10 D 11 A 00 B 01 C 10D 11a ab11 110110a bc da b c d图4.4(2,1,3)卷积编码的网格图五、 EDA 设计方法及工具软件QUARTUS Ⅱ(1) 前端设计(系统建模RTL 级描述)后端设计(FPGAASIC )系统建模。

(2) IP 复用。

(3) 前端设计。

(4) 系统描述:建立系统的数学模型。

(5) 功能描述:描述系统的行为或各子模块之间的数据流图。

(6) 逻辑设计:将系统功能结构化,通常以文本、原理图、逻辑图、布尔表达式来表示设计结果。

(7) 仿真:包括功能仿真和时序仿真,主要验证系统功能的正确性及时序特性。

六、 改变卷积编码器的参数仿真以及结论6.1 不同回溯长度对卷积编码器性能的影响下面将以(2,1,3)卷积码来建立模块仿真。

将编码模块中的Traceback depth 分别设置为20,35,45并在一个图中画出这三种方式下的误码性能曲线得到下图。

从上到下的三条曲线分别是Traceback depth 为20,35,45。

可以看出:回溯长度是在Viterbi 译码过程中一个很重要的参数,他决定了译码延迟,随着他的不断变化,误码性能也随误比特率曲线可以清楚地看到,当回溯长度一定时,随着信道噪声的逐渐减小,系统的误比特率逐渐降低;当回溯长度逐渐增加,系统的误比特率随之逐渐降低,但是当回溯程度a 增加到a ≥5N 时(N 为编码的约束长度),误比特率数值趋于稳定,因此,在确定回溯长度时既要考虑到随着a 的增加误比特率随之降低的趋势,也要考虑到译码延迟会变大,在选取回溯长度时,通常取a =5N 。

状态 a =00 b =01 c =10 d =11图 6.1不同回溯长度对误码性能的影响分析不同回溯长度对卷积码无码性能的影响时用到的程序如下:x=-10:5;y=x;for i=1:length(x)SNR=x(i);sim(‘yima’);y(i)=mean(BitErrorRate);Endsemilogy(x,y);Hold on;for i=1:length(x)SNR=x(i);sim(‘yima2’);y(i)=mean(BitErrorRate);Endsemilogy(x,y);6.2 不同码率对卷积编码器误码性能的影响下面图是通过改变卷积码的码率为1/2和1/3而得到的二条对比曲线。

上面的一条曲线是码率为1/2,下面的是码率为1/3。

卷积码的码率R=k/n,他是卷积码的一个重要参数,当改变卷积码的码率时,系统的误码性能也将随之发生变化。

从图中的误比特率曲线可以看出,当码率一定时,随着信道噪声的逐渐减小,系统的误比特率也呈现出增大的趋势,也就是说码率越低,系统的误比特率就越小,误码性能就越好。

图6.2卷积码不同码率对误码性能的影响分析不同码率对卷积码误码性能的影响时用到的程序如下:X=0:5;y=x;for i=1:length(x)SNR=x(i);sim(‘yimal’);y(i)=mean(BitErrorRate);endsemilogy(x,y);hold on;for i=1;length(x)SNR=x(i);Sim(‘yima2’);y(i)=mean(BitErrorRate);endsemilogy(x,y);6.3 不同约束长度对卷积编码器的误码性能影响如下图,对于码率一定的卷积码,当约束长度N发生变化时,系统的误码性能也会随之发生变化,我们以码率R=1/2的(2,1,3)和(2,1,7)卷积码为例展开分析。

上面的曲线是(2,1,3)卷积码的误码性能曲线。

下面的曲线是(2,1,7)卷积码的误码性能曲线。

从图中的误比特率曲线可以清楚的看到,随着约束长度可以降低系统的误比特率,但是随着约束长度的增加,译码设备的复杂性也会随之增加,所以对于码率为1/2的卷积码,我们在选取约束长度时一般为3-9。

图6.3不同约束长度对卷积码误码性能的影响分析不同约束长度对卷积码误码性能影响用到的程序如下:x=0:5;y=x;for i=1:length(x)SNR=x(i);Sim(‘yima’);y(i)=mean(BitErrorRate);endsemilogy(x,y);hold on;for i=1:length(x)SNR=x(i);sim(‘yima1’);y(i)=mean(BitErrorRate);endsemilogy(x,y);通过上面从(1)回溯长度;(2)码率;(3)约束长度这三个卷积码编码器的重要参数的变化后对译码性能的分析,我们得到在卷积码的编码,译码过程中很多条件是不可能同时满足的。

所以我们要根据具体情况来选择合适的参数。

七、卷积码编码器的VHDL设计与仿真7.1VHDL设计的优点与设计方法VHDL语言采用自上至下和基于库的设计方法,其突出的优点是具有多层次描述系统硬件功能的能力,可以从系统的数学模型直到门级电路。

本设计所用VHDL设计平台是Altera的QuartusⅡEDA软件。

QuartusⅡ界面友好,使用便捷;它支持VHDL语言文本文件,原理图,以及波形与EDIF等格式的文件作为设计输入,并支持这些文件的任意混合设计:具有门级仿真器,可以进行功能仿真和时序仿真,能够产生精确的仿真结果。

7.2卷积码编码器的VHDL实现7.2.1卷积编码器顶层建模的VHDL描述library ieee;use ieee.std_logic_1164.all;entity encoder isport (clk:in std_logic;clr:in std_logic;data_in:in std_logic;c0,c1,c2:out std_logic);end;architecture behave of encoder iscomponent dff2port(d,clk,clr:in std_logic;q:out std_logic);end component;component xor2port (a,b:in std_logic;y:out std_logic);end component;component xor3port (a,b,c:in std_logic;y:out std_logic);end component;signal din,r1,r2,y1,y2: std_logic;begindin<=data_in;u0:dff2port map (din, clk, clr,r1);u1:dff2port map (r1, clk, clr,r2);u2:xor2port map (din,r1,y1);u3:xor3port map (din,r1,r2,y2);c0<=din;c1<=y1;c2<=y2;end;用QuartusⅡ编译后生成的编码器图形符号如图所示。