基于Quartus_II的流水灯设计仿真

- 格式:ppt

- 大小:1.65 MB

- 文档页数:34

图2.1 LED灯电路3.点击图2.1.2中的【N e xt】进入工作目录,工程名的设定对话框如图2.1.3所示。

第一个输入框为工程目录输入框,用户可以输入如:FPGA等工作路径来设定工程的目录,设定好后,所有的生成文件将放入这个工作目录。

的哥输入框为工程名称输入框,第三个输入框位顶层实体名称输入框。

用户可以设定E X P1,一般情况下工程名称与实体名称相同。

使用者也可以根据自己的实际情况来设定。

4.点击【Next】,进入下一个设定对话框,按默认选项直接点击【Next】进行器件选择对话框,如图2.1.4-A和图2.1.4-B所示。

这里我们选择Cyclone II系列芯片EP2C5T144C8。

首先在对话框的左上方的Family下拉菜单中选取Cyclone II,在中间右边的Speed grade下拉菜单中选取8,在左下方的Availa ble devices中选取EP2C5T144C8,点击【Next】完成器件的选取,进入EDA TOOL设定界面如图2.1.5所示。

5.按默认选项,点击【Next】出现新建工程以前所有的设定信息,如图2.1.6所示,点击Finish完成新建工程的建立,如图2.1.7所示。

6.点击File>New,新建一个VHDL文件。

如图2.1.8所示。

7.点击OK,将VHDL程序写入后,如图2.1.9所示,并点击File>Save,无需做任何更改,点击OK即可。

如图2.1.10所示。

8.按照自己的想法,在新建的VHDL文件中编写VHDL程序。

9.代码书写结束后,选择Processing>Start Compilation对编写的代码进行编译,直到编译通过。

10.编译通过后,对试验中用到的LED进行管脚绑定。

选择Assign ments> Pins,会出现管脚分配对话框,如图2.1.11所示。

11.首先选择对应的引脚,然后在l o c a t i o n中按表2.1-1中端口引脚对应关系输入V H D L设计中对应的端口名称引脚号,如图2.1.12所示。

第1章SOPC流水灯实验实验步骤如下:1.1 实验目的熟悉使用QuartusII软件;熟悉使用SOPC Builder建立自己的Nios2系统;熟悉使用Nios II IDE软件进行编程、调试和下载程序。

1.2 实验设备硬件:PC机一台MagicSOPC教学实验开发平台一套软件:Quartus II7.0、Nios II IDE 7.01.3 实验内容本实验的内容是使用QuartusII中的SOPC Builder建立一个NiosII系统,并使用NiosII IDE编写C程序,在NiosII IDE中下载程序、调试程序。

1.4 实验预习要求预习《SOPC嵌入式系统实验教程二》第3章3.3节,熟悉建立带DDR SDRAM的NiosII 系统;熟悉PIO外设的使用。

1.5 实验步骤1.5.1使用Quartus II建立工程仿照Quartus II7.0软件使用的实验,建立一个Nios2_system的工程,并使工程名与实体名相同。

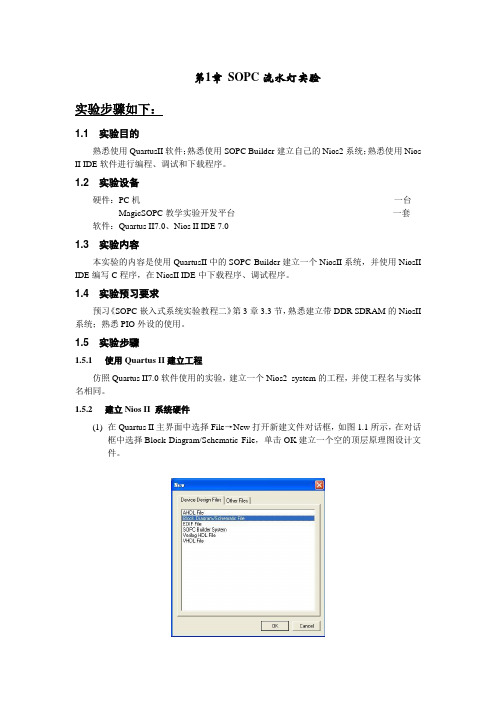

1.5.2建立Nios II 系统硬件(1)在Quartus II主界面中选择File→New打开新建文件对话框,如图1.1所示,在对话框中选择Block Diagram/Schematic File,单击OK建立一个空的顶层原理图设计文件。

图1.1 新建文件对话框(2)在Quartus II主界面中选择Tools→SOPC Builder打开如图1.2所示的对话框,在System Name一栏中填入Nios II 系统的名称nios2_ep2c35,然后单击OK进入到如图1.3所示的SOPC Builder的主界面。

图1.2 Create New System对话框图1.3 SOPC Builder的主界面(3)双击SOPC Builder主界面左侧中的“Nios II Processor-Altera Corporation”,出现Nios II CPU的配置向导对话框,如图1.4所示,在这果可以有三种Nios II CPU选择,我们选择快速型的Nios II/f,然后单击Next进入下一步配置。

EDA大作业流水灯设计基于Quartus II的花样流水灯的设计流水灯是一串按一定的规律像流水一样连续闪亮,流水灯控制是可编程控制器的一个应用,其控制思想在工业控制技术领域也同样适用。

流水灯控制可用多种方法实现,但对现代可编程控制器而言,基于EDA技术的流水灯设计也是很普遍的。

1.设计目的a.学习使用EDA集成设计软件Quartus II,电路描述,综合,模拟过程b.了解基于EDA应用系统的设计方法c. 掌握使用EDA工具设计流水灯的设计思路和设计方法d.熟练使用Quartus II对实验程序进行改错,调试以及演示现象2. 设计说明流水灯设计是由八只LED显示灯来实现的,通过程序代码来控制这八只灯的亮灭,从而实现花型的变化(快慢,顺序)。

3.程序设计3.1library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY first ISPORT (clk : IN std_logic;rst : IN std_logic;c : OUT std_logic_vector(7 DOWNTO 0));END first;ARCHITECTURE arch OF first ISCONSTANT state0 : std_logic_vector(2 DOWNTO 0) := "000";CONSTANT state1 : std_logic_vector(2 DOWNTO 0) := "001";CONSTANT state2 : std_logic_vector(2 DOWNTO 0) := "010";CONSTANT state3 : std_logic_vector(2 DOWNTO 0) := "011";CONSTANT state4 : std_logic_vector(2 DOWNTO 0) := "100";CONSTANT state5 : std_logic_vector(2 DOWNTO 0) := "101"; CONSTANT state6 : std_logic_vector(2 DOWNTO 0) := "110"; CONSTANT state7 : std_logic_vector(2 DOWNTO 0) := "111"; SIGNAL state : std_logic_vector(2 DOWNTO 0);SIGNAL cnt : std_logic_vector(2 DOWNTO 0);BEGINPROCESS(clk,rst)BEGINIF (NOT rst = '1') THENstate <= state0;cnt <= "000";ELSIF(clk'EVENT AND clk='1')THENcnt <= cnt + "001";IF (cnt = "111") THENCASE state ISWHEN state0 =>state <= state1;WHEN state1 =>state <= state2;WHEN state2 =>state <= state3;WHEN state3 =>state <= state4;WHEN state4 =>state <= state5;WHEN state5 =>state <= state6;WHEN state6 =>state <= state7;WHEN state7 =>state <= state0; WHEN OTHERS =>NULL;END CASE;END IF;END IF;END PROCESS;PROCESS(state)BEGINCASE state ISWHEN state0 =>c <= "";WHEN state1 =>c <= "";WHEN state2 =>c <= "";WHEN state3 =>c <= "";WHEN state4 =>c <= "";WHEN state5 =>c <= "";WHEN state6 =>c <= "";WHEN state7 =>c <= "";WHEN OTHERS =>NULL;END CASE;END PROCESS;END arch;3.2library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY second ISPORT (clk : IN std_logic;rst : IN std_logic;c : OUT std_logic_vector(7 DOWNTO 0));END second;ARCHITECTURE arch OF second ISCONSTANT state0 : std_logic_vector(2 DOWNTO 0) := "000"; CONSTANT state1 : std_logic_vector(2 DOWNTO 0) := "001"; CONSTANT state2 : std_logic_vector(2 DOWNTO 0) := "010"; CONSTANT state3 : std_logic_vector(2 DOWNTO 0) := "011"; CONSTANT state4 : std_logic_vector(2 DOWNTO 0) := "100"; CONSTANT state5 : std_logic_vector(2 DOWNTO 0) := "101"; CONSTANT state6 : std_logic_vector(2 DOWNTO 0) := "110"; CONSTANT state7 : std_logic_vector(2 DOWNTO 0) := "111"; SIGNAL state : std_logic_vector(2 DOWNTO 0);SIGNAL cnt : std_logic_vector(2 DOWNTO 0);BEGINPROCESS(clk,rst)BEGINIF (NOT rst = '1') THENstate <= state0;cnt <= "000";ELSIF(clk'EVENT AND clk='1')THENcnt <= cnt + "001";IF (cnt = "111") THENCASE state ISWHEN state0 =>state <= state1; WHEN state1 =>state <= state2; WHEN state2 =>state <= state3; WHEN state3 =>state <= state4; WHEN state4 =>state <= state5; WHEN state5 =>state <= state6; WHEN state6 =>state <= state7; WHEN state7 =>state <= state0; WHEN OTHERS =>NULL;END CASE;END IF;END IF;END PROCESS;PROCESS(state)BEGINCASE state ISWHEN state0 =>c <= "";WHEN state1 =>c <= "";WHEN state2 =>c <= "";WHEN state3 =>c <= "";WHEN state4 =>c <= "";WHEN state5 =>c <= "";WHEN state6 =>c <= "";WHEN state7 =>c <= "";WHEN OTHERS =>NULL;END CASE;END PROCESS;END arch;3.3library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY third ISPORT (clk : IN std_logic;rst : IN std_logic;c : OUT std_logic_vector(7 DOWNTO 0));END third;ARCHITECTURE arch OF third ISCONSTANT state0 : std_logic_vector(2 DOWNTO 0) := "000"; CONSTANT state1 : std_logic_vector(2 DOWNTO 0) := "001"; CONSTANT state2 : std_logic_vector(2 DOWNTO 0) := "010"; CONSTANT state3 : std_logic_vector(2 DOWNTO 0) := "011"; CONSTANT state4 : std_logic_vector(2 DOWNTO 0) := "100"; CONSTANT state5 : std_logic_vector(2 DOWNTO 0) := "101"; CONSTANT state6 : std_logic_vector(2 DOWNTO 0) := "110"; CONSTANT state7 : std_logic_vector(2 DOWNTO 0) := "111"; SIGNAL state : std_logic_vector(2 DOWNTO 0);SIGNAL cnt : std_logic_vector(2 DOWNTO 0);BEGINPROCESS(clk,rst)BEGINIF (NOT rst = '1') THENstate <= state0;cnt <= "000";ELSIF(clk'EVENT AND clk='1')THENcnt <= cnt + "001";IF (cnt = "111") THENCASE state ISWHEN state0 =>state <= state1; WHEN state1 =>state <= state2; WHEN state2 =>state <= state3; WHEN state3 =>state <= state4; WHEN state4 =>state <= state5; WHEN state5 =>state <= state6; WHEN state6 =>state <= state7; WHEN state7 =>state <= state0; WHEN OTHERS =>NULLEND CASE;END IF;END IF;END PROCESS;PROCESS(state)BEGINCASE state ISWHEN state0 =>c <= "";WHEN state1 =>c <= "";WHEN state2 =>c <= "";WHEN state3 =>c <= "";WHEN state4 =>c <= "";WHEN state5 =>c <= "";WHEN state6 =>c <= "";WHEN state7 =>c <= "";WHEN OTHERS =>NULL;END CASE;END PROCESS;END arch;3.4library ieee;use ieee.std_logic_1164.all;entity sanba isport(a,b,c:in std_logic;y7,y6,y5,y4,y3,y2,y1,y0:out std_logic); end entity sanba;architecture behav of sanba issignal abc: std_logic_vector(2 downto 0);beginabc <= a & b & c ;process(a,b,c)begincase abc iswhen "000" =>y0<='0';y1<='1';y2<='1';y3<='1';y4<='1';y5<='1';y6<='1';y7<='1';when "001" =>y0<='1';y1<='0';y2<='1';y3<='1';y4<='1';y5<='1';y6<='1';y7<='1';when "010" =>y0<='1';y1<='1';y2<='0';y3<='1';y4<='1';y5<='1';y6<='1';y7<='1';when "011" =>y0<='1';y1<='1';y2<='1';y3<='0';y4<='1';y5<='1';y6<='1';y7<='1';when "100" =>y0<='1';y1<='1';y2<='1';y3<='1';y4<='0';y5<='1';y6<='1';y7<='1';when "101" =>y0<='1';y1<='1';y2<='1';y3<='1';y4<='1';y5<='0';y6<='1';y7<='1';when "110" =>y0<='1';y1<='1';y2<='1';y3<='1';y4<='1';y5<='1';y6<='0';y7<='1';when "111" =>y0<='1';y1<='1';y2<='1';y3<='1';y4<='1';y5<='1';y6<='1';y7<='0'; when others =>end case;end process;end architecture behav;3.5 library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY first ISPORT (clk : IN std_logic;rst : IN std_logic;c : OUT std_logic_vector(7 DOWNTO 0));END first;ARCHITECTURE arch OF first ISCONSTANT state0 : std_logic_vector(2 DOWNTO 0) := "000"; CONSTANT state1 : std_logic_vector(2 DOWNTO 0) := "001"; CONSTANT state2 : std_logic_vector(2 DOWNTO 0) := "010"; CONSTANT state3 : std_logic_vector(2 DOWNTO 0) := "011"; CONSTANT state4 : std_logic_vector(2 DOWNTO 0) := "100"; CONSTANT state5 : std_logic_vector(2 DOWNTO 0) := "101"; CONSTANT state6 : std_logic_vector(2 DOWNTO 0) := "110"; CONSTANT state7 : std_logic_vector(2 DOWNTO 0) := "111"; SIGNAL state : std_logic_vector(2 DOWNTO 0);SIGNAL cnt : std_logic_vector(2 DOWNTO 0);BEGINPROCESS(clk,rst)BEGINIF (NOT rst = '1') THENstate <= state0;cnt <= "000";ELSIF(clk'EVENT AND clk='1')THENcnt <= cnt + "001";IF (cnt = "111") THENCASE state ISWHEN state0 =>state <= state1;WHEN state1 =>state <= state2;WHEN state2 =>state <= state3;WHEN state3 =>state <= state4; WHEN state4 =>state <= state5; WHEN state5 =>state <= state6; WHEN state6 =>state <= state7; WHEN state7 =>state <= state0; WHEN OTHERS =>NULL;END CASE;END IF;END IF;END PROCESS;PROCESS(state)BEGINCASE state ISWHEN state0 =>c <= "";WHEN state1 =>c <= "";WHEN state2 =>c <= "";WHEN state3 =>c <= "";WHEN state4 =>c <= "";WHEN state5 =>c <= "";WHEN state6 =>c <= "";WHEN state7 =>c <= "";WHEN OTHERS =>NULL;END CASE;END PROCESS;END arch;3.6 library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY first ISPORT (clk : IN std_logic;rst : IN std_logic;c : OUT std_logic_vector(7 DOWNTO 0));END first;ARCHITECTURE arch OF first ISCONSTANT state0 : std_logic_vector(2 DOWNTO 0) := "000"; CONSTANT state1 : std_logic_vector(2 DOWNTO 0) := "001"; CONSTANT state2 : std_logic_vector(2 DOWNTO 0) := "010"; CONSTANT state3 : std_logic_vector(2 DOWNTO 0) := "011"; CONSTANT state4 : std_logic_vector(2 DOWNTO 0) := "100"; CONSTANT state5 : std_logic_vector(2 DOWNTO 0) := "101";CONSTANT state6 : std_logic_vector(2 DOWNTO 0) := "110"; CONSTANT state7 : std_logic_vector(2 DOWNTO 0) := "111"; SIGNAL state : std_logic_vector(2 DOWNTO 0);SIGNAL cnt : std_logic_vector(2 DOWNTO 0);BEGINPROCESS(clk,rst)BEGINIF (NOT rst = '1') THENstate <= state0;cnt <= "000";ELSIF(clk'EVENT AND clk='1')THENcnt <= cnt + "001";IF (cnt = "111") THENCASE state ISWHEN state0 =>state <= state1;WHEN state1 =>state <= state2;WHEN state2 =>state <= state3;WHEN state3 =>state <= state4;WHEN state4 =>state <= state5;WHEN state5 =>state <= state6;WHEN state6 =>state <= state7;WHEN state7 =>state <= state0; WHEN OTHERS =>NULL;END CASE;END IF;END IF;END PROCESS;PROCESS(state)BEGINCASE state ISWHEN state0 =>c <= "";WHEN state1 =>c <= "";WHEN state2 =>c <= "";WHEN state3 =>c <= "";WHEN state4 =>c <= "";WHEN state5 =>c <= "";WHEN state6 =>c <= "";WHEN state7 =>c <= "";WHEN OTHERS =>NULL;END CASE;END PROCESS;END arch;3.7 library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY first ISPORT (clk : IN std_logic;rst : IN std_logic;c : OUT std_logic_vector(7 DOWNTO 0));END first;ARCHITECTURE arch OF first ISCONSTANT state0 : std_logic_vector(2 DOWNTO 0) := "000"; CONSTANT state1 : std_logic_vector(2 DOWNTO 0) := "001"; CONSTANT state2 : std_logic_vector(2 DOWNTO 0) := "010"; CONSTANT state3 : std_logic_vector(2 DOWNTO 0) := "011"; CONSTANT state4 : std_logic_vector(2 DOWNTO 0) := "100"; CONSTANT state5 : std_logic_vector(2 DOWNTO 0) := "101"; CONSTANT state6 : std_logic_vector(2 DOWNTO 0) := "110"; CONSTANT state7 : std_logic_vector(2 DOWNTO 0) := "111"; SIGNAL state : std_logic_vector(2 DOWNTO 0);SIGNAL cnt : std_logic_vector(2 DOWNTO 0);BEGINPROCESS(clk,rst)BEGINIF (NOT rst = '1') THENstate <= state0;cnt <= "000";ELSIF(clk'EVENT AND clk='1')THENcnt <= cnt + "001";IF (cnt = "111") THENCASE state ISWHEN state0 =>state <= state1; WHEN state1 =>state <= state2; WHEN state2 =>state <= state3; WHEN state3 =>state <= state4; WHEN state4 =>state <= state5; WHEN state5 =>state <= state6; WHEN state6 =>state <= state7; WHEN state7 =>state <= state0; WHEN OTHERS =>NULL;END CASE;END IF;END IF;END PROCESS;PROCESS(state)BEGINCASE state ISWHEN state0 =>c <= "";WHEN state1 =>c <= "";WHEN state2 =>c <= "";WHEN state3 =>c <= "";WHEN state4 =>c <= "";WHEN state5 =>c <= "";WHEN state6 =>c <= "";WHEN state7 =>c <= "";WHEN OTHERS =>NULL;END CASE;END PROCESS;END arch;3.8 library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY first ISPORT (clk : IN std_logic;rst : IN std_logic;c : OUT std_logic_vector(7 DOWNTO 0));END first;ARCHITECTURE arch OF first ISCONSTANT state0 : std_logic_vector(2 DOWNTO 0) := "000"; CONSTANT state1 : std_logic_vector(2 DOWNTO 0) := "001"; CONSTANT state2 : std_logic_vector(2 DOWNTO 0) := "010"; CONSTANT state3 : std_logic_vector(2 DOWNTO 0) := "011"; CONSTANT state4 : std_logic_vector(2 DOWNTO 0) := "100"; CONSTANT state5 : std_logic_vector(2 DOWNTO 0) := "101"; CONSTANT state6 : std_logic_vector(2 DOWNTO 0) := "110"; CONSTANT state7 : std_logic_vector(2 DOWNTO 0) := "111"; SIGNAL state : std_logic_vector(2 DOWNTO 0);SIGNAL cnt : std_logic_vector(2 DOWNTO 0);BEGINPROCESS(clk,rst)BEGINIF (NOT rst = '1') THENstate <= state0;cnt <= "000";ELSIF(clk'EVENT AND clk='1')THENcnt <= cnt + "001";IF (cnt = "111") THENCASE state ISWHEN state0 =>state <= state1;WHEN state1 =>state <= state2;WHEN state2 =>state <= state3; WHEN state3 =>state <= state4; WHEN state4 =>state <= state5; WHEN state5 =>state <= state6; WHEN state6 =>state <= state7; WHEN state7 =>state <= state0; WHEN OTHERS =>NULL;END CASE;END IF;END IF;END PROCESS;PROCESS(state)BEGINCASE state ISWHEN state0 =>c <= "";WHEN state1 =>c <= "";WHEN state2 =>c <= "";WHEN state3 =>c <= "";WHEN state4 =>c <= "";WHEN state5 =>c <= "";WHEN state6 =>c <= "";WHEN state7 =>c <= "";WHEN OTHERS =>NULL;END CASE;END PROCESS;END arch;4.流水灯原理图图1 顶层原理图5.仿真波形图图(2)顶层仿真波形图6.心得体会通过本次课程设计,我基本对EDA有了入门的了解和认识,在课堂之外进一步加深了对EDA课程各知识点的学习和以及quartusII软件开发平台的操作。

FPGA入门系列实验教程——LED流水灯1.实验任务让实验板上的8个LED实现流水灯的功能。

通过这个实验,进一步掌握采用计数与判断的方式来实现分频的Verilog HDL的编程方法以及移位运算符的使用。

2.实验环境硬件实验环境为艾米电子工作室型号EP2C8Q208C8增强版开发套件。

软件实验环境为Quartus II8.1开发软件。

3.实验原理流水灯,顾名思义就是让LED象水一样的点亮。

如果把流水做慢动作播放,可以想象到其实就是移动,即:把水块不断地向同一方向移动,而原来的水块保持不动,就形成了流水。

同样,如果使得最左边的灯先亮;然后,通过移位,在其右侧的灯,由左向右依次点亮,而已经亮的灯又不灭,便形成了向右的流水灯。

初始状态时,8个灯都不亮。

每来一个时钟脉冲CLK,计数器就加1。

每当判断出计数器中的数值达到25000000时,就会点亮一个灯,并进行移位。

FPGA输出的数据就应该首先是10000000,隔1秒钟变成11000000……一直变化到11111111,这样,依次点亮所有的灯,就形成了流水灯。

而当8个灯都点亮时,需要一个操作使得所有的灯恢复为初始状态,即:灯都不亮。

然后,再一次流水即可。

如果是右移位,就出现向右流水的现象;反之,向左流水。

4.实验程序module ledwater(clk,led);//模块名及端口参数output[7:0]led;//输出端口定义input clk;//输入端口定义,50M时钟reg[8:0]led_out;//变量led_out定义为寄存器型reg[8:0]led_out1;//变量led_out1定义为寄存器型reg[25:0]buffer;//中间变量buffer定义为寄存器型always@(posedge clk)beginbuffer=buffer+1;if(buffer==26'd2*******)//判别buffer数值为25000000时,做输出处理beginled_out=led_out<<1;//led向左移位,空闲位自动添0补位if(led_out==9'b000000000)led_out=9'b111111111;led_out1=~led_out;//取反输出endendassign led=led_out1[7:0];endmodule5.实验步骤(1)建立新工程项目:打开Quartus II软件,进入集成开发环境,点击File→New project wizard建立一个工程项目ledwater。

实验一、4-2编码器及流水灯实验注意事项:1、特别注意:在做Quartus II 工程时必须将未分配的管脚置为三态输入。

Quartus II --> Assignments --> Device … --> Device --> Device & Pin Options … --> Unused Pins --> Reserve all unused pins : AS input tri-stated 。

2、按键SW1—SW4与LED 指示灯LED1—LED4分布图如下:FPGA 管脚备注3、系统复位与系统时钟(50MHz )分配脚4、对EP3C25-B 型电路板的LED 与按键测试程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY LED_BUTTON ISPORT ( BUTTON_IN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED_OUT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END LED_BUTTON;ARCHITECTURE A OF LED_BUTTON ISBEGINLED_OUT <= not BUTTON_IN;END A;管脚分配为:BUTTON_IN分别接N1(SW1)、N2(SW2)、U9(SW3)、V9(SW4);LED_OUT分别接:P11(LED1)、U11(LED2)、R11(LED3)、N11(LED4)。

按注意事项1进行设置!!!之后再次编译!内容一、4-2编码器的设计1、有按键按下时则进行编码输出给LED显示,采用优先编码方式;2、自行编写4-2编码器VHDL代码;3、管脚分配注意事项:参照LED与按键测试程序。

内容二、4位流水灯的实现1、编写实现1s时间间隔流水灯VHDL代码;2、管脚分配注意事项:参照LED与按键测试程序。

综合课程设计题 目 基于Quartus II 6.0的花样流水灯的设计学生姓名专业名称 ,指导教师2013 年 6 月 24 日基于Quartus II 6.0的花样流水灯的设计随着EDA技术发展和应用领域的扩大与深入,EDA技术在电子信息、通讯、自动控制及计算机应用等领域的重要性突出。

随着技术市场与人才市场对EDA 的需求不断提高,产品的市场需求和技术市场的要求也必然会反映到教学领域和科研领域中来。

因此学好EDA技术对我们有很大的益处。

EDA是指以计算机为工具,在EDA软件平台上,根据设计社描述的源文件(原理图文件、硬件描述语言文件或波形图文件),自动完成系统的设计,包括编译、仿真、优化、综合、适配(或布局布线)以及下载。

流水灯是一串按一定的规律像流水一样连续闪亮,流水灯控制是可编程控制器的一个应用,其控制思想在工业控制技术领域也同样适用。

流水灯控制可用多种方法实现,但对现代可编程控制器而言,基于EDA技术的流水灯设计也是很普遍的。

1.设计目的1.1 学习使用EDA集成设计软件Quartus II,电路描述,综合,模拟过程1.2 了解基于EDA应用系统的设计方法1.3 掌握使用EDA工具设计流水灯的设计思路和设计方法1.4熟练使用Quartus II对实验程序进行改错,调试以及演示现象2. 设计说明此次实验要求我们通过学习的EDA课程,来编制VHDL程序,以及使用这些程序代码来显示我们所要求的结果。

流水灯设计是由八只LED显示灯来实现的,通过程序代码来控制这八只灯的亮灭,在实验初期,我们首先得编程序,通过我们上课所学的基础知识,再结合近段时间去图书馆查阅的有关参考书籍,以及网上所搜索的相关知识,我们小组共同完成了程序的编制,程序代码在下面有详细介绍。

其次,我们需要掌握QuartusII的用法,因为要求的现象是通过这个软件实现的,在EDA实验课程中老师有详细介绍QuartusII的使用方法,所以在这一阶段对我们来说也比较得心应手,安装,调试,然后将编好的程序输入,在此过程中我们遇到了点小困难,显示程序有错误,但是通过我们集体的努力,终于发现,是因为在操作时,我们应该先创建自己的文件夹,然后统一存放在一起,而我们存放的地方有误,所以显示不出我们所输入的代码。

实验五流水灯的设计一、实验目的1、了解流水灯的工作原理。

二、实验原理及内容实验原理要完成本实验,首先必须了解流水灯的原理。

所谓的流水灯实际上就是由多个LED发光二极管构成的电路,当发光二极管可以依次点亮时,即能呈现流水的效果。

实验内容1、设计能带8个LED发光管发光,并按照要求轮流发光,产生流水灯的流动效果。

2、应具有两种以上不同风格的流动闪亮效果。

比如依次点亮或者依次熄灭。

(选作)3、有起动、停止控制键。

(选作)4、有流动闪亮效果选择设置键。

(选作)5、对所编写的电路进行编译及正确的仿真。

三、实验条件Quartus II实验环境四、实验与仿真顶层文件如下:Cp为时钟信号R为异步清零端。

当r=1时清零。

S[2..0]为输入端。

根据s的不同取值来实现不同的功能。

D[7..0]为预制数Q[7..0]为输出功能表如下VHDL编码如下library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity traffic isport(clk,enb:in std_logic;ared,agreen,ayellow,bred,bgreen,byellow:buffer std_logic;acounth,acountl,bcounth,bcountl:buffer std_logic_vector(3 downto 0));end traffic;architecture one of traffic isbeginprocess(clk,enb)variable lightstatus:std_logic_vector(5 downto 0);beginif(clk'event and clk='1')thenlightstatus:=ared&agreen&ayellow&bred&bgreen&byellow;if((acounth="0000" and acountl="0000") or(bcounth="0000" and bcountl="0000"))thencase lightstatus iswhen "010100"=>lightstatus:="001100";acountl<="0101";acounth<="0000";bcountl<="0101";bcounth<="0000"; when"001100"=>if(enb='1')thenlightstatus:="100010";acountl<="0000";acounth<="0011";bcountl<="0101";bcounth<="0010";elselightstatus:="010100";acountl<="0101";acounth<="0100";bcountl<="0000";bcounth<="0101"; end if;when "100010"=>lightstatus:="100001";acountl<="0101";acounth<="0000";bcountl<="0101";bcounth<="0000";when"100001"=>lightstatus:="010100";acountl<="0101";acounth<="0100";bcountl<="0000";bcounth<="0101";when others=>lightstatus:="010100";acountl<="0101";acounth<="0100";bcountl<="0000";bcounth<="0101";end case;elseif(acountl="0000")thenacounth<=acounth-1;acountl<="1001";elseacountl<=acountl-1;end if;if(bcountl="0000")thenbcounth<=bcounth-1;bcountl<="1001";elsebcountl<=bcountl-1;end if;end if;end if;ared<=lightstatus(5);agreen<=lightstatus(4);ayellow<=lightstatus(3);bred<=lightstatus(2);bgreen<=lightstatus(1);byellow<=lightstatus(0); end process;end one;仿真:右移:依次点亮灯左移:依次点亮灯循环右移:循环点亮循环左移:循环点亮。

end process;

led_8bit<=tmp;

end keyboard1;

在完成流水灯源程序的编辑后,执行”Processing”菜单下的“Start Compilation”命令,对keyboard1.vhd进行编译。

在完成对源文件的编译后,执行“File”菜单的“New”命令,或者直接按主窗口上的“创建新的文本文件”按钮,在弹出的新文件类型选择对话框中,选择“Vector Waveform File”生成仿真文件。

对引脚进行锁定。

执行”Assignments”菜单下的“Pins”命令,根据下图进行引脚设置。

用电缆连接电脑与设备箱,执行”Tools”菜单下的“Programmer”命令,在弹出的对话框中,单击“Hardware Setup”并在新弹出的对话框中选择驱动,然后退出至上一层对话框,单击“Start”进行下载烧录。

【实验数据整理与归纳】

keyboard11.vhd 实际效果图

keyboard11.vwf

【实验结果与分析】

计数译码系统电路的仿真波形如图keyboard11.vwf所示,键值为"1110"时,LED0~LED7的状态应为"11000000";键值为"1101"时,LED0~LED7的状态应为"00110000",依此类推。

仿真结果验证了设计的正确性。

而实际情况与仿真结果相吻合。

【实验中遇到的问题及解决方案】

1.不知道如何对引脚进行锁定。

解决方案:上网搜寻教程。

2.驱动安装失败。

解决方案:根据老师发的教程,更换别的方法进行安装。