数字式竞赛抢答器的VHDL设计

- 格式:docx

- 大小:108.21 KB

- 文档页数:10

「基于VHDL的智力竞赛抢答器完全设计」智力竞赛抢答器是一种常见的比赛辅助设备,它可以帮助比赛主持人快速确定哪位选手按下抢答器按钮,并且在一定的时间内限制其他选手抢答。

本文将基于VHDL(Very High Speed Integrated Circuit Hardware Description Language)对智力竞赛抢答器进行完全设计。

首先,我们需要确定抢答器的基本功能。

智力竞赛抢答器应该具备以下功能:1.按下按钮时抢答器需要发出信号,主持人可以通过这个信号来确认哪位选手抢答。

2.如果已经有选手抢答,其他选手不能再次抢答,抢答器需要提供信号以阻止其他选手抢答。

基于上述功能需求,我们可以进行如下设计。

首先,我们需要使用VHDL语言定义抢答器所需要用到的模块和信号。

```entity 抢答器 isportStart_Button : in std_logic; -- 抢答器按钮输入信号Response : out std_logic; -- 抢答信号Busy : out std_logic -- 抢答器忙碌信号end entity 抢答器;```在抢答器模块中,我们需要定义两个重要的信号:Start_Button,表示抢答器按钮的输入信号;Response,表示抢答信号的输出;Busy,表示抢答器忙碌信号的输出。

接下来,我们需要定义这些信号的行为。

根据抢答器的功能需求,我们可以进行如下行为定义。

```architecture 抢答器行为 of 抢答器 issignal isPressed : std_logic := '0'; -- 按钮按下信号signal isBusy : std_logic := '0'; -- 抢答器忙碌信号beginprocess(Start_Button)beginif Start_Button = '1' and isBusy = '0' then -- 按钮按下,且抢答器没有被占用isPressed <= '1'; -- 设置按钮按下信号为1isBusy <= '1'; -- 设置抢答器忙碌信号为1end if;if isPressed = '1' then -- 如果按钮被按下Response <= '1'; -- 输出抢答信号else -- 如果按钮未被按下Response <= '0'; -- 不输出抢答信号end if;end process;--重置抢答器状态reset_process : processbeginif Start_Button = '0' thenisPressed <= '0'; -- 标记按钮未被按下isBusy <= '0'; -- 标记抢答器未被占用end if;end process;--根据抢答器的状态设置忙碌信号busy_signal_process : process(response, isBusy) beginif isBusy = '1' thenBusy <= '1'; -- 输出忙碌信号elseBusy <= '0'; -- 不输出忙碌信号end if;end process;end architecture 抢答器行为;```以上代码定义了抢答器的行为,通过进程的方式处理输入信号,并根据当前的状态输出相应的信号。

数字系统设计与硬件描述语言期末考试作业题目:数字式竞赛抢答器设计学院:电子信息工程专业:电子信息工程学号:姓名:一、选题设计描述1.功能介绍此设计用于竞赛的四人抢答,有如下的功能:(1)具有多路抢答功能,台数设计为四;(2)具有抢答器开始后30秒倒计时,30秒后无人抢答显示超时,并报警;(3)能显示超前抢答犯规,并警报;(4)能显示各组得分,大队加分,答错扣分;当系统复位,主持人按下抢答开始按键,处于使能状态,抢答开始,某路抢答键按下时,该路信号将其他路信号锁存,同时抢答铃声响起,直至此路按键松开,显示该路组号。

2.算法简介本设计采用分层设计思想,分为:信号鉴别模块、计时模块、计分模块、BCD译码模块、分频器,还有顶层模块。

信号鉴别模块。

此模块主要实现抢答器的抢答功能,并能够分辨是正常抢答还是提前抢答,选取最先按下的一路信号,锁存其余信号,实现信号选取功能。

在此模块中,用到的信号为抢答信号a、b、c、d;抢答使能信号en;抢答结果信号states;警报时钟信号clk2;复位信号rst;提前抢答信号fangui。

计时模块。

此模块主要实现抢答过程中的计时功能,在抢答开始后进行30秒的倒计时,且在30秒后显示无人抢答报警信号。

其中有抢答时钟信号clk;系统复位信号rst;抢答使能信号en;无人抢答警报信号warn;计时中止信号stop;计时十位个位信号tb,ta。

计分模块。

此模块主要实现给四个抢答器计分的功能,初始条件下,为每个抢答器信号预制5分,当某组抢答且回答正确时加一分,答错减一分,未获答题机会时保持不变。

其中设有时钟信号clk;复位信号rst;抢答使能信号en;抢答结果显示信号states;记分加减信号add(add=‘1’时为加,add=‘0’时为减);四个信号的得分显示信号a_out,b_out,c_out,d_out。

BCD译码模块。

此模块主要实现将抢答结果信号显示在bcd七段译码器上。

题目:基于VHDL语言的八路数字抢答器设计【作者简介】班级:班号:姓名:学号:摘要抢答器作为一种电子产品,早已广泛应用于各种智力和知识竞赛场合,是竞赛问答中一种常用的必备装置;从原理上讲,它是一种典型的数字电路,其中包括了组合逻辑电路和时序逻辑电路.电路结构形式多种多样,可以利用简单的与非门构成,也可以利用触发器构成,也可以利用单片机来完成.利用单片机来设计抢答器,使得结果更简单,功能更优越。

本设计是基于单片机控制的六路抢答器,利用单片机的定时器/计数器定时和记数的原理,将软、硬件有机地结合起来,使得系统能够正确地进行计时,同时使数码管能够正确地显示时间。

用开关做键盘输出,扬声器发生提示。

同时系统能够实现:在抢答中,只有开始后抢答才有效,如果在开始抢答前抢答为无效;抢答限定时间和回答问题的时间可在1-99s 设定;可以显示是哪位选手有效抢答和无效抢答,正确按键后有音乐提示;抢答时间和回答问题时间倒记时显示,满时后系统计时自动复位及主控强制复位;按键锁定,在有效状态下,按键无效非法。

关键词抢答器;EDA;VHDL语言AbstractAnswer devices as an electronic products, has long been widely used in a variety of occasions, intelligence and knowledge competitions, quiz contests are essential in a commonly used device; from the principle, it is a typical digital circuit, including a combination of logic circuits and sequential logic circuit. Circuit structure of a variety of forms, can make use of simple and non-gate structure can also be used to trigger composition, can also be used to complete single-chip microcomputer. Answer the use of single-chip design, and makes the results more simple function better.The design is based on the six-way SCM Answer, and the use of single-chip timer / counter timing and number of the principles in mind, the hardware and software combine to make the system time correctly, while the digital control able to correctly display the time. Switch the keyboard to do with output, speaker prompted occurred. At the same time, the system can be realized: In the Answer, only after the Answer to be valid, if at the beginning of pre-Answer Answer invalid; Answer to answer the question of limited time and the time can be set in 1-99s; can show who's effective and Answer Answer invalid, the correct button prompt after the music; Answer question time and time 倒记时show full time after the system automatically reset and master reset mandatory; keys locked in the effective state, the key is invalid illegal.Key words answer devices;EDA;VHDL language一、设计原理与技术方法:(一)整体简介Max+plusII(或写成Maxplus2,或MP2) 是Altera公司推出的的第三代PLD开发系统(Altera第四代PLD开发系统被称为:QuartusII,主要用于设计新器件和大规模CPLD/FPGA).使用MAX+PLUSII的设计者不需精通器件内部的复杂结构。

1 引言在日常的业余活动中,经常会选择举办一些智力竞赛,这就需要用到抢答器。

目前市场上已有各种各样的智力竞赛抢答器,但绝大多数是早期设计的,以模拟电路、数字电路或者模拟电路与数字电路相结合的产品。

这部分抢答器已相当成熟, 但功能越多的电路相对来说就越复杂,且成本偏高,故障高,显示方式简单( 有的甚至没有显示电路),无法判断提前抢按按钮的行为,不便于电路升级换代。

本设计就是基于VHDL设计的一个智力竞赛抢答器尽量使竞赛真正达到公正、公平、公开。

1.1设计的目的本次设计的目的就是在掌握EDA实验开发系统的初步使用基础上,了解EDA技术,了解并掌握VHDL硬件描述语言的设计方法和思想,通过学习的VHDL语言结合电子电路的设计知识理论联系实际,掌握所学的课程知识,学习VHDL基本单元电路的综合设计应用。

通过对智力竞赛抢答器的设计,巩固和综合运用所学课程,理论联系实际,提高设计能力,提高分析、解决计算机技术实际问题的独立工作能力。

1.2设计的内容本文是设计的一个四路智力竞赛抢答器,利用VHDL设计抢答器的各个模块,并使用EDA 工具对各模块进行仿真验证。

智力竞赛抢答器的设计分为四个模块:鉴别锁存模块;答题计时模块;抢答计分模块以及扫描显示模块。

把各个模块整合后,通过电路的输入输出对应关系连接起来。

设计成一个有如下功能的抢答器:(1)具有第一抢答信号的鉴别锁存功能。

在主持人发出抢答指令后,若有参赛者按抢答器按钮,则该组指示灯亮,显示器显示出抢答者的组别。

同时电路处于自锁状态,使其他组的抢答器按钮不起作用。

(2)具有计分功能。

在初始状态时,主持人可以设置答题时间的初始值。

在主持人对抢答组别进行确认,并给出倒计时计数开始信号以后,抢答者开始回答问题。

此时,显示器从初始值开始计时,计至0时停止计数。

(3)具有计分功能。

在初始状态时,主持人可以给每组设置初始分值。

第三者组抢答完毕后,由主持人打分,答对一次加10分阶段,错则减10分。

课程设计班级:姓名:学号:指导教师:成绩:电子与信息工程学院数字式竞赛抢答器设计要求:设计一个可容纳四组参赛者同时抢答的数字抢答器,可判断第一抢答者并报警指示抢答成功,其他组抢答均无效。

若提前抢答则对相应抢答组发出警报。

给出系统总体组成框图,设计思路,完成以上模块的VHDL 实现及功能仿真,顶层文件及整体仿真。

系统组成框图设计思路抢答队伍共分为四组A,B,C,D 。

当主持人按下CLR 键后,抢答器状态清零,四组队伍才可以按抢答键抢答,如果主持人未按下CLR 键即未宣布抢答开始时,有人抢答会发出报警。

抢答信号A,B,C,D 输入电路中后,将组别号输出到相应端A1,B1,C1,D1,并将组别序号换算为四位二进制信号输出到示端。

抢答输入VHDL程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY QDQ ISPORT(CLR: IN STD_LOGIC;A, B, C, D: IN STD_LOGIC;A1,B1,C1,D1,alarm: OUT STD_LOGIC;STATES: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END ENTITY QDQ;ARCHITECTURE ART OF QDQ ISCONSTANT S1: STD_LOGIC_VECTOR:="0001";CONSTANT S2: STD_LOGIC_VECTOR:="0010";CONSTANT S3: STD_LOGIC_VECTOR:="0100";CONSTANT S4: STD_LOGIC_VECTOR:="1000";BEGINPROCESS(CLR,A,B,C,D) ISBEGINIF CLR='1' THEN STATES<="0000"; A1<='0'; B1<='0'; C1<='0'; D1<='0';alarm<='0'; if (A='1' or B='1' or C='1' or D='1') then alarm<='1';end if;end if;if CLR='0' thenif (A='1'AND B='0'AND C='0'AND D='0') THENA1<='1'; B1<='0'; C1<='0'; D1<='0'; STATES<=S1; alarm<='0';ELSIF (A='0'AND B='1'AND C='0'AND D='0') THENA1<='0'; B1<='1'; C1<='0'; D1<='0'; STATES<=S2; alarm<='0';ELSIF (A='0'AND B='0'AND C='1'AND D='0') THENA1<='0'; B1<='0'; C1<='1'; D1<='0'; STATES<=S3; alarm<='0';ELSIF (A='0'AND B='0'AND C='0'AND D='1') THENA1<='0'; B1<='0'; C1<='0'; D1<='1'; STATES<=S4; alarm<='0';END IF;end if;END PROCESS;END ARCHITECTURE ART;仿真波形心得体会经过一周努力,我成功地设计出了四路电子抢答器。

1方案设计1.1方案设计分析(1)抢答器是知识竞赛、智力竞赛的一种常用装置。

其实现方法大致有三种:一是基于74系列或4000系列IC,用数字系统设计的方法实现;二是基于CPLD/FPGA,使用EDA的方法实现;三是用单片机实现。

(2)三种方法作比较,当抢答器功能较多时,第一种方法电路将是庞大的,电路是复杂的;第二种方法可实现一片式设计,电路是简明的,并且预设置修改方便;至于第三种,单片机大致主要用来做计数器了,略有大材小用之嫌。

(3)本设计采用EDA方法,就多功能抢答器的实现作了尝试,并在Altera公司的低端产品EPK30TC144-3上实现。

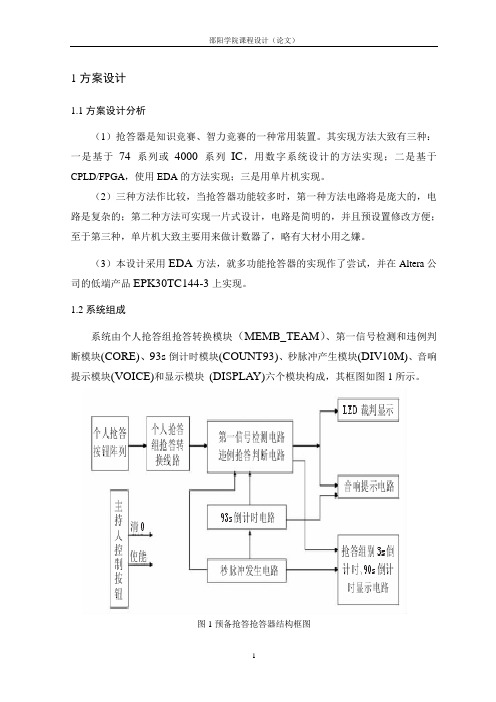

1.2系统组成系统由个人抢答组抢答转换模块(MEMB_TEAM)、第一信号检测和违例判断模块(CORE)、93s倒计时模块(COUNT93)、秒脉冲产生模块(DIV10M)、音响提示模块(VOICE)和显示模块(DISPLAY)六个模块构成,其框图如图1所示。

图1预备抢答抢答器结构框图图2为系统的顶层gdf文件。

图2预备抢答抢答器顶层gdf文件2功能描述(1)全部组员参与抢答。

抢答器供6个代表队(3人/队)比赛,每队设有3个抢答按钮。

知识竞赛进入抢答阶段时,每个队的3个人都可以参与抢答,改变了某些抢答器每队只能一人参与抢答的局面。

如果每队只有一人(即个人抢答竞赛),任意使用每组3只按钮中的一只。

(2)主持人(通常是辅助主持人)控制系统清0和系统启动。

(3)预备抢答。

四声音响提示预备、开始。

前面三响低音为预备提示音,最后一响(高音)为“开始”提示音,抢答器据此自动判断抢答的有效和违例。

常见的另一种抢答方式是:主持人口说“开始”,同时用手按下抢答有效开关。

两者相比较,后者需要人为判断抢答是否违例,容易产生赛场争议,而前者更为合理。

预备抢答阶段除声音提示外,还辅以LED数码管进行3、2、1倒计时显示。

(4)锁存与自动裁判。

锁存第一抢答组别(个人)的编号,并在LED数码管上显示,同时扬声器、LED发出声光提示,提示有效或违例。

VHDL四路抢答器的设计设计要求:1.抢答器同时供N名选手,(此处假设4个)分别用4个按钮S0~ S3表示。

2.设置一个系统“开始复位”开关S,该开关由主持人控制(当主持人按下该开关后以前的状态复位并且开始计时抢答)。

3.抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,并在LED数码管上显示,同时扬声器发出报警声响提示。

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止。

4. 抢答器具有定时抢答功能,且一次抢答的时间(0-99S)。

当主持人启动“开始复位”键后,定时器进行减计时。

5. 如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00。

一、概述抢答器的逻辑结构主要由抢答鉴别lock模块、定时模块、译码模块和报警器模块组成。

在整个抢答器中最关键的是如何实现抢答封锁,在控制键按下的同时计数器倒计时显示有效剩余时间。

除此之外,整个抢答器还需有一个“复位开始”信号,以便抢答器能实现清零和开始。

抢答器共有3个输出显示,选手代号、计数器的个位和十位,他们输出全都为BCD码输出,这样便于和显示译码器连接。

当主持人按下控制键、选手按下抢答键蜂鸣器短暂响起。

•方案设计与论证嘿嘿!将该任务分成N个模块进行设计,分别为:抢答器鉴别模块、抢答器计时模块、译码模块、报警模块,最后是综合。

1. 抢答器鉴别模块:在这个模块中主要实现抢答过程中的抢答功能,并且能实现当有一路抢答按键按下时,该路抢答信号将其余个绿抢答封锁的功能。

在这个模块输入端有WARN输入(以时间控制系统的WARN输出信号为信号源)、一个和“时间控制系统”公用的CLEAR端、4人抢答输入信号端S0,S1,S2,S3和有一个时钟信号端CLK,这个时钟信号是个高频信号,用以扫描S0,S1,S2,S3是否有信号输入。

输出端有对应于S0,S1,S2,S3编号的4个指示灯LED 和4线2进制输出端STATES(用于锁存当前的状态),还有一个STOP 端用于指示S0,S1,S2,S3按钮状态(控制计时器停止)。

实验报告实验名称:VHDL实验实验日期:2012年3月7日学院:信息工程学院班级:2009级通信工程一班姓名:沈晶晶学号:2009550607数字式竞赛抢答器的VHDL设计1、设计任务及要求:设计任务:(1)设计一个可容纳8组参赛的数字式抢答器,每组设一个按钮,供抢答使用。

(2)抢答器具有第一信号鉴别和锁存功能,使除第一抢答者外的按钮不起作用。

(3)设置一个主持人“复位”按钮。

(4)主持人复位后,开始抢答,第一信号鉴别锁存电路得到信号后,由指示灯显示抢答组的编号,同时扬声器发出2~3秒的音响。

扩展功能:(5)设置一个计分电路,每组开始预制100分,由主持人计分,答对一次加10分,答错一次减10分。

设计要求:(1)采用VHDL语言编写程序,并在QUARTUS II平台中进行仿真,下载到EDA实验箱进行验证。

(2)编写设计报告,要求包括方案选择、程序清单、调试过程、测试结果及心得体会。

(3)设计时间和地点:两个星期,信息楼4楼EDA实验室。

定时抢答器的总体框图如图1所示,它由主体电路和扩展电路两部分构成,主体电路完成基本的抢答功能,即开始抢答后,当选手按动抢答键时,能显示选手的编号,同时能封锁输入电路,禁止其他选手抢答。

扩展电路完成各选手的得分显示功能。

定时抢答器的工作过程是:接通电源时,主持人将开关置于“清除”位置,抢答器处于禁止工作状态,编号显示器灭灯;抢答开始时,主持人将控制开关拨到“开始”位置,扬声器给出声响提示,抢答器处于工作状态,这时,抢答器完成以下工作:(1)优先编码器电路立即分辨出抢答者编号,并由锁存器进行锁存,然后由译码显示电路显示编号;(2)扬声器发出短暂声响,提醒主持人注意;(3)控制电路要对输入编码电路进行封锁,避免其他选手再次进行抢答;(4)当选手将问题回答完毕,主持人操作计分开关,计分电路采用十进制加/减计数器、数码管显示。

本轮抢答完毕,主持人操作控制开关,使系统回复到禁止工作状态,以便进行下一轮抢答。

VHDL四路智力抢答器EDA课程设计一、任务与目的1.1熟练掌握EDA工具软件Quartus的使用1.2熟悉使用VHDL硬件描述语言描述数字电路1.3学会使用VHDL进行大规模集成电路设计1.4学习使用CPLD/FPGA实验系统硬件验证电路设计的正确性1.5初步掌握EDA技术并具备一定的可编程逻辑芯片的开发能力二、设计题目与要求2.1设计题目四路智力竞赛抢答器2.2设计要求1.按所布置的题目要求,每一位学生独立完成全过程2.分模块层次化的设计;3.各功能模块的底层文件必须用VHDL语言设计,顶层文件可以用VHDL语言设计,也可以用原理图设计。

2.3设计内容设计一个可容纳四组参赛者同时抢答的数字抢答器。

主持人可控制系统发的清零和抢答的开始,控制电路可实现最快抢答选手按键抢答的判别和锁定功能,并禁止后续其他选手抢答。

抢答选手确定后给出选手编号的显示,抢答选手的编号显示保持到系统被清零为止,若提前抢答则对相应的抢答组发出警告。

*扩展内容:增加答题限时的功能,在确定了抢答成功有效后,有主持人按下答题限时功能键,开始9s的倒计时。

在计时结束后,超时提示LED闪烁。

在主持人按下clear开关时限时复位。

三、功能分析四路智力竞赛抢答器按功能设计分为三个模块1.抢答锁存模块,在主持人发出抢答指令后(start=’1’),若有参赛者按下抢答按钮,则显示器显示抢答组别,同时电路处于自锁状态,使其它组的抢答器不起作用。

主持人可以用清零按钮进行清零(clr=’0’).若抢答指令未发出(start=’0’),而有参赛者按下抢答按钮,则发出警告信号(alm=1).2.显示功能模块,在参赛者抢答信号(组别)发出后,对参赛者信号进行译码,然后用7段数码管显示出来。

3.计时模块,在确定了抢答成功有效后,有主持人按下答题限时功能键,开始9s的倒计时。

在计时结束后,超时提示LED亮。

在主持人按下clear开关时限时复位。

(扩展模块)四、设计思路分析,设计方案合理性分析与选择。

Shaanxi University of Tecnology 通信工程专业课程设计Ⅱ题目竞赛抢答器的设计与实现学生姓名蒋清洋学号0613024047所在院(系)陕西理工学院电信工程系专业班级通信工程专业0 7 3 班指导教师侯宝生完成地点陕西理工学院电信工程系实验室2010 年 3 月 19 日通信工程专业课程设计Ⅱ任务书院(系) 电信工程系专业班级通信工程专业073班学生姓名蒋清洋一、课程设计Ⅱ题目竞赛抢答器的设计与实现二、课程设计Ⅱ工作自 2010 年 3 月 1 日起至 2010 年 3 月 19 日止三、课程设计Ⅱ进行地点: 电信工程系实验室四、课程设计Ⅱ的内容要求:设计一竞赛抢答器的设计与实现(方法要求:EDA)1、设计一个可容纳6组(或4组)参赛的数字式抢答器,每组设一个按钮,供抢答使用。

2、抢答器具有第一信号鉴别和锁存功能,使除第一抢答者外的按钮不起作用。

3、设置一个主持人“复位”按钮。

4、主持人复位后,开始抢答,第一信号鉴别锁存电路得到信号后,有指示灯显示抢答组别,扬声器发出2~3秒的音响。

5、设置一个计分电路,每组开始预置100分,由主持人记分,答对一次加10分,答错一次减10分。

指导教师侯宝生系(教研室)通信工程教研室接受任务开始执行日期2010年3月1日学生签名蒋青洋目录摘要-------------------------------------------------------------------------------- 4 绪论--------------------------------------------------------------------------------- 6 第一章方案及原理----------------------------------------------------------------- 7 一方案提出与分析---------------------------------------------------------- 71.0总体方案框图 ----------------------------------- 71.1方案一 ------------------------------------- 71.2 方案二 -------------------------------------- 71.3 方案分析 -------------------------------------- 7二系统的设计方案 ------------------------------------ 7 三.设计原理-------------------------------------------------------- 93.1总体结构设计------------------------------------------------- 93.2 FPGA简介------------------------------------------------ 9 第二章单元模块设计-------------------------------------------------------- 12一、抢答鉴别单元-------------------------------------------------- 12二、计分器电路单元---------------------------------------------------------- 13三、计时器电路单元--------------------------------------------------------- 14四、译码单元-------------------------------------------------------- 16五、模块的打包:-------------------------------------------------------- 17 第三章硬件测试-------------------------------- 18 外接电路器件------------------------------------------------ 20参考文献------------------------------------------------- 23 课程总结--------------------------------------------------- 24 致谢---------------------------------------------------- 25 附录A ----------------------------------------------------- 26[摘要]抢答器在竞赛、文体娱乐活动(抢答活动)中,能准确、公正、直观地判断出抢答者的机器。

实验报告实验名称:VHDL实验实验日期:2012年3月7日学院:信息工程学院班级:2009级通信工程一班姓名:沈晶晶学号:2009550607数字式竞赛抢答器的VHDL设计1、设计任务及要求:设计任务:(1)设计一个可容纳8组参赛的数字式抢答器,每组设一个按钮,供抢答使用。

(2)抢答器具有第一信号鉴别和锁存功能,使除第一抢答者外的按钮不起作用。

(3)设置一个主持人“复位”按钮。

(4)主持人复位后,开始抢答,第一信号鉴别锁存电路得到信号后,由指示灯显示抢答组的编号,同时扬声器发出2~3秒的音响。

扩展功能:(5)设置一个计分电路,每组开始预制100分,由主持人计分,答对一次加10分,答错一次减10分。

设计要求:(1)采用VHDL语言编写程序,并在QUARTUS II平台中进行仿真,下载到EDA实验箱进行验证。

(2)编写设计报告,要求包括方案选择、程序清单、调试过程、测试结果及心得体会。

(3)设计时间和地点:两个星期,信息楼4楼EDA实验室。

定时抢答器的总体框图如图1所示,它由主体电路和扩展电路两部分构成,主体电路完成基本的抢答功能,即开始抢答后,当选手按动抢答键时,能显示选手的编号,同时能封锁输入电路,禁止其他选手抢答。

扩展电路完成各选手的得分显示功能。

定时抢答器的工作过程是:接通电源时,主持人将开关置于“清除”位置,抢答器处于禁止工作状态,编号显示器灭灯;抢答开始时,主持人将控制开关拨到“开始”位置,扬声器给出声响提示,抢答器处于工作状态,这时,抢答器完成以下工作:(1)优先编码器电路立即分辨出抢答者编号,并由锁存器进行锁存,然后由译码显示电路显示编号;(2)扬声器发出短暂声响,提醒主持人注意;(3)控制电路要对输入编码电路进行封锁,避免其他选手再次进行抢答;(4)当选手将问题回答完毕,主持人操作计分开关,计分电路采用十进制加/减计数器、数码管显示。

本轮抢答完毕,主持人操作控制开关,使系统回复到禁止工作状态,以便进行下一轮抢答。

抢答器的VHDL代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SJJ ISPORT(TEAM:IN STD_LOGIC_VECTOR(4 DOWNTO 0);RST,CLK:IN STD_LOGIC;JIFEN,S:IN STD_LOGIC;LED:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CQ,CQ_H:OUT STD_LOGIC_VECTOR(3 downto 0);LIGHT:OUT STD_LOGIC_VECTOR(4 downto 0);BELL:OUT STD_LOGIC);END;ARCHITECTURE one OF SJJ ISSIGNAL output:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL d:STD_LOGIC_VECTOR(4 downto 0);SIGNAL lock:STD_LOGIC:='0';SIGNAL ring:STD_LOGIC;BEGINQD:PROCESS(RST,CLK,TEAM)BeginIF RST='1' THEN OUTPUT<="0000"; d<=(OTHERS=>'0'); lock<='0';ElSIF CLK'EVENT AND CLK='1' THENIF TEAM="00001" THEN output<="0001";d<="00001";lock<='1';ELSIF TEAM="00010" THEN output<="0010";d<="00010";lock<='1';ELSIF TEAM="00100" THEN output<="0011";d<="00100";lock<='1';ELSIF TEAM="01000" THEN output<="0100";d<="01000";lock<='1';ELSIF TEAM="10000" THEN output<="0101";d<="10000";lock<='1';END IF;END IF;END PROCESS;XSZ:PROCESS(lock,RST)BEGINIF (RST='1') THEN LED<=output; LIGHT<=d;ELSIF (RST='0') AND (lock'EVENT AND lock='1') THEN LED<=output;LIGHT<=d;END IF;END PROCESS;JF:PROCESS(JIFEN,S)VARIABLE cqi: STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";VARIABLE cqih: STD_LOGIC_VECTOR(3 DOWNTO 0):="0001";BEGINIF JIFEN'EVENT AND JIFEN='1' THENIF S='1' THENIF cqi<9 THEN cqi:=cqi+1;ELSE cqi:=(OTHERS=>'0');END IF;ELSIF S ='0' THENIF cqi>0 THEN cqi:=cqi-1;ELSE cqi:="1001";END IF;END IF;IF cqi=9 AND S='1' THEN cqih:=cqih+1;ELSIF cqi=0 AND S='0' THEN--IF cqih="0000" THEN cqih:="0000";ELSE cqih:=cqih-1;--END IF;END IF;END IF;CQ_H<=cqih; CQ<=cqi;END PROCESS;BR:process(CLK,lock)VARIABLE num:INTEGER RANGE 0 TO 10;BEGINIF lock = '0' THENnum :=0; BELL<='0';ELSIF lock ='1' AND (CLK'EVENT AND CLK = '1') THEN IF num < 2 THENnum := num+1; BELL<='1';ELSE BELL <='0';END IF;END IF;END PROCESS;时序图:引脚检测:CQ[1]的引脚是PIN_52 ,CQ[2] 的引脚是PIN_67,CQ[3] 的引脚是PIN_68 ,CQ_H[0] 的引脚是PIN_47 ,CQ_H[1] 的引脚是PIN_48 ,CQ_H[2] 的引脚是PIN_49,CQ_H[3] 的引脚是PIN_50,JIFEN的引脚是PIN_7,LED[0] 的引脚是PIN_99,LED[1] 的引脚是PIN_103 ,LED[2] 的引脚是PIN_105 ,LED[3] 的引脚是PIN_106,LIGHT[0] 的引脚是PIN_11,LIGHT[1] 的引脚是PIN_32 ,LIGHT[2] 的引脚是PIN_33,LIGHT[3] 的引脚是PIN_34 ,LIGHT[4] 的引脚是PIN_35,RST的引脚是PIN_10 ,S的引脚是PIN_6,TEAM[0] 的引脚是PIN_1 ,TEAM[1] 的引脚是PIN_2,TEAM[2] 的引脚是PIN_3,TEAM[3] 的引脚是PIN_4,TEAM[4] 的引脚是PIN_5。

实验结果:根据实验,我们可以看出,按实验箱上先按键1,则显示管上会显示“1”,按键8可清零,这样就可依次抢答1~5,即5路抢答器。

由THEN[0]~THEN[4]为抢答键,而主持人控制抢答,并清零。

实验体会:我们认为,在这学期的实验中,在收获知识的同时,还收获了阅历,收获了成熟,在此过程中,我们通过查找大量资料,请教同学,以及不懈的努力,不仅培养了独立思考、动手操作的能力,在各种其它能力上也都有了提高。

更重要的是,在实验课上,我们学会了很多学习的方法。

而这是日后最实用的,真的是受益匪浅。

要面对社会的挑战,只有不断的学习、实践,再学习、再实践。

我们进一步熟知了VHDL程序的书写与设计,还更加熟练度应用QUARTUS II的平台进行仿真实验,并学会用VHDL语言自行设计抢答器电路的程序,并了解到VHDL语言设计的出现从根本上改变了以往数字电路的设计模式,使电路由硬件设计转变为软件设计,使电子设计的核心转化为VHDL 语言的编程设计,这样提高了设计的灵活性,使电路的设计复杂程度大大降低。

虽然结束了,也留下了很多遗憾,因为由于时间的紧缺和许多课业的繁忙,并没有做到最好,但是,最起码我们没有放弃,它是我们的骄傲!相信以后我们会以更加积极地态度对待我们的学习、对待我们的生活。

我们的激情永远不会结束,相反,我们会更加努力,努力的去弥补自己的缺点,发展自己的优点,去充实自己,只有在了解了自己的长短之后,我们会更加珍惜拥有的,更加努力的去完善它,增进它。

只有不断的测试自己,挑战自己,才能拥有更多的成功和快乐!。