计算机组成原理复习例题

- 格式:doc

- 大小:361.50 KB

- 文档页数:9

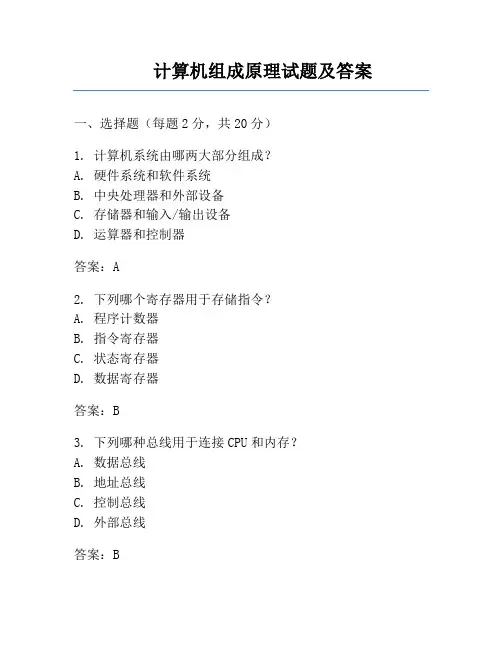

计算机组成原理试题及答案一、选择题。

1. 下列哪个是计算机组成原理的基本概念?A. 数据结构。

B. 操作系统。

C. 计算机体系结构。

D. 算法。

答案,C。

2. 计算机组成原理的核心是什么?A. 中央处理器。

B. 内存。

C. 输入输出设备。

D. 总线。

答案,A。

3. 下列哪个不是计算机组成原理中的主要部件?A. 控制单元。

B. 运算器。

C. 存储器。

D. 输入设备。

答案,D。

4. 计算机组成原理中,数据和指令在内存中是以什么形式存储的?B. 十进制。

C. 八进制。

D. 十六进制。

答案,A。

5. 计算机组成原理中,控制单元的主要功能是什么?A. 控制数据传输。

B. 进行运算。

C. 存储数据。

D. 输入输出。

答案,A。

1. 计算机组成原理中,CPU的作用是进行数据处理和______。

答案,控制。

2. 内存是计算机中的______存储器。

答案,临时。

3. 计算机组成原理中,总线是连接各个部件的______。

答案,通信线路。

4. 控制单元的主要功能是______。

答案,控制数据传输和处理。

5. 计算机组成原理中,运算器负责进行______运算。

答案,算术和逻辑。

1. 简述计算机组成原理中的冯·诺依曼结构。

答,冯·诺依曼结构是一种计算机体系结构,主要包括存储器、运算器、控制器、输入设备和输出设备等五大部分。

其中存储器用于存储数据和指令,运算器用于进行算术和逻辑运算,控制器用于控制数据传输和处理,输入设备用于接收数据输入,输出设备用于显示处理结果。

2. 什么是指令周期?它与时钟周期有什么关系?答,指令周期是指计算机执行一条指令所需的时间,它包括取指令周期、执行周期和访存周期。

时钟周期是CPU中时钟脉冲的时间间隔,它决定了CPU的工作速度。

指令周期与时钟周期的关系在于,时钟周期是指令周期的基本单位,指令周期是由若干个时钟周期组成的。

四、综合题。

1. 简述计算机组成原理中的存储器层次结构。

答,计算机存储器层次结构包括寄存器、高速缓存、内存和外存等多个层次。

1.请说明指令周期、机器周期、时钟周期之间的关系。

2.请说明SRAM的组成结构,与SRAM相比,DRAM在电路组成上有什么不同之处?3.请说明程序查询方式与中断方式各自的特点。

4.简要描述外设进行DMA操作的过程及DMA方式的主要优点。

5.什么是闪速存储器?它有那些特点?6.集中式仲裁有几种方式?画出计数器定时查询方式的逻辑结构图,说明其工作原理。

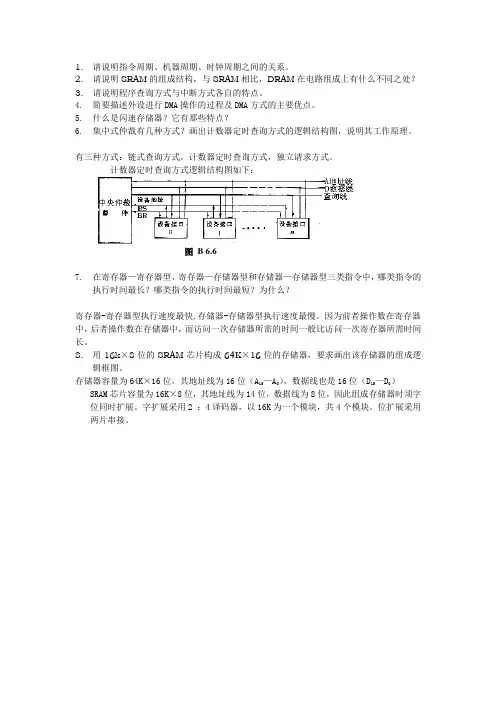

有三种方式:链式查询方式,计数器定时查询方式,独立请求方式。

计数器定时查询方式逻辑结构图如下:图B 6.67.在寄存器—寄存器型,寄存器—存储器型和存储器—存储器型三类指令中,哪类指令的执行时间最长?哪类指令的执行时间最短?为什么?寄存器-寄存器型执行速度最快,存储器-存储器型执行速度最慢。

因为前者操作数在寄存器中,后者操作数在存储器中,而访问一次存储器所需的时间一般比访问一次寄存器所需时间长。

8.用16k×8位的SRAM芯片构成64K×16位的存储器,要求画出该存储器的组成逻辑框图。

存储器容量为64K×16位,其地址线为16位(A15—A0),数据线也是16位(D15—D0)SRAM芯片容量为16K×8位,其地址线为14位,数据线为8位,因此组成存储器时须字位同时扩展。

字扩展采用2 :4译码器,以16K为一个模块,共4个模块。

位扩展采用两片串接。

图C1.19.提高存储器速度可采用哪些措施,请说出至少五种措施。

措施有:采用高速器件,采用cache (高速缓冲存储器),采用多体交叉存储器,采用用双端口存储器,采用相联存储器,加长存储器的字长。

10.若机器字长36位,采用三地址格式访存指令,共完成54种操作,操作数可在1K地址范围内寻找,画出该机器的指令格式。

操作码需用6位,操作数地址码需用10位。

格式如下6 10 10 10OP D1 D2 D3OP:操作码6位D1:第一操作数地址,10位D2:第二操作数地址,10位D3:第三操作数地址,10位11.举例说明存储器堆栈的原理及入栈、出栈的过程。

计算机组成原理复习题(含答案)计算机组成原理复习题⼀、选择题:1.双字节⼀般指(C )⼆进制数。

A.1位B.32位C.16位D.8位2.在主机中,能对指令进⾏译码的器件是(D )。

A.存储器B.ALU C.运算器D.控制器3.若⼀个数的编码是10000000,它的真值是-127,则该编码是(D )。

A.原码B.移码C.补码D.反码4.在I/O控制⽅式中,主要由程序实现的是(C )。

A.PPU⽅式B.DMA⽅式C.中断⽅式D.通道⽅式5.在浮点数的表⽰范围中,(B )在机器数中不出现,是隐含的。

A.阶码B.基数C.尾数D.符号6.指令系统采⽤不同的寻址⽅式的主要⽬的是( D )。

A.提⾼访问速度B.简化指令译码电路C.增加内存容量D.扩⼤寻址范围7.若标志寄存器Z=1 ,表明(C )A.运算结果为负B.运算结果为1 C.运算结果为0 D.运算结果为正8.寄存器间接寻址⽅式中,操作数在(B )中。

A.寄存器B.存储器C.堆栈D.CPU9.DMA接⼝(B )。

A.可以⽤于主存与主存之间的数据交换 B.内有中断机制C.内有中断机制,可以处理异常情况 D.内⽆中断机制10.计算机主频的周期是指(A )A.时钟周期B.指令周期C.⼯作周期D.存取周期11.运算器是由多种部件组成的,其核⼼部件是(D )。

A.数据寄存器B.累加器C.多数转换器 D. 算术逻辑运算单元12.使CPU与I/O设备完全并⾏⼯作⽅式是(C )⽅式。

A.程序直接传送B.中断C.通道D.程序查询13.某计算机字长32位,存储容量为64KB,若按照字节编址,它的寻址范围是(B )A.8K B.16K C.32K D. 4K 14.⽬前我们所说的个⼈台式商⽤机属于( D )。

A.巨型机 B.中型机 C.⼩型机 D.微型机15.冯·诺依曼机⼯作⽅式的基本特点是( B )。

A.多指令流单数据流 B.按地址访问并顺序执⾏指令C.堆栈操作 D.存储器按内容选择地址16.CPU的组成中不包含( A )。

计算机组成原理试题及答案全套第一部分:选择题1.下列关于计算机内存的说法,错误的是:A.内存是计算机的主要存储器件之一B.内存是临时存储器件,供程序运行时使用C.内存容量越大,计算机的性能越强D.内存分为主存和辅存,主存速度较快,但容量相对较小答案:C2.下列关于CPU的说法,错误的是:A.CPU是计算机的核心部件,负责执行指令和控制计算机的运行B.CPU由运算器、控制器和寄存器组成C.CPU的速度越快,计算机的运行速度越快D.CPU的主频越高,计算机的运行速度越慢答案:D3.下列关于指令周期的说法,错误的是:A.指令周期是CPU执行一条指令所需的时间B.指令周期包括取指令、译码、执行、访存四个阶段C.指令周期的长度取决于CPU的主频D.指令周期越短,CPU的执行效率越高答案:D4.下列关于存储器层次结构的说法,错误的是:A.存储器层次结构分为寄存器、高速缓存、主存和辅存B.存储器层次结构越高,存取速度越快,容量越小C.高速缓存是位于CPU和主存之间的高速存储器D.存储器层次结构的设计目标是在速度、容量和成本之间取得平衡答案:B5.下列哪项措施可以提高计算机系统的安全性?A.设置强密码B.定期更新操作系统和应用程序补丁C.安装杀毒软件和防火墙D.以上都是答案:D6.下列关于计算机硬盘的说法,错误的是:A.硬盘是一种磁存储设备,用于长期存储数据B.硬盘的读写速度相对较慢,但容量较大C.硬盘的存储介质是固态闪存芯片D.硬盘采用磁道、扇区和柱面的方式来寻址数据答案:C第二部分:填空题1.计算机系统由________、软件和人员三部分组成。

答案:硬件2.CPU的两个主要功能是执行________和控制计算机的运行。

答案:指令3.存储器层次结构的设计目标是在速度、________和成本之间取得平衡。

答案:容量4.计算机的存储器分为________和辅存两部分。

答案:主存5.操作系统的主要功能包括________管理、文件管理和用户接口等。

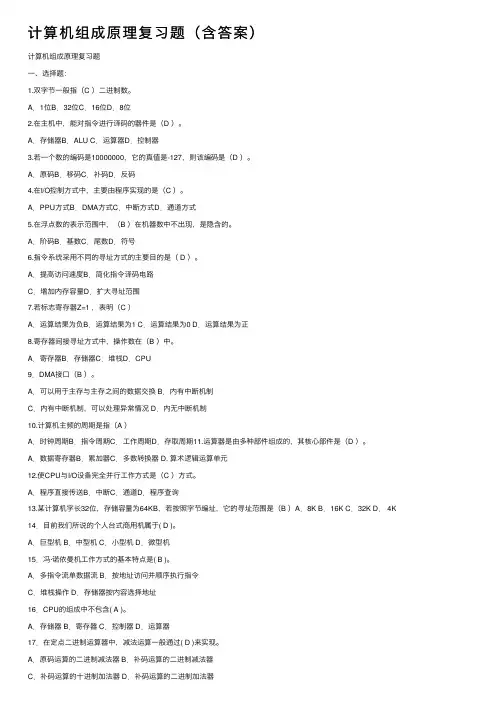

计算机组成原理期末典型例题1.CPU结构如图1所示,其中有一个累加寄存器AC,一个状态条件寄存器,各部分之间的连线表示数据通路,箭头表示信息传送方向。

1)标明图中四个寄存器的名称。

2)简述指令从主存取到控制器的数据通路。

3)简述数据在运算器和主存之间进行存 / 取访问的数据通路。

图1解:1)a为数据缓冲寄存器 DR ,b为指令寄存器 IR ,c为主存地址寄存器,d为程序计数器PC。

2)主存 M →缓冲寄存器 DR →指令寄存器 IR →操作控制器。

3)存贮器读:M →缓冲寄存器DR →ALU →AC4)存贮器写:AC →缓冲寄存器DR →M2. 某机器中,配有一个ROM芯片,地址空间0000H—3FFFH。

现在再用几个16K×8的芯片构成一个32K×8的RAM区域,使其地址空间为8000H—FFFFH。

假设此RAM 芯片有/CS和/WE信号控制端。

CPU地址总线为A15—A0,数据总线为D7—D0,控制信号为R//W,MREQ(存储器请求),当且仅当MREQ和R//W同时有效时,CPU 才能对有存储器进行读(或写)。

1)满足已知条件的存储器,画出地址码方案。

2)画出此CPU与上述ROM芯片和RAM芯片的连接图。

解:存储器地址空间分布如图1所示,分三组,每组16K×8位。

由此可得存储器方案要点如下:1)用两片16K*8 RAM芯片位进行串联连接,构成32K*8的RAM区域。

片内地址:A0 ——A13 ,片选地址为:A14——A15;2)译码使用2 :4 译码器;3)用 /MREQ 作为2 :4译码器使能控制端,该信号低电平(有效)时,译码器工作。

4)CPU的R / /W信号与RAM的/WE端连接,当R // W = 1时存储器执行读操作,当R // W = 0时,存储器执行写操作。

如图1图1CPU与芯片连接如图2:图2的ROM区域,现在用一3. 某机器中,已知配有一个地址空间为(0000—1FFF)16个SRAM芯片(8K×8位)形成一个16K×16位的ROM区域,起始地址为(2000)。

计算机组成原理复习题带答案第1章计算机系统概述⼀、选择题1、在下列四句话中,最能准确反映计算机主要功能的是 C。

A、计算机可以存储⼤量信息B、计算机能代替⼈的脑⼒劳动C、计算机是⼀种信息处理机D、计算机可实现⾼速运算2、1946年2⽉,在美国诞⽣了世界上第⼀台电⼦数字计算机,它的名字叫(1)C,1949年研制成功的世界上第⼀台存储程序式的计算机称为(2)。

(1)A、EDVAC B、EDSAC C、ENIAC D、UNIVAC-Ⅰ(2)A、EDVAC B、EDSAC C、ENIAC D、UNIVAC-Ⅰ3、计算机硬件能直接执⾏的只能是B。

A、符号语⾔B、机器语⾔C、汇编语⾔D、机器语⾔和汇编语⾔4、对计算机软、硬件资源进⾏管理,是 A 的功能。

A、操作系统B、数据库管理系统C、语⾔处理程序D、⽤户程序⼆、填空题1、计算机的各⼤部件通过____总线____________连接在⼀起,它是各部件之间传输信息的通道。

2、计算机按内部信息形式可以分为___模拟____________和___数字信号_两类。

3、计算机硬件⼀般由_运算器,控制器_______、__存储器______、_输⼊_______和、____输出____和五⼤部分组成。

4、运算器是⼀个数据加⼯部件,主要完成⼆进制___算术_______运算及__逻辑________运算。

5、运算器的___位数________越多,计算的精度就越⾼,但是所费的电⼦器件也越多,成本越⾼。

三、简答题1、简述计算机的发展过程。

1、第⼀代电⼦管计算机1946年2⽉,诞⽣了世界上第⼀台电⼦数字计算机——ENIAC ,1949年研制成功的世界上第⼀台存储程序式的计算机EDSAC。

2、第⼆代晶体管计算机1947年在贝尔实验室制成第⼀个晶体管,进⼊20世纪50年代全球出现⼀场以晶体管代替电⼦管的⾰命。

3、第三代集成电路计算机4、⼤规模集成电路计算机5、超⼤规模集成电路计算机3、冯.诺依曼计算机的特点是什么?它包括哪些主要组成部分?各部分的功能是什么?1、计算机由运算器、存储器、控制器、输⼊设备和输出设备五⼤部件组成2、指令和数据以同等的地位存放在存储器内,并可以按地址寻访3、指令和数据均⽤⼆进制数表⽰4、指令由操作码和地址组成。

计算机组成原理试题及答案一、选择题(每题2分,共20分)1. 计算机系统由哪两大部分组成?A. 硬件系统和软件系统B. 中央处理器和外部设备C. 存储器和输入/输出设备D. 运算器和控制器答案:A2. 下列哪个寄存器用于存储指令?A. 程序计数器B. 指令寄存器C. 状态寄存器D. 数据寄存器答案:B3. 下列哪种总线用于连接CPU和内存?A. 数据总线B. 地址总线C. 控制总线D. 外部总线答案:B4. 在计算机系统中,下列哪个设备用于实现数据的输入和输出?A. CPUB. 内存C. 硬盘D. 输入/输出设备答案:D5. 下列哪种存储器属于易失性存储器?A. RAMB. ROMC. 硬盘D. U盘答案:A6. 在计算机中,下列哪种操作称为中断?A. CPU执行指令的过程B. CPU响应外部设备请求的过程C. CPU执行系统调用的过程D. CPU进行输入/输出操作的过程答案:B7. 下列哪种计算机体系结构采用精简指令集?A. CISCB. RISCC. VLIWD. SIMD答案:B8. 在计算机中,下列哪种设备用于实现数据的高速缓存?A. L1缓存B. L2缓存C. 硬盘D. 内存答案:A9. 下列哪种计算机总线标准用于连接显卡?A. PCIB. AGPC. PCI-ED. USB答案:C10. 在计算机系统中,下列哪种设备用于存储大量数据?A. 内存B. 硬盘C. U盘D. 光盘答案:B二、填空题(每题2分,共20分)1. 计算机硬件系统包括________、________和________三大部件。

答案:中央处理器、内存、外部设备2. 计算机的运算器主要包括________和________两部分。

答案:算术逻辑单元、寄存器组3. 计算机的控制器主要包括________、________和________三部分。

答案:指令寄存器、程序计数器、指令译码器4. 计算机的输入/输出设备主要包括________、________、________和________等。

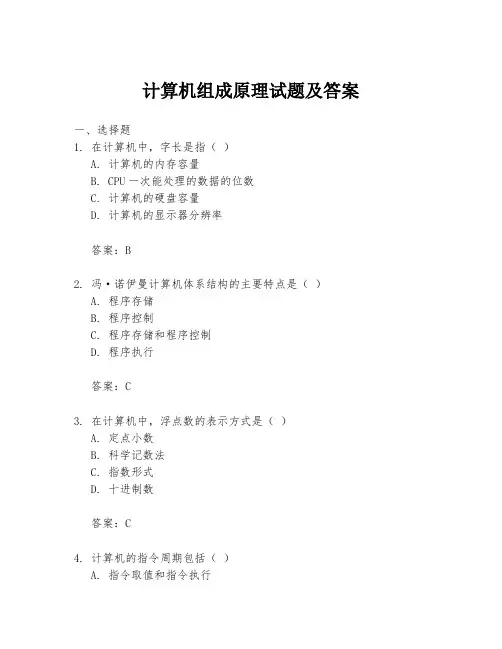

计算机组成原理试题及答案一、选择题1. 在计算机中,字长是指()A. 计算机的内存容量B. CPU一次能处理的数据的位数C. 计算机的硬盘容量D. 计算机的显示器分辨率答案:B2. 冯·诺伊曼计算机体系结构的主要特点是()A. 程序存储B. 程序控制C. 程序存储和程序控制D. 程序执行答案:C3. 在计算机中,浮点数的表示方式是()A. 定点小数B. 科学记数法C. 指数形式D. 十进制数答案:C4. 计算机的指令周期包括()A. 指令取值和指令执行B. 数据取值和数据执行C. 指令取值、数据取值和指令执行D. 指令执行和数据执行答案:A5. 在计算机系统中,主存储器的主要作用是()A. 长期存储数据和程序B. 临时存储数据和程序C. 长期存储操作系统D. 临时存储操作系统答案:B二、填空题1. 计算机的中央处理器(CPU)主要由________和________组成。

答案:算术逻辑单元(ALU);控制单元(CU)2. 在计算机系统中,________是用于暂时存储指令和数据的存储器。

答案:寄存器3. 计算机的存储系统通常包括主存储器和________。

答案:辅助存储器4. 计算机的输入设备包括键盘、鼠标等,而输出设备包括显示器、打印机等。

其中,________是计算机最基本的输入设备。

答案:键盘5. 在计算机中,指令的执行通常分为取指、分析和________三个阶段。

答案:执行三、简答题1. 简述计算机的五大基本组成部件。

答案:计算机的五大基本组成部件包括:输入设备、输出设备、存储器、中央处理器(CPU)和总线。

2. 解释什么是指令流水线,并简述其优缺点。

答案:指令流水线是一种在计算机中用于提高指令执行效率的技术,它将指令的执行过程分解为多个阶段,每个阶段可以并行处理不同的指令。

优点包括提高指令执行速度和CPU利用率;缺点包括资源冲突、流水线冒险等。

四、计算题1. 假设一个计算机的字长为32位,计算其最大正整数的值。

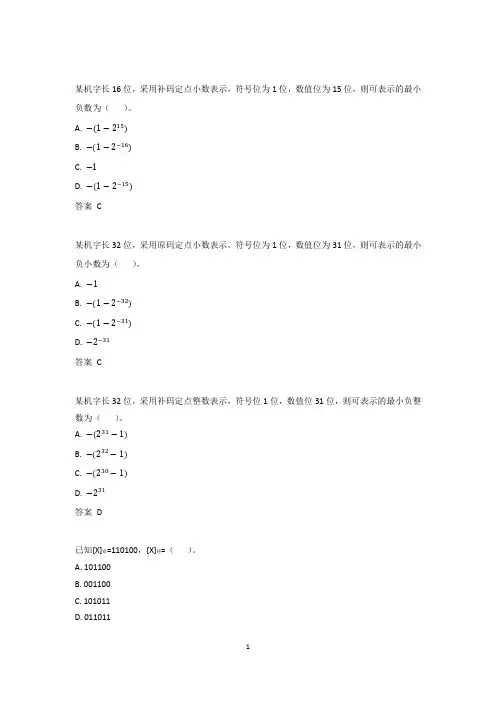

某机字长16位,采用补码定点小数表示,符号位为1位,数值位为15位,则可表示的最小负数为()。

A. −(1−215)B. −(1−2−16)C. −1D. −(1−2−15)答案C某机字长32位,采用原码定点小数表示,符号位为1位,数值位为31位,则可表示的最小负小数为()。

A. −1B. −(1−2−32)C. −(1−2−31)D. −2−31答案C某机字长32位,采用补码定点整数表示,符号位1位,数值位31位,则可表示的最小负整数为()。

A. −(231−1)B. −(232−1)C. −(230−1)D. −231答案D已知[X]原=110100,[X]移=()。

A. 101100B. 001100C. 101011D. 011011答案B下列数中最大的数是()。

A. (101001)2B. (52)8C. (00111001)BCDD. (2C)16答案D下列数中最小的数是()。

A. (101001)2B. (52)8C. (00111001)BCDD. (101)16答案C两个补码数相减,只有在符号位()时有可能产生溢出。

A. 相同B. 不同C. 都是0D. 都是1答案B下列说法正确的是()。

A. 采用双符号位补码进行加减运算可以避免溢出B. 只有定点数运算才有可能溢出,浮点数运算不会产生溢出C. 只有将两个正数相加时才有可能产生溢出D. 只有带符号数的运算才有可能产生溢出答案D浮点数的数值精度取决于()。

A. 阶码的位数B. 尾数的位数C. 阶码采用的编码D. 尾数采用的编码答案B长度相同但格式不同的2种浮点数,假设前者阶码长、尾数短,后者阶码短、尾数长,其他规定均相同,则下列选项中()是正确的。

A. 两者可表示的数的范围和精度相同B. 前者可表示的数的范围大且精度高C. 后者可表示的数的范围小但精度高D. 前者可表示的数的范围小且精度高答案C关于移码,下列选项中()是错误的。

A. 对于同一个数值,移码和补码数值位相同,符号位相反B. 移码的符号位0表示负数,1表示正数C. 移码既可以表示整数,也能表示小数D. 移码不能用于浮点数的尾数部分答案C定点运算器用来进行()。

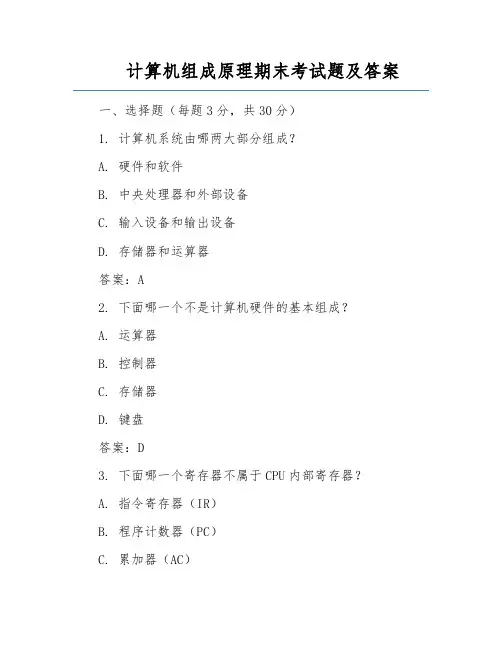

计算机组成原理期末考试题及答案一、选择题(每题3分,共30分)1. 计算机系统由哪两大部分组成?A. 硬件和软件B. 中央处理器和外部设备C. 输入设备和输出设备D. 存储器和运算器答案:A2. 下面哪一个不是计算机硬件的基本组成?A. 运算器B. 控制器C. 存储器D. 键盘答案:D3. 下面哪一个寄存器不属于CPU内部寄存器?A. 指令寄存器(IR)B. 程序计数器(PC)C. 累加器(AC)D. 磁盘地址寄存器(MAR)答案:D4. 下面哪一个不是计算机的性能指标?A. 字长B. 主频C. 内存容量D. 操作系统答案:D5. 下面哪一个不是计算机的总线类型?A. 数据总线B. 地址总线C. 控制总线D. 信号总线答案:D6. 下面哪一个不是存储器的层次结构?A. 缓存(Cache)B. 主存储器(RAM)C. 辅助存储器(硬盘)D. 寄存器答案:D7. 下面哪一个不是计算机的输入设备?A. 键盘B. 鼠标C. 扫描仪D. 打印机答案:D8. 下面哪一个不是计算机的输出设备?A. 显示器B. 打印机C. 扬声器D. 键盘答案:D9. 下面哪一个不是计算机的总线标准?A. PCIB. USBC. SATAD. HTTP答案:D10. 下面哪一个不是计算机的指令类型?A. 数据传送指令B. 运算指令C. 控制指令D. 通信指令答案:D二、填空题(每题3分,共30分)1. 计算机硬件系统主要包括五大部件,分别是________、________、________、________和________。

答案:控制器、运算器、存储器、输入设备、输出设备2. 计算机的运算器主要由________、________和________组成。

答案:算术逻辑单元(ALU)、累加器(AC)、寄存器3. 计算机的指令系统主要包括________、________和________三种类型的指令。

答案:数据传送指令、运算指令、控制指令4. 计算机的存储器层次结构包括________、________和________。

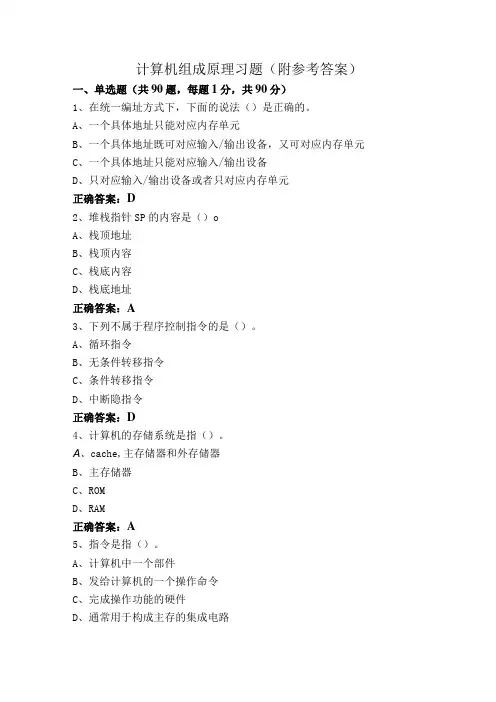

计算机组成原理习题(附参考答案)一、单选题(共90题,每题1分,共90分)1、在统一编址方式下,下面的说法()是正确的。

A、一个具体地址只能对应内存单元B、一个具体地址既可对应输入/输出设备,又可对应内存单元C、一个具体地址只能对应输入/输出设备D、只对应输入/输出设备或者只对应内存单元正确答案:D2、堆栈指针SP的内容是()oA、栈顶地址B、栈顶内容C、栈底内容D、栈底地址正确答案:A3、下列不属于程序控制指令的是()。

A、循环指令B、无条件转移指令C、条件转移指令D、中断隐指令正确答案:D4、计算机的存储系统是指()。

A、cache,主存储器和外存储器B、主存储器C、ROMD、RAM正确答案:A5、指令是指()。

A、计算机中一个部件B、发给计算机的一个操作命令C、完成操作功能的硬件D、通常用于构成主存的集成电路正确答案:B6、相对于微程序控制器,组合逻辑控制器的特点是()。

A、指令执行速度慢,指令功能的修改和扩展容易B、指令执行速度慢,指令功能的修改和扩展难C、指令执行速度快,指令功能的修改和扩展容易D、指令执行速度快,指令功能的修改和扩展难正确答案:D7、中断向量可提供()。

A、主程序的断点地址B、传送数据的起始地址C、被选中设备的地址D、中断服务程序入口地址正确答案:D8、迄今为止,计算机中的所有信息仍以二进制方式表示的理由是()oA、信息处理方便B、物理器件性能所致C、运算速度快D、节约元件正确答案:B9、相联存储器是按()进行寻址的存储器。

A、内容指定方式B、地址指定与堆栈存取方式结合C、堆栈存取方式D、地址指定方式正确答案:A10、若SRAM芯片的容量是2MX8位,则该芯片引脚中地址线和数据线的数目之和是()。

A、29B、21C、18D、不可估计正确答案:A11、若X=I03,尸-25,则下列表达式采用8位定点补码运算实现时,会发生溢出的是()oA^ x+yB、-x+yC> -χ-yD^ χ-y正确答案:D12、系统总线是指()oA、CPU、主存和外围设备之间的信息传送线B、运算器、寄存器和主存之间的信息传送线C、运算器、控制器和寄存器之间的信息传送D、运算器、寄存器和外围设备之间的信息传送线正确答案:A13、CPU可直接编程访问的存储器是()。

一、填空、选择或判断1.多核处理机是空间并行计算机,它有___多__个CPU。

2.计算机的发展大致经历了五代变化,其中第四代是1972-1990 年的_大规模和超大规模集成电路______计算机为代表。

3.计算机从第三代起,与IC电路集成度技术的发展密切相关。

描述这种关系的是_摩尔__定律。

4.1971年,英特尔公司开发出世界上第一片4位微处理器__Intel 4004_____。

首次将CPU的所有元件都放入同一块芯片之内。

5.1978年,英特尔公司开发的___Intel 8086_______是世界上第1片通用16位微处理器,可寻址存储器是_1MB______。

6.至今为止,计算机中的所有信息仍以二进制方式表示的理由是__物理器件性能所致___。

7.冯。

诺依曼计算机工作方式的基本特点是__按地址访问并顺序执行指令_____。

8.20世纪50年代,为了发挥__硬件设备_____的效率,提出了_多道程序___技术,从而发展了操作系统,通过它对__硬软资源______进行管理和调度。

9.计算机硬件能直接执行的只有__机器语言_________ 。

10.完整的计算机系统应包括__配套的硬件设备和软件系统______。

11.计算机的硬件是有形的电子器件构成,它包括_运算器__、_控制器_、_存储器__、_适配器_、_系统总线__、__外部设备__。

12.当前的中央处理机包括__运算器_____、_控制器_____、__存储器_____。

13.计算机的软件通常分为__系统软件_______和___应用软件_____两大类。

14.用来管理计算机系统的资源并调度用户的作业程序的软件称为__操作系统_____,负责将_高级____-语言的源程序翻译成目标程序的软件称为___编译系统____。

15.计算机系统中的存储器分为__内存____和__外存______。

在CPU执行程序时,必须将指令存放在__内存______中。

1 下列数中最小的数为__A___。

A.(101001) 2 B. (52) 8C.(2B) 162.下列数中最大的数为__B__ 。

A.(10010101) 2B.(227) 8C.(96) 163.设寄存器位数为8位,机器数采用补码形式(含1位符号位)。

对应于十进制数-27,寄存器内容为___C__。

A.27H B.9BH C.E5H4.对真值0表示形式唯一的机器数是__B__。

A.原码B.补码和移码C.反码D.以上都不对6.在整数定点机中,下述说法正确的是__B___。

A.原码和反码不能表示-1,补码可以表示-1B.三种机器数均可表示-1C.三种机器数均可表示-1,且三种机器数的表示范围相同7. 在小数定点机中,下述说法正确的是___A__。

A.只有补码能表示-1B.只有原码不能表示-1C.三种机器数均不能表示-18.某机字长8位.采用补码形式(其中1位为符号位),则机器数所能表示的范围是__C__。

A.-127~ +127 B.-128 ~ 128 C. -128 ~ +1279. 用n+1位字长表示定点数(其中1位为符号位),它所能表示的整数范围是 A ,它所能表示的小数范围是 D 。

A.0≤|N| ≤2n-l B.0≤|N| ≤2n+1 -lC. 0≤|N| ≤1- 2-(n+l)D. 0≤|N| ≤1-2-n10. 32位字长的浮点数,其中阶码8位(含1位阶符),尾数24位(含1位数符),则其对应的最大正数为 A ,最小负数为 B ,最小的绝对值为 F ;若机器数采用补码表示,且尾数为规格化形式,则对应的最大正数为 A ,最小正数为 C ,最小负数为 D 。

A.2127(1-2-23) B.-2127(1-2-23) C.2-129D.-2+127 E. 2-128×2-23 F. 2-127×2-2311.16位长的浮点数,其中阶码7位(含1位阶符),尾数9位(含1位数符),当浮点数采用原码表示时,所能表示的数的范围是 D ;当采用补码表示时,所能表示的数的范围是B 。

计算机组成原理期末考试试题及答案一、选择题(每题2分,共20分)1. 计算机系统由哪两部分组成?A. 硬件和软件B. 输入和输出设备C. 中央处理器和外部设备D. 存储器和输入输出设备答案:A2. 下面哪个寄存器用来存放指令?A. 累加寄存器B. 指令寄存器C. 程序计数器D. 状态寄存器答案:B3. 下面哪种总线用于连接CPU和内存?A. 数据总线B. 地址总线C. 控制总线D. 局部总线答案:B4. 下面哪个设备不属于输入设备?A. 键盘B. 鼠标C. 扫描仪D. 打印机答案:D5. 下面哪个设备不属于输出设备?A. 显示器B. 打印机C. 扬声器D. 键盘答案:D6. 下面哪个操作属于逻辑运算?A. 加法B. 减法C. 与运算D. 乘法答案:C7. 下面哪种存储器属于随机访问存储器?A. 硬盘B. U盘C. RAMD. ROM答案:C8. 下面哪个部件负责数据的输入输出操作?A. CPUB. 内存C. 硬盘D. I/O接口答案:D9. 下面哪个技术用于提高CPU的工作频率?A. 超线程B. 超频C. 虚拟化D. 多核答案:B10. 下面哪个总线标准用于连接CPU和外部设备?A. PCIB. USBC. IDED. SATA答案:A二、填空题(每题2分,共20分)1. 计算机的硬件系统主要包括五大部件:________、________、________、________和________。

答案:控制器、运算器、存储器、输入设备、输出设备2. 计算机指令通常由________和________两部分组成。

答案:操作码、操作数3. 在计算机中,数据总线的宽度决定了计算机的________。

答案:字长4. 计算机的存储器系统分为________和________两大部分。

答案:主存储器、辅助存储器5. I/O端口地址分为________和________两种。

答案:统一编址、独立编址三、判断题(每题2分,共20分)1. 计算机的性能主要取决于CPU的性能。

计算机组成原理68题(含答案)计算机组成原理复习题一.单项选择题1.计算机中的主机包含( A )。

A.运算器、控制器、存储器B.运算器、控制器、外存储器C.控制器、内存储器、外存储器D.运算器、内存储器、外存储器2.二进制数10010010,相应的十进制数是( B )(1*2^7+1*2^5+1*2^1=128+16+2=146)A.136B.146C.145D.1443.要使8位寄存器A 中高4位变0,低4位不变,可使用( A )。

(逻辑乘)A. A ∧0FH → AB.A ∨0FH →AC. A ∧F0H → AD. A ∨F0H →A4.在计算机内部用于汉字存储处理的代码是( B )A.汉字输入码B.汉字内码C.汉字字型码D.汉字交换码5.转移指令执行时,只要将转移地址送入( C.程序计数器 )中即可A.地址寄存器B.指令寄存器C.程序计数器D.变址寄存器6.设机器中存有代码10100011B ,若视为移码,它所代表的十进制数为( B.35 )。

A.-23B.35C.53 D-1137.将(-25.25)十进制数转换成浮点数规格化(用补码表示),其中阶符、阶码共4位,数符、尾数共8位,其结果为( B.0101,10011011 )A .0011,10010100 B.0101,10011011 C.0011,1110D.0101,11001018.(2000)10化成十六进制数是( B.(7D0)16 )。

A .(7CD )16 B.(7D0)16 C.(7E0)16 D.(7FO )169. 下列数中最大的数是((10011001)2 =153 )。

A .(10011001)2 B.(227)8 C 。

(98)16 D.(152)1010. ( D. 移码)表示法主要用于表示浮点数中的阶码。

A. 原码B. 补码C. 反码D. 移码11. 在小型或微型计算机里,普遍采用的字符编码是(D. ASC Ⅱ码)。

计算机构成原理复习题一、选择题:1.双字节一般指( C )二进制数。

A.1位B.32位C.16位D.8 位2. 在主机中,能对指令进行译码的器件是(D)。

A .储存器B. ALU C.运算器D.控制器3. 若一个数的编码是10000000,它的真值是-127 ,则该编码是(D)。

A .原码B.移码C.补码D.反码4. 在 I/O 控制方式中,主要由程序实现的是(C)。

A . PPU方式B. DMA方式C.中止方式D.通道方式5.在浮点数的表示范围中,(B )在机器数中不出现,是隐含的。

A .阶码B.基数C.尾数D.符号6. 指令系统采纳不一样的寻址方式的主要目的是( D )。

A.提升接见速度B.简化指令译码电路C.增添内存容量D.扩大寻址范围7.若标记寄存器 Z=1 ,表示( C )A .运算结果为负B.运算结果为 1 C .运算结果为0D.运算结果为正8. 寄存器间接寻址方式中,操作数在(B)中。

A.寄存器B.储存器C.货仓D.CPU9. DMA接口( B)。

A .能够用于主存与主存之间的数据互换B.内有中止体制C.内有中止体制,能够办理异样状况D.内无中止体制10.计算机主频的周期是指( A )A.时钟周期B.指令周期C.工作周期D.存取周期11. 运算器是由多种零件构成的,其核心零件是(D)。

A.数据寄存器B.累加器C.多半变换器 D.算术逻辑运算单元12.使 CPU与 I/O 设施完整并行工作方式是( C )方式。

A.程序直接传递B.中止C.通道D.程序查问13. 某计算机字长32 位,储存容量为64KB,若依据字节编址,它的寻址范围是(B)A. 8K B. 16K C. 32K D. 4K14.目前我们所说的个人台式商用机属于( D A.巨型机B.中型机C.小型机) 。

D.微型机15.冯·诺依曼机工作方式的基本特色是( B)。

A.多指令流单数据流B.按地点接见并次序履行指令C.货仓操作D.储存器按内容选择地点16. CPU的构成中不包含 ( A)。

(完整版)计算机组成原理复习题及答案⼀.选择题1. 我国在__D____ 年研制成功了第⼀台电⼦数字计算机,第⼀台晶体管数字计算机于______ 年完成。

(答案错误)A.1946 1958 B.1950 1968 C.1958 1961 D.1959 19652. 32位微型计算机中乘除法部件位于__A____ 中。

A.CPU B.接⼝ C.控制器 D.专⽤芯⽚3. 没有外存储器的计算机监控程序可以放在___B___ 。

A.RAM B.ROM C.RAM和ROM D.CPU4. 下列数中最⼩的数是__A____ 。

A.(101001)2 B.(52)8 C.(2B)16 D.(44)105. 在机器数___B.C___ 中,零的表⽰形式是唯⼀的。

A.原码B.补码C.移码 D.反码6. 在定点⼆进制运算器中,减法运算⼀般通过___D___ 来实现。

A.原码运算的⼆进制减法器 B.补码运算的⼆进制减法器C.补码运算的⼗进制加法器 D.补码运算的⼆进制加法器7. 下列有关运算器的描述中___C___ 是正确的。

A.只作算术运算,不作逻辑运算 B.只作加法C.能暂时存放运算结果 D.以上答案都不对8. 某DRAM芯⽚,其存储容量为512K×8位,该芯⽚的地址线和数据线数⽬为___D___ 。

A.8,512 B.512,8 C.18,8 D。

19,89. 相联存储器是按___C___ 进⾏寻址的存储器。

A.地址指定⽅式 B.堆栈存取⽅式C.内容指定⽅式 D。

地址指定与堆栈存取⽅式结合10. 指令系统中采⽤不同寻址⽅式的⽬的主要是___B___ 。

A.实现存储程序和程序控制 B.缩短指令长度,扩⼤寻址空间,提⾼编程灵活性C.可以直接访问外存 D.提供扩展操作码的可能并降低指令译码难度11. 堆栈寻址⽅式中,设A为累加寄存器,SP为堆栈指⽰器,Msp为SP指⽰器的栈顶单元,如果操作的动作是:(A)→Msp,(SP)-1→SP,那么出栈操作的动作为:A.(Msp)→A,(SP)+1→SP B.(SP)+1→SP,(Msp)→AC.(SP)-1→SP,(Msp)→A D.(Msp)→A,(SP)-1→SP12. 在CPU中跟踪指令后继地址的寄存器是__B____ 。

《计算机组成原理》例题安康学院 成典勤第三章 系统总线例1.假设总线的时钟频率为33MHz ,且一个总线时针周期为一个总线传输周期。

若在一个总线传输周期可并行传送4个字节的数据,求该总线的带宽,并分析哪些因素影响总线的带宽。

解:总线的带宽是指单位时间内总线上可传输的数据位数,通常用每秒传送信息的字节数来衡量,单位可用MBps (兆字节每秒)表示。

由时针频率f=33MHz ,可得时钟周期T=1/f ,根据题目假设的条件,一个总线传输周期为一个时钟周期,且在一个总线传输周期传输4个字节数据,故总线带宽为)21(132103344/4206=≈⨯⨯=⨯=M MBps Hz B f B T B影响总线带宽的因素有:总线宽度、传输距离、总线发送和接收电路工作频率的限制以及数据传输形式等。

例2.在一个16位的总线系统中,若时针频率为100MHz ,总线传输周期为5个时钟周期,每一个总线传输周期可传送一个字,试计算总线的数据传输率。

解:根据时钟频率为100MHz ,得一个时钟周期为s MHz μ01.0)100/(1=数据传输率为Bps bps s b 6610401032005.0/16⨯=⨯=μ第四章 存储器例3.设CPU 共有16根地址线和8根数据线,并用MREQ 作为访存控制信号,WR 作为读/写命令信号(高电平读,低电平写)。

设计一个容量为32KB 、地址范围为0000H ~7FFFH 且采用低位交叉编址的四体并行存储器。

要求:(1)采用下图所列芯片,详细画出CPU 和存储芯片的连接图。

(2)指出图中每个存储芯片的容量及地址范围(用十六进制表示)。

解:32KB 四体结构的存储器可由4片88⨯K 位存储芯片组成,由于采用低位交叉编址,因此需用末两位地址1A 、0A 控制片选信号,用13根地址线14A ~2A 与存储芯片的地址线相连。

满足地址范围为0000H ~7FFFH 的存储器与CPU 的连接如图所示,图中各片存储芯片的地址范围是:第0片 0,4,…,7FFCH ;第1片 1,5,…,7FFDH ;第2片 2,6,…,7FFEH ;第3片 3,7,…,7FFFH ;例4.用一个8512⨯K 位的闪存存储芯片组成一个324⨯M 位的半导体只读存储器。

试回答:(1)该存储器的数据线数是多少?(2)该存储器的地址线数是多少?(3)共需几片这种存储芯片?(4)说明每根地址线的作用。

解:(1)对于324⨯M 位的存储器,数据线为32位。

(2)对于324⨯M 的的存储器,按字寻址的范围是222,按字节寻址的范围是242,故该存储器的地址线为24位23A ~0A(3)4片8512⨯K 位的闪存可组成32512⨯K 位的存储器,324⨯M 位的存储器共需32片8512⨯K 位的闪存。

(4)CPU 的24根地址线中,最低2位地址01A A 为字节地址,20A ~2A 这19根地址线与闪存的地址线相连,最高3位地址212223A A A 可通过3线---8线译码器形成片选信号。

每一个片选信号同时选中4片闪存,以满足32位的数据线要求。

例5.定量分析n 体低位交叉存储器连续读取n 个字所需的时间。

解:连续读取n 个字所需的时间为τ)1(-+n T ,如下图所示例6.设有8个模块组成的八体存储器结构,每个模块的存取周期为400ns ,存储字长为32位。

数据总线宽度为32位,总线传输周期为50ns ,试求顺序存储(高位交叉)和交叉存储(低位交叉)的存储器带宽。

解:八体存储器连续读出8个字的信息量为b b 256832=⨯顺序存储存储器连续读出8个字的时间是s ns ns 7103232008400-⨯==⨯ 交叉存储存储器连续读出8个字的时间是s ns ns ns 7105.775050)18(400-⨯==⨯-+高位交叉存储器的带宽是bps bps 77108)1032/(256⨯=⨯-低位交叉存储器的带宽是bps bps 771034)105.7/(256⨯=⨯-例7.假设CPU 执行某段程序时,共访问缓存命中3800次,访问主存200次,已知缓存存取周期为50ns ,主存存取周期为250ns 。

求缓存---主存系统的效率和平均访问时间。

解:(1)缓存的命中率为95.0)2003800/(3800=+(2)由题可知,访问主存的时间是访问缓存时间的5倍(250/50=5)设访问缓存的时间为t ,访问主存的时间为5t ,缓存---主存系统的效率为e ,则%3.83%1002.11%1005)95.01(95.0%100=⨯=⨯⨯-+⨯=⨯=t t t e 平均访存时间访问缓存的时间 (3)平均访问时间ns ns ns 60)95.01(25095.050=-⨯+⨯=例8.设某机主存容量为16MB ,缓存的容量为16KB 。

每字块有8个字,每个字32位。

设计一个四路组相联映射(即缓存每组内共有4个字块)的缓存组织,要求:(1)画出主存地址字段中各段的位数。

(2)设缓存初态为空,CPU 依次从主存第0、1、2、…、99号单元读出100个字(主存一次读出一个字),并重复此次序读8次,问命中率是多少?(3)若缓存的速度是主存速度的6倍,试问有缓存和无缓存相比,速度提高多少倍?解:(1)根据每个字块有8个字,每个字32位,得出主存地址字段中字块内地址字段为5位。

根据缓存容量为B KB 14216=,字块大小为52B ,得缓存共有92块,故c=9。

根据四路组相联映射42=r ,得2=r ,则7=-=r c q 。

根据主存容量为B MB 24216=,得出主存地址字段中主存字块标记位数为24-7-5=12主存地址字段各段格式如图所示:(2)由于每个字块中有8个字,而且初态缓存为空,因此CPU 读第0号单元时,未命中,必须访问主存,同时将该字所在的主存块调入缓存第0组中的任一块内,接着CPU 读1~7号单元时,均命中。

同理CPU 读第8、16、…、96号单元时均未命中。

可见CPU 在连续读100个字中共有13次未命中,而后7次循环读100个字全部命中,命中率为%375.98%1008100138100=⨯⨯-⨯ (3)根据题意,设主存存取周期为6t ,缓存的存取周期为t ,没有缓存的访问时间为8006⨯t ,有缓存的访问时间为136)13800(⨯+-t t ,则有缓存和没有缓存相比,速度提高倍数为5.41136)13800(8006≈-⨯+-⨯t t t例9.一个采用直接映射方式的16KB 缓存,假设块长为8个32位的字,试问地址为FDA459H 的主存单元在缓存中的什么位置(指出块号和块内地址,均用十进制表示)?解:根据缓存容量为16KB ,得出缓存的地址为14位。

由于每字32位,块长为8个字,则缓存的块内地址为5位(高3位为字地址,末2位为字节地址)。

地址为FDA459H 的主存单元,其二进制地址为1111 1101 1010 0100 0101 1001,对应缓存第10 0100 010(即十进制170)块中的第6个字的第1字节。

例10.假设缓存的工作速度为主存的5倍,缓存的命中率为90%,试问采用缓存后,存储器的性能提高多少?解:设主存的存取周期为m t ,则缓存的存取周期为m m t t 2.05/=,故平均访存时间为m m m t t t 28.010.090.02.0=⨯+⨯采用缓存后,存储器性能为原来的57.328.0/=m m t t 倍,即提高了2.57倍。

例11.已知缓存---主存系统的效率为85%,平均访问时间为60ns ,缓存比主存快4倍,求主存的存取周期和缓存的命中率。

解:设缓存---主存系统的效率为e 平均访问时间为a t ,缓存的取周期为c t ,命中率为h ,主存的存取周期为m t 。

根据%100⨯=a c t t e 得ns ns e t t a c 5185.060=⨯=⋅= 由于缓存比主存快4倍,则ns ns t t c m 255551)14(=⨯=+⨯=根据m c a t h ht t )1(-+=,其中ns t a 60=,ns t c 51=,ns t m 255=,得%6.95=h例12.设CPU 共有16根地址线,8根数据线,并用MREQ 作为访存控制信号(低电平有效),用WR 作为读/写控制信号(高电平读,低电平写)。

现有芯片及各种门电路(门电路自定),如下图所示。

画出CPU 与存储器的连接图,要求:(1)存储芯片地址空间分配:0~2047为系统程序区;2048~8191为用户程序区。

(2)指出选用的存储芯片类型及数量。

(3)详细画出片选逻辑。

解:根据主存地址空间分配,0~2047为系统程序区,选用1片2K×8位ROM 芯片;2048~8191为用户程序区,选用2K×8位RAM芯片,即存储芯片与CPU的连接如图所示。

例13.一个磁盘存储器共有6个盘片,假设最上、下两个面不可用,每面有204条磁道,每条磁道有12个扇段,每个扇段有512B,磁盘机以7200r/min速度旋转,平均定位(寻道)时间为8ms。

(1)计算该磁盘存储器的存储量。

(2)计算该磁盘存储器的平均寻址时间。

解:(1)6个盘片共有10个记录面,磁盘存储器的总容量为512B×12×204×10=12533760B(2)磁盘存储器的平均寻址时间=平均寻道时间+平均等待时间平均等待时间=[60s/(7200r/min)] ×0.5≈4.165ms平均寻址时间=8ms+4.165ms=12.165ms例14.一个磁盘组共有11片,假设最上、下两个面不用,每片有203道,数据传输率为983040Bps,磁盘组转速为3600r/min,假定每个记录块有1024B,且系统可挂16台这样的磁盘机,计算磁盘存储器的总容量并设计磁盘地址格式。

解:由于数据传输速率=每一磁道的容量×磁盘转速,且磁盘转速为3600r/min=60r/s,故每一磁道的容量=(983040Bps)/(60r/s)=16384B,扇段数=16384B/1024B=16。

表示磁盘地址格式的参数包括:台数为16,记录面为20,磁道数为203,扇段数为16,故磁盘地址格式如图所示。

Welcome To Download !!!欢迎您的下载,资料仅供参考!。