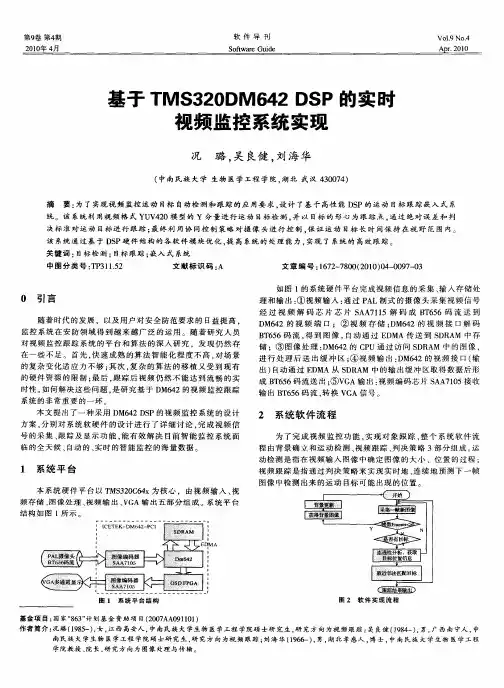

2DSP芯片(TMS320DM642)概述

- 格式:docx

- 大小:58.72 KB

- 文档页数:12

Blackfin561 VS TMS320DM642 全面比较德州仪器公司(Texas Instruments以下简称TI公司)和美国模拟器件公司(Analog Devices以下简称ADI公司),作为全球领先的高性能DSP供应商,它们几乎占据了全球DSP市场全部分额。

TMS320DM642(以下简称DM462)是TI公司近来发布的新一代多媒体处理器,它基于其第二代高性能的 VelociTI VLIW结构,适用于多种数字媒体应用,它的时钟频率为600MHz,指令速度高达4800MIPS。

而ADSP-BF561(以下简称BF561)处理器是ADI公司推出的Blackfin 系列中的高性能产品,主要针对于多媒体和通信方面的各种应用。

BF561的核心由两枚独立的Blackfin 处理器组成。

它集成了一套通用的数字图像处理外围设备,为数字图像处理和多媒体应用创建了一个完整的系统级片上解决方案。

下面我们将对TI公司的 TMS320DM642与ADI公司的Blackfin561做一些简要介绍和比较。

一、体系结构TMS320DM642与Blackfin561的体系结构的最大差别在于TMS320DM642是单核结构、而Blackfin561是双核结构,这就从整体上决定了它们之间的整个架构的不一致性。

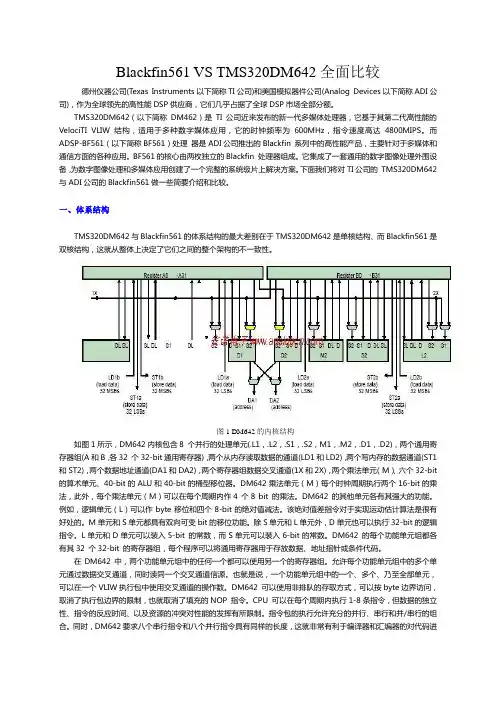

图1 DM642的内核结构如图1所示,DM642内核包含8 个并行的处理单元(.L1,.L2,.S1,.S2,M1,.M2,.D1,.D2),两个通用寄存器组(A和B,各32 个32-bit通用寄存器),两个从内存读取数据的通道(LD1和LD2),两个写内存的数据通道(ST1和ST2),两个数据地址通道(DA1和DA2),两个寄存器组数据交叉通道(1X和2X),两个乘法单元(M)、六个32-bit 的算术单元、40-bit的ALU和40-bit的桶型移位器。

DM642乘法单元(M)每个时钟周期执行两个16-bit的乘法,此外,每个乘法单元(M)可以在每个周期内作4 个8 bit 的乘法。

电子技术DM642嵌入式图像融合处理系统硬件设计研究郝雅婷,马立新(中国矿业大学,北京,100083)摘要:时代的进步使得嵌入式系统朝着更为智能的方向发展,DSP被人们广泛的应用到信号高速处理领域,特别是在图像处理加工领域能够为图像处理提供精准的数据支持。

为此,文章以图像融合硬件系统打造和技术实现为研究对象,将TMS320DM642芯片(以下简称DM642)作为核心处理器,就DM642嵌入式图像融合处理系统的架构、处理器内部配置、硬件设计问题进行探究。

关键词:DM642;嵌入式图像;融合处理系统;硬件设计在工业监督控制、机器视觉、医学影像处理领域会应用一些复杂的算法来进行多图像处理数据,基于这样的要求传统的图像处理系统很难满足系统处理要求。

文章面向实时图像处理,采用模块化的设计思想以新一代高性能多媒体专用DSP芯片DM642为核心,打造了体积小、能耗低、应用性强的嵌入式实时图像处理可拓展硬件平台。

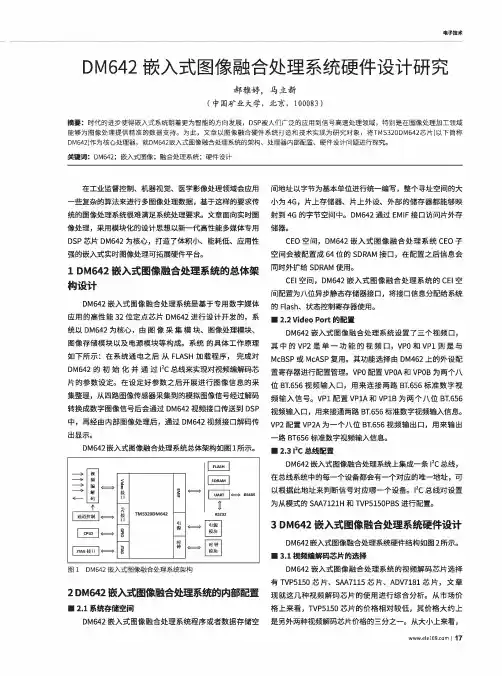

1DM642嵌入式图像融合处理系统的总体架构设计DM642嵌入式图像融合处理系统是基于专用数字媒体应用的高性能32位定点芯片DM642进行设计开发的,系统以DM642为核心,由图像采集模块、图像处理模块、图像存储模块以及电源模块等构成。

系统的具体工作原理如下所示:在系统通电之后从FLASH加载程序,完成对DM642的初始化并通过FC总线来实现对视频编解码芯片的参数设定。

在设定好参数之后开展进行图像信息的采集整理,从四路图像传感器采集到的模拟图像信号经过解码转换成数字图像信号后会通过DM642视频接口传送到DSP 中,再经由内部图像处理后,通过DM642视频接口解码传出显ZBoDM642嵌入式图像融合处理系统总体架构如图1所示。

图1DM642嵌入式图像融合处理系统架构2DM642嵌入式图像融合处理系统的内部配置■2.1系统存储空间DM642嵌入式图像融合处理系统程序或者数据存储空间地址以字节为基本单位进行统一编写,整个寻址空间的大小为4G,片上存储器、片上外设、外部的储存器都能够映射到4G的字节空间中。

基于TMS320DM642芯片的MPEG4SVP视频编码的实现摘要:本文在TI公司的TMS320DM642芯片上实现了MPEG4SVP 算法,并针对DSP硬件系统对算法进行了优化,实现了系统的实时性,可应用于实时视频监控以及远程视频图像传输等多方面。

关键词:视频编码MPEG4SVP DSP1 引言MPEG4标准为ISO于1994年开始制定,最初是为了满足视频会议等的需要,后来经过不断的发展成为一个可以适应于各种多媒体应用,提供各种编码比特率的标准。

与传统的基于像素的视频编码标准不同,MPEG4采用基于对象的视频编码方法,它不仅可以实现对视频图像的高效压缩,还可以提供基于内容的交互功能。

为了支持对多媒体内容的访问和操作,MPEG4标准引入了A/VO的概念,即音/视频对象。

在引入了A/VO对象概念的基础上,MPEG4能够对A/VO对象进行各种操作,增强了对象和用户之间的交互性。

MPEG4采用了基于对象的视频编码算法,把视频分割成各种不同的对象实体,分别进行处理,针对不同的对象进行比特流控制,并能实现多种基于对象的交互功能,有广泛的应用前景[1]。

其中MPEG4SVP是目前MPEG4各种档中应用最为广泛的一种。

我们在TMS320DM642芯片上实现了MPEG4SVP的实时压缩回放,可用于视频监控以及网络视频传输等多方面应用。

2 TMS320DM642芯片特性介绍TMS320DM642是TI公司最新推出的一款针对多媒体处理领域的DSP芯片,芯片内核采用先进的超长指令字(VLIW)结构,每个时钟周期最高可提供8条32位指令,具有高度的并行性和快速的运行能力。

芯片的时钟频率为600MHz,其最大处理能力可达到4800×106条指令/s。

由于具有6个并行的算术逻辑单元与两个并行的硬件乘法器,并利用先进的超长指令字结构,DM642芯片可以完成MPEG4中的DCT变换,运动估计与运动补偿等复杂运算。

为了提高处理器的存取速度,DM642芯片还提供了一些特别适用于视频处理的指令。

基于TMS320DM642和H.264的网络视频监控系统设计摘要h.264作为全新的视频压缩编码标准,虽然提高了编码的效率,却也同时提高了运算的复杂度。

因此,为了提高其适用性就要优化现有的h.264编制码。

对编码算法进行优化可以在保证图像质量的前提下降低运算的复杂度,而dsp具有处理能力强、软件编程简便等特点,所以在进行h.264编码器的设计中作为硬件平台的首选。

关键词 h.264;tms320dm642;视频监控中图分类号tp31 文献标识码a 文章编号 1674-6708(2011)47-0200-021 h.264与tms320dm642h.264与h.263相比,基于同样的质量,其数码率可以降低一半,即数码率相同其信器噪比则有大幅度的提高;但是其计算代码的复杂程度却是h.263的三倍左右,这也是广大用户的困扰所在。

以h.264标准所提供的参考代码为基础,很多用户对h.264涉及到的算法均进行了研究与改进,比如量化算法、运动估计算法以及帧间块模式抉择算法等等,尽管通过一定的改进降低了h.264某个小模块代码的运算复杂度,但是并未与自身硬件平台相结合而开发整个h.264代码。

因此视频应用的一个关键问题就是结合当前的硬件发展,使得h.264代码的复杂度有所降低,以更好的满足系统实时性的要求。

tms320dm642是ti公司所推出的一款高速dsp处理器芯片,它是专门针对多媒体应用而设计开发的,其最高工作主频可达720mhz,处理性能5760mips;它基于c64xdsp内核进一步集成了完备的多媒体接口,可以提供质量较高的视频编、解码的解决方案,因此适用于视频处理技术。

而tms320dm642为基础,构建一个视频编解码硬件平台,将h.264代码做dsp优化,使得代码的实现速度得到大幅度的提高。

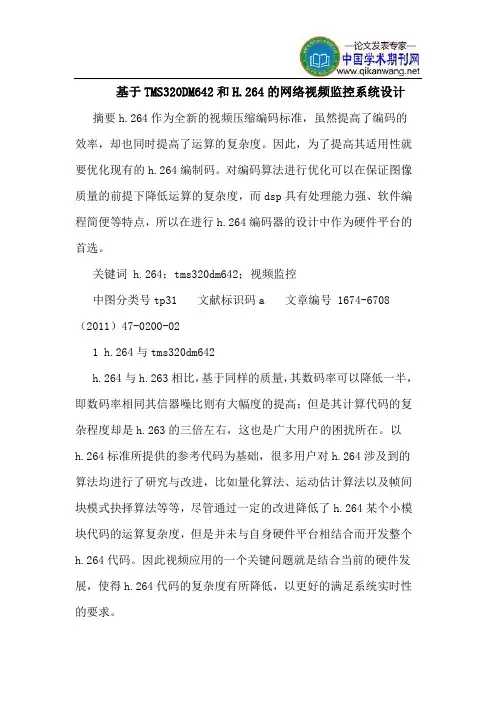

2 系统硬件平台tms320dm642为系统的核心处理器,其硬件平台结构图如下图1所示:基于该硬件平台,系统不仅可以压缩视频经过网络进行传输,还可以利用网络输入对视频进行解压然后将输出显示出来。

基于SPI的双DSP通信协议研究【摘要】提出了改进型SPI(Serial Peripheral interface,串行外围设备接口)协议,在标准SPI协议的基础上,增加了SPI从机主动发起通信的功能,并能指示数据/指令传输,设计了可靠的“帧”格式,帧带有序号和CRC校验,具有完善的出错重传机制。

基于该SPI接口协议,设计了TMS320DM642和TMS320C6747之间的SPI通信接口,给出了接口电路设计和工作流程,并应用到课题组设计的水声通信机中。

【关键词】SPI协议;双DSP通信;TMS320DM642;TMS320C67471.引言在水声通信机的设计中,经常是由一个处理器进行唤醒检测、AGC(自动增益控制)、A/D(模拟-数字转换)、D/A(数字-模拟转换)等工作。

另外一个处理器负责信号调制、解调、纠错编码/解码等复杂计算。

在我们的水声通信机设计中,前端采用低功耗的TMS320C6747浮点DSP,进行数据预处理;后端采用高性能的TMS320DM642定点DSP,进行复杂计算。

这就需要双DSP分工协作,共同完成系统整机的功能。

不可避免的,将涉及到双DSP之间大量的指令和数据交互操作。

我们希望采用灵活的架构,简洁的接口连线,简单的控制协议,实现高可靠和高效率的指令与数据双向传输,通过大量的实验,我们最终选择了SPI协议,并对典型的SPI协议进行了改进。

典型的水声通信机的架构如图1所示。

图1 典型水声通信机的架构在我们的设计中,“处理器A”选用了低功耗的TMS320C6747浮点DSP,“处理器B”选用了高性能的TMS320DM642定点DSP。

在实际系统中,根据水声通信机的不同工作频段和运算能力要求,处理器A也可选择FPGA/CPLD或者低功耗单片机;处理器B也可选择不同运算能力的DSP、ARM或者FPGA。

2.SPI协议SPI(Serial Peripheral Interface,串行外围设备接口)是Motorola公司于2000年提出的一种串行接口协议。

基于DM642的双路视频合成硬件系统摘要:DM642是TI公司推出的一款专门用于视频处理的DSP芯片,它是基于C6000系列的芯片,增加了很多外围设备和接口,具有高速运算能力,在多媒体领域得到了广泛应用。

本文主要分析和介绍了以DM642为核心的双路视频合成硬件系统的工作原理和主要功能模块。

关键词:视频合成DM642 功能模块1 视频合成技术视频合成技术是图像处理方面的一个重要应用,它将一个图像的多个状态或者多幅不同图像进行合成,来实现虚拟面板、图像叠加、模拟场景、图像优化等效果。

多路视频合成显示技术是将通过多个途径(如摄像机、PC机、网络等),采集而来的视频信号进行处理,并按照实际所需进行显示。

本硬件系统是双路视频合成系统,视频信号来源于摄像头。

2 系统工作原理如图1所示,从CCD摄像头得到的两路视频信号经过视频解码器解码,DM642通过I2C总线控制解码器的工作模式和工作状态,使解码器把视频信号解码为DM642可以处理的数据格式,然后两路视频信号分别从vp0、vp1两个视频端口输入到DM642中。

由DM642对两路视频信号进行处理,处理程序可由计算机通过JTAG口下载到FLASH 中。

采集到的视频数据通过EMIF用EDMA送到扩展出来的SDRAM 中,对数据进行存储。

因为DM642的两级缓存的空间不能满足大数据量的存取,它的空间不够,所以要先把视频数据存到SDRAM中,再对数据进行处理。

然后经过处理的视频数据通过vp2视频端口输出到视频编码器,DM642通过I2C总线控制编码器将视频信号编码为显示设备支持的数据格式。

最后系统将视频信号输出。

[1]3 系统结构双路视频合成硬件系统主要包括四个模块:视频采集模块、视频输出模块、DSP视频处理模块和FLASH模块。

视频采集模块主要用于对视频信号的解码,把解码后的数据送到DSP进行数据处理。

视频输出模块把经过DSP处理的数据编码输出到显示设备。

DSP视频处理模块是整个硬件系统的核心,它的主要工作是把经过解码的两路视频数据进行合成处理并送到视频输出模块等待输出。

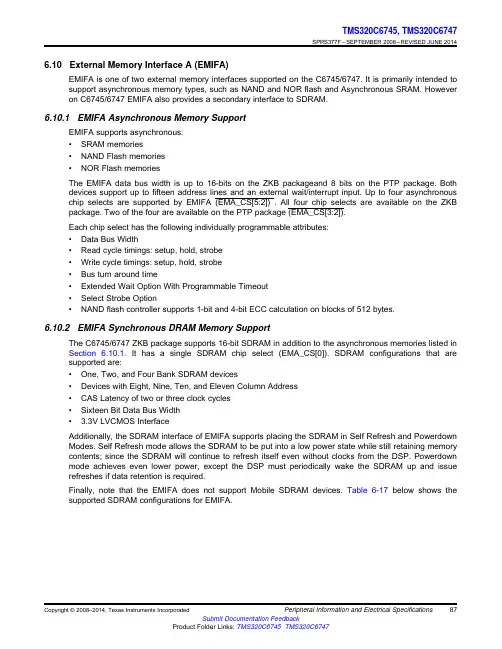

87TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated 6.10External Memory Interface A (EMIFA)EMIFA is one of two external memory interfaces supported on the C6745/6747.It is primarily intended to support asynchronous memory types,such as NAND and NOR flash and Asynchronous SRAM.However on C6745/6747EMIFA also provides a secondary interface to SDRAM.6.10.1EMIFA Asynchronous Memory SupportEMIFA supports asynchronous:•SRAM memories•NAND Flash memories•NOR Flash memoriesThe EMIFA data bus width is up to 16-bits on the ZKB packageand 8bits on the PTP package.Both devices support up to fifteen address lines and an external wait/interrupt input.Up to four asynchronous chip selects are supported by EMIFA (EMA_CS[5:2]).All four chip selects are available on the ZKB package.Two of the four are available on the PTP package (EMA_CS[3:2]).Each chip select has the following individually programmable attributes:•Data Bus Width•Read cycle timings:setup,hold,strobe•Write cycle timings:setup,hold,strobe•Bus turn around time•Extended Wait Option With Programmable Timeout•Select Strobe Option•NAND flash controller supports 1-bit and 4-bit ECC calculation on blocks of 512bytes.6.10.2EMIFA Synchronous DRAM Memory SupportThe C6745/6747ZKB package supports 16-bit SDRAM in addition to the asynchronous memories listed in Section 6.10.1.It has a single SDRAM chip select (EMA_CS[0]).SDRAM configurations that are supported are:•One,Two,and Four Bank SDRAM devices•Devices with Eight,Nine,Ten,and Eleven Column Address•CAS Latency of two or three clock cycles•Sixteen Bit Data Bus Width• 3.3V LVCMOS InterfaceAdditionally,the SDRAM interface of EMIFA supports placing the SDRAM in Self Refresh and Powerdown Modes.Self Refresh mode allows the SDRAM to be put into a low power state while still retaining memory contents;since the SDRAM will continue to refresh itself even without clocks from the DSP.Powerdown mode achieves even lower power,except the DSP must periodically wake the SDRAM up and issue refreshes if data retention is required.Finally,note that the EMIFA does not support Mobile SDRAM devices.Table 6-17below shows the supported SDRAM configurations for EMIFA.SDRAM Interface98TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical Specifications Copyright ©2008–2014,Texas Instruments Incorporated6.11External Memory Interface B (EMIFB)Figure 6-20illustrates a high-level view of the EMIFB and its connections within the device.Multiple requesters have access to EMIFB through a switched central resource (indicated as crossbar in the figure).The EMIFB implements a split transaction internal bus,allowing concurrence between reads and writes from the various requesters.Figure 6-20.EMIFB Functional Block DiagramEMIFB supports a 3.3V LVCMOS Interface.6.11.1EMIFB SDRAM Loading LimitationsEMIFB supports SDRAM up to 152MHz with up to two SDRAM or asynchronous memory loads.Additional loads will limit the SDRAM operation to lower speeds and the maximum speed should be confirmed by board simulation using IBIS models.。

8TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Overview Copyright ©2008–2014,Texas Instruments Incorporated3Device Overview3.1Device CharacteristicsTable 3-1provides an overview of the C6745/6747low power digital signal processor.The table shows significant features of the device,including the capacity of on-chip RAM,peripherals,and the package type with pin count.Table 3-1.Characteristics of the C6745/C6747ProcessorHARDWARE FEATURESC6745C6747PeripheralsNot all peripherals pinsare available at the same time (for moredetail,see the Device Configurations section).EMIFB16bit,up to 128MB SDRAM 16/32bit,up to 256MB SDRAM EMIFAAsynchronous (8-bit bus width)RAM,Flash,NOR,NAND Asynchronous (8/16-bit bus width)RAM,Flash,16bit up to 128MB SDRAM,NOR,NAND Flash Card InterfaceMMC and SD cards supported.EDMA332independent channels,8QDMA channels,2Transfer controllers Timers264-Bit General Purpose (each configurable as 2separate 32-bit timers,1configurable as Watch Dog)UART3(one with RTS and CTS flow control)SPI2(each with one hardware chip select)I 2C2(both Master/Slave)Multichannel AudioSerial Port [McASP]2(each with transmit/receive,FIFO buffer,16/9serializers)3(each with transmit/receive,FIFO buffer,16/9serializers)10/100Ethernet MAC with Management Data I/O 1(RMII Interface)eHRPWM 6Single Edge,6Dual Edge Symmetric,or 3Dual Edge Asymmetric Outputs eCAP 332-bit capture inputs or 332-bit auxiliary PWM outputs eQEP232-bit QEP channels with 4inputs/channel UHPI-1(16-bit multiplexed address/data)USB 2.0(USB0)Full Speed Host Or Device with On-Chip PHY High-Speed OTG Controller with on-chip OTG PHY USB 1.1(USB1)-Full-Speed OHCI (as host)with on-chip PHY General-PurposeInput/Output Port8banks of 16-bit LCD Controller-1RTC-1(32KHz oscillator and seperate power trail.Provides time and date tracking and alarm capability.)PRU Subsystem(PRUSS)2Programmable PRU Cores On-Chip Memory Size (Bytes)320KB RAM 448KB RAMOrganization DSP 32KB L1Program (L1P)/Cache (up to 32KB)32KB L1Data (L1D)/Cache (up to 32KB)256KB Unified Mapped RAM/Cache (L2)DSP Memories can be made accessible to EDMA3,and other peripherals.-ADDITIONAL MEMORY128KB RAMC674x CPU ID +CPU Rev ID Control Status Register (CSR.[31:16])0x1400C674x MegamoduleRevision Revision ID Register (MM_REVID[15:0])0x000051TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Overview Copyright ©2008–2014,Texas Instruments Incorporated Table 3-25.General Purpose Input Output Terminal Functions (continued)SIGNAL NAME PIN NOTYPE (1)PULL (2)MUXED DESCRIPTIONPTPZKB GP4USB0_DRVVBUS/GP4[15]-E4O IPD USB0GPIO Bank 4AMUTE1/EPWMTZ/GP4[14]132D4O IPD McASP1,eHRPWM0,eHRPWM1,eHRPWM2AFSR1/GP4[13]166L3I/O IPD McASP1ACLKR1/ECAP2/APWM2/GP4[12]165L2I/O IPD McASP1,eCAP2AHCLKR1/GP4[11]-L1I/O IPD McASP1AFSX1/EPWMSYNCI/EPWMSYNCO/GP4[10]163K4I/O IPD McASP1,eHRPWM0AXR1[9]/GP4[9]-M1I/O IPD McASP1AXR1[8]/EPWM1A/GP4[8]168M2I/O IPD McASP1,eHRPWM1A AXR1[7]/EPWM1B/GP4[7]169M3I/O IPD McASP1,eHRPWM1B AXR1[6]/EPWM2A/GP4[6]170M4I/O IPD McASP1,eHRPWM2A AXR1[5]/EPWM2B/GP4[5]171N1I/O IPD McASP1,eHRPWM2B AXR1[4]/EQEP1B/GP4[4]173N2I/O IPD McASP1,eQEP AXR1[3]/EQEP1A/GP4[3]174P1I/O IPD AXR1[2]/GP4[2]175P2I/O IPD McASP1AXR1[1]/GP4[1]176R2I/O IPD AXR1[0]/GP4[0]1T3I/O IPD GP5EMB_WE_DQM[0]/GP5[15]60K14O IPU EMIFB GPIOBank 5EMB_WE_DQM[1]/GP5[14]85C15O IPU SPI1_SCS[0]/UART2_TXD/GP5[13]8P4O IPU SPI1,UART2SPI1_ENA/UART2_RXD/GP5[12]7R4I IPU AXR1[11]/GP5[11]6T4I/O IPU McASP1AXR1[10]/GP5[10]4N3I/O IPU UART0_TXD/I2C0_SCL/TM64P0_OUT12/GP5[9]/BOOT[9]2R3I IPU UART0,I2C0,BOOT UART0_RXD/I2C0_SDA/TM64P0_IN12/GP5[8]/BOOT[8]3P3O IPU SPI1_CLK/EQEP1S/GP5[7]/BOOT[7]16T6I IPD SPI1,eQEP1,BOOT SPI1_SIMO[0]/I2C1_SDA/GP5[6]/BOOT[6]14N5I/O IPU SPI1,I2C1,BOOT SPI1_SOMI[0]/I2C1_SCL/GP5[5]/BOOT[5]13P5I/O IPU SPI0_SCS[0]/UART0_RTS/EQEP0B/GP5[4]/BOOT[4]9N4I IPU SPI0,UART0,eQEP0,BOOT SPI0_ENA/UART0_CTS/EQEP0A/GP5[3]/BOOT[3]12R5I IPU SPI0_CLK/EQEP1I/GP5[2]/BOOT[2]11T5I IPD SPI0,eQEP1,BOOT SPI0_SIMO[0]/EQEP0S/GP5[1]/BOOT[1]18P6I IPD SPI0,eQEP0,BOOT SPI0_SOMI[0]/EQEP0I/GP5[0]/BOOT[0]17R6I IPD。

深圳市奇想达科技有限公司 QXD-DM642开发板用户手册版本:3.2日期:2005-11版权声明深圳市奇想达科技有限公司保留随时对其产品修正、改进和完善的权利。

同时也保留在不作任何通告的情况下,终止其任何一款产品的供应和服务的权利,用户在下订单前应获取相关信息版权所有 © 2005 深圳市奇想达科技有限公司第一章 系统特色:※ 主处理器采用TMS320DM642 视频专用的DSP,运算能力达4800MIPS,指令周期为1.67ns;※ 提供四路视频采集接口,支持标准的NTSC/PAL制式的复合视频信号输入;※ 提供一路图像显示接口,可支持S_VIDEO、CVBS视频显示;※ 提供四路音频输入、四路音频输出;※ 提供音视频同步;※ 提供RTC实时时钟;※ 提供RS485/RS232通讯口,可连接标准RS485/RS232设备;※ DSP 片外拥有1~8M × 8位并行Flash Memory;※ 板上扩充32M BYTE的※ 支持33MPCI接口;※ 提供一路以太网接口,带宽※ 具有第二章 产品概述系统使用当前业界领先的运算和处理能力的高速处理器TMS320DM642 作为核心,具有强大的运算能力和高速的数据通道。

应用于如车牌识别,人像和虹膜/指纹识别,视频会议,远程监控,远程图像传输,语音分析,远程自动识别,远程现场处理,智能化小区监控,高速公路监控,图像算法研究等均具有其他处理器难以抗衡的效果。

其主要参数如下:1. 运算能力达4800MIPS,指令周期为1.67ns。

2. 每指令周期可并行执行8 条32 位的指令。

3. 具有增强型的VelocTI 结构,支持全面优化的超长指令字(VLIW)核心。

4. 支持字节和字(8/16/32/64位)的灵活寻址方式。

5. 先进的2 级缓存结构,L1 为16K+16K byte,L2 为256K Byte。

其中L2 缓存可灵活分配为CACHE模式或RAM 模式6. 支持大小Endian 模式7. 64 位的EMIF 接口,最大扩展能力达SRAM,FLASH等无缝连接。

前言《TMS320DM642中文手册》在DSP交流网()网友们的共同努力下,经过一个多月的翻译终于完成了,这是首次尝试,也是一次出色的合作。

此次翻译由网友亮亮发起,并全程负责,在这里对亮亮表示真诚的感谢和敬佩。

同时,非常感谢以下参与翻译的网友们:KaZE 虎妞Michael 碧鲨龙啸九天可可橘子Iceprince 田羽Steward Shayne ward 张焱翔Gaofeng_Q^_^ 风来的西林/$ JH DSP-F2812 方块糖流星~落梦另类爷们kelly 心中的天Embedded-A&D ☆星夜☆/yl 木头┳一人HELLODSP08-04-25DSP交流网联系方式:Email:hellodsp@QQ:778086555TMS320DM642中文手册第1章TMS320DM642 视频/图像定点数字信号处理器 (5)1.1特点(由亮亮翻译) (5)1.2概述(由亮亮翻译) (7)1.3原理框图(由亮亮翻译) (9)第2章器件纵览 (10)2.1器件特性(由亮亮翻译) (10)2.2C P U(D S P核)概述(由K a Z E翻译) (12)2.3存储器映射总结(由虎妞翻译) (18)2.4引导模式(由M i c h a e l翻译) (21)2.5引脚分配(由碧鲨翻译) (22)2.6T M S320D M642的发展(由龙啸九天翻译) (56)第3章器件配置 (59)3.1复位时的配置(由可可橘子翻译) (59)3.2复位后的配置(由l c e p r i n c e翻译) (62)3.3外设配置锁定(由虎妞翻译) (65)3.4器件状态寄存器描述(由田羽翻译) (67)3.5复用引脚配置(由S t e w a r d翻译) (69)3.6调试需要考虑的事项(由S h a y n e w a r d翻译) (71)3.7配置例子(由亮亮翻译) (72)第4章TMS320DM642运行状况 (75)4.1设备运行温度最大的额定值范围(由张焱翔翻译) (75)4.2推荐运行条件(由张焱翔翻译) (76)4.3超过推荐范围的电源电压和设备运行温度的电气特性(除非另有注明外)(由张焱翔翻译) (77)第5章DM642外设信息和电气特性 (79)5.1参数信息(由G a o f e n g_Q^_^翻译) (79)5.2推荐的时钟和控制信号转变行为(由K a Z E翻译) (82)5.3电源(由K a Z E翻译) (82)5.4增强的直接存取器访问(E D M A)控制器(由风来的西林/$翻译) (87)5.5中断(由J H翻译) (92)5.6复位(由J H翻译) (95)5.7时钟倍频P L L(由J H翻译) (100)5.8外部存取接口(E M I F)(由J H翻译) (106)5.9多声道音频串行端口( M c A S P0)外围设备(由D S P-F2812翻译) (121)5.10内部集成电路(I2C)(由方块糖翻译) (130)5.11主机接口(H P I)(由S t e w a r d翻译) (135)5.12外围部件互连标准(由流星~梦落翻译) (141)5.13多通道缓冲串口(M c B S P)(由亮亮翻译) (145)5.14视频端口(由另类爷们翻译) (156)5.15V I C(由K e l l y翻译) (164)5.16以太网媒体存取控制器 (E M A C)(由心中的天翻译) (166)5.17数据输入/输出管理(M D I O)(由l c e p r i n c e翻译) (174)5.18定时器(由E m b e d d e d-A&D翻译) (177)5.19通用输入/输出( G P I O)(由E m b e d d e d-A&D翻译) (179)5.20J T A G(由☆星夜☆/y l翻译) (182)第6章机械参数 (185)6.1热敏参数(由木头┳一人翻译) (185)6.2封装信息(由木头┳一人翻译) (187)第1章TMS320DM642 视频/图像定点数字信号处理器1.1特点l高性能数字媒体处理器-2-,1.67-,1.39-ns 指令周期-500-,600-,720-MHz时钟频率-每周期执行8条32位指令-与C64x完全兼容n V elociT1.2是具有先进超长指令字(VLIW)TMS320C64x DSP核V elociT的升级版-8个独立的功能单元n6个ALU(32/40bit),每个功能单元支持每时钟周期32位算术操作,双16位比特算术操作,或4个8位算术操作n2个乘法器支持每时钟周期4个16×16位的乘法(结果是32位)或者8个8×8位乘法(结果是16位)-具有无需阵列支持的负载存储结构(1)-64/32位通用寄存器-指令打包技术,减少代码容量l指令设置特点-字节寻址(8/16/32/64位数据)-8位溢出保护-可位提取,设置,清除操作-标准化,饱和度(1),位计数-增强交互的V elociT1.2l L1/L2存储器结构-128Kbit(16Kbyte)L1P程序缓存(直接映射)-128Kbit(16Kbyte)L1D数据缓存(2路结合设置)-2Mbit(256Kbyte)L2标准映射RAM/缓存(灵活的RAM/缓存分配)l小端模式,大端模式l64位外部存储器接口(EMIF)-支持异步存储器(SRAM和EPROM)和同步存储器(SDRAM,SBSRAM,ZBT SRAM 和FIFO)直接接口-总共1024Mbyte可寻址外部存储空间l增强的直接存储器访问(EDMA)控制器(64个独立的通道)l10/100Mb/s以太网控制器(EMAC)-适应IEEE802.3-媒体独立接口(MII)-8个独立的发送通道和1个接收通道l管理数据输入输出(MDIO)l3个可配置视频接口-给公共的视频编码解码器件提供一个直接I/F接口-支持多种协议/视频标准l内插VCXO控制接口-支持同步音频/视频l主机接口(HPI)[32/16位]l符合PCI接口规范2.2版本,32位/66MHz,3.3V PCI主/从接口l多通道音频串行接口(McASP)-8个串行数据引脚-多种I2S和相似的比特流格式-完整的数字音频I/F发送器,支持P/DIF, IEC60958-1, AES-3, CP-430格式l I2C总线l2个多通道缓存串行接口l3个32位通用定时器l16个通用输入输出(GPIO)引脚l灵活的PLL时钟发生器l支持IEEE-1149.1(JTAG)边界扫描接口l548引脚球栅阵列(BGA)封装(GDK和ZDK为后缀),0.8mm Ball Picth(1) l548引脚球栅阵列(BGA)封装(GNK和ZNK为后缀),1.0mm Ball Picth(1) l0.13μm/6等级CMOS工艺l I/O采用3.3V供电,内核采用1.2V供电(-500)l I/O采用3.3V供电,内核采用1.4V供电(A-500,A-600,-600,-720)注:红色标示的是翻译不确定的地方1.2概述TMS320C64x DSP芯片(包括TMS320DM642)是在TMS320C6000 DSP平台上的高性能定点DSP。

视频实时处理,由于视频处理中数据量大,要求速度快因此采用TM320DM642。

视频处理机应用于视频采集、视频处理、视频输出的视频实时处理。

视频处理机的解决方案有多种选择,但是市场主流产品一般选择两种方案:1)采用CPU+ASIC。

2)采用双CPU结构,即一个嵌入式CPU和一个专用信号处理芯片DSP。

受专用DSP芯片处理能力的限制,现有的嵌入式中使视频处理机的视频处理算法基本是H.263以下的标准。

l 硬件设计本文介绍一种基于TMS320DM642 DSP的视频采集设计方案。

其操作系统、通信协议、网络协议、音视频处理软件均在一颗TMS320DM642上实现,降低了开发的难度。

TMS320DM642芯片简介:TI公司的TMS320DM642(以下简称DM642)是一款专门面向多媒体应用的专用DSP。

该DSP时钟高达600MHz,8个并行运算单元,处理能力达4800MIPS(Million Instructions Per Second)每秒处理的百万级的机器语言指令数;采用二级缓存结构;具有64位外接存储器接口;兼容IEEE—1149.1(JTAG)边界扫描;为了面向多媒体应用,还集成了3个可配置的视频端口、面向音频应用的McASP(Multi Channel AudioSerial Pott)、10/100Mb/s的以太网MAC等外设。

鉴于DM642的上述优点,本网系视频处理机统以DM642为核心,完成音视频信号的实时采集、压缩及传输功能。

系统电路组成如图1所示。

从视频处理机的视频信号和从麦克风输入的音频信号经采集、A/D转换为数字信号后送入DSP。

DSP在信源处对音视频信号进行压缩编码和合流,然后通过局域网或因特网将数据传输给视频监控中心。

监控中心可同时监视多个现场,接收或发送报警信号,并根据需要通过异步串行总线RS-485实时控制,调整摄像头的方向和位置。

1.1 视频采集电路本系统采用的视频解码芯片是Philips公司的SAA7115。

52TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Overview Copyright ©2008–2014,Texas Instruments IncorporatedTable 3-25.General Purpose Input Output Terminal Functions (continued)SIGNAL NAME PIN NOTYPE (1)PULL (2)MUXED DESCRIPTION PTPZKB (3)GP7[14]is initially configured as a reserved function after reset and will not be in a predictable state.This signal will only be stable afterthe GPIO configuration for this pin has been ers should carefully consider the system implications of this pin being in an unknown state after reset.GP6EMB_D[15]/GP6[15]74F13I/O IPD EMIFB GPIO Bank 6EMB_D[14]/GP6[14]76E`6I/O IPD EMB_D[13]/GP6[13]78E13I/O IPD EMB_D[12]/GP6[12]79D16I/O IPD EMB_D[11]/GP6[11]80D15I/O IPD EMB_D[10]/GP6[10]82D14I/O IPD EMB_D[9]/GP6[9]83D13I/O IPD EMB_D[8]/GP6[8]84C16I/O IPD EMB_D[7]/GP6[7]62J16I/O IPD EMB_D[6]/GP6[6]63J15I/O IPD EMB_D[5]/GP6[5]64J13I/O IPD EMB_D[4]/GP6[4]66H16I/O IPD EMB_D[3]/GP6[3]68H13I/O IPD EMB_D[2]/GP6[2]70G16I/O IPD EMB_D[1]/GP6[1]72G13I/O IPD EMB_D[0]/GP6[0]73F16I/O IPD GP7EMU[0]/GP7[15]-J5I/O IPU JTAG RTCK/GP7[14](3)157K1I/O IPD General-Purpose IO signal EMB_A[11]/GP7[13]91B12O IPD EMIFB GPIO Bank 7EMB_A[10]/GP7[12]105A9O IPD EMB_A[9]/GP7[11]92C12O IPD EMB_A[8]/GP7[10]94D12O IPD EMB_A[7]/GP7[9]95A11O IPD EMB_A[6]/GP7[8]96B11O IPD EMB_A[5]/GP7[7]97C11O IPD EMB_A[4]/GP7[6]98D11O IPD EMB_A[3]/GP7[5]100A10O IPD EMB_A[2]/GP7[4]101B10O IPD EMB_A[1]/GP7[3]102C10O IPD EMB_A[0]/GP7[2]103D10O IPD EMB_BA[0]/GP7[1]107C9O IPU EMB_BA[1]/GP7[0]106B9O IPU (1)PWR =Supply voltage.3.6.21Reserved and No ConnectTable 3-26.Reserved and No Connect Terminal FunctionsSIGNAL NAMEPIN NO TYPE (1)DESCRIPTION PTP ZKB RSV1-F7-Reserved.(Leave unconnected,do not connect to power orground.)59TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Configuration Copyright ©2008–2014,Texas Instruments Incorporated 4.3Pullup/Pulldown ResistorsProper board design should ensure that input pins to the device always be at a valid logic level and not floating.This may be achieved via pullup/pulldown resistors.The device features internal pullup (IPU)and internal pulldown (IPD)resistors on most pins to eliminate the need,unless otherwise noted,for external pullup/pulldown resistors.An external pullup/pulldown resistor needs to be used in the following situations:•Boot and Configuration Pins:If the pin is both routed out and 3-stated (not driven),an external pullup/pulldown resistor is strongly recommended,even if the IPU/IPD matches the desired value/state.•Other Input Pins:If the IPU/IPD does not match the desired value/state,use an external pullup/pulldown resistor to pull the signal to the opposite rail.For the boot and configuration pins,if they are both routed out and 3-stated (not driven),it is strongly recommended that an external pullup/pulldown resistor be implemented.Although,internal pullup/pulldown resistors exist on these pins and they may match the desired configuration value,providing external connectivity can help ensure that valid logic levels are latched on these device boot and configuration pins.In addition,applying external pullup/pulldown resistors on the boot and configuration pins adds convenience to the user in debugging and flexibility in switching operating modes.Tips for choosing an external pullup/pulldown resistor:•Consider the total amount of current that may pass through the pullup or pulldown resistor.Make sure to include the leakage currents of all the devices connected to the net,as well as any internal pullup or pulldown resistors.•Decide a target value for the net.For a pulldown resistor,this should be below the lowest V IL level of all inputs connected to the net.For a pullup resistor,this should be above the highest V IH level of all inputs on the net.A reasonable choice would be to target the V OL or V OH levels for the logic family of the limiting device;which,by definition,have margin to the V IL and V IH levels.•Select a pullup/pulldown resistor with the largest possible value;but,which can still ensure that the net will reach the target pulled value when maximum current from all devices on the net is flowing through the resistor.The current to be considered includes leakage current plus,any other internal and external pullup/pulldown resistors on the net.•For bidirectional nets,there is an additional consideration which sets a lower limit on the resistance value of the external resistor.Verify that the resistance is small enough that the weakest output buffer can drive the net to the opposite logic level (including margin).•Remember to include tolerances when selecting the resistor value.•For pullup resistors,also remember to include tolerances on the IO supply rail.•For most systems,a 1-k Ωresistor can be used to oppose the IPU/IPD while meeting the above ers should confirm this resistor value is correct for their specific application.•For most systems,a 20-k Ωresistor can be used to compliment the IPU/IPD on the boot and configuration pins while meeting the above ers should confirm this resistor value is correct for their specific application.•For more detailed information on input current (I I ),and the low-/high-level input voltages (V IL and V IH )for the device,see Section 5.3,Recommended Operating Conditions.•For the internal pullup/pulldown resistors for all device pins,see the peripheral/system-specific terminal functions table.。

图像处理简介图像处理技术发展到今天,已经被应用到工程学、计算机科学、信息科学、统计学、物理学、化学、生物学、医学甚至社会科学等多个学科,并成为这些学科获取信息的重要来源及利用信息的重要手段,所以图像处理科学己经成为与国计民生紧密相连的一门应用科学。

图像处理技术研究的重点在于图像处理算法和系统结构,随着计算机、集成电路等技术的飞跃发展,图像处理技术在这两方面都取得了长足的发展。

但随着图像信息数据量的增大,图像处理算法复杂度的提高,图像处理技术依然面临着许多挑战性的问题,具体可概括为图像处理的网络化、复杂问题的求解与处理速度的高速化,可以通过选择合适的图像处理平台以及恰当的图像处理算法来解决这些挑战性的问题。

图像处理技术最初是在采用高级语言编程在计算机上实现的,后来还在计算机中加入了图像处理器(GPU),协同计算机的 CPU 工作,以提高计算机的图形化处理能力。

在大批量、小型化和低功耗的要求提出后,图像处理平台依次出现了基于 VLSI 技术的专用集成电路芯片((ASIC)和数字信号处理器((DSP),近年来,随着EDA 技术的发展以及FPGA(Field-Programmable Gate Array,现场可编程门阵列)技术的提高,越来越多的厂家和科研机构将FPGA 作为图像处理技术实现的主要平台,以提高图像处理系统的性能。

FPGA 是在PAL, GAL, CPLD 等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

4.2数字图像处理的硬件平台数字图像处理的发展是和计算机、集成电路等技术的发展密切相关的,曾经作为数字图像处理平台的有:计算机、专业集成电路、DSP 芯片和 FPGA,下面将按时间的顺序予以介绍。

从 1946 年到 1964 年,计算机分别进入了“电子管计算机时代,和“晶体管计算机时代”,这个时代的计算机才能称之为现代计算机,特别是进入“晶体管计算机时代”后,由于晶体管比电子管小得多,不需要暖机时间,消耗能量较少,处理更迅速、更可靠。

第 2 章TMS320C6000 DSP 芯片概述本章介绍了TI公司是DSP芯片和DSP芯片的命名规则,并着重介绍了TMS320DM642的器件特性及总体原理框图。

本章的知识要点为理解TMS320DM6 4的原理框图构成,本章建议安排 2 个课时进行学习。

2.1 DSP 芯片概述随着信息技术的高速发展,数字信号处理器(Digital Signal Processor,DSP)的应用范围越来越广,普及率越来越高。

DSP的应用领域主要包括:图形图像领域(如图形变换、图像压缩、图像传输、图像增强、图像识别等)、自动化控制领域(如导航和定位、振动分析、磁盘驱动、激光打印、机器人控制等)、消费电力领域(如智能玩具、扫描仪、机顶盒、VCD/DVD 可视电话、传真机等)、电子通信领域(如蜂窝电话、IP电话、无线调制解调器、数字语音嵌入等)、语音处理领域(如语音综合、语音增强、语音识别、语音编码等)、工业应用领域(如数字控制、机器人技术、在线监控等)、仪器仪表领域(如数字滤波器、函数发生器、瞬时分析仪、频谱分析仪、数据采集仪器等)、医疗器械领域(如诊断设备、助听器、病情监控器、心电图设备、超声设备等)、军事领域(如导弹制导、导航、雷达、保密通信等)。

因此,DSP 在当今电子通信类产品中起到了不可或缺的作用。

2.1.1 主要类型DSP 芯片主要分为以下两大类:(1)专用DSP芯片。

这类芯片被设计和加工成独立的电路模块,只能完成功能单一的任务,它们的使用场合比较特殊,通常应用于高速信号处理环境中,如执行FFT运算、数值滤波运算、卷积运算等,专用DSP芯片通过硬件逻辑实现信号处理算法,而不是采用内部编程的方法,这种机制保证了专用DSP芯片的执行效率、提高了其运算速度,专用DSP芯片在应用中无须程序设计。

只要根据其功能设计外围电路即可。

(2)通用可编程数字信号处理器(Programmable Digital Signal Processor)。

这类芯片通过嵌入内部的程序来调用自身的硬件资源,使用起来更加灵活,应用领域也更加广泛。

狭义上讲DSP是一种“更高”级别的单片机,它有着和单片机类似的输入输出引脚、定时器、计数器、外设接口、数据地址总线等,两者在功能组织方面存在着很多类似之处。

DSP 和单片机在应用领城中也有重叠的区域,比如二者均可以用在自动控制、信号处理和通信等领域,它们在这些领域中所起的作用.扮演的角色也类似。

但是,从深层次上分析,DSP和单片机之间又存在本质上的不同,表现为以下几个方面。

硬件资源方面的不同之处DSP具有较高的主频,DSP主频一般为几百兆赫,单片机的主频通常为几兆赫到几十兆赫,DSP主频远远高于单片机主频,DSP和单片机在主频上的差异决定了两者在处理数据速度上的巨大差距。

在硬件结构方面,DSP具有更多的数据总线和地址总线,并行处理数据的能力更加强大,DSP器件的数字信号处理功能表现尤为突出,TMS320DM64强大的视频处理功能就是一个典型的例子。

处理事务能力方面的不同之处DSP拥有强大且高效的硬件资源,其应用领域广、应用层面高,DSP的应用范围已经远远超越了单片机的应用范围,DSP能够处理更加复杂的综合性事务,涉及视频、音频、网络、图形图像等多种领域。

以上比较可帮助读者更好地理解DSP芯片的功能和作用。

应用系统使用DSP芯片还是单片机应视具体环境和要求而定,尽管DSP芯片拥有较高的运算速度,但DSP电路系统设计复杂,研发成本高,所以并不是所有的场合都适合选用DSP芯片。

DSF芯片的生产厂家很多,类型多样,主要的产品如表2-1所示。

2.1.2 TI 公司的DSP芯片TI 公司是DSP芯片的主要生产厂家之一,该公司研发出多歌高性能的DSP产品,例如定点型DSP芯片C1x、C2x、C2xx、C5x、C54x 和C6x 等,浮点型DSP芯片C3x、C4x、C67x 等,多处理器型DSP芯片C8x等。

从DSP芯片出现的先后顺序来看,TT公司的DSP产品主要经历了7个发展阶段,如表2-2所示:从功能上来划分,TI公司的DSP芯片主要包括TMS32OC2OO0 TMS320C3000、TMS320C5000和TMS320C600C等几个系列。

TMS320C2000系列DSP芯片的硬件结构更多地考虑了工业应用环境,适合在机电控制、电力电子系统中应用,如照明控制、光纤网络、工业自动化等相关产品。

TMS320C300C系列DSP芯片适合在数字音频、激光打印机、扫描仪、读码器、视频会议、工业自动化、机器人和伺服控制产品中应用。

TMS320C5000系列DSP芯片适合通信设备的开发,如媒体播放器、3G电话、电子图书、无线Modem GPS接收装置、指纹识别系统等。

TMS320C6000系列DSP芯片的硬件结构功能强大,适用于高速信号处理设备中,如图像图形处理、无线网络、多媒体网关、宽带视频转换器、视频主/从模式服务器和网络相机等。

TMS320C2000系列DSP芯片主要包括两种类型:一类是TMS320F28X子系列芯片,另一类是TMS320F24X子系列芯片。

F28x子系列DSP芯片的片上资源比F24x子系列DSP芯片的片上资源丰富,适合在高精度控制系统中应用. C2000系列DSP芯片内部带有FLASH存储器,可以直接存储程序,无须再外扩FLASH存储器,这是C2000系列DSP程序存储上的优势。

根据时钟频率来划分,C2000系列DSP芯片包括3个层次:F2810、F2812等芯片为第1层次,该类芯片的指令执行速度为150MIPS; F243、LF2403A、LF2402A、LF2406A、LC2406A、LF2407A 等芯片为第2 层;C242F241、LC2404A, LC2402A, LF2401A 等芯片为第3层次。

第2层次和第3层次芯片的指令执行速度为40MIPS.相对较慢。

TI公司的浮点型DSP芯片包括两类:一类是TMS320C300係列DSP芯片.另一类是TMS32067X系列DSP芯片。

C31/C32属于C3000系列芯片的早期产品,主频为60MHz以此为基础延生出主频80MHz的C31和主频60/75MHZ的C33。

TMS32067X系列DSP芯片属于高档浮点型信号处理器,C6701为最精简的一种,工作主频167MHz以此款芯片为基础相继延生出多种类型的C67x芯片,如工作主频225MHz的C6713,工作主频100MHz的C6712,工作主频150MHz的C6712C和工作主频200MHz的6711C等。

TMS320C5000系列DSP芯片主要包括TMS320C54)子系列和TMS320C55x子系列,根据时钟频率划分为多个层次,C5401 (50MIPS)、C5402 (100-160MIPS )、C5404 (120MIPS )、C5407 (120MIPS)、C5409 (80-160MIPS), C5410 (100-160MIPS )和C5416 (120-160MIPS)等芯片位于C5000系列的底层,在这些底层芯片的基础上,C5000系列DSP芯片划分为3种应用级别的器件;(1)应用功能较强级别的DSP芯片,如C5501 (400MIPS )、C5502(400MIPS)、C5509 (288-400MIPS)、C5510 (320-400MIPS)等,这一类芯片逐渐向C55X™ 技术的芯片方向发展;(2)精简指令集型的DSP芯片,相继出现了C5470 (C54x +ARM7)、C5471(C54x+ARM7) OMAP5910(C55x+ARM9)等,该类芯片向OMAP、C55x™和ARM9集成型芯片发展;(3)C5000多核DSP芯片,女口C5420 (200MIPS)、C5421 (200MIPS), C5441(532MIPS) 等,在此基础上,将进一步向C55X™多核DSP芯片发展。

TMS320C600C系列DSP芯片已衍生出多个子系列,包括C62x子系列、C64x子系列和C67x 子系列(浮点型DSP, C6201、C6202、C6203、C6211、C6204、C6205、C6701、C6711、C6712 和C6713 属于第1 代C6000 芯片,C6414, C6415、C6416 C6411、C6412 和DM642 为第2代C6000芯片,第3代C6000芯片尚处于研发阶段.主要目标是多核DSP芯片、新型1.0GHz C64x子系列芯片和高档浮点型DSP芯片。

C6000系列DSP芯片包括的类型非常多,应用领域存在较大差别,如C6414用于一般系统产品、06416用于3G无线网络产品、C6412用于嵌入式通信设备、C6411用于多媒体网关产品等。

本书主要对TMS320C6000系列DSP芯片C64x子系列进行阐述。

2.1.3 TI 公司DSP S片的命名规则TI公司的DSP芯片类型多样,在选择DSP芯片时一定要仔细辨别芯片表面的标识,以免选错器件。

以TMS32OC6412型DSP芯片为例,介绍TI公司DSP芯片的命名规则,TMS320C6412芯片的符号含义如图2-1所示.“TMS为芯片标识的前缀,“ 320”表示芯片的类别,“C”表示芯片采用了CMOS加工工艺,“6412 ”表示芯片的型号,“GDK表明芯片的封装类型,“()”内部的数字一般表示芯片正常工作时的温度范围,“600”表示芯片的主频或工作频率。

TI公司的DSP芯片类型众多,对芯片名称中的标识进行归纳,各字段含义如表2-3所示。

图2-1 TI 公司DSR芯片命名规则2.2 TMS320DM642 DSP 芯片概况TMS320DM64是TI公司于2003年左右推出的一款32位定点DSP芯片,主要面向数字媒体,属于C6000系列DSP芯片。

DM642保留了C64x原有的内核机构及大部分外设的基础上增加了3个双通道数字视频口,可同时处理多路数字视频流。

2.2.1 DM642 概述TMS320C64X DSF芯片(包括TMS320DM642勺装置)是TMS320C6000 DSF平台上具有最高性能的定点DSFTMS320DM642DM642)是基于由德州仪器(TI )开发的超长指令字(VLIW) 结构,因而DM642芯片是数字媒体应用的最优选择。

DM642在主频720MHz下处理速度达到5760MIPS, C64x DSF核具有64个32位字长的通用寄存器和8个独立的功能单元。

DM642每周期能够提供4个16位MACs每秒可提供2880百万个MACs或者8个8位MACs每秒5760MMAC。

DM642具有一个两层的缓存结构和一个强大且多样的外设设备。