VHDL四位全加器三种语言编程

- 格式:doc

- 大小:15.55 KB

- 文档页数:3

实验一四位串行进位加法器的设计一、实验目的1.理解一位全加器的工作原理2.掌握串行进位加法器的逻辑原理3.进一步熟悉Quartus软件的使用,了解设计的全过程,二、实验容1.采用VHDL语言设计四位串行进位的加法器2.采用画原理图的方法设计四位串行进位加法器三、实验步骤1、使用VHDL语言设计1.打开File—>New Project Wizard输入文件名adder4保存在D 盘,打开File—>New—>VHDL File,从模版中选择库的说明,use 语句的说明,实体的说明,结构体的说明,编写VHDL代码,然后保存、编译。

打开File—>New—>Other File—>Vector Waveform File,查找引脚,从Edit中选择End Time 输入40、ns 保存。

从Assignments—>Settings—>Simulator Settings —>Functional然后Processing—>Generate Functional Simnlation Netlist —>确定。

选择Start Simulation保存最后的波形图,打开File —>close关闭工程。

底层文件:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY fadder ISPORT(a, b,cin : IN STD_LOGIC;s, co : OUT STD_LOGIC);END fadder;ARCHITECTURE arc1 OF fadder ISBEGINs<=a xor b xor cin;co<=((a xor b)and cin)or(a and b);END arc1;顶层文件:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY adder4 ISPORT(c0: IN STD_LOGIC;a,b : IN STD_LOGIC_VECTOR(3 DOWNTO 0);s : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);c4 : OUT STD_LOGIC);END adder4;ARCHITECTURE arc2 OF adder4 ISCOMPONENT fadderPORT(a, b,cin : IN STD_LOGIC;s, co : OUT STD_LOGIC);END COMPONENT;SIGNAL carry : STD_LOGIC_VECTOR(3 DOWNTO 1); BEGINu1 : fadder PORT MAP (a=>a(0), b=>b(0),cin=>c0,s=>s(0),co=>carry (1));u2 : fadder PORT MAP (a=>a(1),b=>b(1),cin=>carry(1),s=>s(1),co=>carry (2));u3 : fadder PORT MAP (a=>a(2),b=>b(2),cin=>carry(2),s=>s(2),co=>carry (3));u4 : fadder PORT MAP(a=>a(3),b=>b(3),cin=>carry(3),s=>s(3),co=>c4);END arc2;2、使用原理图的方法设计打开File—>New Project Wizard输入文件名adder4保存在D 盘,打开File—>New—>VHDL File,从模版中选择库的说明,use 语句的说明,实体的说明,结构体的说明,编写VHDL代码,然后选择File-->Create/Update-->Create Symbol Files for Current File,选择File-->New-->Other File-->Vector Waveform File,查找引脚,从Edit中选择End Time 输入40、ns 保存。

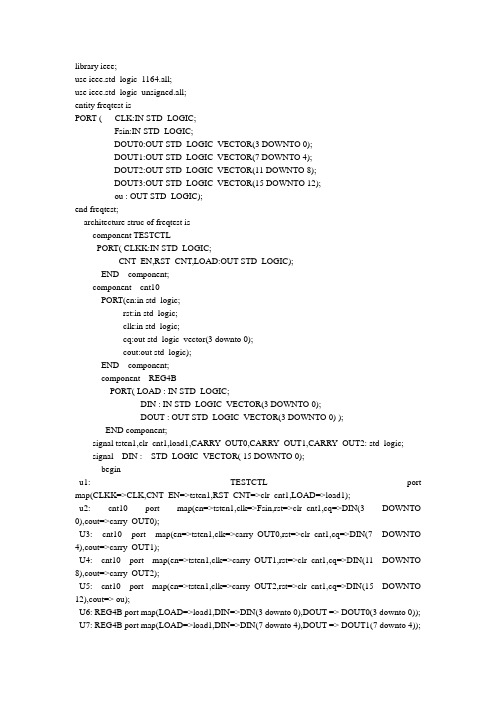

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity freqtest isPORT ( CLK:IN STD_LOGIC;Fsin:IN STD_LOGIC;DOUT0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT1:OUT STD_LOGIC_VECTOR(7 DOWNTO 4);DOUT2:OUT STD_LOGIC_VECTOR(11 DOWNTO 8);DOUT3:OUT STD_LOGIC_VECTOR(15 DOWNTO 12);ou : OUT STD_LOGIC);end freqtest;architecture struc of freqtest iscomponent TESTCTLPORT( CLKK:IN STD_LOGIC;CNT_EN,RST_CNT,LOAD:OUT STD_LOGIC);END component;component cnt10PORT(en:in std_logic;rst:in std_logic;clk:in std_logic;cq:out std_logic_vector(3 downto 0);cout:out std_logic);END component;component REG4BPORT( LOAD : IN STD_LOGIC;DIN : IN STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) );END component;signal tsten1,clr_cnt1,load1,CARRY_OUT0,CARRY_OUT1,CARRY_OUT2: std_logic;signal DIN : STD_LOGIC_VECTOR( 15 DOWNTO 0);beginu1: TESTCTL port map(CLKK=>CLK,CNT_EN=>tsten1,RST_CNT=>clr_cnt1,LOAD=>load1);u2: cnt10 port map(en=>tsten1,clk=>Fsin,rst=>clr_cnt1,cq=>DIN(3 DOWNTO 0),cout=>carry_OUT0);U3: cnt10 port map(en=>tsten1,clk=>carry_OUT0,rst=>clr_cnt1,cq=>DIN(7 DOWNTO 4),cout=>carry_OUT1);U4: cnt10 port map(en=>tsten1,clk=>carry_OUT1,rst=>clr_cnt1,cq=>DIN(11 DOWNTO 8),cout=>carry_OUT2);U5: cnt10 port map(en=>tsten1,clk=>carry_OUT2,rst=>clr_cnt1,cq=>DIN(15 DOWNTO 12),cout=> ou);U6: REG4B port map(LOAD=>load1,DIN=>DIN(3 downto 0),DOUT => DOUT0(3 downto 0)); U7: REG4B port map(LOAD=>load1,DIN=>DIN(7 downto 4),DOUT => DOUT1(7 downto 4));U8: REG4B port map(LOAD=>load1,DIN=>DIN(11 downto 8),DOUT => DOUT2(11 downto 8));U9: REG4B port map(LOAD=>load1,DIN=>DIN(15 downto 12),DOUT => DOUT3(15 downto 12));END struc;。

四位全加器的VHDL实现通信0704 王学申0120703490117一、设计要求:采用QuartusII或Max+PlusII集成开发环境,利用VHDL硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四位进位加法器。

二、设计分析加法器是数字系统中的基本逻辑器件。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

实现多位二进制数相加的电路称为加法器,它能解决二进制中1+1=10的功能(当然还有 0+0、0+1、1+0).三、加法器的分类(一)半加器能对两个1位二进制数进行相加而求得和及进位的逻辑电路称为半加器。

或:只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路,称为半加器。

图1为半加器的方框图。

图2为半加器原理图。

其中:A、B分别为被加数与加数,作为电路的输入端;S为两数相加产生的本位和,它和两数相加产生的向高位的进位C一起作为电路的输出。

图1 半加器图2 半加器原理图根据二进制数相加的原则,得到半加器的真值表如表1所列。

信号输入信号输出A B S C0 0 0 00 1 1 01 0 1 01 1 0 1表1 半加器的真值表由真值表可分别写出和数S,进位数C的逻辑函数表达式为:(1) C=AB (2)由此可见,式(1)是一个异或逻辑关系,可用一个异或门来实现;式(2)可用一个与门实现。

仿真结果如图3所示:图3 半加器仿真图(二)全加器除本位两个数相加外,还要加上从低位来的进位数,称为全加器。

图4为全加器的方框图。

图5全加器原理图。

被加数A i、加数B i从低位向本位进位C i-1作为电路的输入,全加和S i与向高位的进位C i作为电路的输出。

能实现全加运算功能的电路称为全加电路。

实验四全加器的设计一、实验目的通过VHDL语言设计4位全加器,掌握加法器的设计方法;学习利用软件工具的模块封装(1位全加器)及连接使用方法,在软件工具的原理图输入法下完成4位全加器的设计。

二、实验原理根据数字电路全加器的理论知识,按图1所示的1位全加器的管脚图进行设计。

图 1 1位全加器管脚图三、实验内容用VHDL语言设计1位全加器,进行编译、波形仿真及器件编程。

代码一见附录,仿真图如下图 2 1位全加器功能仿真图使用原理图设计4位全加器进行编译、波形仿真及器件编程。

原理图如下仿真图如下用VHDL语言设计4位全加器,进行编译、波形仿真及器件编程,代码二见附录,仿真图如下图 5 4位全加器功能仿真图附录代码一、library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity swqjq isport (a,b:in std_logic;ci:in std_logic;co:out std_logic;s:out std_logic);end swqjq;architecture zhang of swqjq isbeginprocess (a,b,ci)beginif(a='0'and b='0'and ci='0') thens<='0';co<='0';elsif(a='1'and b='0'and ci='0') thens<='1';co<='0';elsif(a='0'and b='1'and ci='0') thens<='1';co<='0';elsif(a='1'and b='1'and ci='0') thens<='0';co<='1';elsif(a='0'and b='0'and ci='1') thens<='1';co<='0';elsif(a='0'and b='1'and ci='1') thens<='0';co<='1';elsif(a='1'and b='0'and ci='1') thens<='0';co<='1';elses<='1';co<='1';end if;end process;end zhang;代码二、library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder4b isport ( ci:in std_logic;a,b:in std_logic_vector(3 downto 0);s:out std_logic_vector(3 downto 0);co:out std_logic);end adder4b;architecture zhang of adder4b issignal sint:std_logic_vector(4 downto 0); signal aa,bb:std_logic_vector(4 downto 0); beginaa<='0'&a(3 downto 0);bb<='0'&b(3 downto 0);sint<=aa+bb+ci;s(3 downto 0)<=sint(3 downto 0);co<=sint(4);end zhang;。

电子设计自动化实验实验名称综合性实验二、硬件描述语言的层次化设计实验设备(1) EDA实验箱 ( 型号 ), ( 2)计算机 , ( 3) EDA软件( QuartusII )实验目的1、熟悉 EDA软件( QuartusII)的硬件描述语言输入设计方法;2、掌握 VHDL语言的层次化设计方法和仿真分析方法;3、了解功能仿真、时序仿真和时序参数分析的意义。

实验内容1、用 VHDL语言完成 4 位十进制计数器、 4 位锁存器、测频控制器的设计,包括编译、综合、仿真;**2、采用层次化设计的方法,用VHDL语言的元件例化语句写出 4 位十进制频率计的顶层文件,并分别给出其测频功能和时序仿真分析波形图,并加以分析;**3、用 EDA实验箱进行硬件验证,并分析测量结果; 建议硬件测试实验电路采用电路结构,待测信号F_IN 接 clock0 ;测频控制时钟CLK接 clock2 ; **4、在 2 基础上将其扩展为8 位十进制频率计,或带译码输出的 4 位十进制频率计。

实验报告要求根据以上实验内容写出实验报告:1、简述 4 位频率计模块的工作原理及其设计、编译、仿真分析过程;2、给出模块设计文件、仿真测试文件、仿真结果波形图及其分析报告;3、简述硬件验证过程和验证结果。

1、简述 4 位频率计模块的工作原理根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为 1 秒的对输入信号脉冲计数允许的信号; 1 秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器清0 信号。

这 3 个信号可以由一个测频控制信号发生器产生,即TESTCTL,它的设计要求是,TESTCTL的计数使能信号CNT_EN能产生一个1 秒脉宽的周期信号,并对频率计的每一计数器 CNT10的 ENA使能端进行同步控制。

当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要产生一个锁存信号LOAD,在该信号上升沿时,将计数器在前1 秒钟的计数值锁存进各锁存器REG4B中,并由外部的7 段译码器译出,显示计数值。

VHDL四位全加器三种语言编程四位全加器的三种VHDL语言描述方式:一:数据流描述方式libraryieee;use ieee.std_logic_1164.all;entity add1 isport(a,b,cin:instd_logic;s,cout:outstd_logic);end add1;architecture dataflow of add1 isbegins<=(a xor b) xorcin;cout<=((a xor b)and cin)or(a and b);end dataflow;二:行为描述方式libraryieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entity add22 isport(a,b,cin:instd_logic;s,co:outstd_logic);end add22;architecture dataflow of add22 issignaltmp:std_logic;beginprocess(a,b,cin)variable n:integer range 0 to 3;constants_vector:std_logic_vector(3 downto 0):="1010"; constantco_vector:std_logic_vector(3 downto 0):="1100"; beginn:=0;if a='1' then n:=n+1;end if;if b='1' then n:=n+1;end if;ifcin='1' then n:=n+1;end if;s<=s_vector(n) after 10 ;co<=co_vector(n);end process;end dataflow;三:结构描述方式Library ieee;Use ieee.std_logic_1164.all; Entity and_2 is port(a,b: in std_logic;c: out std_logic);End and_2;Architecture behave of and_2 is beginc<= (a and b);End behave;Library ieee;Use ieee.std_logic_1164.all; Entity or_2 is port(a,b: in std_logic;c: out std_logic);End or_2;Architecture behave of or_2 is beginc<= (a or b);End behave;Library ieee;Use ieee.std_logic_1164.all; Entity xor_2 isport(a,b: in std_logic;c: out std_logic);End xor_2;Architecture behave of xor_2 is beginc<= (a xor b);End behave;Library ieee;Use ieee.std_logic_1164.all; Entity add33 isport(A,B,Cin: in std_logic; Co,S: out std_logic);End add33;Architecture structure of add33 is component and_2port(a,b: in std_logic;c: out std_logic);End component;component or_2port(a,b: in std_logic;c: out std_logic);End component;component xor_2port(a,b: in std_logic;c: out std_logic);End component;signal tmp1,tmp2,tmp3:std_logic; beginu1:xor_2 port map(A,B,tmp1);u2:and_2 port map(tmp1,Cin,tmp2); u3:xor_2 port map(tmp1,Cin,S);u4:and_2 port map(A,B,tmp3);u5:or_2 port map(tmp2,tmp3,Co); End structure;。

4位⼆进制全加器的设计4位⼆进制全加器的设计摘要加法器是产⽣数的和的装置。

加数和被加数为输⼊,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输⼊,⽽和数与进位为输出则为全加器。

常⽤作计算机算术逻辑部件,执⾏逻辑操作、移位与指令调⽤。

在电⼦学中,加法器是⼀种数位电路,其可进⾏数字的加法计算。

在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。

加法器可以⽤来表⽰各种数值,如:BCD、加三码,主要的加法器是以⼆进制作运算。

多位加法器的构成有两种⽅式:并⾏进位和串⾏进位⽅式。

并⾏进位加法器设有并⾏进位产⽣逻辑,运⾏速度快;串⾏进位⽅式是将全加器级联构成多位加法器。

通常,并⾏加法器⽐串⾏加法器的资源占⽤差距也会越来越⼤。

我们采⽤4位⼆进制并⾏加法器作为折中选择,所选加法器为4位⼆进制先⾏进位的74LS283,它从C0到C4输出的传输延迟很短,只⽤了⼏级逻辑来形成和及进位输出,由其构成4位⼆进制全加器,并⽤Verilog HDL进⾏仿真。

关键字全加器,四位⼆进制,迭代电路,并⾏进位,74LS283,Verilog HDL仿真总电路设计⼀、硬件电路的设计该4位⼆进制全加器以74LS283(图1)为核⼼,采⽤先⾏进位⽅式,极⼤地提⾼了电路运⾏速度,下⾯是对4位全加器电路设计的具体分析。

图11)全加器(full-adder )全加器是⼀种由被加数、加数和来⾃低位的进位数三者相加的运算器。

基本功能是实现⼆进制加法。

全加器的功能表输⼊输出输⼊输出逻辑表达式:CI B A S ⊕⊕==AB'CI'+A'BCI'+A'B'CI+ABCI()AB CI B A CO ++=其中,如果输⼊有奇数个1,则S 为1;如果输⼊有2个或2个以上的1,则CO=1。

实现全加器等式的门级电路图如图2所⽰,逻辑符号如图3所⽰.图2 图32)四位⼆级制加法器 a) 串⾏进位加法器四位⼆进制加法器为4个全加器的级联,每个处理⼀位。

vhdl编程实例VHDL编程实例- 设计与实现一个4位的全加器在本篇文章中,我们将一步一步地回答如何设计和实现一个4位的全加器。

VHDL编程语言将是我们用于描述和模拟这个电路的工具。

第一步:理解全加器的原理在编写代码之前,我们首先需要理解全加器的原理。

全加器是一种用于对两个二进制数字进行相加的电路。

它接收三个输入信号:两个位的输入(A 和B)以及一个进位输入(C_in)。

全加器的输出结果为一个位的和(S)和一个进位输出(C_out)。

我们可以使用如下的真值表来描述全加器的输出结果:输入信号输出结果A B C_in S C_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1了解了全加器的工作原理后,我们可以开始编写代码了。

第二步:编写全加器的VHDL代码我们将使用VHDL语言来描述和模拟全加器。

下面是一个简单的4位全加器的VHDL代码实现:vhdlEntity声明entity full_adder isport (A, B : in std_logic_vector(3 downto 0);C_in : in std_logic;S : out std_logic_vector(3 downto 0);C_out : out std_logic);end full_adder;Architecture声明architecture Behavioral of full_adder isbeginprocess(A, B, C_in)variable carry : std_logic;begincarry := C_in;for i in 0 to 3 loopS(i) <= A(i) xor B(i) xor carry;carry := (A(i) and B(i)) or (carry and (A(i) xor B(i)));end loop;C_out <= carry;end process;end Behavioral;在此代码中,我们首先声明了一个实体(entity)和一个架构(architecture)。

电子科技大学UNIVERSITY OF ELECTRONIC SCIENCE AND TECHNOLOGY OF CHINA数字逻辑设计实验报告实验题目: 4bit模9加法器学生姓名:指导老师:一、实验内容设计一个4bit模9加法器。

输入为两个4bit的二进制数,输出为两数相加后模9的结果。

其数学表达式为:y=(x1+x2)mod 9。

二、实验要求1、功能性要求:能够实现4bit无符号数的模9加法运算,即输入两个4比特数据时能够正确输出其相加并模9运算结果。

2、算法要求:模加法器有多种算法,可采用任意算法进行设计。

3、设计性要求:采用全加器、半加器和基本门结构化描述。

能够编写Test Bench文件,并利用Modelsim进行仿真。

在Modelsim仿真正确的基础上,能够生成bit文件并上板验证其正确性。

4、基本上板要求:在上板实验时,输入的两个4bit数采用拨码开关输入,输出采用LED灯进行显示。

三、设计思路1、整体思路:为了实现4bit无符号数的模9加法运算,可以先将两个4bit的加数a和b 先分别模9,相加之后再模9得到最终结果。

2、模9器:先找出读入的5bit数与模9后的4bit数之间的关系,画出卡诺图,再根据卡诺图得出其相应的逻辑表达式即可。

设读入的5bit数为carry、a、b、c、d,模9后得到的4bit数为w、x、y、z。

则化简后得到的逻辑表达式分别为:w = carry’ab’c’d’,x= carry’bc + carry’a’b + carry’bd + carrya’b’c’d’,y = carry’a’c + carry’cd + carry’abc’d’ + carrya’b’c’d’,z= carry’a’d + carry’acd’ + carry’abd’ + carry a’b’c’d’。

3、全加器:全加器可以实现两个1bit数a、b和进位输入cin的相加,其真值表如下所示:这里全加器由半加器和或门构成,其原理图如下:4、半加器:半加器是全加器的基本组成单元,可以实现两个1bit数a和b的相加,并将进位输出,其真值表如下:半加器由一个异或门和一个与门构成,其原理图如下所示:5、数码管显示:单个数码管一共有7个端(不含小数点),用来表示组成一个数字的7个部分,故只要找到这7个段和模9后的4bit数间的对应关系,将其画出卡诺图并化简成逻辑表达式即可。

VHDL语言简介VHDL(VHSIC Hardware Description Language)即可高速集成电路硬件描述语言,是一种用于描述数字系统和电路的硬件描述语言。

它在1981年由美国国防部的高速集成电路联合委员会(VHSIC)开发,用于设计大规模集成电路。

VHDL是一种面向对象的语言,可以用于描述各种数字系统,从简单的逻辑门到复杂的处理器。

它提供了丰富的语法和语义,使得设计人员可以准确地描述他们的电路和系统。

VHDL的优势VHDL作为一种硬件描述语言,在数字系统设计中具有许多优势。

1.可重用性:VHDL允许设计人员创建可重用的模块和子系统,这些模块和子系统可以在不同的项目中重复使用,提高了设计效率和可维护性。

2.仿真和验证:VHDL具有强大的仿真和验证能力,可以在设计之前对系统进行全面的仿真和验证。

这有助于检测和纠正潜在的问题,并确保系统在硬件实现之前达到预期的功能。

3.抽象级别:VHDL允许设计人员在不同的抽象级别上描述系统,从高级的行为级别到底层的结构级别。

这使得设计人员可以根据需要在不同的级别上工作,并且可以更容易地进行系统级别的优化。

4.灵活性和可扩展性:VHDL支持灵活的设计方法和工作流程,并允许设计人员在设计过程中进行迭代和修改。

它还可以与其他常用的设计工具和方法集成,以满足特定的需求。

VHDL语言的基本结构VHDL语言由模块、实体、架构以及信号和过程等基本元素组成。

模块(Module)模块是VHDL中描述数字系统的最基本单位。

一个模块可以包含多个实体和架构,并通过连接信号进行通信。

每个模块都有一个顶层实体和一个或多个架构。

实体(Entity)实体是描述模块的接口和行为的抽象。

它定义了输入输出端口,以及模块对外部环境的接口。

一个实体可以有一个或多个架构。

架构(Architecture)架构描述模块的具体行为和内部结构。

它定义了模块的内部信号和过程,以及对外部信号和过程的接口。

四位全加器的三种VHDL语言描述方式:

一:数据流描述方式

libraryieee;

use ieee.std_logic_1164.all;

entity add1 is

port(a,b,cin:instd_logic;

s,cout:outstd_logic);

end add1;

architecture dataflow of add1 is

begin

s<=(a xor b) xorcin;

cout<=((a xor b)and cin)or(a and b);

end dataflow;

二:行为描述方式

libraryieee;

use ieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entity add22 is

port(a,b,cin:instd_logic;

s,co:outstd_logic);

end add22;

architecture dataflow of add22 is

signaltmp:std_logic;

begin

process(a,b,cin)

variable n:integer range 0 to 3;

constants_vector:

std_logic_vector(3 downto 0):="1010"; constantco_vector:

std_logic_vector(3 downto 0):="1100";

begin

n:=0;

if a='1' then n:=n+1;

end if;

if b='1' then n:=n+1;

end if;

ifcin='1' then n:=n+1;

end if;

s<=s_vector(n) after 10 ;

co<=co_vector(n);

end process;

end dataflow;

三:结构描述方式

Library ieee;

Use ieee.std_logic_1164.all; Entity and_2 is

port(a,b: in std_logic;

c: out std_logic);

End and_2;

Architecture behave of and_2 is begin

c<= (a and b);

End behave;

Library ieee;

Use ieee.std_logic_1164.all; Entity or_2 is

port(a,b: in std_logic;

c: out std_logic);

End or_2;

Architecture behave of or_2 is begin

c<= (a or b);

End behave;

Library ieee;

Use ieee.std_logic_1164.all; Entity xor_2 is

port(a,b: in std_logic;

c: out std_logic);

End xor_2;

Architecture behave of xor_2 is begin

c<= (a xor b);

End behave;

Library ieee;

Use ieee.std_logic_1164.all; Entity add33 is

port(A,B,Cin: in std_logic; Co,S: out std_logic);

End add33;

Architecture structure of add33 is component and_2

port(a,b: in std_logic;

c: out std_logic);

End component;

component or_2

port(a,b: in std_logic;

c: out std_logic);

End component;

component xor_2

port(a,b: in std_logic;

c: out std_logic);

End component;

signal tmp1,tmp2,tmp3:std_logic; begin

u1:xor_2 port map(A,B,tmp1);

u2:and_2 port map(tmp1,Cin,tmp2); u3:xor_2 port map(tmp1,Cin,S);

u4:and_2 port map(A,B,tmp3);

u5:or_2 port map(tmp2,tmp3,Co); End structure;。